# Adaptive Microscopy on Integrated Circuit Structures in Scanning Electron Microscope Images

Ronald Wilson<sup>1\*</sup>, Navid Asadizanjani<sup>1</sup>, Domenic Forte<sup>1</sup> and Damon L. Woodard<sup>1</sup>

<sup>1</sup>. Department of Electrical and Computer Engineering, University of Florida, Gainesville, USA

\* Corresponding author: ronaldwilson@ufl.edu

Scanning Electron Microscopy (SEM) has played a substantial role as an enabler in understanding various aspects in the lifecycle of Integrated Circuits (IC) ranging from the assistance in design verification and quality assurance during the manufacturing phase[1,2] to the detection of various hardware exploits, such as trojan<sup>1</sup> inserted in the circuit with malicious intent[3]. In the past, when ICs were small and simple, it was common for engineers to perform these procedures manually using optical microscopy images[4]. However, with the ongoing trend of trying to pack in more logic gates and other structures into an IC of limited size, SEM imaging has been one of the most common methods to obtain high definition images of the structures in the IC.

Despite being able to address its scope in the industry, the imaging modality still has a major shortcoming. In [3], the scanning time for an IC of size 1.5mm x 1.5mm employing a 130nm node technology was estimated to be about 24 minutes for a low quality image to 30 days for a high definition image. With current node technology being less than 20 nm, the time frame required for acquiring all the structures in the IC with reasonable quality is unfeasible. Also, unlike other fields of engineering currently using SEM, any errors induced by the imaging modality due to lack of image quality would certainly change the purpose and underlying functionality of the circuit. Hence, there is a need for an approach that would address this problem, and, in this paper, we are introducing a method that will help resolve this issue.

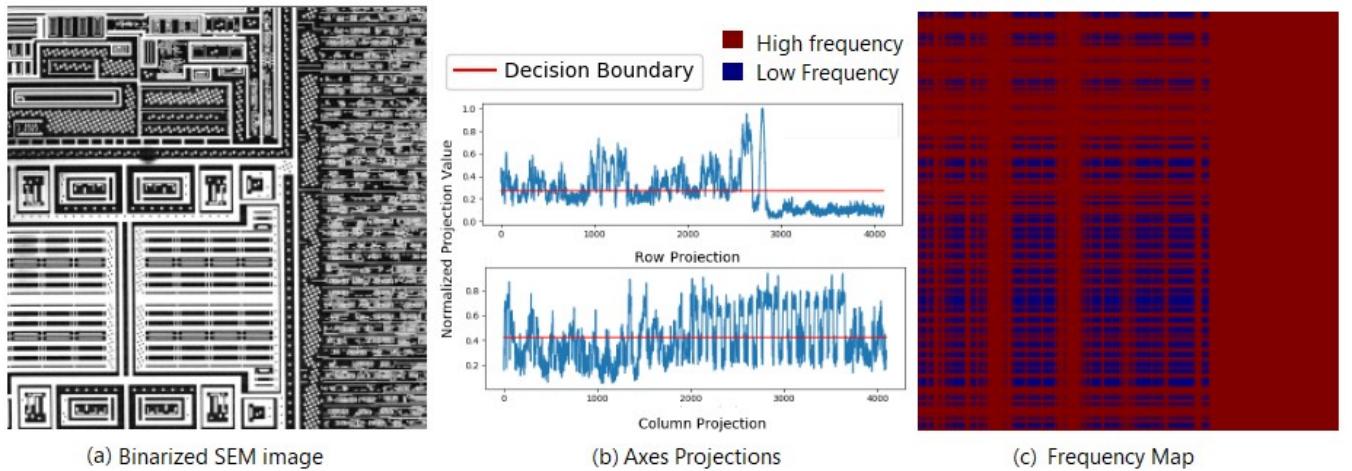

The SEM image in Fig. 1(a), shows a typical frame from an IC. It can be observed that the structures in the IC are of various sizes and so, can be logically reasoned that structures having relatively large and uncomplicated shapes can be imaged at a lower quality and complicated structures at a higher quality without considering their contextual or functional meaning. This would help reduce imaging times for the entire IC.

The proposed method, firstly, requires the binarization of the image with a traditional image processing algorithm such as thresholding. It then involves the extraction of run-length encoded components in the image and the projection of the SEM image onto its axes. A run-length encoded component is defined as the length of sequence of adjacent pixels in the image with the same pixel value. The projection for either axis can be calculated as the sum of all run-length encoded components divided by the frequency of the corresponding component. The projections can also be normalized by the length of axes for easy visual interpretation. However, this normalization provides no additional benefit to the method.

Intuitively, the method assigns a higher penalty for short run-length encoded components with high frequency and low penalty for long run-length encoded components with low frequency. In simpler terms, the projection of high frequency components approaches zero while low frequency components continue to move further away from zero. This can be seen from Fig. 1(b). The projection values are

then thresholded for a decision boundary. In the paper, the decision boundary is taken as the mean of the projection. However, depending on the type of material imaged, the decision boundary can be quantized to more than 2 regions based on the parameters in the imaging modality and time constraints on the image acquisition phase. Any region in the image having either projections less than the decision boundary are marked as high frequency and the rest as low frequency. Fig. 1(c) shows the result of the application of the method on the sample shown in Fig. 1(a).

Comparing the results given in Fig. 1, the proposed method was able to localize high and low frequency regions of the image successfully. This information can then be used to dynamically change the imaging parameters as necessary for different regions of the sample rather than using a constant setting for the entire sample. Considering the fact that low quality imaging takes significantly less time than high quality imaging[3], the time required to image a sample would only be constrained by the high frequency regions present in the sample. In conclusion, depending on the complexity of the structures in the sample, application of our algorithm will cause a reduction in imaging time for the entire sample.

**Figure 1.** An example workflow in the algorithm from left to right. The example shows an SEM image of the metal layer of an IC employing 130nm node technology imaged at 100 $\mu$ m, 10 $\mu$ s/pixel, 1024x1024 at 5 kV for the magnification, dwelling time, resolution and excitation voltage respectively

## References:

- [1] Soden, Jerry M., and Richard E. Anderson. "IC failure analysis: techniques and tools for quality reliability improvement." *Proceedings of the IEEE 81.5* (1993): 703-715.

- [2] May, Gary S., and Costas J. Spanos. *Fundamentals of semiconductor manufacturing and process control*. John Wiley & Sons, 2006:95-96

- [3] Vashistha, N., Rahman, M. T., Shen, H., Woodard, D. L., Asadizanjani, N., & Tehranipoor, M. (2018). Detecting Hardware Trojans Inserted by Untrusted Foundry Using Physical Inspection and Advanced Image Processing. *Journal of Hardware and Systems Security*, 2(4), 333-344.

- [4] Torrance, Randy, and Dick James. "The state-of-the-art in IC reverse engineering." *Cryptographic Hardware and Embedded Systems-CHES 2009*. Springer, Berlin, Heidelberg, 2009. 363-381.