# An ISI Scrambling Technique for Dynamic Element Matching Current-Steering DACs

Jason Remple, Andrea Panigada, and Ian Galton, Fellow, IEEE

Abstract—The linearity of high-resolution current-steering digital-to-analog converters (DACs) is often limited by inter-symbol interference (ISI). While dynamic element matching (DEM) can be applied to convert a portion of the ISI to uncorrelated noise instead of nonlinear distortion, DEM alone fails to prevent ISI from at least introducing strong second-order nonlinear distortion. This paper addresses this problem by proposing, analyzing, and experimentally demonstrating a low-cost add-on technique, called ISI scrambling, that, in conjunction with DEM, causes a DAC's ISI to be free of nonlinear distortion. The ISI scrambling technique is demonstrated in a 1-GS/s, 14-bit DEM DAC implemented in 90 nm CMOS technology. The DAC's measured linearity is in line with the state of the art and its measured output power spectra closely match those predicted by the paper's theoretical results.

Index Terms— DAC, ISI, DEM, current-steering, non-return-to-zero.

#### I. Introduction

INTER-SYMBOL interference (ISI) often limits the linearity of high-resolution current-steering digital-to-analog converters (DACs). It is caused by parasitic memory effects within the DAC's constituent 1-bit DACs, which cause each 1-bit DAC output waveform to depend not only on the 1-bit DAC's current input bit value but also on one or more of its prior input bit values.

Dynamic element matching (DEM) is often applied to multibit current-steering DACs to cause error from clock skew and component mismatches to be noise-like waveforms instead of nonlinear distortion [1-9]. It also causes some of the ISI to be a pseudo-random waveform, but even with DEM the ISI contains at least a strong second-order distortion component [10].

The most effective previously-published means of mitigating DAC ISI is to implement the constituent 1-bit DACs as return-to-zero (RZ) 1-bit DACs. RZ 1-bit DACs are reset to a signal-independent state at the end of each clock period. This mitigates ISI because it reduces the dependence of the 1-bit DACs on past input bit values. Unfortunately, the technique's efficacy degrades with clock frequency because of the reduced time available to discharge signal-dependent 1-bit DAC circuit nodes during the reset phase. RZ 1-bit DACs are also significantly more sensitive to clock jitter than their non-return-to-zero (NRZ) counterparts, particularly at high clock frequencies, and they typically consume more than twice the power of comparable NRZ 1-bit DACs.

Other previously published ISI-mitigation techniques measure and then suppress ISI by trimming the delays in the 1-bit

DAC switch drivers [11], canceling part of the ISI in either the digital or analog domain [10, 12-14], or dynamically reordering the 1-bit DACs to minimize the ISI [15-16]. The downsides of these techniques are that they require analog-to-digital converter (ADC) based ISI measurement circuitry, their accuracy is limited by that of the measurement circuitry, and they are foreground calibration techniques so they do not track changes in voltage or temperature.

All-digital ISI-mitigation techniques have also been published in which a modified DEM algorithm spectrally shapes the ISI [17-20]. These techniques are useful in oversampling continuous-time delta-sigma data converters. However, as proven in [10], it is not possible for any such technique to suppress nonlinear distortion across the full Nyquist band, so they are not well-suited to wideband applications that utilize the full Nyquist bandwidth of the DAC.

This paper presents a simple, low-cost, add-on technique called ISI scrambling that works in conjunction with DEM to address these problems. By pseudo-randomly scrambling each 1-bit DAC's transient error, the technique converts the ISI error component that would otherwise have been nonlinear distortion into a noise-like waveform that is free of nonlinear distortion. The paper presents a rigorous mathematical analysis of the technique, presents a 90 nm CMOS, 1-GS/s, 14-bit DEM DAC enabled by the technique that achieves linearity in line with the present state of the art, and shows that the measured results closely match the performance predicted by the mathematical analysis. Furthermore, the paper presents the first published experimental demonstration of a key theoretical result presented in [10] in that when the technique is disabled, the ISI nonlinearity manifests primarily as second-order distortion.

#### II. ISI SCRAMBLING TECHNIQUE

A conventional DEM DAC consists of a DEM encoder that drives multiple 1-bit DACs, the outputs of which are summed to form the DEM DAC's output [21]. The output of the  $i^{th}$  conventional 1-bit DAC is

$$y'_{i}(t) = (c'_{i}[n_{i}] - \frac{1}{2})K_{i}\Delta + e'_{i}(t),$$

(1)

where  $c'_i[n]$ , which takes on values of 0 and 1, is the 1-bit DAC's binary input sequence,  $K_i$  is the 1-bit DAC's weight,  $\Delta$  is the overall DEM DAC's minimum step-size,  $c'_i(t)$  represents the 1-bit DAC's error waveform,  $n_t = \lfloor f_s t \rfloor$  is the largest integer

This work was supported by the National Science Foundation under Award 1909678 and Microchip Technology Inc. Jason Remple and Andrea Panigada are with Zeku Inc., San Diego, CA, 92130, USA. Ian Galton is with the

Electrical and Computer Engineering Department of the University of California at San Diego, La Jolla, CA 92092-0407, USA.

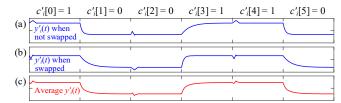

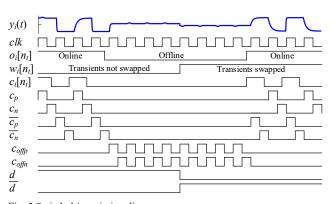

Fig. 1 Example 1-bit DAC outputs with the transient errors: (a) not swapped, (b) swapped, and (c) averaged.

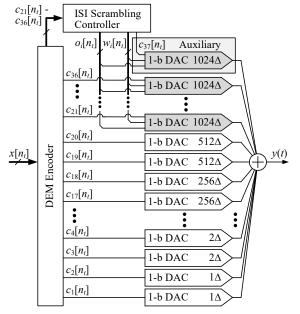

Fig. 2 ISI scrambling DEM DAC block diagram.

less than or equal to  $f_s t$ , and  $f_s$  is the 1-bit DAC's sample rate [10].<sup>†</sup>

The ISI scrambling technique is a supplement to DEM that converts what would otherwise have been nonlinear ISI error into pseudo-random noise. It incorporates 1-bit DACs that are modified to periodically swap the transient errors that cause nonlinear distortion in conventional 1-bit DACs. Each modified 1-bit DAC, called an ISI scrambling 1-bit DAC in the remainder of the paper, can be configured in real-time to be taken offline and to swap its transient errors.

The idea is to control each of the ISI-scrambling 1-bit DACs such that it spends an equal amount of time with its transient errors swapped and not swapped on average, which causes the average rise and fall transient errors to be symmetric. This is illustrated in Fig. 1. Fig. 1(a) shows an example 1-bit DAC output waveform, Fig. 1(b) shows the corresponding output waveform with its transient errors swapped, and Fig. 1(c) shows the average of the two cases.

Each ISI scrambling 1-bit DAC is taken offline when it transitions from swapping to not swapping its transients, or vice versa. This reduces the disturbance to the overall DAC output caused by inverting the swap state. When an ISI scrambling 1-bit DAC is offline, an auxiliary 1-bit DAC is used temporarily in its place.

A block diagram of the implemented ISI scrambling DEM

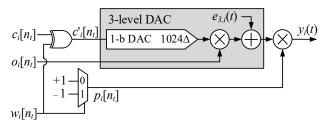

Fig. 3 ISI scrambling 1-bit DAC block diagram.

DAC is shown in Fig. 2. It consists of the digital DEM encoder presented in [4], a digital ISI scrambling controller, 20 conventional 1-bit DACs, and 17 ISI scrambling 1-bit DACs. The ISI scrambling 1-bit DACs are shaded in Fig. 2. The conventional 1-bit DACs have weights 1, 1, 2, 2, 4, 4, ..., 512, 512, and the ISI scrambling 1-bit DACs all have a weight of 1024. As proven in Section IV, only the 1024-weight 1-bit DACs contribute nonlinear ISI error to the overall DEM DAC output, so the other 1-bit DACs need not be ISI scrambling 1-bit DACs. The top 1024-weight ISI scrambling 1-bit DAC shown in Fig. 2 is the auxiliary 1-bit DAC. The remaining 1024-weight 1-bit DACs are called the *primary* ISI scrambling 1-bit DACs.

The ISI scrambling controller coordinates taking the primary ISI scrambling 1-bit DACs offline and inverting their swap states. It generates the  $o_i[n_t]$  and  $w_i[n_t]$  binary sequences that control the online state and the swap state, respectively, of each ISI scrambling 1-bit DAC.<sup>‡</sup> The ISI scrambling controller waits a random number of clock cycles between taking randomly-selected individual primary ISI scrambling 1-bit DACs offline. The number of wait cycles is chosen from 1 to  $N_{Delay}$  with equal probability where  $N_{Delay}$  is a register setting that ranges from 16 to 65536. The purposes of the random wait time are to prevent the ISI errors from being correlated with the input and to avoid introducing periodic disturbances to the overall DEM DAC output that could result in spurs. When selected by the ISI scrambling controller, each primary ISI scrambling 1-bit DAC is taken offline for 8 clock cycles and its swap state is inverted after being offline for 4 clock cycles. The auxiliary 1-bit DAC is offline when it is not taking the place of one of the primary ISI scrambling 1-bit DACs. When the auxiliary 1-bit DAC is offline, the ISI scrambling controller randomly inverts or does not invert its swap state with the objective of ensuring that its rise and fall transient errors are symmetric on average.

A behavioral block diagram of each ISI scrambling 1-bit DAC is shown in Fig. 3. It contains a conventional 1-bit DAC with additional components that implement the ISI-scrambling features. The components within the shaded box together behave as a 3-level DAC with ideal outputs  $-512\Delta$ , 0, and  $512\Delta$ , where the output level of 0 corresponds to the offline state  $(o_i[n_i] = 0)$ . The error,  $e_{3,i}(t)$ , represents the error of the 3-level DAC. It includes the error of the conventional 1-bit DAC as well as that of the  $o_i[n_i]$  multiplier.

The ISI scrambling controller swaps the ISI errors of the conventional 1-bit DAC by setting  $w_i[n_t] = 1$ , which causes two inversions in the signal path of  $c_i[n_t]$ . The first inversion is caused

<sup>&</sup>lt;sup>†</sup> The prime character is used in this paper to denote variables that pertain to conventional 1-bit DACs.

<sup>&</sup>lt;sup>‡</sup> A sequence indexed with  $n_t$  is technically a continuous-time function, but is referred to as a sequence because it remains constant over each sample period.

by the XOR gate and the second inversion is caused by the  $p_i[n_i]$  multiplier. In the ideal case where  $e_{3,i}(t) = 0$  and the multipliers are error-free,  $y_i(t)$  is an exact analog representation of  $c_i[n_t]$  when the 1-bit DAC is online  $(o_i[n_t] = 1)$ , because the input signal passes through the XOR gate and the multiplier unchanged if swapping is disabled  $(w_i[n_t] = 0)$ , and the two inversions in the signal path cancel each other out if swapping is enabled  $(w_i[n_t] = 1)$ . The error,  $e_{3,i}(t)$ , only passes through a single inversion when the transients are swapped which allows its polarity in  $y_i(t)$  to be controlled by the ISI scrambling controller.

#### III. CIRCUIT DETAILS

In conventional DEM DACs with NRZ 1-bit DACs, the nonlinear portion of the ISI error primarily consists of second-order and third-order distortion [10, 22]. However, to the extent that the output of each 1-bit DAC is negligibly affected by the states of the other 1-bit DACs, the ISI error consists of just secondorder distortion [10]. The ISI scrambling technique mitigates second-order distortion, so the circuit architecture was chosen to separately mitigate third-order distortion by minimizing the extent to which the 1-bit DACs influence each other as described below.

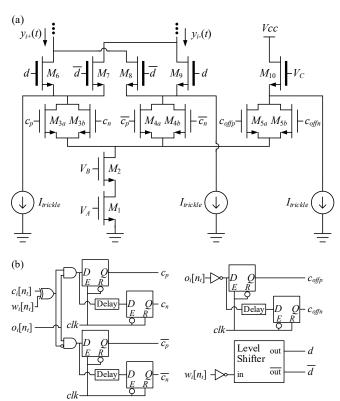

Figure 4 shows the current-steering cell and switch driver that comprise each 1-bit DAC. Transistor  $M_1$  sets the signal-bearing portion of the 1-bit DAC current, so its dimensions are large to facilitate good matching [23]. The dimensions of  $M_2$  are comparatively small to reduce the current source's parasitic output capacitance and thereby reduce ISI [24].

Transistors  $M_{k\,a}$  and  $M_{k\,b}$  for k=3, 4, and 5 steer the 1-bit DAC's signal-bearing current to one or the other of its two output terminals or divert it away from both output terminals depending on the states of  $c_i[n_t]$  and  $o_i[n_t]$  according to the timing diagram shown in Fig. 5. A quad switching technique is used wherein the transistors  $M_{k\,a}$  and  $M_{k\,b}$  for k=3, 4, or 5 each conduct the 1-bit DAC's signal-bearing current for half of each clock cycle [25-28]. This improves DAC linearity because, as implied by Fig. 5, exactly one switch turns on and exactly one switch turns off at each clock edge which causes the disturbance to the sources of  $M_{k\,a}$  and  $M_{k\,b}$  to be largely independent of the 1-bit DAC input [26]. The gate voltages of  $M_{k\,a}$  and  $M_{k\,b}$  are such that each transistor is in saturation when it conducts current, which increases the 1-bit DAC's output impedance.

Thick oxide transistors  $M_6$  through  $M_9$  implement the 1-bit DAC is online, i.e., when  $o_i[n_t] = 1$ , they swap or do not swap the connections between their sources and the two 1-bit DAC outputs depending on  $w_i[n_t]$ . Toggling  $w_i[n_t]$  while the 1-bit DAC is online would result in different transient errors than toggling  $c_i[n_t]$  and contribute significant distortion to the DAC output. Hence,  $w_i[n_t]$  is only toggled when the 1-bit DAC is offline. Toggling  $w_i[n_t]$  when the 1-bit DAC is offline still causes unwanted charge to be injected into the DAC's output terminals, but much of this charge is cancelled because rising and falling transitions of the gate voltages of  $M_6$  and  $M_9$  coincide with falling and rising transitions of the gate voltages of  $M_7$  and  $M_8$ , respectively. Furthermore, d and  $\overline{d}$  change state at random times so any error from charge injection is independent of the DAC's

Fig. 4 ISI scrambling 1-bit DAC implementation, (a) current-steering cell, (b) switch driver.

Fig. 5 Switch driver timing diagram.

input code and does not contribute harmonic distortion.

The level-shifter in Fig. 4(b) that drives the gates of  $M_6$ through  $M_9$  is powered by an on-chip LDO similar to that presented in [29], except that an external bypass capacitor is used instead of an internal Miller capacitor. The LDO output voltage is such that when d is high and  $\overline{d}$  is low,  $M_6$  and  $M_9$  are in saturation and  $M_7$  and  $M_8$  are off, and when d is low and  $\bar{d}$  is high,  $M_6$  and  $M_9$  are off and  $M_7$  and  $M_8$  are in saturation. Keeping  $M_6$ through  $M_9$  in saturation when conducting the 1-bit DAC's signal-bearing current increases the 1-bit DAC's output impedance, thereby reducing the dependence of its transient error on the overall DEM DAC's output [22, 30]. Hence, in addition to implementing the transient swapping feature,  $M_6$  through  $M_9$ perform the function of the cascode stages commonly used in conventional current-steering 1-bit DACs [7, 12-13, 15-16, 22, 27, 31]. As such, they improve overall DEM DAC linearity at the expense of a small reduction in headroom. The  $I_{trickle}$  current

sources shown in Fig. 4(a) prevent  $M_6$  through  $M_{10}$  from turning off when not conducting the 1-bit DAC's signal-bearing current, thereby reducing nonlinear distortion that would otherwise be caused by code-dependent output capacitance variations [31].

Two versions of the IC were fabricated that differ only in that each 1-bit DAC in the second version includes an extra cascode stage. The second version was fabricated to evaluate the effect of further increasing the 1-bit DAC output impedances. The measured performance of the two versions was found to be indistinguishable, which supports the assumption made in the analysis in Section IV that the error caused by finite 1-bit DAC output impedance is negligible, at least relative to the linearity achieved by the IC as reported in Section V. Hence, this paper presents the details of only the first version of the chip.

The main sources of transient errors that cause nonlinear ISI are the skews between the rising and falling edges of the gate voltages of  $M_{3a}$ ,  $M_{3b}$ ,  $M_{4a}$ , and  $M_{4b}$ , and mismatches among  $M_{3a}$ ,  $M_{3b}$ ,  $M_{4a}$ , and  $M_{4b}$ . The transient swapping feature implemented by  $M_6$  through  $M_9$  swaps these transient errors, but does not swap any additional transient error introduced by mismatches among  $M_6$  through  $M_9$ . However, the impedance looking into the sources of  $M_6$  through  $M_9$  is relatively low, so mismatches among  $M_6$  through  $M_9$  do not cause significant transient errors. Monte Carlo simulations support this assertion. With mismatches applied only to  $M_6$  through  $M_9$ , they predict a second harmonic of less than -97 dBc for a full-scale sinusoidal input sequence. In contrast, with mismatches applied to all transistors except  $M_6$  through  $M_9$ , ISI scrambling disabled, and the same full-scale input sequence, they predict a second harmonic of −72 dBc.

As explained in Section II each 1-bit DAC has a weight  $K_i$  = 1, 2, 4, 8, ..., or 1024. The overall DEM DAC's minimum-step size,  $\Delta$ , is 2.4  $\mu$ A, so the nominal signal-bearing current sourced by  $M_1$  and  $M_2$  in the  $K_i$  = 1 1-bit DAC is 1.2  $\mu$ A. The current-steering cells in the  $K_i$  = 2, 4, and 8 1-bit DACs were implemented by increasing the widths of  $M_1$  and  $M_2$  by factors of 2, 4, and 8, respectively, relative to those in the  $K_i$  = 1 1-bit DAC while keeping the dimensions of the other transistors unchanged. The current-steering cells of weights  $K_i$  = 16, 32, ..., and 256, were implemented by replicating each transistor in the  $K_i$  = 8 current-steering cell 2, 4, 8, ..., and 32 times, respectively, with the replicated transistors connected in parallel. The 1-bit DACs of weight 512 and 1024 were implemented as parallel copies of the  $K_i$  = 256 1-bit DAC.

In the current-steering cells of weight  $K_i = 1, 2, 4$ , and 8 in which  $M_6$  through  $M_{10}$  are each implemented with unit-weight transistors, the nominal value of  $I_{trickle}$  is 280 nA. In the current-steering cells of weights  $K_i = 16, 32, ...,$  and 256, in which  $M_6$  through  $M_{10}$  are each implemented by connecting  $2^{-3}K_i$  unit-weight transistors in parallel, the nominal value of  $I_{trickle}$  is 3% of the signal-bearing current.

Better matching could have been achieved by implementing each  $K_i$ -weight current-steering cell for  $K_i \ge 2$  by simply connecting  $K_i$  unit-weight current-steering cells in parallel. However, doing so would have significantly increased the required current-steering cell drive strength for  $K_i \ge 2$ , which would have

correspondingly increased the area and current consumption of the switch drivers.

In the absence of other considerations, the best switch driver scaling strategy to match the 1-bit DAC transients is to have the weight of each switch driver be proportional to the weight of the current-steering cell it drives. The switch driver latches are as described in [31], and in TSMC 90 nm technology a minimum-size latch has more drive strength than is required to drive a  $K_i = 1$  current-steering cell. Consequently, if the latches were scaled in proportion to the current-steering cells they would consume far more area and power than necessary. Instead, all current-steering cells are driven by copies of a switch driver that is optimized to drive a  $K_i = 256$  current-steering cell. Dummy transistors are used to load the switch drivers in each 1-bit DAC with a weight of  $K_i = 128$  and lower, so the loads driven by all the switch drivers are approximately equal to the load of a  $K_i = 256$  current-steering cell.

As proven in Section IV, ISI scrambling is not necessary in 1-bit DACs 1-20. Hence, the ISI scrambling feature is disabled in these 1-bit DACs by setting  $o_i[n_t]$  and  $w_i[n_t]$  to 1 and 0, respectively, for i = 1, 2, ..., 20 and all t. Alternatively, the ISI-scrambling circuitry could have been omitted from 1-bit DACs 1-20, but this would have degraded matching.

The clock input buffer is a two-stage differential to single-ended amplifier. The first stage is a differential pair with diode-connected load transistors, and the second stage is a differential pair with a current mirror load. The clock input buffer drives a clock tree that distributes the clock to the 1-bit DACs. The targeted total jitter of the clock input buffer and clock tree is 100 fs RMS, and was verified via simulation. The jitter target ensures that the jitter does not limit the noise performance of the DAC when DEM is enabled.

The placed and routed (P/R) digital block, clock input buffer, bias circuitry, and set of switch drivers are each powered by their own power domain to reduce coupling through the supplies. The power and ground are distributed via wide traces to reduce supply impedance, and extensive on-chip decoupling fills most of the unused area in the chip.

# IV. ANALYSIS

This section along with the appendices presents a mathematical derivation that quantifies the behavior of the ISI scrambling technique. It also develops theoretical DAC output PSD expressions that are compared against and closely match the corresponding measured power spectra in Section V. The section and appendices may be skipped without loss of continuity by those who are not interested in the mathematical details.

# A. ISI Scrambling 1-Bit DAC Output Model

In conventional current-steering DACs, particularly significant types of errors include mismatches among the 1-bit DACs, transient errors, ISI, and clock feedthrough. For most current-steering DACs, these errors are dominant and  $e'_i(t)$  in (1) is well-modeled as

$$e'_{i}(t) = \begin{cases} e_{11i}(t), & \text{if } c'_{i}[n_{t}-1] = 1, c'_{i}[n_{t}] = 1, \\ e_{01i}(t), & \text{if } c'_{i}[n_{t}-1] = 0, c'_{i}[n_{t}] = 1, \\ e_{00i}(t), & \text{if } c'_{i}[n_{t}-1] = 0, c'_{i}[n_{t}] = 0, \\ e_{10i}(t), & \text{if } c'_{i}[n_{t}-1] = 1, c'_{i}[n_{t}] = 0, \end{cases}$$

$$(2)$$

where  $e_{11i}(t)$ ,  $e_{00i}(t)$ ,  $e_{00i}(t)$ , and  $e_{10i}(t)$ , are  $T_s$ -periodic ( $T_s = 1/f_s$ ) waveforms that correspond to the errors made by the 1-bit DAC for the four possible combinations of the current and previous 1-bit DAC input bit values [10]. During each clock cycle,  $e'_i(t)$  is equal to one of the four  $T_s$ -periodic error waveforms. Formulating  $e'_i(t)$  in terms of these waveforms simplifies the subsequent analysis. It does not impose any restrictions on the 1-bit DAC input sequence, nor does it cause  $e'_i(t)$  to be periodic.

As shown in [10], an equivalent form of (1) is

$$y'_{i}(t) = x'_{i}[n_{t}]\alpha_{i}(t)K_{i}\Delta + \beta_{i}(t) + x'_{i}[n_{t}-1]\gamma_{i}(t) + x'_{i}[n_{t}]x'_{i}[n_{t}-1]\eta_{i}(t),$$

(3)

where

$$x'_{i}[n_{i}] = c'_{i}[n_{i}] - \frac{1}{2},$$

(4)

and  $\alpha_i(t)$ ,  $\beta_i(t)$ ,  $\gamma_i(t)$ , and  $\eta_i(t)$  are linear combinations of  $e_{11i}(t)$ ,  $e_{01i}(t)$ ,  $e_{00i}(t)$ , and  $e_{10i}(t)$  so they are  $T_s$ -periodic waveforms. The  $x'_i[n_t]x'_i[n_t-1]\eta_i(t)$  term in (3) is a second-order nonlinearly distorted version of the 1-bit DAC's input sequence and is caused by ISI. When the rise and fall transients of the 1-bit DAC output waveform are asymmetric, such as illustrated in Fig. 1(a),  $\eta_i(t)$  is nonzero which causes the 1-bit DAC to introduce second-order nonlinear ISI error. Without DEM, this would cause the overall DAC to introduce second-order and several higher-order nonlinear distortion terms, but, as shown in [10], DEM prevents all but second-order nonlinear distortion.

It follows from Fig. 3 that  $p_i^2[n_t] = 1$ ,

$$p_i[n_t] = 1 - 2w_i[n_t], \text{ and } c'_i[n_t] = \left(c_i[n_t] - \frac{1}{2}\right)p_i[n_t] + \frac{1}{2}, \quad (5)$$

so (1) and Fig. 3 imply that

$$y_i(t) = x_i [n_i] o_i [n_i] K_i \Delta + e_i(t)$$

, (6)

where

$$x_i[n_t] = c_i[n_t] - \frac{1}{2},$$

(7)

and  $e_i(t)$  represents all error from non-ideal behavior. To the extent that the  $p_i[n_t]$  multiplier is ideal, Fig. 3 implies that

$$e_{i}(t) = p_{i}[n_{i}]e_{3i}(t)$$

. (8)

Given that  $e_{3,i}(t)$  during the *n*th clock period depends on whether the ISI scrambling 1-bit DAC is offline or online during the *n*th and (n-1)th clock periods, it is convenient for the following analysis to define sequences that are 1 or 0 depending on the four combinations of offline and online statuses during the two clock periods. Specifically, these sequences are defined as

$$o_{++,i}[n_t] = o_i[n_t - 1]o_i[n_t],$$

(9)

$$o_{+\times i}[n_t] = o_i[n_t - 1](1 - o_i[n_t]),$$

(10)

$$o_{x+i}[n_t] = (1 - o_i[n_t - 1])o_i[n_t], \tag{11}$$

and

$$o_{xx,i}[n_t] = (1 - o_i[n_t - 1])(1 - o_i[n_t]), \tag{12}$$

which have the property that one of  $o_{++,i}[n_t]$ ,  $o_{+\times,i}[n_t]$ ,  $o_{\times+,i}[n_t]$ , and  $o_{\times\times,i}[n_t]$  is 1 and the rest are 0 during each clock cycle.

In the error formulation of the conventional 1-bit DAC, a specific  $T_s$ -periodic error waveform is defined for each combination of the 1-bit DAC's current and previous input bit values. This results in the  $2^2 = 4$   $T_s$ -periodic error waveforms used in (2) to formulate  $e'_i(t)$ . Applying similar reasoning to the 3-level DAC in the shaded box in Fig. 3 results in  $3^2 = 9$   $T_s$ -periodic error waveforms used to formulate

$$e_{3,i}(t) = o_{++,i}[n_t]e_i'(t)$$

$$+o_{+\times,i}[n_t][c_i'[n_t-1]e_{1\times i}(t) + (1-c_i'[n_t-1])e_{0\times i}(t)]$$

$$+o_{\times+,i}[n_t][c_i'[n_t]e_{\times 1i}(t) + (1-c_i'[n_t])e_{\times 0i}(t)]$$

$$+o_{\times\times,i}[n_t]e_{\times\times,i}(t),$$

(13)

where  $e_{1\times i}(t)$ ,  $e_{0\times i}(t)$ ,  $e_{\times i}(t)$ ,  $e_{\times 0i}(t)$ , and  $e_{\times \times i}(t)$  are 5 of the 9  $T_s$ -periodic error waveforms and the remaining 4  $T_s$ -periodic error waveforms are contained in the definition of  $e'_i(t)$ , which is given by (2).

Thus,  $e_i(t)$  is given by (8) with  $e_{3,i}(t)$  given by (13) provided the error introduced by the  $p_i[n_t]$  multiplier in Fig. 3 is negligible. Otherwise, it is necessary to define two error waveforms,  $e_{3,i}^+(t)$  and  $e_{3,i}^-(t)$ , that have forms similar to the right side of (13) except that their constituent  $T_s$ -periodic error waveforms correspond to the cases of  $p_i[n_t] = 1$  and  $p_i[n_t] = -1$  respectively. Then,  $e_i(t) = e_{3,i}^+(t)$  when  $p_i[n_t] = 1$  and  $e_i(t) = -e_{3,i}^-(t)$  when  $p_i[n_t] = -1$ . In this case ISI scrambling does not completely eliminate ISI-induced second-order nonlinear distortion because  $e_{3,i}^+(t) \neq e_{3,i}^-(t)$ . Yet as supported by the experimental results presented in Section V, the error introduced by the  $p_i[n_t]$  multiplier in Fig. 3 is indeed negligible. The reason is that the  $p_i[n_t]$  multiplier is implemented as a swapper cell as explained in Section III so it only introduces error when  $p_i[n_t]$  changes state and this only happens when the 1-bit DAC is offline.

## B. ISI Scrambling DEM DAC Output Model

Equations (6)-(13) were formulated to model ISI scrambling 1-bit DACs, but with  $o_i[n_t] = 1$  and  $w_i[n_t] = 0$  for all t they can also be used to model conventional 1-bit DACs. This is because a conventional 1-bit DAC is equivalent to an ISI scrambling 1-bit DAC that never goes offline and never has its transient errors swapped. Consequently, in the following analysis all the 1-bit DACs in Fig. 2 are modelled via (6)-(13) but with  $o_i[n_t] = 1$  and  $p_i[n_t] = 1$  for i = 1, 2, ..., 20 and for all t.

As proven in [4], the DEM encoder's outputs,  $c_i[n_t]$ , cause the  $x_i[n_t]$  sequences, which are given by (7) and take on values that are restricted to  $\frac{1}{2}$  and  $-\frac{1}{2}$ , to satisfy

$$x_i[n_t] = \frac{m_i x[n_t] + \lambda_i[n_t]}{\Lambda}, \qquad (14)$$

where

$$\sum_{i=1}^{36} K_i m_i = 1, \text{ and } \sum_{i=1}^{36} K_i \lambda_i [n_t] = 0.$$

(15)

Given that the ISI scrambling technique causes the auxiliary 1-bit DAC to sometimes take the place of one of the primary ISI scrambling 1-bit DACs, (15) implies

<sup>†</sup> The subscript characters + and × denote "online" and "offline" respectively.

$$\sum_{i=1}^{37} K_i m_i o_i[n_t] = 1 \quad \text{and} \quad \sum_{i=1}^{37} K_i \lambda_i[n_t] o_i[n_t] = 0.$$

(16)

At the circuit level, the summation operation in Fig. 2 is implemented by connecting the outputs of the current-steering 1-bit DACs. Under the assumption that the impedance of each 1-bit DAC is high enough that its output is negligibly affected by the states of the other 1-bit DACs, an assumption which is supported by the measured results presented in Section V, it follows that the output of the overall DAC is given by

$$y(t) = \sum_{i=1}^{37} y_i(t) . {17}$$

Substituting (6) with  $e_i(t) = 0$  and (14) into (17), and simplifying the result using (16) results in

$$y(t) = x[n_t], (18)$$

which represents the overall DEM DAC output in the absence of non-ideal behavior. In contrast, as shown in Appendix A, the 1-bit DAC errors cause the overall DAC output to degrade to

$$y(t) = \alpha(t)x[n_t] + \beta(t) + e_{DAC}(t),$$

(19)

where  $\alpha(t)$  and  $\beta(t)$  are  $T_s$ -periodic waveforms and  $e_{DAC}(t)$  represents the overall DAC's remaining non-ideal performance.

The first term on the right side of (19) is the desired signal component of the DAC output. As shown in [10], its continuous-time Fourier transform (CTFT) is

$$\mathfrak{I}_{CT}\left\{\alpha(t)x[n_t]\right\} = A_p(j\omega)X(e^{j\omega T_s}), \tag{20}$$

where  $A_p(j\omega)$  is the CTFT of

$$\alpha_p(t) = \begin{cases} \alpha(t) & \text{if } 0 \le t < T_s, \\ 0 & \text{otherwise,} \end{cases}$$

(21)

and  $X(e^{j\omega Ts})$  is the discrete-time Fourier transform (DTFT) of x[n]. Ideally,  $\alpha(t) = 1$  in which case the  $\alpha(t)x[n_t]$  term in (19) reduces to the right side of (18), and (20)-(21) imply that  $|A_p(j\omega)| = \sin(\pi T_s f)/\pi f$ . This corresponds to the classic zero-order-hold frequency response roll-off of an ideal DAC. In practice, 1-bit DAC errors cause  $\alpha(t)$  to deviate from unity, but, as implied by (20) and (21), this just affects the frequency response roll-off without introducing nonlinear distortion. Moreover, the effect on the frequency roll-off typically is not significant in current steering DACs [10].

The  $\beta(t)$  term in (19) introduces fixed tones in the DAC output at integer multiples of  $f_s$ . Such tones occur in all types of DACs, e.g., as a result of clock feedthrough. They do not fall within any Nyquist band of the DAC output and do not depend on the DAC input, so they do not cause problems in typical DAC applications [10].

In contrast, the  $e_{DAC}(t)$  term in (19) limits performance in typical applications. As proven in Appendix A it can be written as

$$e_{DAC}(t) = e_{MM}(t) + e_{ISI-linear}(t) + e_{ISI-noise}(t), \qquad (22)$$

where  $e_{MM}(t)$  is caused by mismatches among the 1-bit DACs and the remaining two terms are caused by ISI.

The expression for  $e_{MM}(t)$  is

$$e_{MM}(t) = \frac{1}{\Delta} \sum_{i=1}^{37} o_{++,i}[n_t] \lambda_i[n_t] \varepsilon_i(t) , \qquad (23)$$

where each  $\varepsilon_i(t)$  is a  $T_s$ -periodic waveform defined in Appendix A and DEM causes the  $\lambda_i[n_t]$  sequences to be zero-mean, pseudo-random sequences that are uncorrelated with the DAC's

input sequence,  $x[n_t]$ , i.e.

$$\begin{aligned}

& \mathbb{E}\left\{\lambda_{i}[n_{t}]\right\} = 0 \\

& \mathbb{E}\left\{\lambda_{i}[n_{t}]\lambda_{i}[m_{t}]\right\} = 0 \text{ for } m_{t} \neq n_{t}

\end{aligned} \text{ regardless of } x[n_{t}], \quad (24)$$

where  $E\{u\}$  denotes the expected value of u [4]. Without DEM the  $\lambda_i[n_t]$  sequences would be nonlinearly related to the DAC input, so  $e_{MM}(t)$  would contain nonlinear distortion. With DEM  $e_{MM}(t)$  is a zero-mean pseudo-random noise waveform because of the behavior of the  $\lambda_i[n_t]$  sequences [10].

The expression for  $e_{ISI-linear}(t)$  is

$$e_{ISI-linear}(t) = x[n_t - 1]\gamma(t), \qquad (25)$$

where  $\gamma(t)$  is a  $T_s$ -periodic waveform defined in Appendix A. The 1-bit DAC errors cause  $\gamma(t)$ , and hence  $e_{ISI-linear}(t)$ , to deviate from 0, but the argument applied above to show that the  $\alpha(t)x[n_t]$  term in (19) does not introduce nonlinear distortion also applies to  $e_{ISI-linear}(t)$ . While the 1-bit DAC errors cause  $\alpha(t)$  to deviate slightly from its ideal value of  $\alpha(t) = 1$ , they cause  $\gamma(t)$  to deviate slightly from its ideal value of  $\gamma(t) = 0$ , so in addition to not introducing nonlinear distortion,  $e_{ISI-linear}(t)$  typically has much lower power than  $\alpha(t)x[n_t]$ .

The expression for  $e_{ISI-noise}(t)$  is

$$e_{ISI-noise}(t) = e_{DEM}(t) + e_{IS}(t)$$

, (26)

where  $e_{DEM}(t)$  and  $e_{IS}(t)$  are error waveforms resulting from ISI that comprise noise instead of nonlinear distortion because of DEM and ISI scrambling, respectively. The expression for  $e_{DEM}(t)$  is

$$e_{DEM}(t) = \frac{1}{\Delta} \sum_{i=1}^{37} \lambda_{i} [n_{t} - 1] \Big[ o_{++,i} [n_{t}] \gamma_{i}(t) + z_{i} [n_{t}] \lambda_{i} [n_{t}] \Big]$$

$$+ \frac{1}{\Delta} \sum_{i=21}^{37} \Big( o_{+\times,i} [n_{t}] \gamma_{+\times,i}(t) \lambda_{i} [n_{t} - 1]$$

$$+ \Delta \cdot o_{\times+,i} [n_{t}] \varepsilon_{\times+,i}(t) \lambda_{i} [n_{t}]$$

$$+ 2^{-14} \cdot z_{i} [n_{t}] [x [n_{t} - 1] \lambda_{i} [n_{t}] + x [n_{t}] \lambda_{i} [n_{t} - 1] \Big),$$

(27)

where  $\varepsilon_{x+,i}(t)$  and  $\gamma_{+x,i}(t)$  are defined in Appendix A, and  $z_i[n_t] = o_{++,i}[n_t]p_i[n_t]\eta_i(t)/\Delta$ . Every term on the right side of (27) contains one or both of  $\lambda_i[n_t]$  and  $\lambda_i[n_t-1]$ , so, as in the case of  $e_{MM}(t)$ , DEM causes  $e_{DEM}(t)$  to comprise zero-mean pseudo-random noise instead of nonlinear distortion.

The expression for  $e_{IS}(t)$  is

$$e_{IS}(t) = \sum_{i=21}^{37} \left( e_{i}(t) + p_{i}[n_{t}] \left[ o_{++,i}[n_{t}] \beta_{i}(t) + o_{+\times,i}[n_{t}] \beta_{+\times,i}(t) \right] + o_{\times+,i}[n_{t}] \beta_{\times+,i}(t) + o_{\times\times,i}[n_{t}] e_{\times\times,i}(t) \right]$$

$$+ 2^{-14} x[n_{t}] \left[ \tilde{o}_{++,i}[n_{t}] \varepsilon_{i}(t) + \tilde{o}_{\times+,i}[n_{t}] \varepsilon_{\times+,i}(t) \right]$$

$$+ 2^{-14} \Delta^{-1} x[n_{t} - 1] \left[ \tilde{o}_{++,i}[n_{t}] \gamma_{i}(t) + \tilde{o}_{+\times,i}[n_{t}] \gamma_{+\times,i}(t) \right] \right),$$

(28)

where

$$e_i(t) = \frac{1}{2^{28} \Lambda^2} q_i[n_t] x[n_t] x[n_t - 1] \eta_i(t), \qquad (29)$$

$$q_i[n_t] = o_{++i}[n_t]p_i[n_t],$$

(30)

and the factors in (28) that are not defined above are defined in Appendix A. To show that  $e_{IS}(t)$  does not introduce nonlinear distortion, it is sufficient to show that

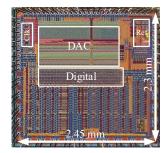

Fig. 6 Die photograph.

$$E\{e_{ts}(t)f(x[n_t],x[n_t-1],x[n_t-2],...)\}=0$$

(31)

holds for every deterministic nonlinear function of the DEM DAC's input sequence,  $f(x[n_t], x[n_t-1], x[n_t-2], ...)$ . Given that  $x[n_t]$  is deterministic, it follows from (31) that it is sufficient to show

$$E\{e_{ts}(t)\} = 0 \text{ regardless of } x[n_t] \text{ for all } t.$$

(32)

Every term on the right side of (28) contains either  $p_i[n_t]$ ,  $\tilde{o}_{++,i}[n_t]$ ,  $\tilde{o}_{++,i}[n_t]$ , or  $\tilde{o}_{\times+,i}[n_t]$ , all of which, by definition, are zero-mean random sequences that are independent of  $x[n_t]$  for all t. In addition,  $p_i[n_t]$  is independent of the other stochastic sequences in (28), and so it follows from (28) that (32) holds.

If ISI scrambling were not enabled,  $p_i[n_t] = 1$  and  $o_{++,i}[n_t] = 1$  for all t, which would cause the  $e_i(t)$  terms in (28) to contribute second-order nonlinear distortion. In contrast, the other terms in (28) as well as those in (23) and (27) either have zero means regardless of  $x[n_t]$  or have no dependence on  $x[n_t]$ , so they do not contribute nonlinear distortion in either the absence or presence of ISI scrambling.

As shown in [4],  $m_i = 0$  for i = 1, 2, ..., 20, so (14) and (7) imply that the  $c_i[n_t]$  outputs of the DEM encoder for these values of i do not contain components proportional to  $x[n_t]$ . This is why the summation in (28) starts from i = 21, and why the bottom 20 1-bit DACs in Fig. 2 need not be ISI scrambling 1-bit DACs.

To show that  $e_{IS}(t)$  does not introduce spurious tones, it is sufficient to show that

$$\lim_{\tau \to \infty} \mathbb{E}\left\{e_{IS}(t)e_{IS}(t+\tau)\right\} = 0 \quad \text{regardless of } x[n_t] \text{ for all } t. (33)$$

By definition,  $x[n_t]$  is deterministic, and, for sufficiently large  $\tau$  and any i and j,  $o_i[n_t]$ ,  $o_j[n_{t+\tau}]$ ,  $p_i[n_t]$ , and  $p_j[n_{t+\tau}]$  are independent, and  $p_i[n_t]$  and  $p_j[n_{t+\tau}]$  are zero mean. As explained in Appendix A,  $\tilde{o}_{**,i}[n]$  is the zero-mean portion of  $o_{**,i}[n]$  where \*\* is a place-holder for \*+, \*+, \*+, \*+, \* or \*- Therefore, (9)-(12) imply that  $\tilde{o}_{ab,i}[n_t]$ ,  $\tilde{o}_{cd,j}[n_{t+\tau}]$ ,  $p_i[n_t]$ , and  $p_j[n_{t+\tau}]$  are independent for sufficiently large  $\tau$  and any i and j, where a, b, c, and d are any combination of + and  $\times$ . Expanding  $\mathbb{E}\{e_{IS}(t)e_{IS}(t+\tau)\}$  using (28) and applying the above observations, verifies that (33) holds.

# C. Effect of ISI Scrambling for Sinusoidal Inputs

As explained above, the  $e_i(t)$  terms in (28) would contribute nonlinear distortion if it were not for ISI scrambling, so the properties of these terms are of particular interest. The power spectral density (PSD) of  $e_i(t)$  is derived in Appendices B and C for a full-scale input signal,  $x[n_t] = 8192\Delta \sin(2\pi n_t f_0/f_s)$ , where  $f_0/f_s$  satisfies

$$0 < f_0/f_s < \frac{1}{2}$$

and  $f_0/f_s \neq \frac{1}{4}$ , (34)

to avoid the degenerate cases of either the fundamental or the second harmonic of the input signal aliasing to zero frequency in  $x[n_t]$ .

The derivation involves two key components. Appendix B proves that the  $q_i[n_t]$  factor of  $e_i(t)$  with  $n_t$  replaced by n is a wide-sense stationary (WSS) discrete-time random process, and derives an expression for its autocorrelation,  $R_{q,i}[k]$ . Appendix C applies this result to show that  $e_i(t)$  is a cyclo-stationary continuous-time random process, and derives expressions for its time-average autocorrelation,  $\overline{R}_{e,i}(\tau)$ , and PSD,  $S_{e,i}(j\omega)$ .

Given that each  $e_i(t)$  term in (28) is proportional to  $p_j[n_i]$  if and only if j = i, and, by definition,  $p_i[n]$  is independent of  $p_j[n]$  when  $i \neq j$ , it follows that  $e_i(t)$  and  $e_j(t)$  are independent when  $i \neq j$ . Consequently, the PSD of the portion of  $e_{DAC}(t)$  that would be nonlinear distortion if ISI scrambling were not applied is

$$S_{e_{IS}}(j\omega) = \sum_{i=21}^{37} S_{e,i}(j\omega). \tag{35}$$

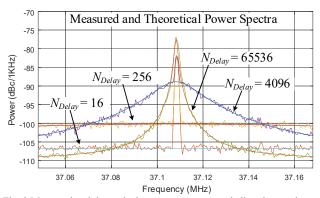

Theoretical curves calculated from (35) and its supporting equations in Appendices B and C are shown in Section V to closely match measurement results. The theoretical results prove and the measured results demonstrate that the ISI scrambling technique converts what would otherwise be ISI-induced second-order harmonic distortion spurs to noise "bumps" centered at the spur frequencies, e.g., at frequencies of 0 and  $2f_0$  Hz in the DAC's first Nyquist band. The peak amplitudes of the noise bump PSDs decrease as the average ISI scrambling 1-bit DAC transient swapping rate is increased. Hence, they decrease as  $N_{Delay}$  is decreased.

#### V. MEASUREMENT RESULTS

The IC was implemented in a TSMC 90 nm process. A die photograph of it is shown in Fig. 6. The die measures 2.3 mm × 2.45 mm and its active area is 1.48 mm<sup>2</sup>. The incremental circuit area required to implement ISI scrambling is 0.08 mm<sup>2</sup> of which 0.03 mm<sup>2</sup> corresponds to digital logic. The IC was tested in a QFN64 package and all grounds were down-bonded to the package's ground paddle. In addition to the DAC core, the IC contains LVDS interface circuitry interspersed throughout the pad ring and a direct digital synthesizer (DDS) integrated in the P/R digital block. The DDS was used for all measurements presented in this section.

The packaged IC was mounted to a test circuit board with an Ironwood elastomer socket. The clock signal applied to the test circuit board was generated by passing the single-ended output of a low-jitter laboratory signal generator through a passive bandpass filter to suppress noise and spurious tones. A balun and associated passive matching circuitry on the test circuit board converts the clock signal to differential form prior to the IC. A transformer and associated passive matching circuitry on the test circuit board converts the differential DAC output to a single-ended signal that was measured via a laboratory signal analyzer to obtain the results presented in this section.

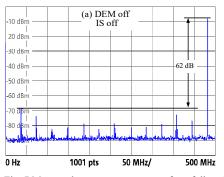

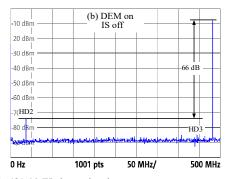

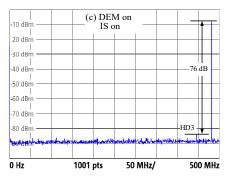

Fig. 7 shows representative DAC output power spectra for a 481.4 MHz single-tone input sequence. Compared to the case with both DEM and ISI scrambling disabled, the results indicate

Fig. 7 Measured output power spectra for a full-scale 481.4 MHz input signal.

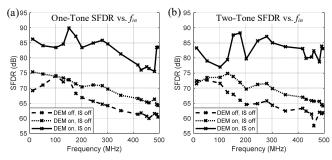

Fig. 8 Measured SFDR vs. frequency (a) one-tone input signals, and (b) two-tones input signals separated by 3.52 MHz.

that enabling just DEM improves the spurious-free dynamic range (SFDR) by only 4 dB whereas enabling both DEM and ISI scrambling improves the SFDR by 14 dB. With DEM enabled and ISI scrambling disabled, the measured SFDR is limited by an aliased second harmonic caused by ISI as predicted by the corresponding theoretical result presented in [10]. As predicted by the theoretical results presented in this paper, the measured second harmonic is highly attenuated when both DEM and ISI scrambling are enabled.

Similar results also hold for other input signals. Fig. 8 shows measured SFDR values versus signal frequency for single-tone and two-tone DAC input sequences. The data demonstrate that ISI scrambling significantly increases the measured SFDR values relative to the cases where ISI scrambling is disabled.

Fig. 9 shows several measured and theoretically calculated power spectra corresponding to a 481.4 MHz single-tone DAC input sequence with DEM and ISI scrambling enabled. To demonstrate the correspondence between theory and measurement, the power spectra are shown over a zoomed-in frequency band centered on the frequency at which the limiting aliased second harmonic occurs in the absence of ISI scrambling. A pair of power spectra, one measured and one calculated, are superimposed for each of  $N_{Delay} = 16$ , 256, 4096, and 65536. The calculated power spectra were obtained via the equations derived in Section IV and the appendices with a noise floor added to match that of the measured power spectra,  $\alpha(t)$  approximated as unity (its ideal value), and each  $\eta_i(t)$  approximated as a constant taken to be that which yielded the best overall match between the calculated and measured power spectra.

As predicted by the analysis in Section IV and demonstrated in Fig. 9, ISI scrambling converts what would otherwise be second-order nonlinear distortion into a spectral noise "bump" and the height of the bump decreases with  $N_{Delay}$ . Except for a -82

Fig. 9 Measured and theoretical power spectra around aliased second harmonic for full-scale 481.4 MHz single-tone input signal.

Fig. 10 Measured second harmonic versus frequency for a full-scale single-tone input signal.

dBc residual second-order spur in the measured results, the measured and corresponding calculated power spectra shown in Fig. 9, are in very close agreement.

The authors believe that the residual second-order spur is the result of differential path mismatches from transistors  $M_6$  through  $M_9$  in Fig. 4(a) through the test circuit board's output network up to the transformer. Evidence in support of this belief is that the residual spur was not predicted by simulations in the absence of such mismatches, and it was found to vary somewhat across different copies of the IC and test circuit board.

With DEM and ISI scrambling enabled, the DAC's SFDR for input frequencies above 300 MHz is limited by higher third-order distortion than was predicted by simulations prior to IC fabrication. The authors subsequently realized they had made a mistake in the simulation setup which caused the impedance of the ground bond wires to be underestimated. The measured third-order distortion was reproduced in simulation when the mistake was corrected. Nearly identical third order distortion was observed in simulation when ISI scrambling was disabled and  $M_7$  and  $M_8$  in Fig. 4(a) were removed, which shows that ISI scrambling is not the cause of the third-order distortion. If the

TABLE I NSD/SNDR MEASURED OVER FIRST NYQUIST BAND

|          | N:      | SD (dBc/H | z)     | SNDR (dB) |        |        |  |

|----------|---------|-----------|--------|-----------|--------|--------|--|

| $f_{in}$ | DEM off | DEM on    | DEM on | DEM off   | DEM on | DEM on |  |

| (MHz)    | IS off  | IS off    | IS on  | IS off    | IS off | IS on  |  |

| 51       | -163.4  | -147.1    | -146.3 | 63.6      | 59.9   | 59.4   |  |

| 180      | -158.1  | -145.8    | -145.2 | 62.4      | 58.6   | 58.3   |  |

| 481      | -150.8  | -144.8    | -144.8 | 60.3      | 57.8   | 57.8   |  |

TABLE II

KEY SPECIFICATIONS OF RECENT STATE-OF-THE-ART DACS

|              | Process (nm) | Resolution (bits) | Sample<br>Rate<br>(GHz) | Full<br>Scale<br>(mA) | Power<br>(mW) | Technique  |

|--------------|--------------|-------------------|-------------------------|-----------------------|---------------|------------|

| This<br>Work | 90           | 14                | 1000                    | 20                    | 238*          | DEM / IS   |

| [5]          | 40           | 16                | 1600                    | 16/20                 | 40            | DEMDRZ     |

| [7]          | 16           | 16                | 6000                    | 40                    | 350           | Static Cal |

| [8]          | 22           | 14                | 600                     | 16                    | 202           | MNC        |

| [9]          | 28           | 14                | 10000                   | 16                    | 162           | OIC        |

| [13]         | 65           | 16                | 9000                    | 16                    | 1080          | DPD        |

| [15]         | 140          | 14                | 200                     | 20                    | 270           | DMM        |

| [16]         | 65           | 16                | 3200                    | 20                    | 240           | 3DSC       |

| [30]         | 90           | 12                | 1250                    | 16                    | 128           | DRRZ       |

\*1.2 mW is due to ISI scrambling

problem caused by the DAC ground impedance were fixed, simulations suggest that the third-order distortion would be limited by the 1-bit DAC output impedance [22, 30-32].

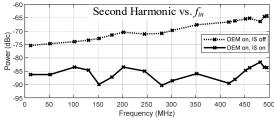

Fig. 10 shows the effect of ISI scrambling on the second-harmonic for full-scale single tone input sequences. With DEM enabled and ISI scrambling disabled, the ratio of the power of the desired signal component to the power of the second-harmonic decreases with input frequency. In contrast, with both DEM and ISI scrambling enabled, the ratio of the two components does not increase with frequency.

These observations are predicted by the analysis presented in Section IV. The CTFT of the DAC's desired signal component given by (20) is proportional to  $A_p(j\omega)$ , which is the CTFT of the  $T_s$ -duration pulse,  $\alpha_p(t)$ , equal to one period of  $\alpha(t)$ . The second-order distortion caused by ISI is represented by the  $e_i(t)$ terms in (28). By the same reasoning that led to (20), the CTFT of  $e_i(t)$  is proportional to  $H_{p,i}(j\omega)$ , which is the CTFT of a  $T_s$ duration pulse,  $\eta_{p,i}(t)$ , equal to one period of  $\eta_i(t)$ . While  $\alpha_p(t)$  is approximately constant for most of  $0 \le t < T_s$ ,  $\eta_{p,i}(t)$  is the result of 1-bit DAC transient errors so it is non-zero mainly over a short interval close to t = 0. Consequently,  $|H_{p,i}(j\omega)|$  decreases less over the first Nyquist band than  $|A_p(j\omega)|$  such that the second-order distortion exhibits less frequency roll-off than the desired signal component. In contrast, the residual second-order distortion term that remains when ISI-scrambling is enabled is not caused by ISI, so it does not appear in  $e_i(t)$  and is not subject to this effect.

Five randomly-selected copies of the IC were tested. For full-scale single-tone input sequences with frequencies spanning the Nyquist band, the worst measured second harmonic of the five copies is –64 dBc with DEM enabled and ISI scrambling disabled and –78 dBc with both DEM and ISI scrambling enabled. The power spectra and SFDR measurements presented in this section are from the IC copy with the worst second-order distortion when ISI scrambling is disabled.

The full-scale single-tone noise performance of the IC is shown in Table I. Enabling DEM reduces the SNDR by about

Fig. 11 SFDR comparison of recent state-of-the-art DACs.

3 dB, which is expected; DEM increases the number of 1-bit DAC transitions and causes the 1-bit DAC rise and fall transition mismatches to increase the overall DEM DAC's output noise. The same degradation in SNDR was observed in simulation when DEM was enabled. In contrast, the RZ 1-bit DACs used in [4, 8] have the same number of output transitions regardless of whether DEM is enabled, so enabling DEM does not degrade the SNDR for full-scale input signals in those cases. Enabling ISI scrambling in addition to DEM reduces the SNDR by up to 0.5 dB, which shows that the noise caused by DEM dominates the noise floor. As expected, the noise performance of the IC is worse than those of DACs that incorporate 1-bit DAC mismatch error calibration [7-8, 13, 15-16, 34]. However, the ISI scrambling technique's low circuit area and power consumption makes it inexpensive to combine with previously published techniques that calibrate 1-bit DAC mismatch errors.

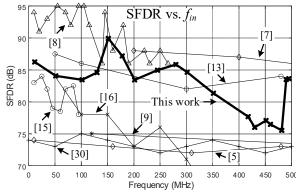

Table II and Fig. 11 present key specifications of the IC along with those of several other published state-of-the-art DACs. The P/R digital block includes the DEM encoder, ISI scrambling controller and DDS, and consumes 105 mW from a 1.2 V supply. The analog circuitry consumes the remaining 133 mW from 1.2 V and 3.3 V supplies (the DAC output current is sourced from the 3.3 V supply). The data show that the IC exhibits better SFDR performance than all but the DACs presented in [7], [8], and [13]. The DAC presented in [13] achieves high linearity, but it requires manual laboratory measurements to iteratively configure its foreground calibration technique which limits its applicability. The DAC presented in [8] uses RZ 1-bit DACs to avoid being limited by nonlinear ISI (measurements show that its SFDR drops by 10 dB when its 1-bit DACs are operated in NRZ mode). Had the DAC presented in [8] been augmented with ISI scrambling, it is likely that it could have used NRZ 1-bit DACs and thereby avoided the downsides of RZ 1-bit DACs without sacrificing linearity. The DAC presented in [7] uses NRZ 1-bit DACs and no ISI-mitigation techniques are mentioned in [7]. This suggests that excellent design and layout practices as well as the advanced 16 nm CMOS IC technology in which it is implemented are likely responsible for keeping its nonlinear ISI in check. Yet the analysis in Section IV shows that its NRZ 1-bit DACs must be introducing significant nonlinear ISI, so it is reasonable to expect that it too could have benefited from ISI scrambling.

#### VI. APPENDIX A

Substituting (7) into the right-most equation in (5) and substituting the result into (13) yields

$$e_{3,i}(t) = o_{++,i}[n_t]e_i'(t)$$

$$+o_{+\times,i}[n_t][\beta_{+\times,i}(t) + x_i[n_t - 1]p_i[n_t - 1]\gamma_{+\times,i}(t)]$$

$$+o_{\times+,i}[n_t][\beta_{\times+,i}(t) + x_i[n_t]p_i[n_t]\mathcal{E}_{\times+,i}(t)\Delta]$$

$$+o_{\times\times,i}[n_t]e_{\times\times,i}(t),$$

(36)

where

$$\beta_{+\times,i}(t) = \frac{1}{2} \left[ e_{1\times i}(t) + e_{0\times i}(t) \right], \quad \beta_{\times+,i}(t) = \frac{1}{2} \left[ e_{\times 1i}(t) + e_{\times 0i}(t) \right], \quad (37)$$

$$\gamma_{+\times,i}(t) = e_{1\times i}(t) - e_{0\times i}(t)$$

, and  $\varepsilon_{\times+,i}(t) = \frac{1}{\Lambda} [e_{\times 1i}(t) - e_{\times 0i}(t)]$ . (38)

As explained in Section II,  $p_i[n_t]$  only changes when the ISI scrambling 1-bit DAC has been offline for multiple clock cycles. This implies that  $p_i[n_t] = p_i[n_t-1]$  whenever  $o_{\times\times,i}[n] = 0$ . In such cases, both  $p_i[n_t]p_i[n_t-1] = 1$  and  $p_i^2[n_t] = 1$ , because  $p_i[n_t]$  takes on values of only 1 and -1. Consequently, (36) implies

$$p_i[n_t]e_{3,i}(t) = o_{++,i}[n_t]p_i[n_t]e'_i(t)$$

$$+o_{+\times,i}[n_t] \Big[ p_i[n_t] \beta_{+\times,i}(t) + x_i[n_t-1] \gamma_{+\times,i}(t) \Big]$$

$$+o_{\times+,i}[n_t] \Big[ p_i[n_t] \beta_{\times+,i}(t) + x_i[n_t] \varepsilon_{\times+,i}(t) \Delta \Big]$$

$$(39)$$

$$+o_{\times\times,i}[n_t]p_i[n_t]e_{\times\times i}(t).$$

As explained in Section IV-A,  $o_{+\times,i}[n_t] = o_{\times+,i}[n_t] = o_{\times\times,i}[n_t] = 0$  when  $o_{++,i}[n_t] = 1$ . Thus, (6), (8), and (39) imply that the output of the *i*th ISI scrambling 1-bit DAC is

$$y_i(t) = x_i[n_t]K_i\Delta + p_i[n_t]e_i'(t),$$

(40)

when  $o_{++,i}[n_t] = 1$ . Performing an analysis nearly identical to that applied in [10] to derive (3) from (1) and (2), and applying  $p_i[n_t]p_i[n_t-1] = 1$  and  $p_i^2[n_t] = 1$  results in

$$y_i(t) = x_i[n_i]\alpha_i(t)K_i\Delta + e_{++i}(t),$$

(41)

when  $o_{++,i}[n_t] = 1$ , where

$$e_{++,i}(t) = p_i[n_t]\beta_i(t) + x_i[n_t - 1]\gamma_i(t) + p_i[n_t]x_i[n_t]x_i[n_t - 1]\eta_i(t).$$

(42)

Given that one of  $o_{++,i}[n_t]$ ,  $o_{+\times,i}[n_t]$ ,  $o_{\times+,i}[n_t]$ , and  $o_{\times\times,i}[n_t]$  is 1 and the rest are 0 during each clock cycle and  $o_i[n_t] = 1$  when  $o_{++,i}[n_t] = 1$ , it follows from (6), (8), (39), and (41) that

$$y_{i}(t) = x_{i}[n_{t}]o_{i}[n_{t}]K_{i}\Delta$$

$$+o_{++,i}[n_{t}]\left[x_{i}[n_{t}]\varepsilon_{i}(t)\Delta + e_{++,i}(t)\right]$$

$$+o_{+\times,i}[n_{t}]\left[p_{i}[n_{t}]\beta_{+\times,i}(t) + x_{i}[n_{t}-1]\gamma_{+\times,i}(t)\right]$$

$$+o_{\times+,i}[n_{t}]\left[p_{i}[n_{t}]\beta_{\times+,i}(t) + x_{i}[n_{t}]\varepsilon_{\times+,i}(t)\Delta\right]$$

$$+o_{\times\times,i}[n_{t}]p_{i}[n_{t}]e_{\times\times}(t),$$

(43)

where

$$\varepsilon_i(t) = K_i(\alpha_i(t) - 1). \tag{44}$$

The random sequences  $o_{++,i}[n_t]$ ,  $o_{+\times,i}[n_t]$ ,  $o_{\times+,i}[n_t]$ , and  $o_{\times\times,i}[n_t]$  can each be written as

$$o_{**,i}[n] = \tilde{o}_{**,i}[n] + \overline{o}_{**,i}, \qquad (45)$$

Fig. 12 Markov state transition diagram corresponding to the primary ISI scrambling 1-bit DACs.

where \*\* is a placeholder for ++, +×, ×+, or ××,  $\tilde{o}_{**,i}[n]$  is the zero-mean portion of  $o_{**,i}[n]$ , and  $\overline{o}_{**,i}$  is the mean of  $o_{**,i}[n]$ .

The DEM encoder causes  $m_i = 0$  for  $1 \le i \le 20$  and  $m_i = 2^{-14}$  for  $21 \le i \le 36$  [4]. Therefore, substituting (43) with (45) and (14) into (17), simplifying the result with (16), and applying  $o_i[n_i] = 1$  for all i = 1, 2, ..., 20 results in (19), (22), (23), and (25)-(28), where

$$\alpha(t) = 1 + 2^{-14} \sum_{i=21}^{37} \left( \overline{o}_{++,i} \varepsilon_i(t) + \overline{o}_{\times+,i} \varepsilon_{\times+,i}(t) \right), \tag{46}$$

$$\beta(t) = \sum_{i=1}^{20} \beta_i(t), \tag{47}$$

and

$$\gamma(t) = \frac{2^{-14}}{\Delta} \sum_{i=21}^{37} \left( \overline{o}_{++,i} \gamma_i(t) + \overline{o}_{+\times,i} \gamma_{+\times,i}(t) \right). \tag{48}$$

## VII. APPENDIX B

The autocorrelation of  $q_i[n]$  for i = 21, 22, ..., 37 is derived in this appendix using a Markov chain to model the states of each ISI-scrambling 1-bit DAC. An analysis is first presented that applies to the primary 1-bit DACs, i.e., to  $q_i[n]$  for i = 21, 22, ..., 36. Then an analysis is presented that applies to the auxiliary 1-bit DAC, i.e., to  $q_i[n]$  for i = 37.

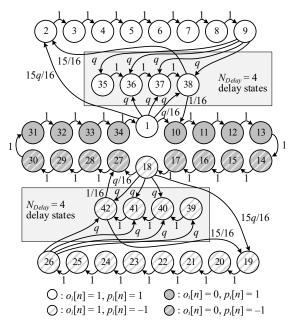

Fig. 12 shows a Markov chain state diagram that applies to the *i*th ISI-scrambling 1-bit DAC for the example case of  $N_{Delay}$  = 4, where i = 21, 22, ..., 36. The example uses  $N_{Delay} = 4$  to simplify the figure and its explanation, but the results derived below apply to the general case.

Each of the states in Fig. 12 with a single output state transition probability of 1 implements a one clock delay wait period. For example, States 10-17 implement the 8 clock delays during which the *i*th 1-bit DAC is offline and its transients are changed from not swapped to swapped.

The hashmarks in Fig. 12 denote states in which the *i*th 1-bit DAC's transients are swapped. For example, the 1-bit DAC's

transients are swapped in the second half of States 10-17 as indicated by the hashmarks on the symbols for States 14-17.

As explained in Section II, whenever a primary ISIscrambling 1-bit DAC goes from its offline to online state, all of the primary ISI-scrambling 1-bit DACs remain online for X clock periods where X is a random variable that takes on integer values from 1 to  $N_{Delay}$ , each with probability  $q = 1/N_{Delay}$ . Hence, if the *i*th 1-bit DAC is in State 1 at time index n, then the probability that one of the primary ISI-scrambling 1-bit DACs will be taken offline at time index n+1 is q. As there are 16 such 1-bit DACs, the probability that the *i*th 1-bit DAC will be taken offline at time index n+1 is q/16, and the probability that one of the other 1-bit DACs will be taken offline at time index n+1 is 15q/16. These two cases correspond States 10 and 2, respectively, in Fig. 12. If none of the primary 1-bit DACs are taken offline for another 1, 2, or 3 clock cycles, then the ith 1-bit DAC enters State 38, 37, or 36, respectively. Similar reasoning can be applied to each of the subsequent states to verify that the Markov chain correctly models the states of each primary ISI-scrambling 1-bit DAC per the explanation in Section

The number of Markov chain states,  $N_{States}$ , depends on  $N_{Delay}$ , which can be set via the SPI and can be as large as 65536. The example described above uses  $N_{Delay} = 4$  which resulted in  $N_{States} = 42$ . In general,  $N_{States} = 34+2N_{Delay}$  because the consecutive clock periods during which none of the primary 1-bit DACs are offline are represented by  $2N_{Delay}+2$  possible states. Specifically, these states are States 1, 18, C-D, and E-F, where

$$C = 35,$$

$D = 35 + N_{Delay} - 1,$

$E = 35 + N_{Delay},$   $F = 35 + 2N_{Delay} - 1.$  (49)

It follows from (9), (30), and the Markov chain's definition that

$$q_{i}[n] = \begin{cases} 1, & \text{if } s_{i}[n] \in S_{1}, \\ -1, & \text{if } s_{i}[n] \in S_{-1}, \\ 0, & \text{otherwise,} \end{cases}$$

(50)

where  $s_i[n]$  is the state of the Markov chain during the *n*th clock cycle,  $S_1 = \{2, 3, ..., 9, C, C+1, ..., D\}$ , and  $S_{-1} = \{19, 20, ..., 26, E, E+1, ..., F\}$ . Therefore,

$$E\{q_{i}[n]q_{i}[n+k]\} = \sum_{u \in S_{1}} \sum_{v \in S_{1}} \Pr(s_{i}[n] = u, s_{i}[n+k] = v)$$

$$+ \sum_{u \in S_{-1}} \sum_{v \in S_{-1}} \Pr(s_{i}[n] = u, s_{i}[n+k] = v)$$

$$- \sum_{u \in S_{1}} \sum_{v \in S_{-1}} \Pr(s_{i}[n] = u, s_{i}[n+k] = v)$$

$$- \sum_{u \in S_{-1}} \sum_{v \in S_{-1}} \Pr(s_{i}[n] = u, s_{i}[n+k] = v),$$

(51)

where  $Pr(s_i[n] = u, s_i[n+k] = v)$  is the joint probability that the Markov chain states at time indices n and n+k are u and v, respectively.

The values of  $Pr(s_i[n] = u, s_i[n+k] = v)$  can be derived via the Markov chain's  $N_{States} \times N_{States}$  state transition matrix,  $P = [p_{u,v}]$ , where  $p_{u,v}$  is the element on the *u*th row and *v*th column of P and is the probability that the Markov chain will be in State v at any time index m given that it was in State u at time index m-1. Although P has a relatively large dimension, most of its elements are zero. Specifically, the Markov chain's definition implies that the only non-zero elements of P are:

$$\begin{aligned} p_{34,1} &= p_{m, m+1} = 1 \text{ for all } m \notin \{1, 9, 18, 26, 34, D, E\}, \\ p_{1,2} &= p_{18,19} = 15q/16, \ p_{1,10} = p_{18,27} = q/16, \\ p_{D,2} &= p_{F,19} = 15/16, \ p_{D,10} = p_{F,27} = 1/16, \\ p_{9,C+m} &= p_{26,E+m} = q, \text{ for } 0 \le m < N_{Delay}, \\ p_{1,C+m} &= p_{18,E+m} = q, \text{ for } 1 \le m < N_{Delay}. \end{aligned}$$

(52)

The Markov chain's definition further implies that there is a non-zero probability of the system successively entering States 1-9, C-D, 10-26, E-F, 27-34, 1, which is a loop that includes all  $N_{States}$  states. This implies that every state can be reached from every other state, so the Markov chain satisfies the definition of being *irreducible*.

By the same reasoning, regardless of the system's state at any given time index n, there is a non-zero probability that it will return to the same state at time index n+m, where  $m=N_{States}$ . The Markov chain's definition also implies that there is a non-zero probability of the system successively entering the states in the order listed above but skipping either State C or State E. This implies that regardless of the system's state at any given time index n, there is a non-zero probability that it will return to the same state at time index n+m, where  $m=N_{States}-1$ . Given that the greatest common divisor of  $N_{States}$  and  $N_{States}-1$  is 1 regardless of the value to which  $N_{States}$  is set, this implies that the Markov chain satisfies the definition of being aperiodic.

As the Markov chain is irreducible, aperiodic, and has a finite number of states, it approaches a steady state in that the sequence of its states' probability distributions as a function of time index n converges to a unique steady-state probability distribution as  $n \to \infty$  [33]. This implies that

$$\begin{bmatrix} \pi_1 & \pi_2 & \cdots & \pi_{N_{States}} \end{bmatrix} = \begin{bmatrix} \pi_1 & \pi_2 & \cdots & \pi_{N_{States}} \end{bmatrix} \mathbf{P}$$

(53)

where  $\pi_u$  is the steady-state probability of the system being in State u. This matrix equation along with the probability distribution property that  $\pi_1 + \pi_2 + \cdots + \pi_{N_{States}} = 1$  can be solved to find the values of  $\pi_1, \pi_2, \cdots, \pi_{N_{States}}$ .

As the objective of this appendix is to derive the steady-state autocorrelation of  $q_i[n]$ , the Markov chain is taken to have converged to its steady state in the following analysis, i.e.,

$$\Pr(s_i[n] = u) = \pi_u \quad \text{for all } n. \tag{54}$$

Therefore,

$$\Pr\{s_i[n] = u, \ s_i[n+k] = v\} = \pi_u p_{u,v}(k)$$

(55)

where  $p_{u,v}(k)$  is the probability that the Markov chain's state at time index n+k is v given that it was in State u at time index n. Substituting this into (51) leads to an expression for  $\mathrm{E}\{q_i[n]q_i[n+k]\}$  that is independent of n. This implies that  $\mathrm{E}\{q_i[n]q_i[n+k]\} = \mathrm{E}\{q_i[n]q_i[n-k]\}$ . Furthermore, the definition of  $q_i[n]$  implies that  $\mathrm{E}\{q_i[n]\} = 0$ , so the mean of  $q_i[n]$  is also independent of n. It follows that  $q_i[n]$  is WSS. Substituting (55) into (51) and applying these observations implies that the autocorrelation of  $q_i[n]$  can be written as

$$R_{q,t}[k] = \sum_{u \in S_1} \pi_u \left[ \sum_{v \in S_1} p_{u,v} (|k|) - \sum_{w \in S_{-1}} p_{u,w} (|k|) \right] + \sum_{r \in S_{-1}} \pi_r \left[ \sum_{s \in S_{-1}} p_{r,s} (|k|) - \sum_{t \in S_1} p_{r,t} (|k|) \right].$$

(56)

The properties of Markov chains imply that

$$\begin{bmatrix} p_{u,1}(k) & p_{u,2}(k) & \dots & p_{u,N_{\text{Source}}}(k) \end{bmatrix} = \mathbf{b}_u \mathbf{P}^k, \tag{57}$$

where  $\mathbf{b}_u$  is a row vector of length  $N_{States}$  with a 1 in column u and zeros in all other columns [33]. Matrix equation (57) with the definition of  $\mathbf{P}$  via (52) is used to calculate the values of  $p_{u,v}(k)$  in (56).

The above analysis applies only to the primary ISI-scrambling 1-bit DACs, but it can be modified to apply to the auxiliary ISI-scrambling 1-bit DAC as follows. The properties of the  $o_{37}[n]$  and  $p_{37}[n]$  stochastic sequences described in Section II imply that the auxiliary ISI-scrambling 1-bit DAC's states can be modeled via a Markov chain with an  $N_{States} \times N_{States}$  state transition matrix,  $\mathbf{P} = [p_{u,v}]$ , that is similar to that described above for the primary ISI-scrambling 1-bit DACs. The only non-zero elements of the state transition matrix are still given by (52) except with  $p_{1,2} = p_{18,19} = p_{1,10} = p_{18,27} = q/2$  and  $p_{D,2} = p_{F,19} = p_{D,10} = p_{F,27} = 1/2$  because of the 50% chance that the swap state of the auxiliary ISI-scrambling 1-bit DAC gets inverted each time it goes offline.

By the same reasoning applied previously, **P** is irreducible and aperiodic, and  $q_{37}[n]$  is given by (50) with i = 37,  $S_1 = \{3, 4, ..., 9, 28, 29, ..., 34\}$ , and  $S_{-1} = \{11, 12, ..., 17, 20, 21, ..., 26\}$ . Consequently,  $R_{q,37}[k]$  is given by (56) with probability distributions calculated via (53) and (57) using the version of **P** corresponding to the auxiliary ISI-scrambling 1-bit DAC.

## VIII. APPENDIX C

Suppose  $x[n_t] = 8192\Delta \sin(\omega_0 n_t)$ , where  $\omega_0 = 2\pi f_0/f_s$ , and  $f_0/f_s$  satisfies (34). As  $e_i(t)$  has zero mean and  $x[n_t]$  is deterministic, the autocorrelation of  $e_i(t)$  can be written as

$$R_{e,i}(t,\tau) = g_i(t)g_i(t+\tau) E\{q_i[n_t]q_i[n_{t+\tau}]\},$$

(58)

with

$$g_i(t) = 2^{-2} \eta_i(t) \sin(\omega_0 n_t) \sin(\omega_0 (n_t - 1)). \tag{59}$$

The DAC's input sequence is generated digitally, so  $f_0/f_s$  is a rational number. This implies that  $g_i(t)$  is periodic with a period,  $T_g$ , where  $T_g$  is an integer multiple of  $T_s$ . As  $\eta_i(t)$  is periodic with a period of  $T_s$  by definition, this implies that  $g_i(t)g_i(t+\tau)$  is periodic in t with a period,  $T_g$ .

As proven in Appendix B, the discrete-time stochastic sequence,  $q_i[n]$ , is WSS, so the expectation term in (58) can be written as

$$E\{q_{i}[n_{i}]q_{i}[n_{i+\tau}]\} = R_{q_{i}}[n_{i+\tau} - n_{i}], \tag{60}$$

the right side of which is given by (56) with k replaced by  $n_{t+\tau} - n_t$ . The quantity  $n_{t+\tau}$  can be written as  $n_{t+\tau} = \lfloor n_t + \langle f_s t \rangle + n_\tau + \langle f_s \tau \rangle \rfloor$  where, for any real number  $x, \lfloor x \rfloor$  denotes the largest integer less than or equal to x, and  $\langle x \rangle = x - \lfloor x \rfloor$  is the fractional part of x. For any real numbers x and  $y, \lfloor x \rfloor - \lfloor y \rfloor$  can be written as  $\lfloor x - \lfloor y \rfloor$ , so

$$n_{t+\tau} - n_t = \left\lfloor \left\langle f_s t \right\rangle + n_\tau + \left\langle f_s \tau \right\rangle \right\rfloor. \tag{61}$$

The only term that contains t on right side of (61) is  $\langle f_s t \rangle$ , which is  $T_s$ -periodic, so (60) must be  $T_s$ -periodic in t. Given  $g_i(t)g_i(t+\tau)$  is periodic in t with a period,  $T_g$ , and  $T_g$  is an integer multiple of  $T_s$ , it follows from (58) and (60) that  $R_{e,i}(t,\tau)$  is periodic in t with a period of  $T_g$ . Consequently,  $e_i(t)$  is a cyclostationary random process and its average PSD is the Fourier transform of the average of  $R_{e,i}(t,\tau)$  over one  $T_g$  period of t, i.e., the Fourier

transform of

$$\overline{R}_{e,i}(\tau) = \frac{1}{T_g} \int_0^{T_g} g_i(t) g_i(t+\tau) R_{q,i}[n_{t+\tau} - n_t] dt .$$

(62)

Substituting (59) into (62) and applying sinusoid product-tosum identities shows that the integrand of (62) can be written as

$$f_{\tau}(t) \left[ 2\cos^{2}(\omega_{0}) + \cos\left(2\omega_{0}\left(n_{t+\tau} - n_{t}\right)\right) + \cos\left(2\omega_{0}\left(n_{t+\tau} + n_{t} - 1\right)\right) - 2\cos(\omega_{0})\cos\left(2\omega_{0}n_{t} - \omega_{0}\right) - 2\cos(\omega_{0})\cos\left(2\omega_{0}n_{t+\tau} - \omega_{0}\right) \right],$$

$$(63)$$

where

$$f_{\tau}(t) = 2^{-7} R_{a,i} \left[ n_{t+\tau} - n_{t} \right] \eta_{i}(t) \eta_{i}(t+\tau) . \tag{64}$$

Both  $\cos(2\omega_0 n_t - \omega_0)$  and  $\cos(2\omega_0 n_{t+\tau} + \omega_0)$  are constant with respect to t over successive intervals of  $T_s$ . Furthermore, they average to zero over intervals of  $T_g$  in t because the restrictions on  $\omega_0$  imposed by (34) prevent them from aliasing to zero frequency. By the same reasoning,  $\cos(2\omega_0(n_{t+\tau} + n_t - 1))$  averages to zero over intervals of  $T_g$  in t, and it is constant with respect to t over two fixed sub-intervals of every successive  $T_s$  time interval. Given that  $f_t(t)$  is  $T_s$ -periodic in t, the above observations imply that the last three terms on the right side of (63) average to zero in (62), so they do not contribute to  $\overline{R}_{e,t}(\tau)$ .

As explained above, (61) and, hence,  $\cos(2\omega_0(n_{t+\tau}-n_t))$  are  $T_s$ -periodic in t. Given that  $f_t(t)$  is  $T_s$ -periodic in t and  $\cos^2(\omega_0)$  is constant, it follows that all the terms in (63) which contribute to  $\overline{R}_{e,t}(\tau)$  are  $T_s$ -periodic in t, so (62) can be written as

$$\overline{R}_{e,i}(\tau) = \frac{1}{T_s} \int_0^{T_s} f_{\tau}(t) \left[ 2\cos^2(\omega_0) + \cos\left(2\omega_0 \left(n_{t+\tau} - n_t\right)\right) \right] dt . (65)$$

Equation (61) implies that

$$n_{t+\tau} - n_t = \begin{cases} n_{\tau}, & \text{if } \langle f_s t \rangle < 1 - \langle f_s \tau \rangle, \\ n_{\tau} + 1, & \text{otherwise,} \end{cases}$$

(66)

so (65) with (64) can be rewritten as

$$\overline{R}_{e,i}(\tau) = w_i [n_\tau] \int_0^{T_s(1-\langle f_s \tau \rangle)} \eta_i(t) \eta_i(t+\tau) dt

+ w_i [n_\tau + 1] \int_{T_s(1-\langle f_s \tau \rangle)}^{T_s} \eta_i(t) \eta_i(t+\tau) dt,$$

(67)

where

$$w_{i}[n_{\tau}] = \frac{2^{-7} R_{q,i}[n_{\tau}]}{T_{s}} \left[ 2\cos^{2}(\omega_{0}) + \cos(2\omega_{0}n_{\tau}) \right].$$

(68)

As  $\eta_i(t)$  is  $T_s$ -periodic, the  $\eta_i(t+\tau)$  integrand factors in the first and second integrals on the right side of (67) can be replaced by  $\eta_i(t+\tau-n_\tau T_s)$  and  $\eta_i(t+\tau-(n_\tau+1)T_s)$ , respectively, without changing  $\overline{R}_{e,i}(\tau)$ . By definition,  $\langle f_s\tau \rangle = f_s\tau - n_\tau$ , so these replacements can be written as  $\eta_i(t+T_s\langle f_s\tau \rangle)$  and  $\eta_i(t-T_s(1-\langle f_s\tau \rangle))$ , respectively. Hence, with these replacements, both integrals have integrands of the form  $\eta_i(t)\eta_i(u)$  and the limits of integration are such that t and u are limited to and, together, span the range  $[0, T_s]$ . Therefore, (67) can be rewritten as

$$\overline{R}_{e,i}(\tau) = w_i [n_\tau] \eta_{p^*,i} (\tau - n_\tau T_s)

+ w_i [n_\tau + 1] \eta_{p^*,i} (\tau - (n_\tau + 1) T_s),$$

(69)

where

$$\eta_{p^*,i}(u) = \int_{-\infty}^{\infty} \eta_{p,i}(t) \eta_{p,i}(t+u) dt$$

(70)

and

$$\eta_{p,i}(t) = \begin{cases} \eta_i(t) & \text{if } 0 \le t < T_s, \\ 0 & \text{otherwise.} \end{cases}$$

(71)

By definition,  $\eta_{p^*,i}(\tau)$  is nonzero only when  $-T_s < \tau < T_s$ , so (69) can be rewritten as

$$\overline{R}_{e,i}(\tau) = \sum_{n=-\infty}^{\infty} w_i[n] \eta_{p^*,i}(\tau - nT_s). \tag{72}$$

Taking the CTFT of (72) yields

$$S_{e,i}(j\omega) = H_{p^*,i}(j\omega) \sum_{n=-\infty}^{\infty} w_i[n] e^{-j\omega n T_s}$$

$$= H_{p^*,i}(j\omega) W_i(e^{j\omega T_s}),$$

(73)

where  $H_{p^*,i}(j\omega)$  is the CTFT of  $n_{p^*,i}(t)$  and  $W_i(e^{i\omega Ts})$  is the DTFT of  $w_i[n]$ . Taking the DTFT of (68) with  $n_t$  replaced by n yields

$$W_{i}\left(e^{j\omega T_{s}}\right) = \frac{2^{-8}}{T_{s}} \left[4\cos^{2}\left(\omega_{0}\right)S_{q,i}\left(e^{j\omega T_{s}}\right) + S_{q,i}\left(e^{j(\omega+2\omega_{0})T_{s}}\right) + S_{q,i}\left(e^{j(\omega-2\omega_{0})T_{s}}\right)\right]$$

(74)

where  $S_{q,i}(e^{j\omega Ts})$  is the DTFT of  $R_{q,i}[k]$  which is given by (56).

#### REFERENCES

- [1] R. van de Plassche, "Dynamic element matching for high-accuracy monolithic D/A converters," *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 1976, pp. 148-149.

- [2] K. O. Sullivan, C. Gorman, M. Hennessy and V. Callaghan, "A 12-bit 320-MSample/s current-steering CMOS D/A converter in 0.44 mm<sup>2</sup>," *IEEE J. of Solid-State Circuits*, vol. 39, no. 7, pp. 1064-1072, July 2004.

- [3] B. Jewett, J. Liu and K. Poulton, "A 1.2 Gs/s 15b DAC for precision signal generation," *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2005, pp. 110-111.

- [4] K. L. Chan, J. Zhu and I. Galton, "Dynamic element matching to prevent nonlinear distortion from pulse-shape mismatches in high-resolution DACs," *IEEE J. of Solid-State Circuits*, vol. 43, no. 9, pp. 2067-2078, September 2008.

- [5] W.-T. Lin, H.-Y. Huang and T.-H. Kuo, "A 12-bit 40 nm DAC achieving SFDR > 70 dB at 1.6 GS/s and IMD < -61dB at 2.8 GS/s with DEMDRZ technique," *IEEE J. of Solid-State Circuits*, Vol. 49, no. 3, pp. 708-717, March 2014.

- [6] W. Mao, Y. Li, C. Heng and Y. Lian, "High dynamic performance current-steering DAC design with nested-segment structure," *IEEE Transactions on Very Large Scale Integration Systems*, vol. 26, no. 5, pp. 995-999, May 2018.

- [7] C.-H. Lin, K. L. J. Wong, T.-Y. Kim, G. R. Xie, D. Major, G. Unruh, S. R. Dommaraju, H. Eberhart and A. Venes, "A 16b 6 GS/s Nyquist DAC with IMD < -90dBc up to 1.9 GHz in 16 nm CMOS," *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2018, pp. 360 362.

- [8] D. Kong, K. Rivas-Rivera and I. Galton, "A 600 MS/s DAC with over 87-dB SFDR and 77-dB peak SNDR enabled by adaptive cancellation of static and dynamic mismatch error," *IEEE J. of Solid-State Circuits*, vol. 54, no. 8, pp. 2219-2229, August 2019.

- [9] H.-Y. Huang and T.-H. Kuo, "A 0.07-mm<sup>2</sup> 162-mW DAC achieving >65 dBC SFDR and < -70 dBc IM3 at 10 GS/s with output impedance compensation and concentric parallelogram routing," *IEEE J. of Solid-State Circuits*, vol. 55, no. 9, pp. 2478-2488, September 2020.

- [10] J. Remple and I. Galton, "The effects of inter-symbol interference in dynamic element matching DACs," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 64, no. 1, pp. 14-23, Jan. 2017.

- [11] T. He, M. Ashburn, S. Ho, Y. Zhang and G. Temes, "A 50MHZ-BW continuous-time ΔΣ ADC with dynamic error correction achieving 79.8dB SNDR and 95.2dB SFDR," *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2018, pp. 230-232.

- [12] S. Su and M. S.-W. Chen, "A 12-bit 2 GS/s dual-rate hybrid DAC with pulse-error pre-distortion and in-band noise cancellation achieving > 74 dBc SFDR and <-80 dBc IM3 up to 1 GHz in 65 nm CMOS," *IEEE J. of Solid-State Circuits*, vol. 51, no. 12, pp. 2963-2978, December, 2016.

- [13] S. Su and M. S.-W. Chen, "A 16-bit 12-GS/s single-/dual-rate DAC with a successive bandpass delta-sigma modulator achieving <-67-dBc IM3 within DC to 6-GHz tunable passbands," *IEEE J. of Solid-State Circuits*, vol. 53, no. 12, pp. 3517-3527, Dec. 2018.

- [14] D. Basak, S. Kalani, P. Kinget and K. Pun, "An on-chip static and dynamic DAC error correction technique for high speed multibit delta-sigma modulators," *IEEE Int. Symposium on Circuits and Systems (ISCAS)*, Florence, 2018, pp. 1-5.

- [15] Y. Tang, J. Briaire, K. Doris, R. van Veldhoven, P. C. W. van Beek, H. J. A. Hegt and A. H. M. van Roermund, "A 14-bit 200 MS/s DAC with SFDR > 78 dBc, IM3 < -83 dBc and NSD < -163 dBm/Hz across the whole nyquist band enabled by dynamic-mismatch mapping", *IEEE J. of Solid-State Circuits*, vol. 46, no. 6, pp. 1371-1381, June 2011.

- [16] H. Van de Vel, J. Briaire, C. Bastiaansen, P. van Beek, G. Geelen, H. Gunnink, Y. Jin, M. Kaba, K. Luo, E. Paulus, B. Pham, W. Relyveld and P. Zijlstra, "A 240mW 16b 3.2GS/s DAC in 65nm CMOS with <-80dBc IM3 up to 600 MHz," *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2014, pp. 206-208.

- [17] T. Shui, R. Schreier and F. Hudson, "Mismatch shaping for a current-mode multibit delta-sigma DAC," *IEEE J. of Solid-State Circuits*, vol. 34, no. 3, pp. 331-338, March 1999.

- [18] L. Risbo, R. Hezar, B. Kelleci, H. Kiper and M. Fares, "Digital approaches to ISI-mitigation in high-resolution oversampled multi-level D/A converters," *IEEE J. of Solid-State Circuits*, vol. 46, no. 12, pp. 2892-2903, December 2011.

- [19] A. Sanyal, P. Wang and N. Sun, "A thermometer-like mismatch shaping technique with minimum element transition activity for multibit ΔΣ DACs," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 61, no. 7, pp. 461-465, July 2014.

- [20] A. Sanyal, L. Chen and N. Sun, "Dynamic element matching with signalindependent element transition rates for multibit ΔΣ modulators," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 62, no. 5, pp. 1325-1334, May 2015.

- [21] I. Galton, "Why Dynamic-Element-Matching DACs Work," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 57, no. 2, pp. 69–74, Feb. 2010.

- [22] L. Lai, X. Li, Y. Fu, Y. Liu and H. Yang, "Demystifying and Mitigating Code-Dependent Switching Distortions in Current-Steering DACs," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 66, no. 1, pp. 68-81, January 2019.