# FlexFilt: Towards Flexible Instruction Filtering for Security

Leila Delshadtehrani delshad@bu.edu Boston University Boston, Massachusetts, USA Sadullah Canakci scanakci@bu.edu Boston University Boston, Massachusetts, USA William Blair wdblair@bu.edu Boston University Boston, Massachusetts, USA

Manuel Egele megele@bu.edu Boston University Boston, Massachusetts, USA

Ajay Joshi joshi@bu.edu Boston University Boston, Massachusetts, USA

#### **ABSTRACT**

As the complexity of software applications increases, there has been a growing demand for intra-process memory isolation. The commercially available intra-process memory isolation mechanisms in modern processors, e.g., Intel's memory protection keys, trade-off between efficiency and security guarantees. Recently, researchers have tended to leverage the features with low security guarantees for intra-process memory isolation. Subsequently, they have relied on binary scanning and runtime binary rewriting to prevent the execution of unsafe instructions, which improves the security guarantees. Such intra-process memory isolation mechanisms are not the only security solutions that have to prevent the execution of unsafe instructions in untrusted parts of the code. In fact, we identify a similar requirement in a variety of other security solutions. Although binary scanning and runtime binary rewriting approaches can be leveraged to address this requirement, it is challenging to efficiently implement these approaches.

In this paper, we propose an efficient and flexible hardware-assisted feature for runtime filtering of user-specified instructions. This flexible feature, called FlexFilt, assists with securing various isolation-based mechanisms. FlexFilt enables the software developer to create up to 16 instruction domains, where each instruction domain can be configured to filter the execution of user-specified instructions. In addition to filtering unprivileged instructions, FlexFilt is capable of filtering privileged instructions. To illustrate the effectiveness of FlexFilt compared to binary scanning approaches, we measure the overhead caused by scanning the JIT compiled code while browsing various webpages. We demonstrate the feasibility of FlexFilt by implementing our design on the RISC-V Rocket core, providing the Linux kernel support for it, and prototyping our full design on an FPGA.

#### **CCS CONCEPTS**

- Security and privacy  $\rightarrow$  Hardware security implementation.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

ACSAC '21, December 6–10, 2021, Virtual Event, USA © 2021 Association for Computing Machinery. ACM ISBN 978-1-4503-8579-4/21/12...\$15.00 https://doi.org/10.1145/3485832.3488019

#### **KEYWORDS**

Hardware security, OS security, memory protection domains

#### **ACM Reference Format:**

Leila Delshadtehrani, Sadullah Canakci, William Blair, Manuel Egele, and Ajay Joshi. 2021. FlexFilt: Towards Flexible Instruction Filtering for Security. In Annual Computer Security Applications Conference (ACSAC '21), December 6–10, 2021, Virtual Event, USA. ACM, New York, NY, USA, 14 pages. https://doi.org/10.1145/3485832.3488019

#### 1 INTRODUCTION

Today's software is a complex mixture of trusted code written in-house and untrusted code such as third-party libraries and application plugins. The coexistence of trusted code with potentially vulnerable or malicious untrusted code in the same process could comprise the confidentiality and integrity of the trusted code. To limit the effects of bugs and security vulnerabilities, a variety of security solutions partition sensitive data and code into isolated components. Researchers have leveraged various techniques including Operating System (OS)-based [10, 44] and virtualization-based techniques [8, 40, 46], hardware-based trusted execution environments [4, 23], and memory protection domains [32, 58, 61] to enforce isolation.

To guarantee the integrity of the isolation, the above-mentioned security solutions have to prevent an untrusted component from accessing or modifying the isolated components. To this end, a variety of prior work [4, 5, 14, 15, 24, 30, 32, 49, 58, 61, 65-67] faced a common challenge, i.e., preventing the execution of various unsafe instructions in untrusted parts of the code (either in user space or kernel space). Such unsafe instructions could compromise the integrity of the isolation mechanisms by modifying access permissions, disabling protections, gaining higher privilege, etc. To prevent the execution of such unsafe instructions, previous works have leveraged various approaches such as Control-Flow Integrity (CFI) [14, 24, 49] and binary scanning and binary rewriting [4, 5, 30, 32, 49, 61, 65, 67]. As currently existing CFI solutions [21, 25, 31, 35, 35, 45] have nontrivial performance overhead (> 10%), leveraging CFI to prevent the execution of unsafe instructions is expensive. Additionally, CFI cannot simply be leveraged in self-modifying or dynamically generated code [58]. As shown by previous works, binary scanning and binary rewriting approaches can filter unsafe instructions in static code [32, 61]. However, an efficient implementation of binary scanning and binary rewriting, especially for dynamically generated code, is challenging.

To clarify the challenges involved in binary scanning and binary rewriting for preventing the execution of unsafe instructions, consider the case of memory protection keys. In recent years, various processors including ARM [51], IBM Power [54], and Intel [55] provided hardware-assisted memory protection keys, an extension to page-based memory permissions. Accordingly, a software developer can associate a group of memory pages with the same protection key to create a memory protection domain. Subsequently, the software developer can update the access permission of all the pages in the same domain by updating the corresponding permission bits of the protection key. While ARM and IBM Power only allow the OS to modify the corresponding permission of a protection key, Intel MPK allows a user-space process to make this modification. Intel MPK stores the corresponding permission bits of all the protection keys in a new thread-local register, called protection key right register (PKRU). Modifying the permission bits of a protection domain requires writing into PKRU leveraging a new user-space instruction, called WRPKRU. The execution of the WRPKRU instruction is fast but an untrusted component can gain access permission to any protection domain by simply writing into PKRU through executing the WRPKRU instruction.

To ensure that all the occurrences of WRPKRU instructions are safe, various approaches such as Hodor [32] and ERIM [61] rely on binary inspection and runtime binary rewriting. One of the main challenges in ensuring the safety of WRPKRU occurrences through binary inspection is the implicit (unintended) occurrences of the instruction. Such implicit occurrences could be the result of the WRPKRU instruction forming across the boundary between two consecutive instructions or as a sub-sequence of a longer instruction. An attacker can perform a control-flow hijacking attack to jump into the point that an implicit WRPKRU instruction occurs. To address this challenge, Hodor leverages debug registers to trigger a hardware watchpoint once an explicit or implicit WRPKRU is about to be executed. A vetting mechanism at kernel level allows the execution to continue only for safe occurrences of the WRPKRU instruction. ERIM intercepts each executable page and scans through the page for unsafe instructions; then, it enables the execute permission iff no unsafe occurrences exist. Otherwise, ERIM implements a runtime binary rewriting approach to rewrite the implicit occurrences of unsafe instructions.

The above-mentioned challenges for restricting the occurrence of WRPKRU instructions to safe locations indicate the requirement for an efficient approach to filter unsafe instructions at runtime. This requirement is not limited to memory protection domains, WRPKRU instructions, or x86 processors. We observed that a number of isolation-based security solutions, on different processor architectures, have to prevent the execution of various unsafe instructions in untrusted parts of the code. In the rest of this paper, we refer to the unsafe instructions as target instructions that should be filtered. Depending on the isolation mechanism, the target instructions could be privileged or unprivileged instructions. In x86 processors, other security solutions [30, 65] limit the execution of target instructions such as privileged MOV CR0, MOV CR3, and VMRUN. Prior work on ARM processors [4, 5, 67] prevent the occurrence of target instructions such as MSR, LDC, and MCR in untrusted parts of the code. Recent works leveraging memory protection domains on

RISC-V architecture [14, 15, 58] have to limit the execution of the WRPKRU equivalent instruction.

The previous works are limited to filtering the execution of certain target instructions. In this paper, we strive to provide a generalized solution for filtering target instructions. Such a generalized solution should satisfy the following requirements: 1) flexibility to be applicable to a variety of instructions, 2) efficiency to be applicable at runtime, and 3) fine-granularity to be able to filter various parts of the code. To this end, we propose FlexFilt, an efficient and flexible hardware-assisted capability for runtime filtering of target instructions at page granularity. FlexFilt provides the generalized instruction filtering capability via two mechanisms, i.e., instruction protection domains and flexible hardware-level filters. FlexFilt enables the software developer to create instruction protection domains by assigning the same protection key to a group of executable pages. At the hardware level, FlexFilt provides configurable filters to prevent the execution of various user-defined instructions. The hardware-level filters can then be associated with instruction protection domains and subsequently prevent the execution of target instructions in memory pages assigned to the corresponding domain. FlexFilt is an efficient hardware-assisted feature and incurs negligible performance overhead for filtering target instructions at runtime. FlexFilt satisfies all the previously mentioned requirements of a generalized instruction filtering solution. In addition to filtering user-space instructions, FlexFilt is capable of filtering privileged instructions (i.e., supervisor mode and hypervisor mode).

To demonstrate the feasibility of FlexFilt's design, we leverage the RISC-V open Instruction Set Architecture (ISA) [64] and implement FlexFilt on the RISC-V Rocket core [3]. To evaluate FlexFilt in a realistic environment, we provide the OS support for our hardware design and prototype our full design (including hardware, OS, and user-space software) on the Xilinx Zedboard FPGA [52]. In summary, our contributions are as follows:

- We propose FlexFilt, a flexible hardware-assisted feature, which enables a software developer to efficiently prevent the execution of various instructions at a page granularity.

- To demonstrate the feasibility of our design, we implement a practical prototype, consisting of the RISC-V Rocket core enhanced with FlexFilt and the Linux kernel support for FlexFilt, on an FPGA.

- To illustrate the effectiveness of FlexFilt compared to binary scanning approaches, we measure the overhead of scanning JIT compiled bytes generated by V8 JavaScript engine while browsing various webpages.

In the spirit of open science and to facilitate the reproducibility of our experiments, we will submit our work for artifact evaluation and open-source our full design.

#### 2 MOTIVATION AND RELATED WORK

As mentioned before, a variety of previous works faced the challenge of preventing the execution of target instructions in untrusted parts of the code. Table 1 lists these works, their target instructions, and the approaches they used for filtering the instructions.

| Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Mechanism        | Target Instructions                     | Privilege Level   | Filtering Approach                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------|-------------------|------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ERIM [61]        | WRPKRU, XRSTOR                          | User              | Binary inspection and rewriting          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Hodor [32]       | WRPKRU                                  | User              | Binary scanning and hardware watchpoints |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | libmpk [49]      | WRPKRU                                  | User              | CFI or relying on an approach like ERIM  |

| 06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Xu et al. [66]   | WRPKRU                                  | User              | Relying on approach like Hodor or ERIM   |

| XOU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Donky [58]       | WRPKRU                                  | User              | Hardware-assisted call-gates             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IMIX [24]        | Extended instruction (SMOV)             | User              | CFI                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Fidelius [65]    | MOV CR0, MOV CR4, WRMSR, VMRUN, MOV CR3 | Supervisor        | Binary scanning                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Underbridge [30] | WRPKRU, MOV CR3                         | User & Supervisor | Binary scanning and rewriting            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Silhouette [67]  | MSR                                     | User              | Binary scanning                          |

| Donky [58] WRPKRU User Hardware-assiste IMIX [24] Extended instruction (SMOV) User CFI Fidelius [65] MOV CR0, MOV CR4, WRMSR, VMRUN, MOV CR3 Supervisor Binary scan Underbridge [30] WRPKRU, MOV CR3 User & Supervisor Binary scan Silhouette [67] MSR User Binary scan TZ-PKR [4] LDC, MCR Supervisor Binary scan SKEE [5] N/A Supervisor Binary scan Binary scan SKEE [5] N/A Supervisor Binary scan Skee Supervisor Binary Skee Binary Skee Binary Skee Binary Skee Binary Skee Binary Skee Bi | Binary scanning  |                                         |                   |                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SKEE [5]         | N/A                                     | Supervisor        | Binary scanning                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Donky [58]       | N/A                                     | User              | Hardware-assisted call-gates             |

| RISC-V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SealPK [14]      | Extended instruction (WRPKR)            | User              | Hardware-assisted instruction filtering  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FlexFilt         | Various instructions                    | User & Supervisor | Hardware-assisted flexible filters       |

Table 1: Comparison of previous works that prevent the execution of target instructions at runtime.

## 2.1 Instruction Filtering in Processors

x86 Processors. Recently, with the availability of Intel MPK [55] on high-end commercial x86 processors, researchers focused on deploying MPK in a secure way. To ensure the security of Intel MPK for intra-process memory isolation, it is necessary to prevent an untrusted component from executing WRPKRU or XRSTOR instructions, which might lead to unauthorized access to protected memory pages. 1 As an example, consider a scenario where the software developer aims to only allow the execution of WRPKRU instruction in trusted parts of the code. In this example, we assume that the software developer writes two trusted functions, namely good\_code1 and good\_code2. She modifies the permission bits of her memory protection domains through WRPKRU instructions only in the two trusted functions and she wants to prevent the execution of WRPKRU in other parts of the code. As shown in Table 1, various recent works leveraged different approaches to prevent the unsafe execution of WRPKRU (and XRSTOR) instruction. Hodor [32] leverages binary scanning and hardware watchpoints to prevent the execution of unsafe WRPKRU instructions. ERIM [61] relies on binary inspection and binary rewriting techniques to prevent an unsafe execution of a WRPKRU or an XRSTOR instructions. libmpk [49] and the work by Xu et al. [66] address the scalability issue of Intel MPK using software-based and hardware-based virtualization techniques, respectively. These virtualization techniques [49, 66] rely on CFI or previous approaches such as ERIM and Hodor to filter unsafe WRPKRU instructions. Donky [58] uses a hardware-assisted call-gate mechanism to secure the domain transitions of MPK, without the need for binary scanning or CFI. IMIX [24] assumes the mitigation approaches such as CFI and Code-Pointer Integrity (CPI) [41] to prevent an attacker from reusing the trusted code containing SMOV, an extended instruction for secure load and store.

The need to filter target instructions in x86 architecture is not limited to user-space instructions protecting MPK. Fidelius [65] proposes a software-based extension to protect the Virtual Machine (VM) against an untrusted hypervisor. Fidelius utilizes binary scanning to restrict the execution of instructions that might hijack the control flow (e.g., VMRUN) or switch the address space (e.g., MOV CR3). Underbridgee [30] retrofits Intel MPK for kernel space isolation.

To prevent the bypassing of the isolation enforced by MPK, Underbridge leverages binary scanning and rewriting. Subsequently, Underbridge ensures that system servers do not contain any explicit or implicit CR3 instructions that modify the page table base register. 2.1.2 ARM Processors. Researchers have faced the instruction filtering requirement on ARM processors too. Silhouette [67] provides a protected implementation of the shadow stack on embedded ARM processors. Silhouette scans the code to ensure that it does not contain an instruction, such as MSR, that can be used to modify the program state without the need for a store instruction. TZ-PKR [4] provides a real-time protection of the OS kernel by leveraging ARM TrustZone [50]. SKEE [5] implements a light-weight framework for a secure kernel-level execution environment on ARM architectures, without relying on a higher privileged layer. To prevent the kernel from executing target privileged instructions, both TZ-PKR and SKEE scan the kernel executables looking for certain control instructions, such as MCR and LDC. These instructions are replaced with hooks that jump to a switch gate.

2.1.3 RISC-V Processors. Multiple recent works [14, 15, 58] provided memory protection keys for RISC-V. In addition to the x86 implementation, Donky [58] provides the intra-process memory isolation feature for RISC-V and leverages hardware-assisted callgates to secure its implementation. Similarly, SealPK [14, 15] implements the memory protection keys for RISC-V. SealPK provides a hardware-assisted feature allowing the software developer to restrict the execution of the WRPKRU instruction to a contiguous range of memory addresses (e.g., one trusted function). Unlike the flexible design of FlexFilt, SealPK's implementation is limited to allowing the execution of a fixed instruction in only one trusted function.

## 2.2 Shortcomings of Existing Approaches for Instruction Filtering

As discussed before, a large number of previous works [4, 5, 30, 32, 61, 65, 67] rely on binary scanning to prevent the execution of target instructions. In CISC architectures such as x86, one of the challenges in filtering target instructions is the implicit (unintended) occurrences of these instructions. The target instructions can be formed implicitly across the boundary between instructions or as a sub-sequence of a longer instruction. Filtering the target instructions in RISC architectures, including ARM and RISC-V, is simpler because these architectures use fixed-length instructions. Although both ARM and RISC-V support compressed instructions (16-bit instructions), instructions cannot be loaded at any offset in

<sup>&</sup>lt;sup>1</sup> XRSTOR restores the full or partial state of a processor's state during a context switch. The XRSTOR instruction can modify the contents of the PKRU register (which stores the permission bits of all the domains) by setting a specific bit in the eax register before executing the instruction [61].

the memory (unlike x86). As FlexFilt monitors and filters instructions at the execution stage, we are not concerned with the implicit vs explicit occurrences of instructions.

Although binary scanning approaches are efficient for the static code, binary scanning and subsequently binary rewriting can be costly for dynamically generate code. In Section 6, we analyze the overhead of scanning the Just-In-Time (JIT) compiled pages while browsing various websites and discuss the challenges faced by prior work to prevent the execution of target instructions in the JIT code. FlexFilt provides flexible instruction filters that allow the software developer to prevent the execution of target instructions on any page, irrespective of whether the page contains static code or dynamically generated code (e.g., JIT compiled), without relying on binary scanning and binary rewriting.

### 2.3 Watchpoints and Hardware Monitors

Most modern architectures provide a number of hardware watch-points or debug registers. A hardware watchpoint is a debugging mechanism that allows the software developer to monitor a number of programmer-specified memory locations. Whenever the monitored locations are accessed, the hardware triggers an exception and traps into the debugger. Unfortunately, due the limited number of hardware watchpoints in modern architectures (e.g., only 4 watchpoints in x86), it cannot effectively be used as a fine-grained standalone solution to filter instructions at runtime.

In addition to commercially available hardware watchpoints, researchers have proposed a variety of dedicated [29, 68] and flexible hardware monitors [16, 18-20]. iWatcher [68] provides a large yet limited number of programmable hardware watchpoints while Greathouse et al. [29] propose an approach that supports an unlimited number of watchpoints. Even with an unlimited number of watchpoints, the software developer still has to utilize binary scanning to identify all the possible occurrences of target instructions and monitor the execution of each occurrence using a watchpoint. To leverage FlexFilt, the software developer only needs to specify the list of target instructions and the trusted parts of the code. Flexible hardware monitors such as PUMP [20], FlexCore [18], Harmoni [19], and PHMon [16] are capable of performing a variety of monitoring tasks. FlexCore and Harmoni have similar capabilities as PUMP; however, PUMP is more flexible and it has been more extensively adopted [12, 36, 57]. Although it is feasible to leverage PUMP to prevent the execution of target instructions, specifying the tag checking and propagation rules for PUMP is a challenging task. FlexFilt requires fewer and less invasive hardware modifications compared to PUMP's invasive hardware modifications on all stages of the CPU, caches, and main memory. PHMon can filter the execution of target instructions in a specific range of memory addresses leveraging a number of match units. However, the number of memory regions to filter target instructions is limited to the number of match units. Hence, unlike FlexFilt, PHMon cannot enforce a fine-grained instruction filtering at page granularity.

## 2.4 Hardware-Assisted Instruction Stream Customization

A large number of modern processors provide the Âţops capability to convert a complex ISA to simpler and easier to execute stream of instructions. Additionally, several processors such as IBM's DAISY [22], TransmetaâĂŹs Crusoe and Efficieon [13], and

NvidiaâĂŹs Denver [9] implement a dynamic binary translator hardware and a software layer for performance optimization. A number of prior works provide the hardware support for runtime instruction customization and leverage it for functionalities beyond dynamic optimizations, e.g., safety/security checking and enforcement, profiling, and dynamic code decomposition [11, 59, 60]. DISE [11] is a programmable macro engine that translates userdefined instruction streams to customized streams at the decoder level. Importantly, DISE does not support per-domain or addressbased instruction customization, which is a fundamental requirement in our instruction filtering use cases. Context-Sensitive Decoding (CSD) [59] enables program instructions to be dynamically translated into a customized set of Âţops. CSD can turn on and turn off the custom translations in different address ranges specified through a set of Model-Specific Registers (MSRs). The limited number of registers available for specifying the address ranges for instruction customization is in contrast with the requirements of some of our use cases, e.g., filtering WRPKRU in various untrusted functions. As modifying the contents of MSRs requires transitions to the kernel level, frequent runtime modification of these MSRs for addressing the limited number of available MSRs or handling the JIT compiled code could lead to high performance overheads. Context-Sensitive Fencing (CSF) [60] proposes a microcode level defense against Spectre attacks [39] by leveraging CSD.

In principle, hardware-assisted dynamic instruction customization approaches, such as DISE and CSD, can be complementary to FlexFilt upon detecting a target instruction. For example, one might be interested in replacing a target instruction with a sequence of safe instructions, e.g., a NOP instruction. Assuming that the imminent execution of a target instruction is an indication of an attack that undermines the security of the system, we currently terminate the program execution rather than replacing the target instruction with safe instructions. However, in the absence of the dynamic instruction customization support, we can provide additional flexibility by performing other operations in the exception handler instead of terminating the process, e.g., trap to a debugger.

#### 3 BACKGROUND

We leverage the RISC-V open Instruction Set Architecture (ISA) to design, implement, and evaluate FlexFilt. In this section, we provide the background information on the RISC-V ISA [64]. In this paper, our focus is on commonly used 64-bit RISC-V processors (RV64). RISC-V ISA dedicates four opcodes for custom instruction-set extensions. Instructions with these opcodes, called custom instructions, are reserved for customization and will not be used by future standard extensions. We leverage RISC-V custom instructions to configure FlexFilt. The RISC-V ISA has unprivileged [62] and privileged [63] ISA specifications. Currently, the RISC-V ISA provides three privilege levels, i.e., user/application, supervisor, and machine modes. The highest level of privilege belongs to the machine mode, which is a mandatory privilege level for any RISC-V core.

For RV64, RISC-V specifies two page-based virtual memory systems, i.e., Sv39 and Sv48. Sv39 and Sv48 provide a 39-bit and a 48-bit virtual address space, respectively, where in both cases the address space is divided into 4KB pages. The privilege spec of RISC-V ISA specifies the virtual address translation process and the format of the Page Table Entry (PTE). Each PTE holds the mapping between a

virtual address of a page and its corresponding address of a physical frame. Bits 3-1 of each PTE are the page permission bits, indicating whether a page is readable, writable, and executable, respectively. The top 10 bits of an Sv39 and Sv48 PTE (bits 63-54) are reserved for future use, e.g., to facilitate research experiments [63]. The previous works on memory protection keys for RISC-V including Donky [58] and SealPK [14] leverage these 10 unused bits to store the memory protection key information.

In addition to access permissions stored in PTE, RISC-V ISA specifies the Physical Memory Protection (PMP) capability. PMP provides a per thread view (for each hart) that enables the programmable machine mode to limit the physical addresses that are accessible by software. PMP divides the physical memory address into up to 16 configurable regions, where each region can be configured with specific access permissions. At hardware level, a PMP unit utilizes machine-mode CSRs to specify the memory access permission (read, write, and execute) of each region. At runtime, PMP checks are applied to all the accesses in user and supervisor modes. Various previous works [37, 38, 42, 43, 53] leverage PMPs for providing an additional security layer. One could be tempted to implement FlexFilt on top of PMP. However, each PMP region is specified by a contiguous range of memory addresses and there are only 16 PMPs available. For our design, we are interested in creating instruction domains at page granularity, which is not feasible with 16 available PMPs. Hence, we do not build our instruction domains on top of the existing PMP feature.

#### 4 THREAT MODEL

FlexFilt can be leveraged in a variety of security use cases introduced by prior work (see Table 1). In our work, for each use case, we follow the common threat model in the prior work. For intra-process memory isolation approaches, we assume that the untrusted parts of the code might contain vulnerabilities that an adversary can exploit to inject or reuse arbitrary instructions including the target instructions (e.g., WRPKRU). We do not assume any restrictions about what an attacker would do after a successful attack. We assume that the safe occurrences of target instructions in trusted parts of the code are surrounded by call gates or trampolines similar to the ones described in [32, 61], which protect these occurrences against control-flow hijacking attacks.

As the OS is responsible for allocating the instruction domains and maintaining FlexFilt's information, we assume the OS kernel is (partially) trusted. We assume all hardware components, including our modifications, are trusted and bug free. Hence, rowhammer, side-channel, and fault attacks are beyond the scope of this work.

#### 5 DESIGN

In this section, we discuss FlexFilt's design goals, the challenges involved in implementing FlexFilt, and our solutions to address those challenges. As discussed before, we identified a common requirement for a flexible runtime instruction filtering capability in a variety of previous works. Unlike prior works that provide a solution capable of filtering a small number of specific target instructions, we strive to provide a generalized solution for the runtime filtering of target instructions. Such a generalized solution should be flexible, efficient, and fine-grained. To be compatible with existing OS-supported memory protections, we implement FlexFilt

at page granularity, i.e., each executable page can apply a combination of the configured instruction filters. This design choice allows us to leverage the already existing OS-managed structures such as PTE as well as hardware structures such as Translation Lookaside Buffer (TLB) in our implementation. While, providing a finer granularity for instruction filtering requires substantial modifications at both OS-level and hardware-level.

We need to provide the OS support as well as a software API to enable a software developer to use FlexFilt. In the rest of this section, we will first discuss our hardware design choices, followed by the OS support for FlexFilt, and then the software support to configure our flexible instruction filters.

## 5.1 Hardware Design

In this section, we discuss the hardware design of FlexFilt.

5.1.1 Instruction Protection Domains. To leverage the existing OS-level and hardware-level structures for memory protection, we implement FlexFilt at page granularity. Inspired by the design of memory protection keys, we devise instruction protection keys, which enable us to simply divide the software code into trusted and untrusted executable partitions. The software developer can assign the same instruction protection key to a group of executable pages, which subsequently creates instruction protection domains. The existing memory protection keys such as Intel MPK are only applicable to data memory accesses, not instruction addresses. Here, our focus is on associating fetched instructions to protection domains according to the corresponding address of each instruction.

Prior work [14, 15, 58] leverages the 10 unused bits of the RISC-V Sv39/Sv48 PTE to store the memory protection key. Similarly, we can utilize these 10 unused bits to store the instruction protection keys, which provides up to 1024 instruction protection domains. Supporting a large number of data memory protection domains is a necessity in various use cases, such as Persistent Memory Object (PMO) [66] and OpenSSL [49]. However, supporting a large number of domains is not required for instruction protection domains. According to our literature review, previous works with the instruction filtering requirements only needed two instruction domains, i.e., a trusted and an untrusted domain. However, providing only two instruction protection domains could be restrictive for some use cases (e.g., the combination of various protection mechanisms). Intuitively, we would not need 1024 instruction domains, even if we apply all the protection mechanisms proposed by a variety of the previous works into a single system. As a trade-off for the number of instruction domains, we utilize the 4 lower bits of the 10 unused bits in the PTE to store the instruction protection keys (ipkey). Accordingly, FlexFilt supports up to 16 instruction protection domains, where each domain filters target instructions in the domain's corresponding pages.

5.1.2 Flexible Filters. One of the main design goals of FlexFilt is providing **flexible** instruction filters, capable of filtering various target instructions. To achieve this goal, we design each filter in an inherently flexible way. We leverage a bit-granular match/mask mechanism, similar to the matching mechanism used in the prior work [16, 17]. This design choice enables us to filter one specific instruction or a group of instructions with one Flexible Filter. As an example, consider various branch instructions, including BEQ, BNE, BLT, BGE, BLTU, and BGEU, in the RISC-V ISA. These branch

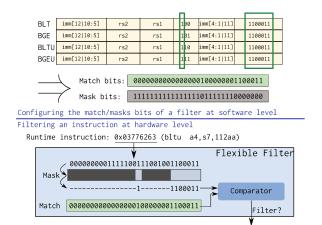

Figure 1: The Flexible Filter design, applied to a subset of RISC-V branch instructions.

instructions share the same opcode value (1100011) and they are distinguished based on the value of funct3 bits. In this scenario, a flexible bit-granular instruction filter offers the user the option of filtering a specific branch instruction, a subset of the branch instructions, or all of the above-mentioned branch instructions.

Consider a scenario where the user is interested in filtering four of the previously mentioned branch instructions, i.e., BLT, BGE, BLTU, BGEU. Figure 1 shows the format of these instructions. The common bits of these instructions, specified with a green box, can be used for identifying them. In this example, the uncommon bits are don't cares. Accordingly, the software developer can simply describe the four branch instructions using Match and Mask bits. The Match bits specify the 32-bit value of an instruction identified as one of the four branch instructions and the Mask bits specify the don't care bits. At the hardware level, our Flexible Filters enforce such a matching/masking approach (the bottom part of Figure 1). The control logic of the Mask acts like a filter that blocks the masked parts of an instruction (specified by 1 bits in the Mask and shown by dark gray color in Figure 1) and passes through the rest of the instruction bits (shown by transparent gray color in Figure 1). The output of this control logic, which contains the don't care bits, is passed into a comparator module to be compared with the Match. If these two values match, then the Flexible Filter activates an output signal, indicating that current instruction should be filtered. For additional information on the filtering capabilities of our Flexible Filters, refer to Appendix A.

As mentioned before, an instruction protection domain is a group of executable pages assigned with the same instruction protection key. Each instruction protection domain prevents the execution of various user-defined target instructions in its corresponding pages. Ideally, we are interested in a flexible feature capable of filtering any number of target instructions in each domain. In reality, providing such a capability is not practical due to resource limitations and the substantial area and power overheads induced by such excessive flexibility. With a limited number of instruction filters for each domain, we consider two design options. First, each instruction domain has a fixed number of dedicated instruction filters. Second, there is a fixed number of shared instruction filters, and each instruction domain can apply a combination of these shared filters to its corresponding pages. Although the first option provides

more flexibility in terms of filtering capabilities, it requires more hardware resources. Additionally, the instruction filter information for all the domains should be maintained by the OS during context switches. Considering the overheads involved with the first design option, we choose the second option in our design. We leave further investigation into the overheads involved in implementing the first design option as part of our future work.

By choosing the second design option, i.e., a fixed number of shared configurable instruction filters, the next design question we have to answer is the exact number of shared instruction filters. To choose the number of instruction filters, we examine the number of required filters in the previous works (listed in Table 1). Most of the previous works required to filter only one target instruction. In the worst case scenario, Fidelius [65] needed to filter the execution of three unique instruction types (five instructions in total). Considering the possibility of enforcing a combination of protection mechanisms, we choose to implement four shared instruction filters in our design. Subsequently, each instruction domain can be configured to apply a combination of the shared instruction filters.

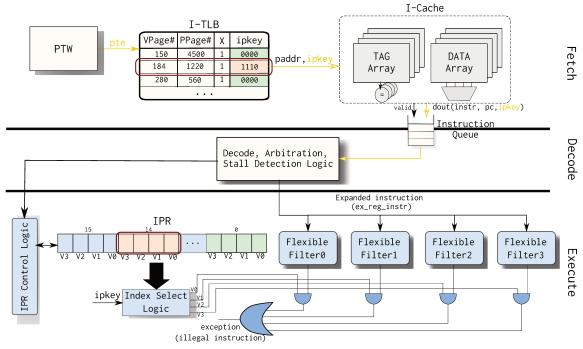

5.1.3 Microarchitecture Support. In our design, FlexFilt supports up to 16 instruction domains and provides four Flexible Filters, where a combination of these filters is applicable to each instruction domain. For each page, we specify the instruction domain by storing the ipkey in the 4 previously unused bits of PTE. For each instruction execution, in addition to checking the PTE permission bits (e.g., the X bit, which indicates that the page is executable), we need to determine if the instruction should be filtered. To this end, we first have to identify the corresponding domain of the instruction. At hardware level, the Instruction TLB (I-TLB) maintains the virtual to physical address translation of the instructions as well as their corresponding permission bits. We augment the I-TLB with a new field to store the associated ipkey of each virtual address. Whenever there is an I-TLB miss, the hardware Page Table Walker (PTW) walks the page table and fills the I-TLB with the missing information including the ipkey. As each instruction domain applies a combination of the Flexible Filters, we need to maintain the configured combination of each domain. To this end, for each domain, we associate a valid bit to each of the Flexible Filters. We store all the valid bits in a separate 64-bit register, called Instruction Protection Register (IPR).

Figure 2 demonstrates our modifications to the RISC-V Rocket core [3] to implement FlexFilt. The modified I-TLB stores the ipkey information (received from PTW) for each entry. On an I-TLB hit, the ipkey value gets transferred to the I-Cache (alongside the physical address) and subsequently on an I-Cache hit, the instruction and its associated ipkey gets stored in the Instruction Queue. Subsequently, the ipkey value gets transferred to the decode and then execute stage without any modifications. At the execute stage, FlexFilt uses the ipkey value to read the corresponding valid bits (4-bits) of the instruction domain from IPR. In the same cycle, each of the 4 Flexible Filters receives the 32-bit instruction in the execute stage, and performs the filtering operation based on its Match and Mask bits configuration (Figure 1). If the resulting filter signal of any of the Flexible Filters is high and at the same

$<sup>^2{\</sup>rm Note}$  that with four instruction filters we can filter all the target instructions in Fidelius [65] based on their instruction type.

Figure 2: Simplified overview of the modifications to the RISC-V Rocket core to support FlexFilt. The blue, yellow, and gray colors show the new, minimally modified, and unmodified components, respectively.

time its corresponding valid bit is active, then FlexFilt prevents the execution of the instruction by causing an illegal instruction exception.

5.1.4 Unprivileged vs Privileged Target Instructions. While Figure 2 shows the main components of FlexFilt to filter unprivileged instructions, this implementation does not take the privilege level of the instructions into account. As discussed in Section 2, some of the previous works focused on preventing the execution of target instructions in the kernel space while others focused on preventing the execution in user space. To filter instructions in user space, we simply access the priv field provided in the MStatus CSR of the Rocket core and only apply the Flexible Filters on user-level instructions. To filter the target instructions at kernel level, we use a similar approach as PMPs. We add two pairs of new CSRs to store the physical address range for filtering kernel-level instructions. To specify the kernel-level target instructions, we implement four dedicated Flexible Filters. These dedicated filters are only applicable to kernel-level instructions executing in the physical address range specified with our newly added CSRs. The abovementioned CSRs and dedicated filters can only be configured from the machine mode.

#### 5.2 OS support

FlexFilt is capable of filtering target instructions in OS-managed processes as well as the kernel itself. In our design, we consider scenarios where each user-space process can filter different target instructions. To enable a per-process instruction filtering capability, we need to provide the OS support for FlexFilt. In this section, we discuss the Linux kernel modifications to support FlexFilt.

5.2.1 Instruction Protection Keys. We implement our instruction protection keys on top of the existing support for memory protection keys. The Linux kernel provides three new system calls, i.e., pkey\_mprotect, pkey\_alloc, and pkey\_free, to support Intel MPK. pkey\_mprotect is an extension to mprotect system call. In addition to updating the permission bits of the PTEs of specified pages, pkey\_mprotect assigns a protection key to the PTE. pkey\_alloc and pkey\_free system calls enable a software developer to allocate and free a protection key, respectively. The kernel implements an allocation bitmap (16-bit for Intel MPK) to keep track of the allocated pkeys. The recent works on memory protection keys for RISC-V [14, 58] extend the Linux kernel support of memory protection keys to the RISC-V ISA. We modify the existing support for pkey\_alloc and pkey\_mprotect in the kernel to allocate an instruction protection key and associate the specified executable pages with an ipkey, respectively. We add a new flag to pkey\_alloc and pkey\_mprotect system calls to identify an instruction protection operation. Unlike the existing memory protection proposals on RISC-V, we only use 4 bits of the unused PTE bits to store our protection keys. Hence, we add an instruction allocation bitmap to keep track of 16 instruction protection domains.

5.2.2 Per Process OS Support. To enable a per process view for instruction protection domains, we maintain the domain information during context switches. We modify the task\_struct in the Linux kernel to keep the configuration of each Flexible Filter, which includes the Match and Mask bits. Additionally, we maintain the bitmap of allocated ipkeys as well as IPR contents. In Section 7, we discuss the overhead of maintaining FlexFilt information during context switches.

5.2.3 Kernel-Level Instruction Filtering Support. The kernel-level Flexible Filters and their corresponding physical address range

Table 2: FlexFilt's Application Programming Interface (API).

| Invoked            |  |

|--------------------|--|

| Custom Instruction |  |

| SETMATCH, SETMASK, |  |

| and SETPRIV        |  |

| WRIPR              |  |

|                    |  |

CSRs can only be configured from the machine mode. In the RISC-V environment, the Berkeley Boot Loader (BBL) [56] enables us to configure our kernel-level filters and their CSRs from the machine mode, prior to booting up the Linux kernel. As our kernel-level filters are applicable to all processes, we do not need to maintain their configuration during context switches.

## **5.3 Software Support**

For configuring FlexFilt, we leverage the standard RISC-V custom instruction extension to define new instructions. Table 2 shows our software API and the unprivileged custom instructions that each API invokes to configure FlexFilt. We provide the config\_filter function to configure each Flexible Filter by specifying its corresponding Match, Mask, and privilege bits. The software developer can leverage the config\_instr\_domain function to set the valid bit of a Flexible Filter for a specific instruction domain. We also provide five privileged custom instructions, which are accessible only at the supervisor level. We leverage these five instructions to maintain FlexFilt's information during context switches.

We leverage the pkey\_mprotect system call to associate a group of executable pages, specified by addr and len, with an ipkey. Multiple functions with non-contiguous address ranges can be assigned with the same ipkey and subsequently create one instruction domain. To invoke the pkey\_mprotect system call, we should obtain the address range of each instruction domain. In a deployed system, the software developer can annotate the source code to specify the sections of the program belonging to an instruction domain. Then, we can modify the loader to invoke pkey\_mprotect based on the extracted information from annotations. Rather than modifying the compiler and the loader, as a proof of concept, we leveraged LD\_PRELOAD. We leave the required modifications to the loader as part of our future work.

As an example, consider the scenario we described in Section 2. In this scenario, a software developer wants to allow the execution of WRPKRU instruction in two trusted functions (good\_code1 and good\_code2) while preventing the execution of WRPKRU in other parts of the code. To specify the trusted instruction domain, we first allocate a new ipkey (via pkey\_alloc system call). By assigning the same ipkey to both good\_code1 and good\_code2 functions, we associate them with the same trusted instruction domain, i.e., domain1. Then, we configure Flexible Filters to prevent the execution of the WRPKRU instruction in the default domain, i.e., domain0. To assign the allocated ipkey to the two trusted functions, we need to invoke the pkey\_mprotect system call, which requires the address and length of the trusted functions as input arguments. To this end, as a proof of concept, we mark the two trusted functions with an attribute in the source code and use a linker script to page align these functions. To obtain the address range of these two functions and invoke pkey\_mprotect, rather than modifying