# Low-Loss High-Density Inverse-Designed Structures for High Power Signal Routing on Integrated Silicon Photonics Foundry Platforms

Joel B. Slaby, Alec M. Hammond, and Stephen E. Ralph <sup>\*</sup>

*Georgia Institute of Technology, North Ave NW, Atlanta, GA 30332*

<sup>\*</sup> *stephen.ralph@ece.gatech.edu*

**Abstract:** We present inverse-designed compact multi-mode structures (bend, mode converter, and taper) for single-mode operation to enable low-loss, high power, and high-density signal routing with a demonstrated bend insertion loss of 0.48 dB on commercial foundry platforms. © 2022 The Author(s)

## 1. Introduction

Integrated photonic chip architectures continue scaling to higher component counts requiring more densely packed components with increasing functionality. Furthermore, many applications such as optical beamforming networks and photonic processing networks require densely packed arrays and high power low-loss photonic elements. While traditional analytical theory and simulations can produce efficient bends, they often require valuable chip real-estate and are often limited by the excitation of higher order modes [1]. Here we present and experimentally validate highly compact, inverse-designed, multimode structures with engineered mode profiles that minimize loss and support higher powers while ensuring higher order modes are suppressed.

## 2. Design and Simulation

Conventional integrated waveguide designs are limited by the single mode cutoff width. In contrast, inverse design enables us to use a wider multimode waveguide (and other routing structures) while retaining the necessary features of a single mode structure. Therefore, we chose a waveguide width of  $1\mu\text{m}$  to minimize the overlap of the fundamental  $\text{TE}_{00}$  mode with the waveguide-cladding interface. This results in lower loss from sidewall scattering, while increasing the power handling by reducing the peak intensity. However, wider waveguides introduce the challenge of higher order mode excitation. Thus, we designed devices using topology optimization to both route the fundamental mode  $\text{TE}_{00}$  while suppressing higher order modes (taper and bend) and convert between modes (mode converter).

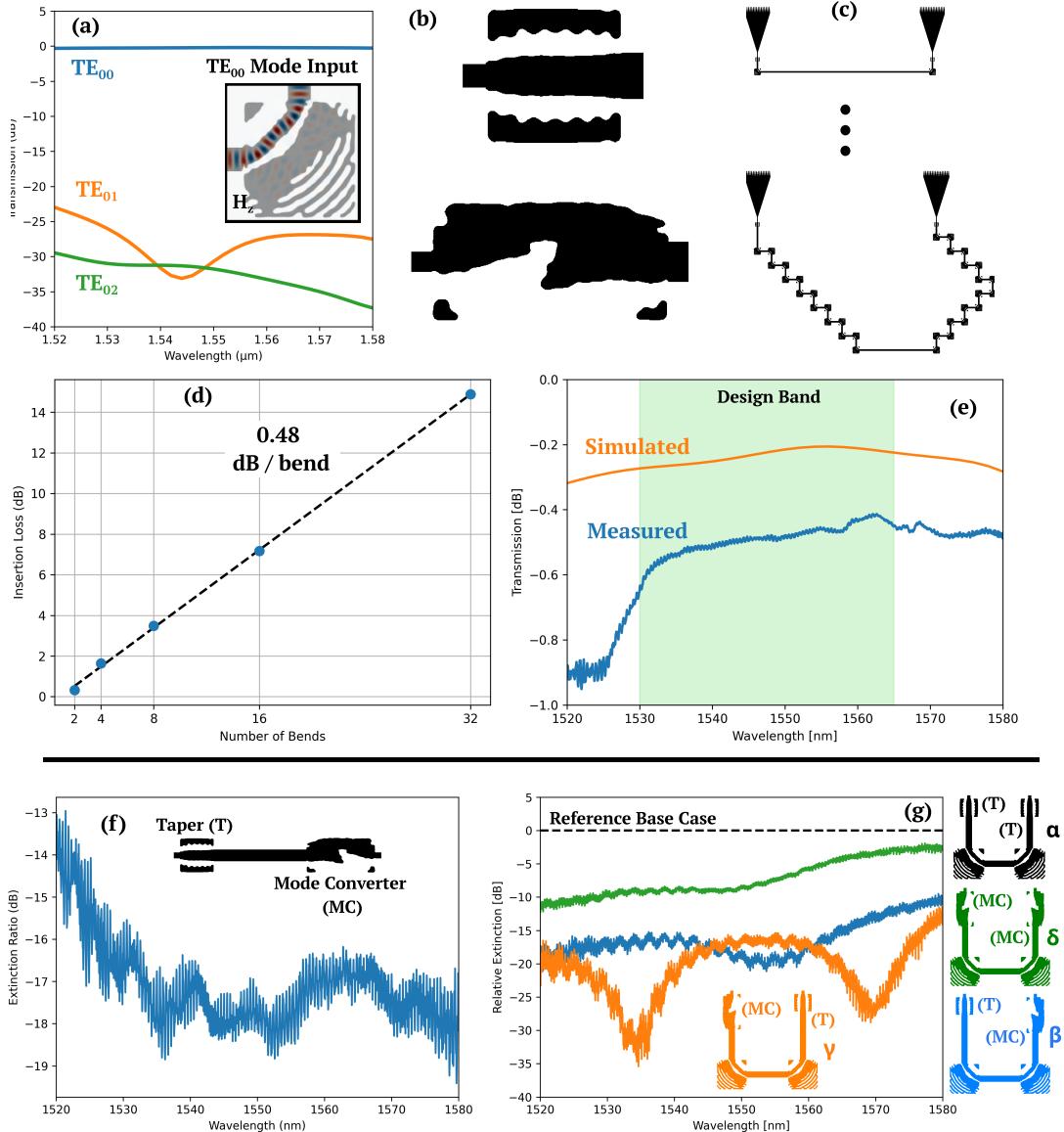

Topology optimization enables efficient gradient calculations of performance based objective functions with respect to millions of design parameters [2, 3]. In this case, we designed a bend that maximized the power transmission of the fundamental mode ( $\text{TE}_{00}$ ) across C-band (1530 to 1565 nm) restricted to a compact ( $5 \times 5\mu\text{m}$ ) design space, Fig. 1a. We separately designed compact tapers and mode converters to transition from the single mode waveguide to the multimode waveguide, Fig 1b. To design the taper, we maximized the power in the fundamental mode and therefore suppressed the power in the higher modes. The mode converter was optimized to efficiently couple from  $\text{TE}_{00}$  in a single mode waveguide to  $\text{TE}_{01}$  in a multimode waveguide. This mode converter is used to both taper to the multimode waveguide and to characterize the  $\text{TE}_{01}$  performance of the bend.

## 3. Experimental Results

The designs were fabricated on the GlobalFoundries 45CLO commercial foundry process [4]. The chips were characterized using a C+L band laser source and high-responsivity logarithmic photodiodes. A fiber array was aligned to grating couplers until maximum coupling was achieved at 1550 nm. Cascaded test structures were used to characterize the bend insertion loss, Fig. 1c. The linearized response was used to extract the loss of a single device, 0.48 dB per bend at 1550nm (Fig. 1d and across C-band (Fig. 1e). The experimental insertion loss is shown to be within 0.25dB of simulation which we attribute to surface roughness and fabrication variability.

Using the same cascaded device measurement technique, the compact tapers exhibited an insertion loss of less than 0.05 dB/device and the mode converter demonstrated an average of 1 dB/device of loss across C-band. Due to Lorentz reciprocity and the back-to-back insertion loss characterization method, it is not possible to determine the exact output mode power distribution given this setup. Instead, we estimate orthogonality of output modes

Fig. 1: Simulated TE<sub>00</sub> transmission through bend. (b) Taper (upper) and mode converter (lower). (c) Layout of cascaded bend structures for characterization. (d) Linearized insertion loss estimation. Extrapolated to 0.48 dB/bend. (e) Simulated vs. experimental measurement of bend transmission. (f) Extinction between taper (T) and mode converter (MC). (g) Bend extinction relative to the base case of 2 tapers and 2 bends. Each curve converts the input to TE<sub>00</sub> (T) or TE<sub>01</sub> (MC) and measures the corresponding output mode.

between the taper and mode converter by measuring a high extinction ratio, 18dB (Fig. 1f), between the two devices, confirming that the mode converter excites a higher order mode.

The modal transfer characteristics of the bend were then measured using combinations of the mode converter and the taper. As seen in Fig. 1g, the test structures are referenced to the base case  $\alpha$  (2 tapers) to measure the higher order mode excitation power penalty in the TO bend. The similarity between Fig 1f and the cases  $\beta$  (1 taper and 1 MC) and  $\gamma$  (1 MC and 1 taper) indicates minimal mode excitation from the bend. Finally, case  $\delta$  (2 MC) indicates  $\sim 10$  dB extinction of higher order modes in the bend.

## References

1. L. Chrostowski, *Silicon Photonics Design* (Cambridge University Press, 2015).

2. A. M. Hammond, et al., “High-performance hybrid time/frequency-domain topology optimization” *Opt. Express*, 2022.

3. A. F. Oskooi, et al. “MEEP” *Comput. Phys. Commun.* 181(3) (2010).

4. M. Rakowski, et al. “45nm CMOS” (OFC), 2020.