# Sub-Terahertz Devices and Test Metrology

Lei Li<sup>#1</sup>, Mohammad Javad Asadi<sup>^</sup>, Tianze Li<sup>\$</sup>, Xiaopeng Wang<sup>#</sup>, James C. M. Hwang<sup>#\$</sup>

<sup>#</sup>School of Electrical and Computer Engineering, <sup>\$</sup>Department of Material Science and Engineering

Cornell University, Ithaca, NY, USA

<sup>^</sup>Qualcomm Corp., Irvine, CA, USA

<sup>1</sup>ll886@cornell.edu

**Abstract**—As 6G wireless communications push the operation frequency above 110 GHz, it is critical to have low-loss interconnects that can be accurately tested. To this end, D-band (110 GHz to 170 GHz) substrate-integrated waveguides (SIWs) are designed on a 100- $\mu$ m-thick SiC substrate. The fabricated SIWs are probed on-wafer in a single sweep from 70 kHz to 220 GHz with their input/output transitioned to grounded coplanar waveguides (GCPWs). From CPW-probed scattering parameters, two-tier calibration is used to de-embed the SIW-GCPW transitions and to extract the intrinsic SIW characteristics. In general, the record low loss measured agrees with that obtained from finite-element full-wave electromagnetic simulation. For example, across the D band, the average insertion loss is approximately 0.2 dB/mm, which is several times better than that of coplanar or microstrip transmission lines fabricated on the same substrate. A 3-pole filter exhibits a 1-dB insertion loss at 135 GHz with 20-dB selectivity and 11% bandwidth, which is order-of-magnitude better than typical on-chip filters. These results underscore the potential of using SIWs to interconnect transistors, filters, antennas, and other circuit elements on the same monolithically integrated chip.

**Index Terms**—Calibration, millimeter wave integrated circuits, semiconductor waveguides, silicon carbide, transmission lines

## I. INTRODUCTION

CONVENTIONAL microwave monolithic integrated circuits (MMICs) are based on coplanar or microstrip transmission lines, which, at frequencies above 110 GHz, suffer from high loss, significant crosstalk, and limited power capacity. By contrast, substrate-integrated waveguides (SIWs) [1] have low loss, minimum crosstalk, and high power capacity. However, because the size of SIWs is on the order of the guided wavelength  $\lambda$ , SIWs are usually implemented at the board level for hybrid integration with active devices. Monolithic integration becomes feasible when the operation frequency exceeds 110 GHz, so that  $\lambda < 1$  mm in a typical semiconductor such as Si. In the case of high-power GaN-on-SiC MMICs, SIWs are especially attractive because SiC is high in dielectric constant, electrical resistivity, breakdown strength, mechanical toughness, and thermal conductivity, but low in loss tangent [2]–[5]. Table I compares these properties of SiC with those of Si and other substrate materials.

Table II shows that, despite the advantages of SIWs, to date there are few reports of SIWs above 110 GHz [6]–[12], whether

TABLE I

PROPERTIES OF COMMON SUBSTRATE MATERIALS

| Property                                 | Quartz    | Sapphire  | Si        | GaAs      | InP       | GaN       | AlN       | SiC       | Diamond   |

|------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Dielectric Constant                      | 3.8       | 10        | 12        | 13        | 9.6       | 8.9       | 8.5       | 9.7       | 5.7       |

| Loss Tangent                             | $10^{-4}$ | $10^{-4}$ | $10^{-4}$ | $10^{-4}$ | $10^{-3}$ | $10^{-4}$ | $10^{-4}$ | $10^{-4}$ | $10^{-4}$ |

| Resistivity ( $\Omega \cdot \text{cm}$ ) | $10^{20}$ | $10^{18}$ | $10^5$    | $10^5$    | $10^6$    | $10^5$    | $10^{14}$ | $10^5$    | $10^{13}$ |

| Breakdown Field (MV/cm)                  | 10        | 1         | 0.3       | 0.5       | 0.5       | 3         | 15        | 3         | 10        |

| Thermal Cond. (W/cm°C)                   | 0.05      | 0.4       | 1.3       | 0.5       | 0.7       | 2.5       | 3.4       | 4.2       | 100       |

| Thermal Exp. (ppm/°C)                    | 0.6       | 0.6       | 2.5       | 5.7       | 4.5       | 3.2       | 4.5       | 4.8       | 1         |

| Fracture Tough. (MPa·m <sup>0.5</sup> )  | 0.7       | 1.3       | 0.8       | 0.8       | 1.2       | 0.8       | 4.5       | 4.6       | 3.4       |

TABLE II

SUBSTRATE-INTEGRATED WAVEGUIDES ABOVE 110 GHz

| Year | Substrate | Bandwidth (GHz) | Insertion Loss (dB/mm) <sup>a,b</sup> | Return Loss (dB) <sup>a</sup> | Reference |

|------|-----------|-----------------|---------------------------------------|-------------------------------|-----------|

| 2010 | Si        | 95–200          | 4–6                                   | >14                           | [6]       |

| 2012 | Si        | 150–210         | 2–3                                   | >16                           | [7]       |

| 2017 | SiC       | 160–220         | 0.4–0.7                               |                               | [8]       |

| 2018 | Si        | 110–170         | 0.4–0.6                               | >14                           | [9]       |

| 2019 | SiC       | 150–220         | 0.5–1.2                               |                               | [10]      |

| 2020 | Si        | 243–325         | 0.4–1.0                               | >17                           | [11]      |

| 2021 | SiC       | 110–170         | 0.3±0.1                               | >17                           | [12]      |

| 2023 | SiC       | 110–170         | 0.4±0.1 <sup>c</sup>                  | >17                           | This Work |

<sup>a</sup>For the SIW in series with two SIW-GCPW transitions at its input/output

<sup>b</sup>Normalized by the total length of the SIW and two SIW-GCPW transitions

<sup>c</sup>0.2±0.1 dB/mm after transitions are de-embedded by two-tier calibration.

TABLE III

> 110 GHz FILTERS BASED ON SUBSTRATE-INTEGRATED WAVEGUIDES

| Year | Substrate | Freq. (GHz) | Bandwidth | Insertion Loss (dB) <sup>a</sup> | Return Loss (dB) <sup>a</sup> | Reference |

|------|-----------|-------------|-----------|----------------------------------|-------------------------------|-----------|

| 2020 | Si        | 279         | 1%        | 9                                | 20                            | [11]      |

| 2020 | Si        | 140, 280    | 1%        | 3.9, 2.5                         | 17, 11                        | [13]      |

| 2017 | SiC       | 183         | 5%        | ~1                               | 18                            | [8]       |

| 2021 | SiC       | 135         | 11%       | 1                                | 25                            | [12]      |

| 2023 | SiC       | 195.6       | 1.5%      | 5.6                              | 21.8                          | [14]      |

| 2023 | SiC       | 135         | 11%       | 1.0                              | 15                            | This Work |

<sup>a</sup>For the SIW plus two GCPW-SIW transitions

on Si or SiC. In this paper, we demonstrate D-band (110–170 GHz) SiC SIWs with an insertion loss of  $0.2 \pm 0.1$  dB/mm. Also fabricated on the same wafer is a 3-pole SIW filter with a 1.0-dB insertion loss at 135 GHz and an 11% 3-dB fractional

Fig. 1. (a) Front and back micrographs of a 1.1-mm-long D-band SIW in series with two 0.58-mm-long SIW-GCPW transitions at its input/output. (b) Composite layout of SIW calibration structures: "through," "line," and "reflect" [12].

bandwidth. This paper expands on [12] by including details about the SIW design, fabrication, characterization, and analysis. Optimization of the transition design is also discussed.

## II. DESIGN, FABRICATION, AND CHARACTERIZATION

### A. Design and Simulation

Using analytical equations [15] and finite-element full-wave electromagnetic simulations (HFSS), D-band SiC SIWs are designed and optimized for the fundamental  $TE_{10}$  mode with a cut-off below 100 GHz. Each SIW has two rows of through-substrate vias (TSVs) with diameter  $d = 40 \mu\text{m}$  and center-to-center spacing  $s = 100 \mu\text{m}$  [Fig. 1(a)]. The two TSV rows are parallel to each other with center-to-center spacing  $w = 520 \mu\text{m}$ . The simulated SIW characteristics are plotted together with the measured characteristics in section III.

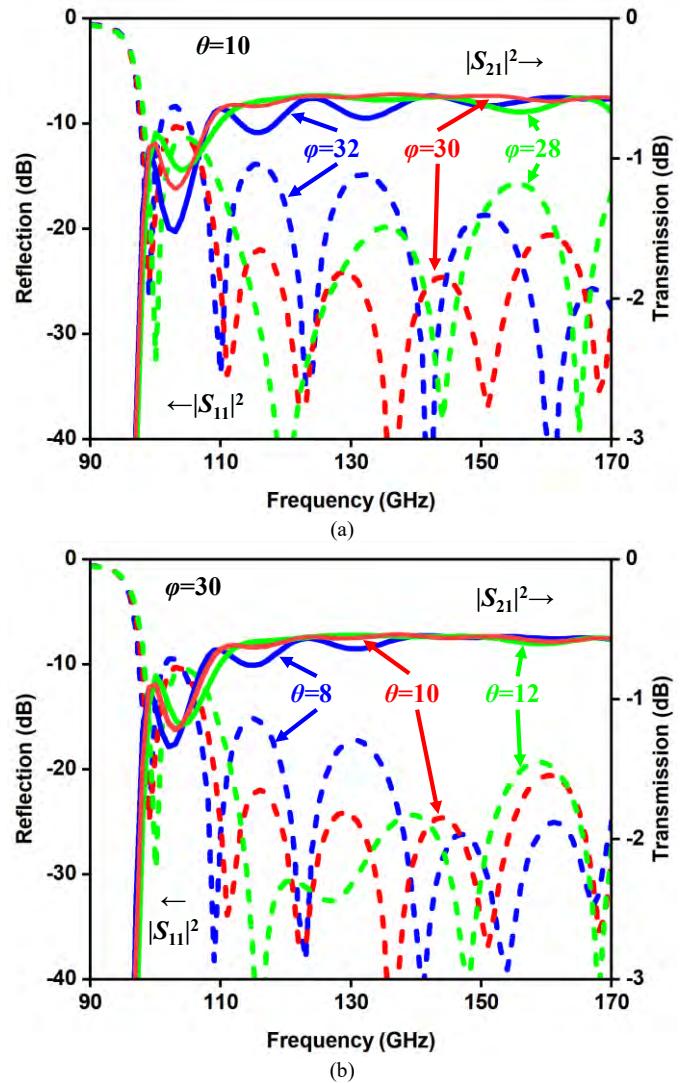

To facilitate wafer probing, each SIW is transitioned [16], [17] to a grounded coplanar waveguide (GCPW) [18] at both the input and output. Each transition is 578-μm long, including a 175-μm GCPW section, a 353-μm tapered section, and a 50-μm SIW section [Fig. 1(a)]. In the GCPW section, the center electrode is 30-μm wide with a 16-μm gap from the ground electrodes. In the tapered section, the center electrode is linearly widened to 155 μm while the gap is linearly widened to 158 μm, corresponding to  $\theta = 10^\circ$  and  $\varphi = 30^\circ$  for the inner and outer tapers, respectively, of the gap. Fig. 2 illustrates the effects of  $\theta$  and  $\varphi$  on the characteristics of a 1.1-mm-long SIW in series with two SIW-GCPW transitions at its input/output. It can be seen that deviations from optimum  $\theta$  and  $\varphi$  increase the ripples in the reflection and transmission coefficients  $S_{11}$  and  $S_{21}$ , thereby compromising the return loss while aggravating the insertion loss across the band. Further, the effect of  $\Delta\varphi$  is more prominent than that of  $\Delta\theta$ . Therefore, iterative optimization of  $\theta$  and  $\varphi$  starts with  $\varphi$  first. Note that with fixed  $w$  and  $\varphi$ , the length of the tapered section is approximately  $(w/2) \cdot \cotan \varphi$ .

To extract the intrinsic SIW characteristics from those measured on the GCPW-SIW-GCPW series, through-reflect-line (TRL) calibration structures [19] are laid out [Fig. 1(b)] and fabricated on the same SiC substrate as the SIWs. Composite layouts, overlapping frontside and backside features, are shown in Fig. 1(b) because they reveal more details than separate frontside and backside micrographs as shown in Fig. 1(a).

Fig. 2. Simulated effects of (a) the inner taper  $\theta$  and (b) outer taper  $\varphi$  on  $S_{11}$  (dash) and  $S_{21}$  (solid) of the GCPW-SIW-GCPW series of Fig. 1(a).

### B. Fabrication

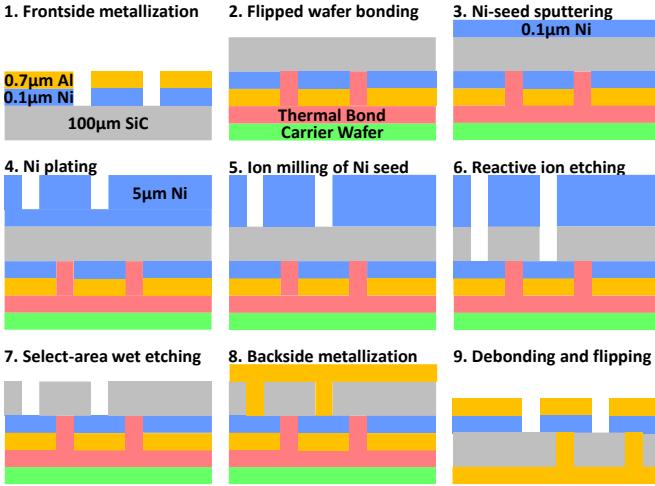

Fig. 3 illustrates the SIW fabrication sequence. The fabrication starts with a 100-mm-diameter, 100-μm-thick high-purity 4H-SiC substrate having  $> 10^6 \Omega\cdot\text{cm}$  resistivity. For frontside processing, the Si face of the substrate is patterned with 100-nm-thick Ni and 700-nm-thick Al, both electron-beam evaporated. The total metal thickness is three times the skin depth at 140 GHz. For backside processing, the substrate is flip-mounted on a sapphire carrier using a thermal bond. A 100-nm-thick Ni seed layer is sputter-deposited, then patterned with a 7-μm-thick photoresist layer before a 5-μm-thick Ni layer is electroplated. This electroplated Ni layer serves as the mask for TSV etching. Before TSV etching, the photoresist layer is removed by solvents and the Ni seed layer is removed by ion milling. After TSV etching, the Ni mask is wet-etched, and a 100-nm-thick Ni adhesion layer and 2-μm-thick Al layer are sputter-deposited. Finally, the SiC substrate is debonded and cleaned.

Fig. 3. Schematic illustration of the SIW fabrication sequence.

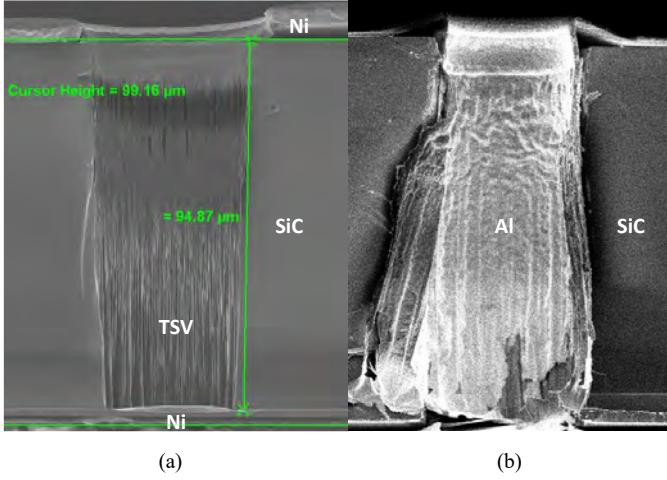

Fig. 4. Scanning electron micrograph of a TSV cross-section after (a) etching away 95- $\mu$ m SiC and (b) complete etching through the SiC and backside metallization.

TSV etching is the most challenging step in SIW fabrication. TSVs are etched in an Oxford Cobra inductively-coupled-plasma (ICP) reactive-ion etcher (RIE) with 50 sccm SF<sub>6</sub> and 10 sccm O<sub>2</sub> under 10 mTorr vacuum, 2000-W ICP power, and 50-W RIE power. The etch rate of SiC is approximately 15  $\mu$ m/h with a 50:1 selectivity over Ni. Fig. 4(a) shows a uniform etch front after etching away 95  $\mu$ m of SiC and just before it reaches the frontside metal. Fig. 4(b) shows the TSV cross-section after completing SiC etching and backside metallization. It can be seen that the TSV sidewall is well covered by Al. The jagged appearance is caused by mechanical cleaving. Macroscopically, it can be seen in Fig. 1(a) that the TSVs are uniform with high yield.

### C. Characterization

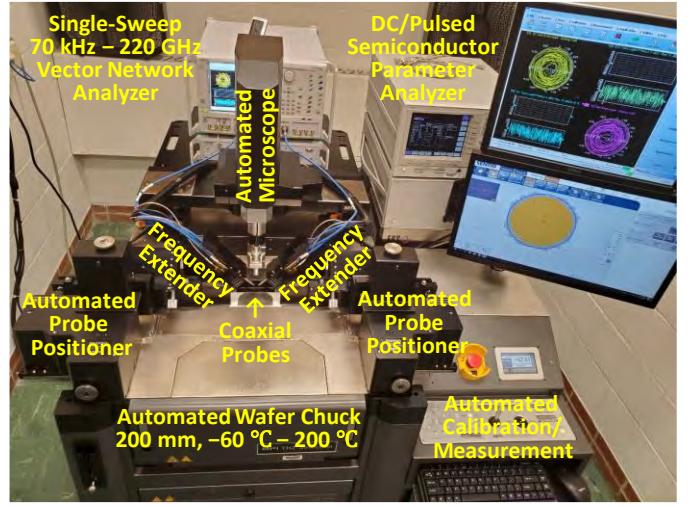

Fig. 5 shows that the measurement setup comprises an Anritsu ME7838G 70-kHz-to-220-GHz single-sweep VNA, an MPI TS2000-IFE automated probe station, two 220-GHz 0.6-mm-dia coaxial probes with 50- $\mu$ m pitches. A two-tier calibration is applied sequentially. Tier-1 calibration establishes the reference planes at the probe tips, using the load-

Fig. 5. Measurement setup.

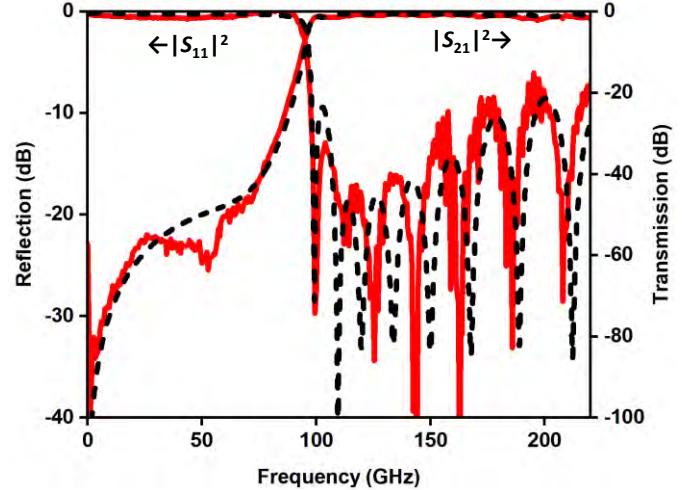

Fig. 6. Measured (solid) vs. simulated (dash) magnitudes of  $S_{11}$  and  $S_{21}$  of the GCPW-SIW-GCPW series with optimized SIW-GCPW transitions.

reflect-reflect-match (LRRM) method [20] and an MPI TCS-050-100-W impedance standard substrate. Tier-2 calibration shifts the reference planes beyond the SIW-GCPW transitions to the intrinsic SIW section, using the TRL method and the calibration structures shown in Fig. 1(b).

## III. RESULTS AND DISCUSSION

### A. GCPW-SIW-GCPW Series

Fig. 6 compares the measured  $S_{11}$  and  $S_{21}$  (after tier-1 calibration with the reference planes at the probe tips) of a GCPW-SIW-GCPW series with a total length of 2.26 mm ( $S_{22}$  and  $S_{12}$  are comparable to  $S_{11}$  and  $S_{21}$ , respectively, and not shown). It can be seen that the measured and simulated results agree across the entire 220-GHz bandwidth, even when the insertion loss approaches 100 dB. Across the D band, the measured return loss is greater than 17 dB, confirming that both the SIW and the SIW-GCPW transition are broadband. The measured insertion loss of  $0.80 \pm 0.13$  dB corresponds to

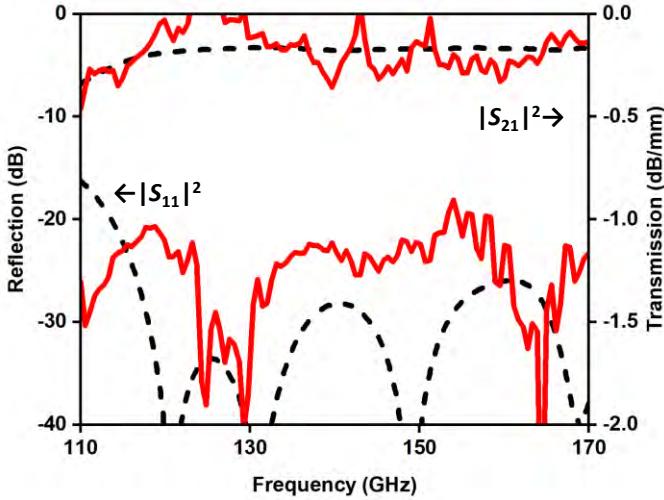

Fig. 7. Measured (solid) vs. simulated (dash) magnitudes of  $S_{11}$  and  $S_{21}$  of the 1.1-mm-long intrinsic SIW section.

approximately  $0.4 \pm 0.1$  dB/mm when normalized by the total length of the SIW and the two SIW-GCPW transitions. (Table II data, including those of [6]–[12], all include one SIW and two SIW-GCPW transitions in the loss and length). The insertion loss reported here is higher than [12]. This can be attributed to the degradation of the probe pads on the SIW-GCPW transition, as the relatively thin ( $0.7\text{-}\mu\text{m}$  Al) pads are repeatedly probed (confirmed in the next subsection). Indeed, it is found that the SIW-GCPW transition has  $0.3 \pm 0.1$  dB insertion loss [21], which is 0.1 dB higher than that reported in [12]. Note that in this work we have repeated all measurements on the same SIW die, to avoid any additional uncertainty from die-to-die variation.

### B. Intrinsic SIW Section

Fig. 7 compares the measured and simulated  $S_{11}$  and  $S_{21}$  (after tier-2 calibration and with the reference planes beyond the SIW-GCPW transitions) of the 1.1-mm-long intrinsic SIW section. Across the D band, the return loss is greater than 17 dB and the average insertion loss is approximately  $0.2 \pm 0.1$  dB/mm, much lower than the value with the SIW-GCPW transitions included. For such a low loss, the data is inevitably noisy. Additionally, parasitic modes launched by the CPW probe onto the SIW-GCPW transition may not completely dissipate before reaching the intrinsic SIW section. This can be alleviated by lengthening the GCPW section of the transition beyond 175  $\mu\text{m}$ , with the tradeoff of larger size and higher loss.

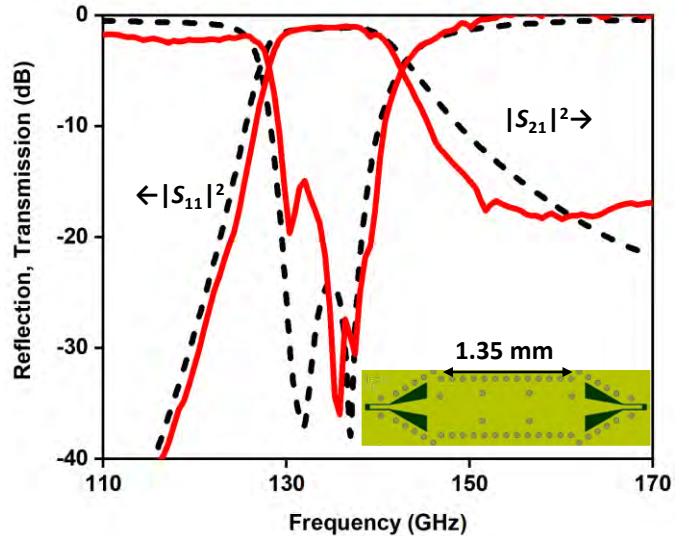

### C. SIW Filter

Fig. 8 compares the measured and simulated magnitudes of  $S_{11}$  and  $S_{21}$  for a three-pole filter comprising a 1.35-mm-long SIW and two GCPW-SIW transitions. It can be seen that the measured results agree with that simulated by using a dielectric constant of 10.2 for SiC [22], [23]. The measured insertion and return losses are 1.0 dB and 15 dB, respectively, at the band center of 135 GHz. The 3-dB bandwidth is 15 GHz or 11%. The out-of-band rejection is greater than 40 dB and 20 dB below and above, respectively. These characteristics are consistent with the high-Q resonators and represent the state of the art of SiC SIW filters (Table III) [12]. They are order-of-magnitude better

Fig. 8. Measured (solid) vs. simulated (dash) magnitudes of  $S_{11}$  and  $S_{21}$  for a three-pole SIW filter.

than that of Si on-chip filters. The rejection below band takes advantage of the SIW cut-off characteristics. The rejection above band can be improved by suppressing higher-order modes.

## IV. CONCLUSION

With a broadband, relatively short, and low-loss SIW-GCPW transition, the D-band SiC SIW exhibits a record-low loss of approximately 0.2 dB/mm. The three-pole filter, with an insertion loss of 1.0 dB, represents the state of the art of SiC SIW filters and is order-of-magnitude better than Si on-chip filters. This shows that above 110 GHz, SiC SIWs may be small enough to replace coplanar or microstrip transmission lines as interconnects for high-power MMICs. Additionally, SiC SIW may enable monolithic integration of high-quality filters and edge-firing antennas on the same chip, which has been challenging for MMICs at any frequency. These SIW-based MMICs can in turn form a linear RF frontend array on a single SiC chip with  $\lambda_0/2$  pitch, because  $\lambda_{TE10} \approx \lambda_0/3$  on SiC and there is little crosstalk between adjacent SIWs.

## V. ACKNOWLEDGEMENT

This work was supported in part by the U.S. National Science Foundation (NSF) under Grant Nos. ECCS-2117305, and ECCS-2122323, the U.S. Office of Naval Research under Grant No. N00014-21-1-2680, as well as the Semiconductor Research Corporation, and the U.S. Defense Advanced Research Projects Agency through the Joint University Microelectronics Program. This work was performed in part at the Cornell NanoScale Facility, an NNCI member supported by NSF Grant No. NNCI-2025233.

## REFERENCES

- [1] K. Wu, M. Bozzi, and N. J. G. Fonseca, "Substrate integrated transmission lines: Review and applications," *IEEE J. Microw.*, vol. 1, no. 1, pp. 345–363, Jan. 2021.

- [2] G. L. Harris, *Properties of Silicon Carbide*, London, UK: INSPEC, 1995.

- [3] S. Chen, M. N. Afsar, and D. Sakdatorn, "Dielectric-parameter measurements of SiC at millimeter and submillimeter wavelengths," *IEEE Trans. Instrum. Meas.*, vol. 57, no. 4, pp. 706–715, Apr. 2008.

- [4] C. R. Jones, J. Dutta, G. Yu, and Y. Gao, "Measurement of dielectric properties for low-loss materials at millimeter wavelengths," *J. Infrared. Milli. Terahz. Waves*, vol. 32, no. 6, pp. 838–847, Jun. 2011.

- [5] C. Liu, D. Yu, D. W. Kirk, and Y. Xu, "Electromagnetic wave absorption of silicon carbide based materials," *RCS Adv.*, vol. 7, no. 2, pp. 595–605, Jan. 2017.

- [6] S. Hu, Y.-Z. Xiong, J. Shi, L. Wang, B. Zhang, D. Zhao, T. G. Lim, and X. Yuan, "THz-wave propagation characteristics of TSV-based transmission lines and interconnects," in *Proc. IEEE Electron. Compon. Technol. Conf.*, 2010, pp. 46–50.

- [7] H. J. Tang, G. Q. Yang, J. X. Chen, W. Hong, and K. Wu, "Millimeter-wave and terahertz transmission loss of CMOS process-based substrate integrated waveguide," in *IEEE MTT-S Int. Microw. Symp. (IMS) Dig.*, Montreal, Canada, Jun. 2012, pp. 17–22.

- [8] Y. Li, L.-A. Yang, H. Zou, H.-S. Zhang, X.-H. Ma, and Y. Hao, "Substrate integrated waveguide structural transmission line and filter on silicon carbide substrate," *IEEE Electron Device Lett.*, vol. 38, no. 9, pp. 1290–1293, Sep. 2017.

- [9] M. Bertrand, E. Pistono, G. Acri, D. Kaddour, F. Podevin, V. Puyal, S. T. Wipf, C. Wipf, M. Wietstruk, M. Kaynak, and P. Ferrari, "Substrate integrated waveguides for mm-wave functionalized silicon interposer," in *IEEE MTT-S Int. Microw. Symp. Dig.*, 2018, pp. 875–878.

- [10] Y. Li, X.-H. Ma, L.-A. Yang, J.-P. Ao, and Y. Hao, "Terahertz monolithic integrated waveguide transmission lines based on wide bandgap semiconductor materials," *J. Appl. Phys.*, vol. 125, no. 15, pp. 151616-1–151616-7, Apr. 2019.

- [11] A. Krivovitca, U. Shah, O. Glubokov, and J. Oberhammer, "Micromachined silicon-core substrate-integrated waveguides at 220–330 GHz," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 12, pp. 5123–5131, Dec. 2020.

- [12] M. J. Asadi, L. Li, W. Zhao, K. Nomoto, P. Fay, H. G. Xing, D. Jena, and J. C. M. Hwang, "Substrate-integrated waveguides for monolithic integrated circuits above 110 GHz," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Atlanta, GA, Jun. 2021, pp. 669–672.

- [13] G. Prigent, A. -L. Franc, M. Wietstruk, and M. Kaynak, "Substrate integrated waveguide bandpass filters implemented on silicon interposer for terahertz applications," in *IEEE MTT-S Int. Microw. Symp.*, 2020, pp. 595–598.

- [14] Y. Liu, L. -A. Yang, Y. Li, S. Liu, Y. Chen, X. Zhang, X. Ma, and Y. Hao, "Terahertz monolithic integrated narrow-band filter based on the silicon carbide substrate," *Semicond. Sci. Technol.*, vol. 38, no. 1, p. 035002, Jan. 2023.

- [15] F. Xu and K. Wu, "Guided-wave and leakage characteristics of substrate integrated waveguide," *IEEE Trans. Microw. Theory Techn.*, vol. 53, no. 1, pp. 66–73, Jan. 2005.

- [16] R. Kazemi, A. E. Fathy, S. Yang, and R. A. Sadeghzadeh, "Development of an ultra wide band GCPW to SIW transition," in *Proc. Radio Wireless Symp. (RWS)*, Santa Clara, CA, Jan. 2012, pp. 171–174.

- [17] B. Krishnan and S. Raghavan, "A review on substrate integrated waveguide transitions," in *TEQIP III Sponsored Int. Conf. Microw. Integr. Circuits, Photonics Wireless Networks (IMICPW)*, Tiruchirappalli, India, May 2019, pp. 424–428.

- [18] Y. C. Shih and T. Itoh, "Analysis of conductor-backed coplanar waveguide," *Electron. Lett.*, vol. 18, no. 12, pp. 538–540, Jun. 1982.

- [19] R. B. Marks, "A multiline method of network analyzer calibration," *IEEE Trans. Microw. Theory Techn.*, vol. 39, no. 7, pp. 1205–1215, Jul. 1991.

- [20] A. Davidson, K. Jones, and E. Strid, "LRM and LRRM calibrations with automatic determination of load inductance," in *ARFTG Conf. Dig.*, Monterrey, CA, Nov. 1990, pp. 57–63.

- [21] L. Li, S. Reyes, M. J. Asadi, W. Zhao, P. Fay, D. Jena, H. G. Xing, and J. C. M. Hwang, "Single-sweep vs. banded characterizations of a D-band ultra-low-loss SiC substrate integrated waveguide," in *ARFTG Microw. Meas. Conf.*, Denver, CO, USA, Jun. 2022.

- [22] L. Li, S. Reyes, M. J. Asadi, X. Wang, G. Fabi, E. Ozdemir, W. Wu, P. Fay, and J. C. M. Hwang, "Extraordinary permittivity characterization using 4H-SiC substrate-integrated waveguide resonators," in *ARFTG Microw. Meas. Symp.*, Las Vegas, NV, USA, Jan. 2023, pp. 1–4.

- [23] L. Li, S. Reyes, M. Javad Asadi, P. Fay, and J. C. M. Hwang, "Extraordinary permittivity characterization of 4H SiC at millimeter-wave frequencies," *Appl. Phys. Lett.* DOI: 10.1063/5.0148623.