# METHODOLOGIES, ARCHITECTURES, AND PROTOTYPES FOR SCALING ON- AND OFF-CHIP INTERCONNECTS

#### A Dissertation

Presented to the Faculty of the Graduate School

of Cornell University

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

by Yanghui Ou November 2024 © 2024 Yanghui Ou ALL RIGHTS RESERVED

# METHODOLOGIES, ARCHITECTURES, AND PROTOTYPES FOR SCALING ON- AND OFF-CHIP INTERCONNECTS

Yanghui Ou, Ph.D. Cornell University 2024

The slowdown of Moore's Law and the end of Dennard scaling have driven modern computing systems to embrace parallelism, both within single chips and across multiple compute devices, in order to meet the growing computational demands. Efficient data movement, both on-chip and off-chip, has thus become increasingly critical. However, scaling on- and off-chip interconnects each presents unique challenges in both methodology and architecture. For on-chip interconnects, challenges include: (1) the methodology challenge of developing a robust framework to model, test, and evaluate on-chip network (OCN) designs across a vast design space, and (2) the architecture challenge of bridging the gap between theoretical advances and practical implementation of scalable, low-diameter OCN topologies. For off-chip interconnects, challenges include: (1) the methodology challenge of modeling large-scale distributed systems accurately, and (2) the architecture challenge of breaking the capacity, latency, and bandwidth trade-offs inherent in current off-chip interconnect technologies. This thesis addresses these challenges by developing new methodologies, proposing architectural solutions, and validating their feasibility through practical silicon prototypes.

The first part of this thesis focuses on OCNs for manycore architectures. I first present Py-OCN, a unified Python-based framework for modeling, testing, and evaluating on-chip networks, which vertically integrates multiple research methodologies and enables productive design space exploration of OCNs. Next, I propose practical low-diameter OCN topologies that can be effectively implemented with a tiled physical design methodology, bridging the gap between principle and practice. Finally, the CIFER chip tape-out demonstrates the feasibility and effectiveness of PyOCN as well as the tiled physical design approach.

The second part of the thesis addresses challenges in scaling off-chip interconnects, particularly for machine learning workloads. I first present LLMCompass-E2E, a comprehensive framework for modeling large-scale distributed LLM training performance. I then explore the po-

tential of emerging co-packaged silicon photonic interconnects by proposing an optically connected multi-stack HBM module which can effectively break the trade-off between memory bandwidth and capacity. Lastly, the PIPES chip tape-out demonstrates a practical implementation of such co-packaged silicon photonic interconnects, highlighting their potential for scalable, high-performance interconnect solutions in large-scale distributed systems.

#### **BIOGRAPHICAL SKETCH**

Yanghui Ou was born on April 23, 1995 to Hongmei Yang and Shaojia Ou. At a young age, Yanghui's greatest passion was actually basketball. He dreamed of becoming the next big basketball star, starting his journey with the school team in elementary school. Little did he know, his true calling would not involve slam dunks but rather solving bugs. During his time at Beijing No. 171 High School, Yanghui first learned about Java and was fascinated by the idea of solving problems with code. He managed to juggle playing in the school basketball team and being a dedicated member of the school's robotics club. Obviously not talented enough for the NBA, Yanghui decided to pursue a career in technology.

Yanghui's high school years were a rollercoaster of ups and downs. Before the college entrance exam, he only listed one university on his application, refusing to consider any alternatives. Unfortunately, his score fell short. He accepted the failure and returned to high school to attend the senior year again. Doubt crept in throughout the year as he sometimes performed worse than the previous year in practice exams, but he gritted his teeth and pushed through. On exam day, Yanghui was in the zone, channeling everything he had learned. This time, he scored high enough to choose any university. He decided to take an adventure far away from home, going all the way south and attending the Hong Kong University of Science and Technology.

Yanghui cherished the beautiful scenery and vibrant campus life at HKUST. Other than winning the championship of the undergraduate basketball league for mainland students with his awesome teammates and coaches, he also found his passion for computer architecture. In fall 2016, he participated in an exchange program at Cornell University, where he took the world's best computer architecture course taught by Prof. Christopher Batten. It was at that time that he decided to pursue a PhD career in computer architecture.

In 2018, Yanghui fulfilled his dream of joining the PhD program at Cornell University. He joined Prof. Christopher Batten's group without hesitation. In the next six years, he expanded his knowledge on various aspects of computer architecture and contributed to many projects, ranging from methodologies to silicon prototypes. Beyond technical expertise, he also learned how to conduct good research and witnessed exemplary leadership from his advisor.

Yanghui is deeply grateful for his PhD experience at Cornell University, a period of invaluable professional and personal growth, guided by an exceptional advisor and accompanied by many good friends.

#### **ACKNOWLEDGEMENTS**

My PhD journey has been a mix of joyful moments and challenges. I am grateful to many individuals who have supported, encouraged, and guided me along the way.

First of all, I cannot express enough gratitude to my advisor, Prof. Christopher Batten. His computer architecture course was the spark that inspired me to pursue a PhD in this field. To this day, I can still vividly recall the six key concepts for advanced computer architecture that we repeated before each class. Beyond the countless brainstorming sessions that fueled my research, Chris has also helped me grow in many other ways throughout my PhD. Chris made me a better communicator through his honest and constructive feedback. He constantly encouraged me to step up, talk to people and grow my professional network. Chris taught me the value of open and honest communication, never pretending to understand and nodding my head but instead asking questions, no matter how simple or stupid they might seem. He instilled in me an appreciation for details, such as writing well-formatted code, thoroughly unit testing my own design, and maintaining consistency and clarity in my writing. From him, I learned how to make good slides, how to deliver compelling presentations, how to create clear and effective figures, how to write well-crafted papers, and how to be a good teacher. His mentorship has left an indelible mark on both my professional and personal growth.

I am also immensely thankful to all my PhD friends in the Batten Research Group (BRG) for their support and collaboration. I have learned a great deal from each of you, both professionally and personally. I would like to thank Christopher Torng, who not only taught me a lot about ASIC flow and VLSI but also shared many useful terminal and Vim tricks, arguably the most important survival skills for any PhD student. I joined the group just as Berkin Ilbeyi was about to graduate. but I still learned the concept of JIT and Python acceleration techniques from his impressive work and his paper presentation in our social reading group. Moyang Wang, your expertise in work-stealing runtime and software-centric cache coherence impresses me as much as your skiing and snowboarding skills. I will always treasure the memory of us snowboarding through the woods at Greek Peak and ended up rolling on the ground together. Shunning Jiang, you were a fantastic mentor, and our collaboration on the PyMTL3 project was one of the highlights of my PhD. I will never forget the night when the whole group were crammed in Chris' hotel room, working together before the day of our PyMTL3 tutorial at FCRC'19. Khalid Al-Hawaj, thank you for teaching me gem5 and for your jokes that always lifted my spirits. Tuan Ta, thank you too for showing me

how to hack gem5 and for introducing me to badminton. Lin Cheng, your lessons on memory consistency and cache coherence were invaluable, and so were the board game nights at your place. And thank you for dragging me to Greek Peak to learn snowboarding together. I still recall the day when we finally figured out how to properly make an S-turn and conquered the green track without crashing. Peitian Pan, your work ethic is truly inspiring and I really enjoyed working with you. I am still proud of our epic final project for the HLS course and our snoopy-based cache coherent memory system for the ASIC course. Nick Cebry, you are an amazing friend. Our snowboarding trips to Greek Peak were some of the best times of my PhD. I will never forget the semester when we were the only two BRG members left in Ithaca. I wish you the best for the rest of your PhD journey. Derin Ozturk, though our overlap was brief, it was refreshing to have your robotics expertise add a new dimension to our group. Elton Shih and Niklas Schmelzle, it was a pleasure to finally see some new faces in the group. The future of BRG is in your hands and I am excited to see where you take it. Max Doblas, thank you for visiting our group from Barcelona Supercomputing Center. Your work on genomics was amazing. I was also fortunate to work with three amazing postdoc researchers in BRG. Cheng Tan, thank you for leading the PyOCN paper and for creating a compiler for the UE-CGRA that spared me from manually mapping the kernels on the whiteboard. Thank you for taking me to the gym and teaching me how to build muscle. Shady Agwa, you were always willing to help and thank you for teaching me about SRAM compilers and floorplanning. Austin Rovinski, you were such a physical design wizard and the PIPES project would have been impossible without your help. I will never forget our sleepless nights before the tape-out deadline. I also learned so much about VLSI and open-source EDA from you. I wish you a successful career as a professor and a thriving REALISE lab, or whatever even more creative name you may come up with next.

The Computer Systems Laboratory (CSL) has been a supportive and caring community and I am grateful for my CLS mentors, friends, and colleagues. I would also like to thank Prof. Zhiru Zhang and Prof. Adrian Sampson, for agreeing to be on my committee and providing invaluable insights and feedback on my research. I would also like to thank my fellow PhD friends at CSL. A special mention goes to Zhuangzhuang Zhou, who was also my neighbor in Warrenwood Apartments for almost five years. Thank you for cooking me delicious food and for sharing your stories with me. Weizhe Hua, you will always be my tennis coach and thank you for teaching me how to play tennis. Yi Jiang, thank you for making so many delicious cakes and cookies for the gatherings

at Lin's place. Philip Bedoukian, your cheerful energy never failed to brighten my day. Yanqi Zhang, Yichi Zhang, and Chenhui Deng, thank you for bringing me, a complete badminton newbie, to your pro badminton party and teaching me how to play. I am also grateful for the friendship and inspiring conversations of many other CSL researchers: Ritchie Zhao, Mulong Luo, Kailin Yang, Mingyu Liang, Hanchen Jin, Zichao Yue, Jie Liu, Yixiao Du, and Niansong Zhang.

I would like to thank Prof. David Wentzlaff and the exceptional researchers in his research group for their collaboration on the CIFER project, the optically connected HBM project, and the LLMCompass-E2E project. I am especially grateful to Jonathan Balkind for teaching me about OpenPiton and how to hack the framework. I appreciate Ang Li and Fei Gao for their insightful feedback and advice on the OCN design for CIFER. To the rest of the CIFER team, thank you for your hard work and dedication in making the tape-out a success. A special callout goes to Hengrui Zhang for our productive collaboration on the optically connected HBM project, and the LLMCompass-E2E project. We had so many inspiring discussions and I learned a lot from him about GPU architecture and LLM workloads. Similar thanks go to August Ning and Rohan Prabhakar for our engaging discussions about LLMCompass and LLM training. I learned a lot from your perspectives and expertise.

I would like to express my gratitude to my PIPES teammates. First, I would like to thank my collaborators at Intel. Kaveh Hosseini and Tim Tri Hoang led the PIPES project and I am grateful for their feedback and guidance. Sung-Gun Cho offered tremendous support on the ASIC flow, and meeting the deadline would not have been possible without his help. Ching-Chi Chang helped a lot on pre-silicon verification and AIB debugging. I am also grateful to Prof. Alyosha Molnar and his team, especially Christine Ou, Devesh Khilwani, and Sunwoo Lee, for their collaboration on the TRX integration. My sincere thanks also go to Prof. Keren Bergman and her team for their work on the PIC and the final end-to-end demo. I am particularly thankful to Songli Wang and Yuyang Wang for their generosity in hosting me at Columbia University and for teaching me so much about silicon photonics.

I would like to thank all the other mentors who have inspired and guided me throughout my journey. I thank Prof. Jiang Xu and Prof. Wei Zhang for their inspiring courses at HKUST. Prof. Wei Zhang also supervised my undergraduate final-year project and taught me a lot about FPGA and hardware accelerators. I thank Prof. Hoi-Sing Kwok for supervising some of my undergraduate research projects. Though I did not end up pursuing a career in display technologies,

I explored many interesting topics and broadened my perspective under his guidance. I thank Prof. Charles Sodini for hosting me as a visiting student at MIT for a summer research program. I thank Mr. Jianpeng Qin, my high school English teacher, whose encouragement and guidance helped me persevere through my lowest moments.

I would like to thank all my undergraduate friends and high school friends who, despite being scattered all around the world, have remained a constant source of support and joy. A special thanks to my friend at Hong Kong, Yunhao Feng. Thank you for playing hundreds of hours of Valheim, Satisfactory, and particularly Factorio with me, which turned me into a master of train networks and interstellar logistics, adding a new dimension to my engineering skill set. I would also like to thank Xiangju Chen, Xuanyin Xian, and Zepu Sun for their enduring friendship. Guangyu He, thank you for coming to New York all the way from Germany to visit me and celebrate my birthday. I also appreciate the friendship of Linwei Zhang, Shiyu Li, Jiaziyu Lang, and Zhe Feng. Your thoughtful birthday wishes every year remind me how lucky I am to have such amazing friends.

Finally, I would like to thank my family for raising me up and supporting me unconditionally throughout my life. I look forward to going back home and spending more time with them. I also want to thank Yiran Hao for her support and companionship. Your presence has made my PhD journey brighter and more worthwhile. Special thanks to the true co-author of all my work, my cat, MianMian, for her loyal company during countless late nights. Her emotional support has been a constant source of comfort and strength.

In terms of funding, this thesis was supported in part by DARPA POSH Award #FA8650-18-2-7852, DARPA PIPES Award HR00111920014, DARPA CHIPS Award HR00111830002, DARPA SDH Award #FA8650-18-2-7863, NSF EVE Award #CCF-2008471, NSF PPoSS Award #CCF-2118709, equipment, tool, and/or physical IP donations from Intel, Xilinx, Synopsys, Cadence, and ARM. The U.S. Government is authorized to reproduce and distribute reprints for Government purposes notwithstanding any copyright notation thereon. Any opinions, findings, and conclusions or recommendations expressed in this publication are those of the author(s) and do not necessarily reflect the views of any funding agency.

### TABLE OF CONTENTS

|   | _    | graphical Sketch                                                                |     |

|---|------|---------------------------------------------------------------------------------|-----|

|   |      | ication                                                                         |     |

|   |      |                                                                                 | . V |

|   |      | e of Contents                                                                   |     |

|   |      | of Figures                                                                      |     |

|   |      | of Tables                                                                       |     |

|   | List | of Abbreviations                                                                | XV  |

| 1 |      | oduction                                                                        | 1   |

|   | 1.1  | On-Chip Interconnects                                                           |     |

|   | 1.2  | Off-Chip Interconnects                                                          |     |

|   | 1.3  | Thesis Overview                                                                 |     |

|   | 1.4  | Collaboration, Previous Publications, and Funding                               | 11  |

|   |      |                                                                                 |     |

| I | Scal | ing On-Chip Interconnects                                                       | 16  |

| 2 |      | hodology: A Unified Framework for On-Chip Networks                              | 17  |

|   | 2.1  | Introduction                                                                    | 17  |

|   | 2.2  | Related Work                                                                    | 18  |

|   |      | 2.2.1 Modeling OCNs                                                             | 18  |

|   |      | 2.2.2 Testing OCNs                                                              | 20  |

|   |      | 2.2.3 Evaluating OCNs                                                           | 21  |

|   | 2.3  | PyOCN Framework                                                                 | 23  |

|   | 2.4  | PyOCN for Modeling OCNs                                                         | 23  |

|   | 2.5  | PyOCN for Testing OCNs                                                          | 27  |

|   | 2.6  | PyOCN for Evaluating OCNs                                                       | 29  |

|   | 2.7  | Case Study                                                                      | 31  |

|   | 2.8  | Conclusion                                                                      | 35  |

| 3 | Arcl | hitecture: Low-Diameter On-Chip Networks for Manycore Processors                | 36  |

|   | 3.1  | Introduction                                                                    | 36  |

|   | 3.2  | Manycore OCN Topologies                                                         | 38  |

|   | 3.3  | Manycore OCN Analytical Modeling                                                | 42  |

|   | 3.4  | Manycore OCN Physical Design                                                    | 50  |

|   | 3.5  | Conclusions                                                                     | 52  |

| 4 | Prot | totype: CIFER Chip Tape-Out                                                     | 53  |

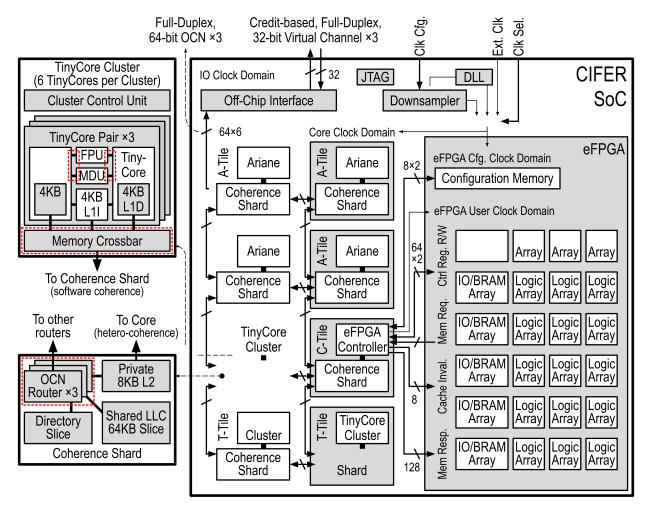

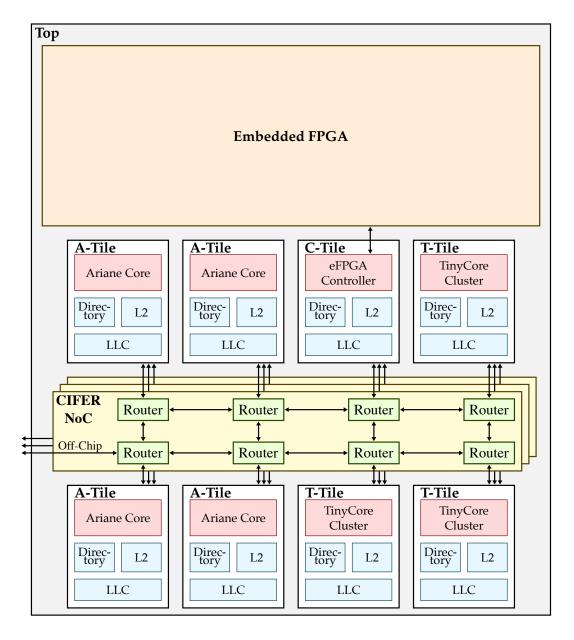

|   | 4.1  | CIFER Architecture                                                              | 53  |

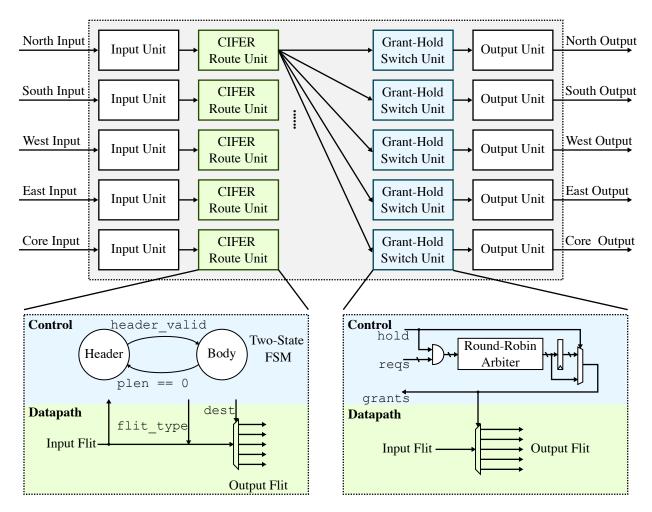

|   | 4.2  | CIFER On-Chip Networks                                                          | 56  |

|   |      | 4.2.1 Supporting Multi-Flit Packets in PyOCN                                    | 56  |

|   |      | 4.2.2 Logical vs. Physical Hierarchy Trade-Offs                                 | 58  |

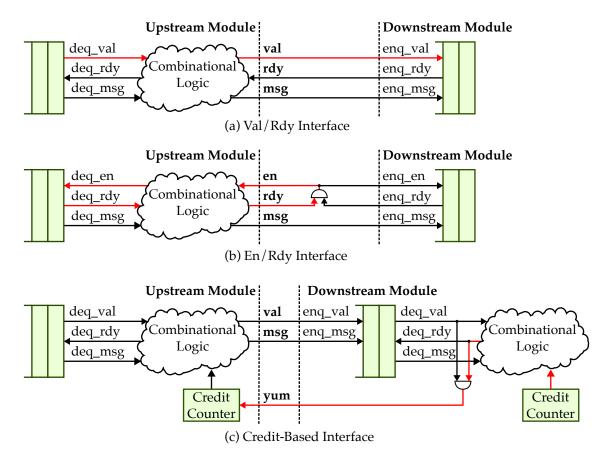

|   |      | 4.2.3 Data Transfer Interface Trade-Offs: Val/Rdy vs. En/Rdy vs. Credit-Based . | 60  |

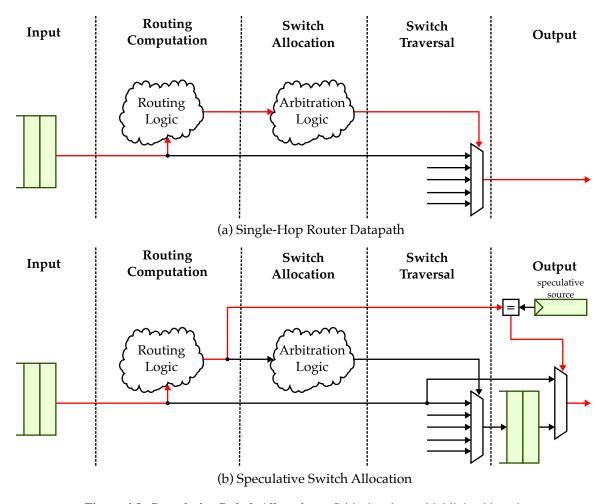

|   |      | 4.2.4 Timing Optimization: Speculative Switch Allocation                        | 63  |

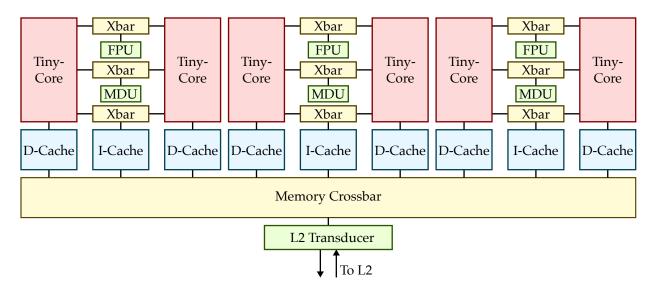

|    | 4.3  | 4.2.5 TinyCluster Resource-Sharing Crossbar and Memory Crossbar Design Conclusion |    |

|----|------|-----------------------------------------------------------------------------------|----|

| II | Scal | ling Off-Chip Interconnects                                                       | 69 |

| 5  |      | SV 8                                                                              | 70 |

|    | 5.1  |                                                                                   | 70 |

|    | 5.2  | e                                                                                 | 72 |

|    |      | e                                                                                 | 73 |

|    |      | <u> </u>                                                                          | 76 |

|    | 5.3  | 1                                                                                 | 80 |

|    |      |                                                                                   | 81 |

|    |      | · ·                                                                               | 83 |

|    | 5.4  |                                                                                   | 84 |

|    | 5.5  | Conclusion                                                                        | 87 |

| 6  | Arch | hitecture: Optically Connected Multi-Stack HBM Module                             | 89 |

|    | 6.1  | Introduction                                                                      | 89 |

|    | 6.2  | Background                                                                        |    |

|    | 6.3  | System Architecture                                                               |    |

|    | 6.4  | Evaluation                                                                        |    |

|    | 6.5  | Related Work                                                                      | 00 |

|    | 6.6  | Conclusions                                                                       | 00 |

| 7  | Prot | totype: PIPES Chip Tape-Out                                                       | 01 |

| •  | 7.1  | Introduction                                                                      |    |

|    | 7.2  | PIPES System Architecture                                                         |    |

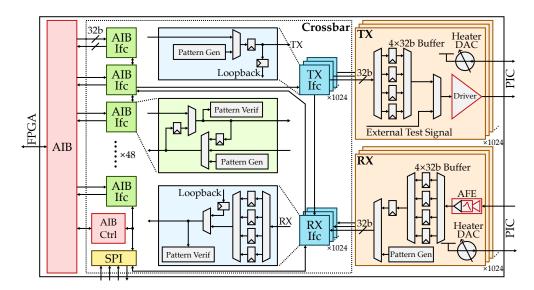

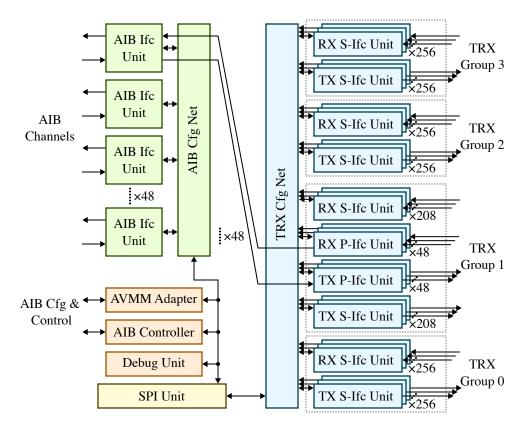

|    | 7.2  | 7.2.1 EIC Architecture                                                            |    |

|    |      | 7.2.2 EIC Scaling Challenges                                                      |    |

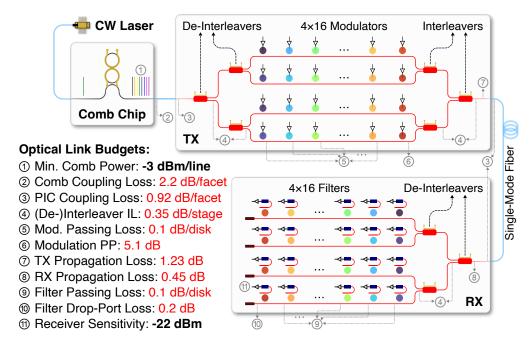

|    |      | 7.2.3 PIC Architecture                                                            |    |

|    |      | 7.2.4 PIC Scaling Challenges                                                      |    |

|    | 7.3  | EIC Design, Implementation, and Verification                                      |    |

|    | 7.0  | 7.3.1 Crossbar Design                                                             |    |

|    |      | 7.3.2 EIC Implementation                                                          |    |

|    |      | 7.3.3 Pre-Silicon Verification                                                    |    |

|    |      | 7.3.4 Post-Silicon Verification                                                   |    |

|    | 7.4  | Link-Level Evaluation                                                             |    |

|    |      | 7.4.1 Simulation-Based Evaluation                                                 |    |

|    |      | 7.4.2 Experimental Evaluation                                                     |    |

|    | 7.5  | System-Level Evaluation                                                           |    |

|    | 7.6  | Conclusion                                                                        |    |

|    | -    |                                                                                   |    |

| 8   | Conclusion |        |                                                        |       |  |  |  |  |  |  |

|-----|------------|--------|--------------------------------------------------------|-------|--|--|--|--|--|--|

|     | 8.1        | Thesis | Summary and Contributions                              | . 125 |  |  |  |  |  |  |

|     | 8.2        | Future | Work                                                   | . 126 |  |  |  |  |  |  |

|     |            | 8.2.1  | Testing Methodology for On-Chip Networks               | . 126 |  |  |  |  |  |  |

|     |            | 8.2.2  | LLMCompass-E2E                                         | . 127 |  |  |  |  |  |  |

|     |            | 8.2.3  | Co-Packaged Optics for Memory and System Interconnects | . 128 |  |  |  |  |  |  |

| Bil | bliogra    | aphy   |                                                        | 131   |  |  |  |  |  |  |

### LIST OF FIGURES

| 1.1  | Trend of Processor Core Count                                            | 2  |

|------|--------------------------------------------------------------------------|----|

| 1.2  | Examples of Manycore Processors                                          | 3  |

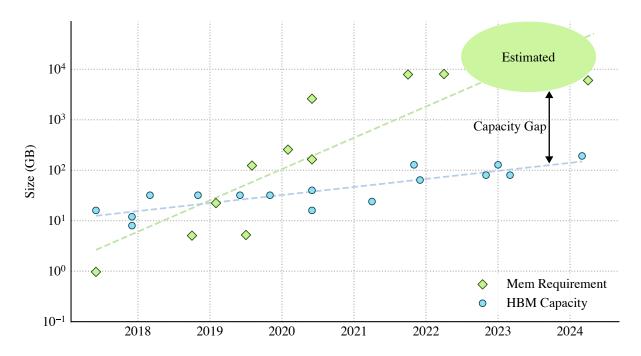

| 1.3  | Trend of Per-Device Memory Bandwidth and Capacity                        | 6  |

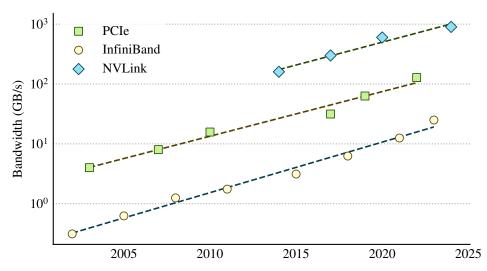

| 1.4  | Trend of Off-Chip Interconnect Bandwidth                                 | 7  |

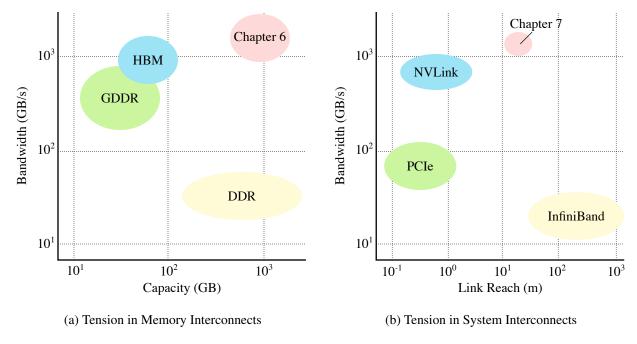

| 1.5  | Tension in Off-Chip Interconnect Technologies                            | 8  |

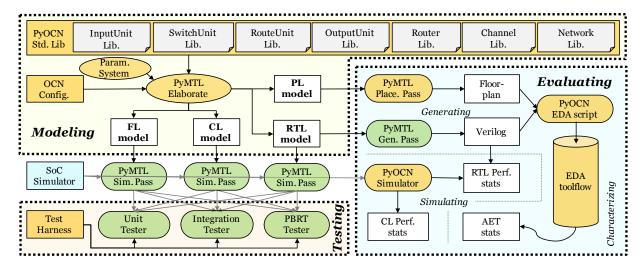

| 2.1  | Overview of PyOCN Framework                                              | 22 |

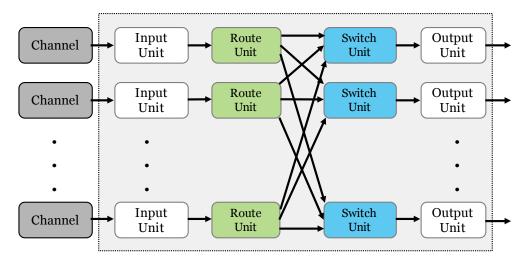

| 2.2  | PyOCN Generic Router Architecture                                        | 24 |

| 2.3  | FL Implementation of Ring Network                                        | 24 |

| 2.4  | CL Implementation of SwitchUnit                                          |    |

| 2.5  | RTL Implementation of SwitchUnit                                         |    |

| 2.6  | Physical Elaboration                                                     |    |

| 2.7  | Unit Test for a Router in 4×4 Mesh                                       |    |

| 2.8  | Property-Based Random Testing for Mesh Network Generator                 |    |

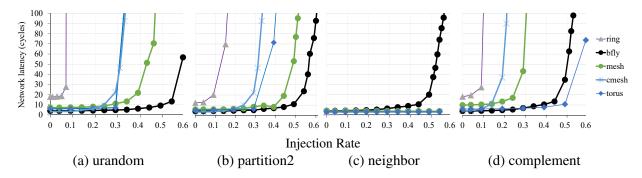

| 2.9  | RTL Simulation Results                                                   |    |

| 2.10 | Router Characterization                                                  |    |

| 2.11 | 4-ary 3-fly Butterfly Network                                            |    |

| 2.12 | 4-ary 3-fly Butterfly Network Floorplan                                  |    |

| 2.13 | Parameterization System Example                                          |    |

| 2.14 | Post Place-and-Route Layout of 4-ary 3-fly Butterfly                     | 34 |

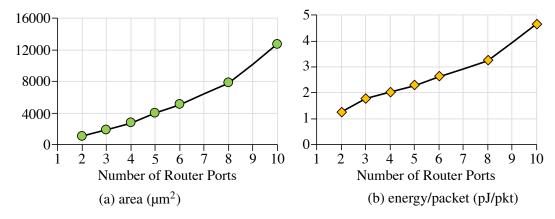

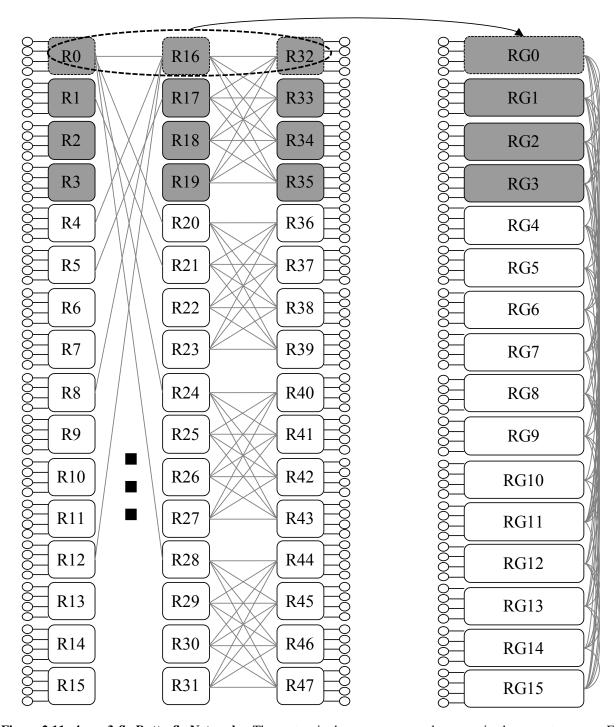

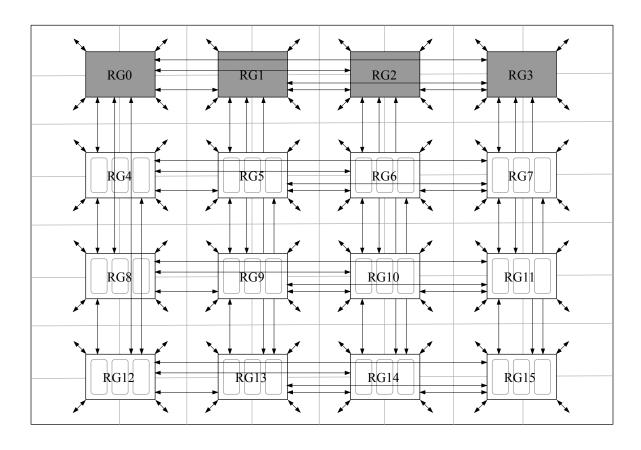

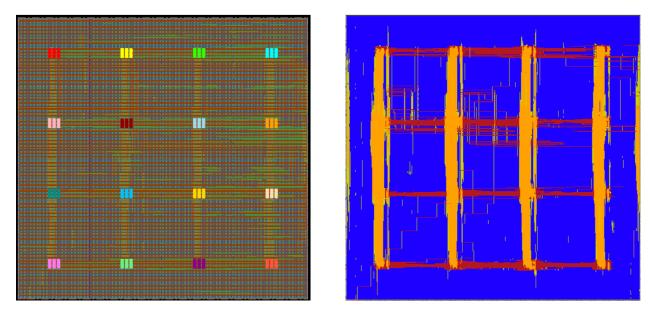

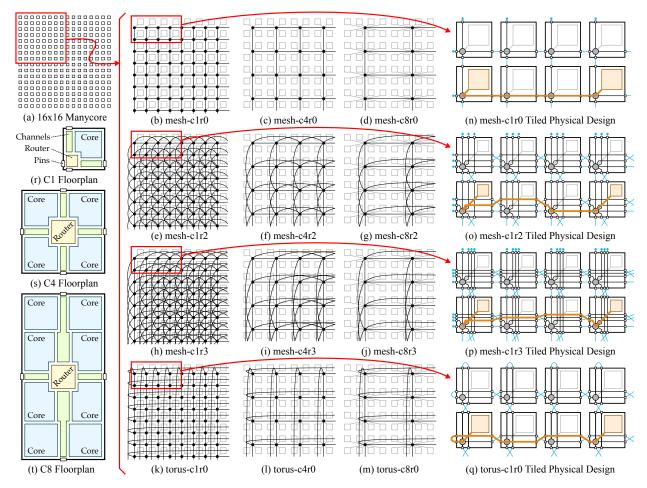

| 3.1  | Twelve Topologies Implemented Using a Tiled Physical Design Methodology  | 39 |

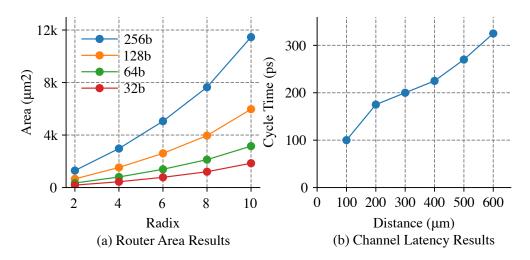

| 3.2  | OCN Component-Level Results                                              | 40 |

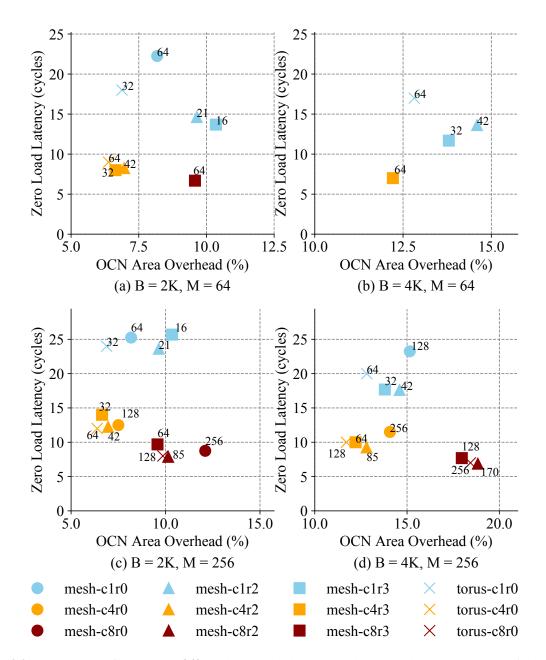

| 3.3  | Latency and Area Trade-Offs                                              | 43 |

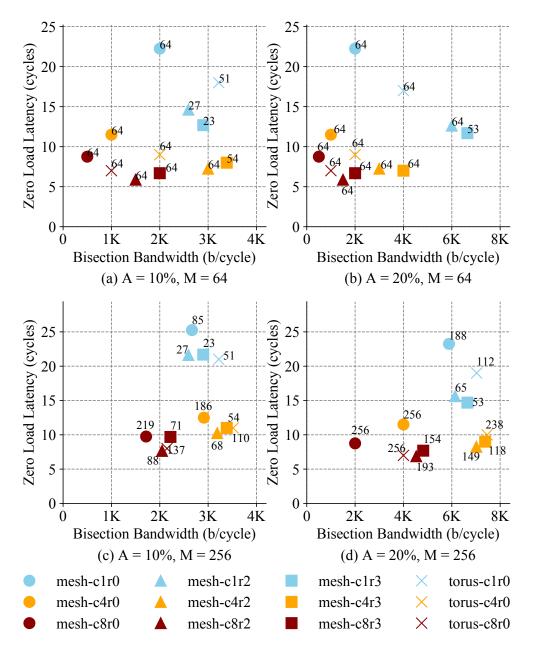

| 3.4  | Latency and Bandwidth Trade-Offs                                         | 44 |

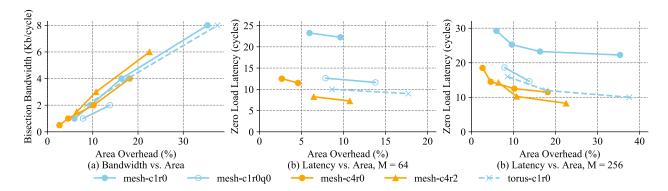

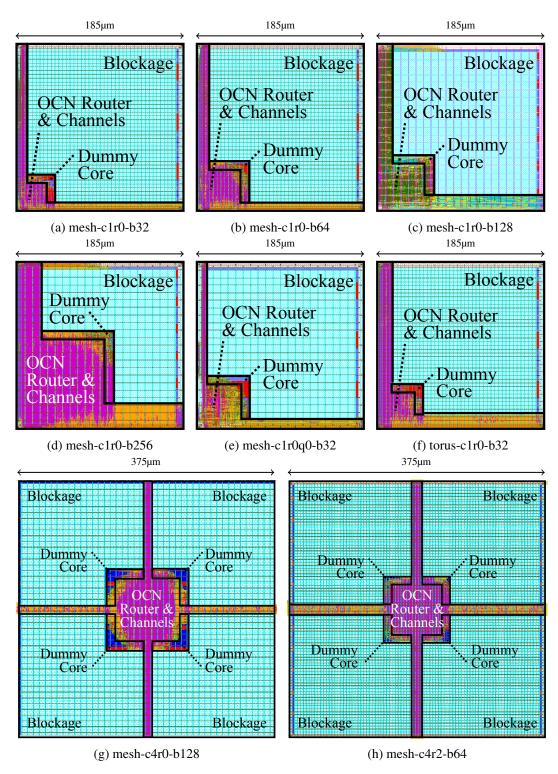

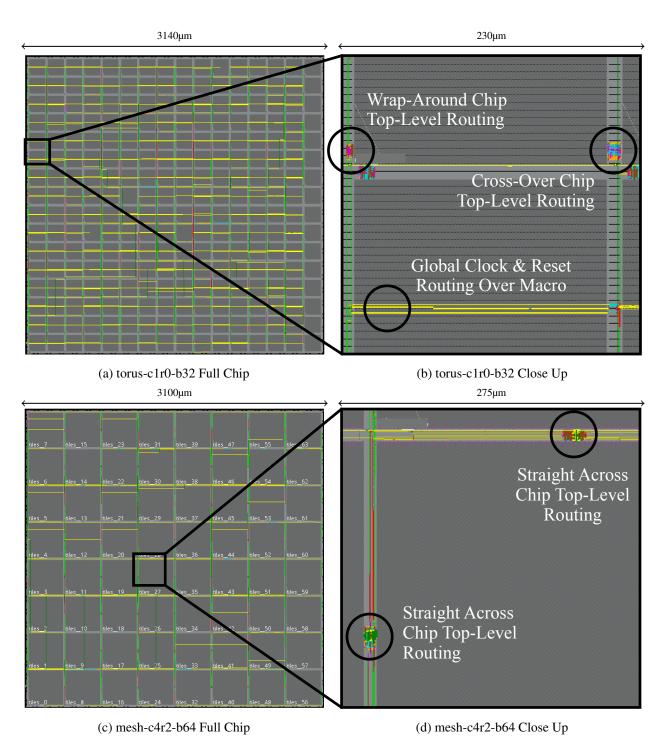

| 3.5  | Bandwidth, Latency, and Area Trade-Offs for Post-Place-and-Route Results | 47 |

| 3.6  | Example Macro-Level Post-Place-and-Route Layouts                         | 48 |

| 3.7  | Example Chip-Level Post-Place-and-Route Layouts                          | 49 |

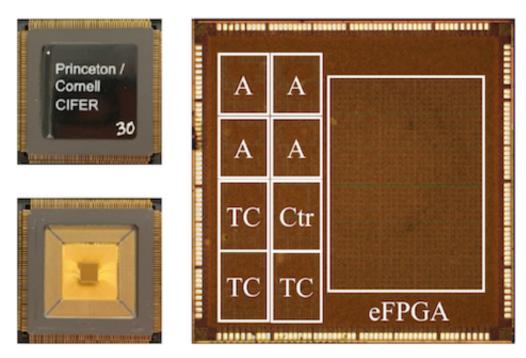

| 4.1  | CIFER Package and Die Photo                                              | 54 |

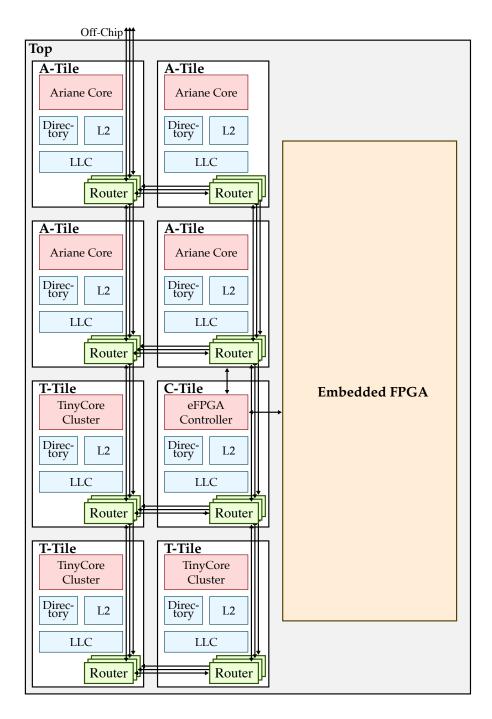

| 4.2  | CIFER SoC Architecture                                                   |    |

| 4.3  | CIFER NoC Header Format                                                  |    |

| 4.4  | CIFER Router Architecture                                                | 57 |

| 4.5  | CIFER SoC Logical Hierarchy                                              | 59 |

| 4.6  | CIFER SoC Physical Hierarchy                                             | 60 |

| 4.7  | Different Handshake Interfaces                                           | 61 |

| 4.8  | Speculative Switch Allocation                                            | 64 |

| 4.9  | TinyCore Cluster Architecture                                            | 65 |

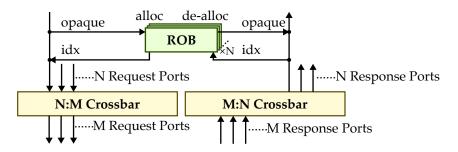

| 4.10 | Resource-Sharing Crossbar Design                                         | 66 |

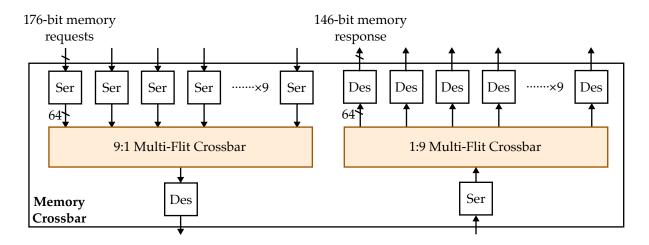

| 4.11 | Memory Crossbar Design                                                   | 66 |

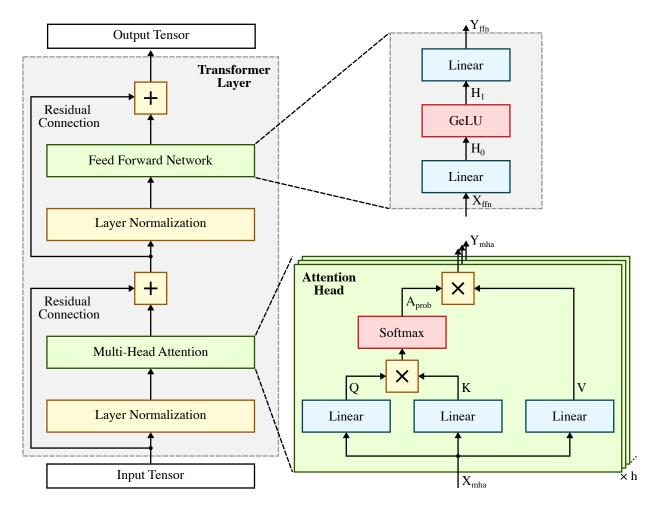

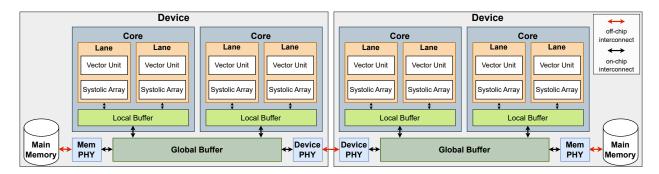

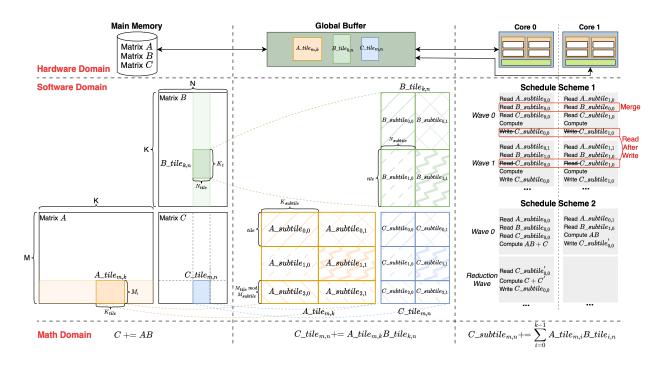

| 5.1  | Architecture of Decoder-Only Transformer Layer                           | 73 |

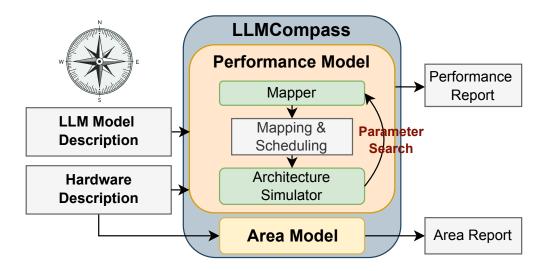

| 5.2  | LLMCompass Overview                                                      | 76 |

| 5.3  | LLMCompass Hardware Description Template                                 |    |

| 5.4  | LLM Model Description in LLMCompass                                   |

|------|-----------------------------------------------------------------------|

| 5.5  | Matrix Multiplication Performance Modeling in LLMCompass              |

| 5.6  | LLMCompass-E2E Overview                                               |

| 5.7  | LLMCompass-E2E Code Example                                           |

| 5.8  | LLMCompass-E2E Operator Example                                       |

| 5.9  | LLM Model Description in LLMCompassE2E                                |

| 5.10 | Computational Graph of A Multi-Head Attention Block                   |

| 6.1  | Memory Requirement for Training LLMs and HBM Capacity Per Device Over |

|      | Time                                                                  |

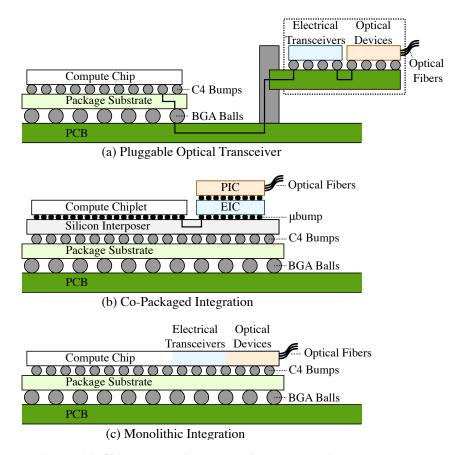

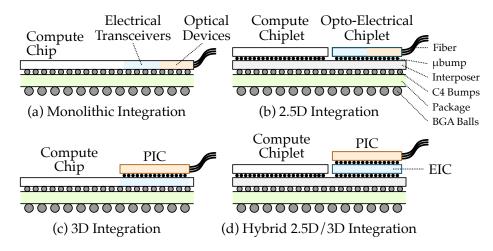

| 6.2  | Silicon Photonics Integration Technologies                            |

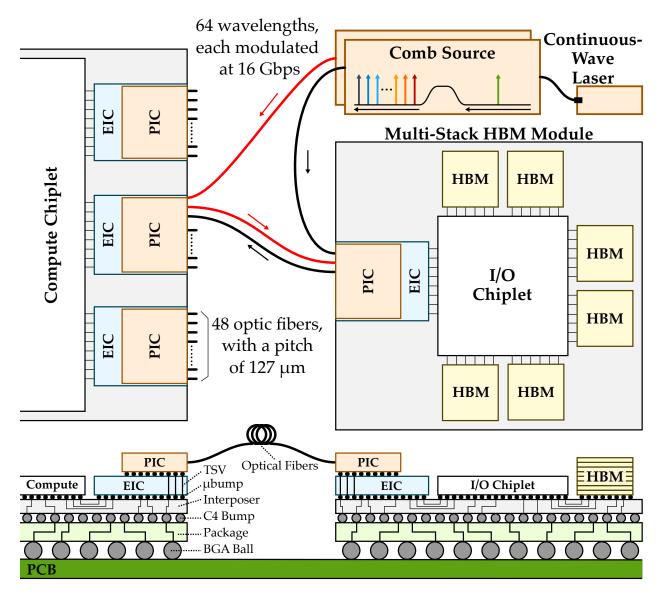

| 6.3  | Example System Architecture                                           |

| 6.4  | Optical Channel Datapath                                              |

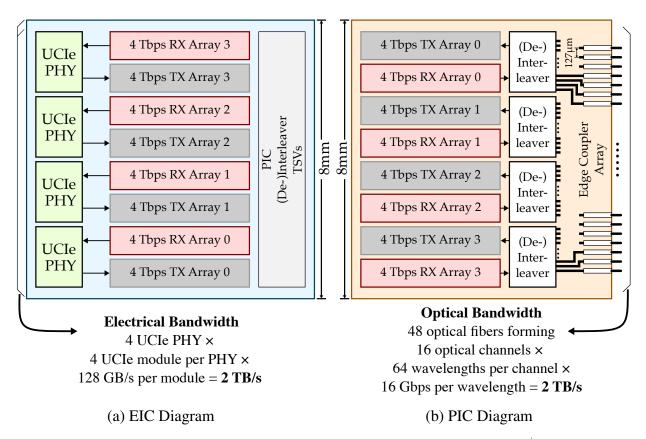

| 6.5  | EIC and PIC Architecture                                              |

| 6.6  | Evaluation Results for Training                                       |

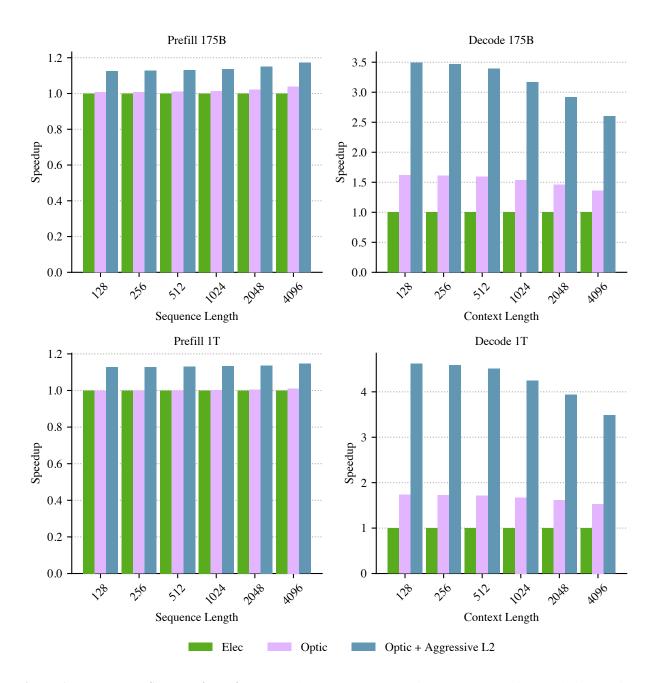

| 6.7  | Per Layer Speedup for Inference                                       |

| 7.1  | Approaches to Tightly Integrated Optical Interconnect                 |

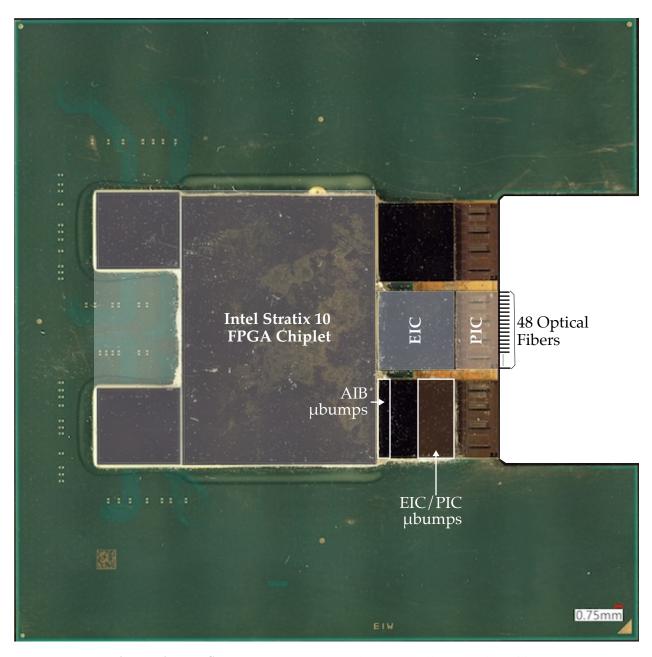

| 7.2  | PIPES Package Photo                                                   |

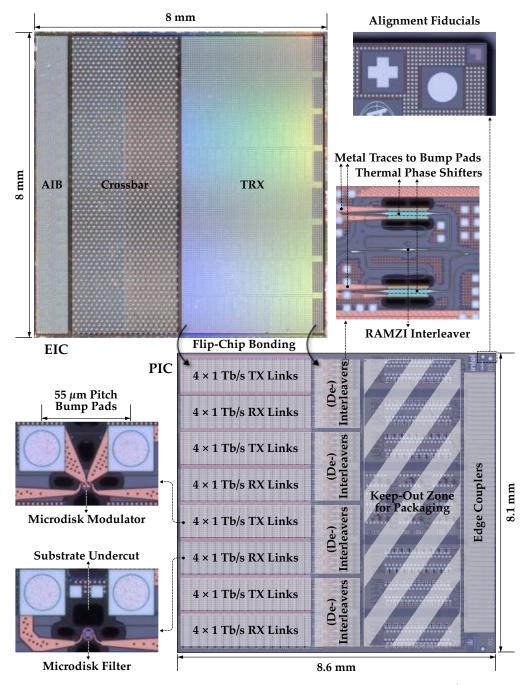

| 7.3  | EIC and PIC Die Photos                                                |

| 7.4  | EIC Architecture Block Diagram                                        |

| 7.5  | Photonic Link Architecture                                            |

| 7.6  | Crossbar Block Diagram                                                |

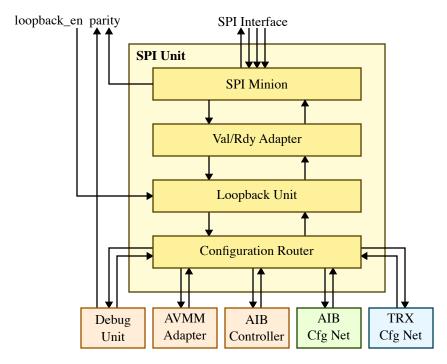

| 7.7  | SPI Configuration Stack                                               |

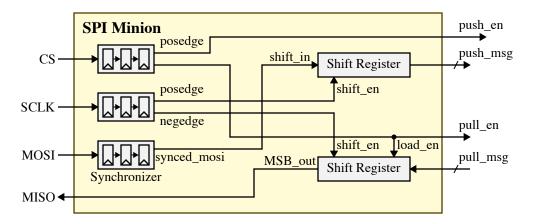

| 7.8  | SPI Minion Diagram                                                    |

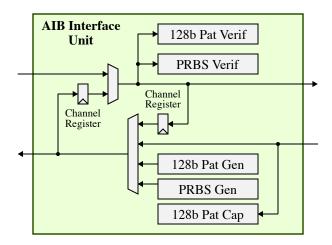

| 7.9  | AIB Interface Unit Datapath Diagram                                   |

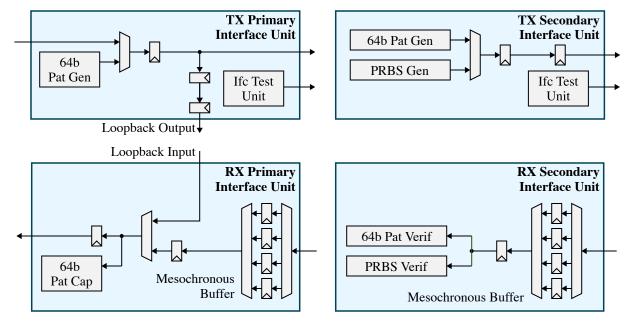

| 7.10 | TRX Interface Unit Datapath Diagram                                   |

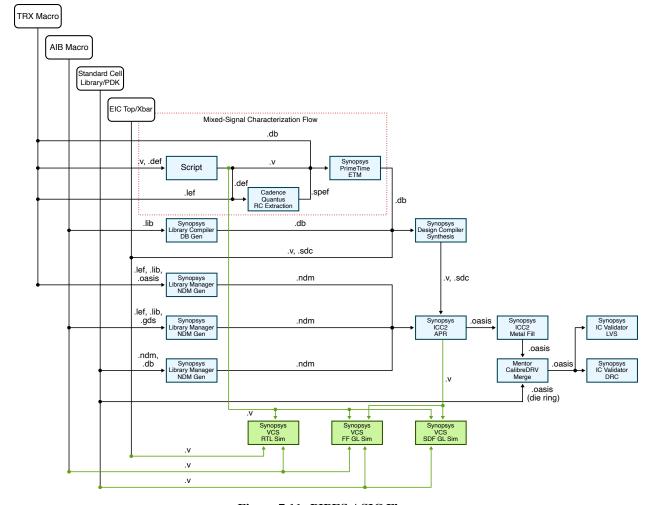

| 7.11 | PIPES ASIC Flow                                                       |

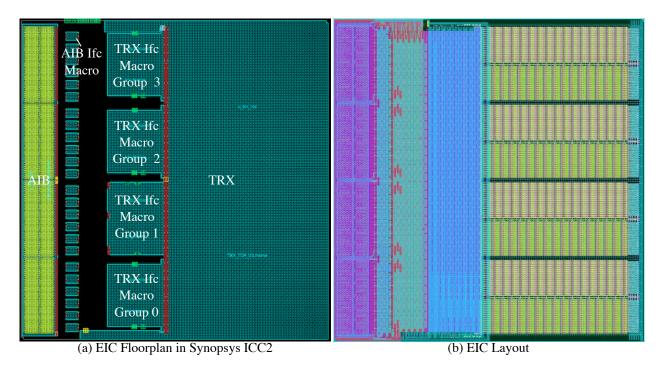

| 7.12 | EIC Floorplan and Layout                                              |

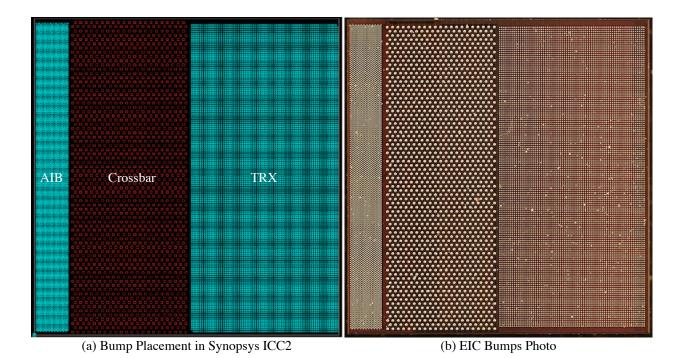

| 7.13 | EIC Bumps                                                             |

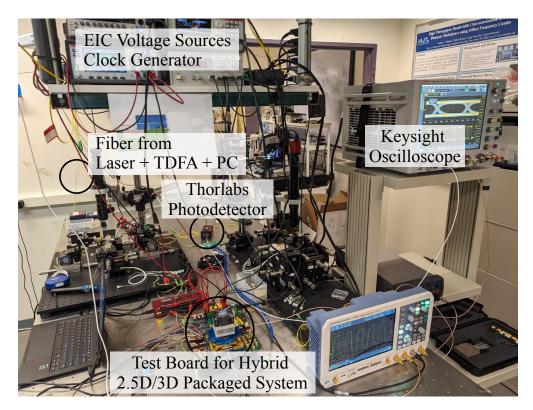

| 7.14 | Experimental Setup                                                    |

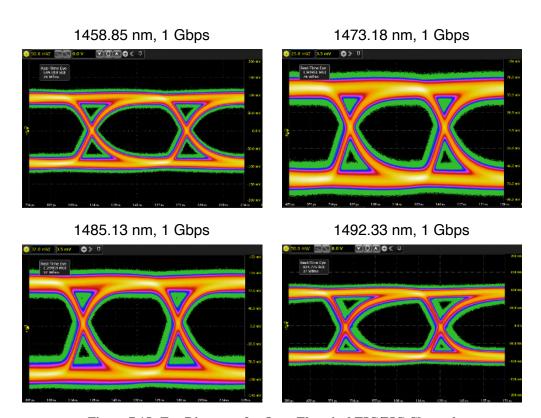

| 7.15 | Eye Diagrams for Opto-Electrical EIC/PIC Channel                      |

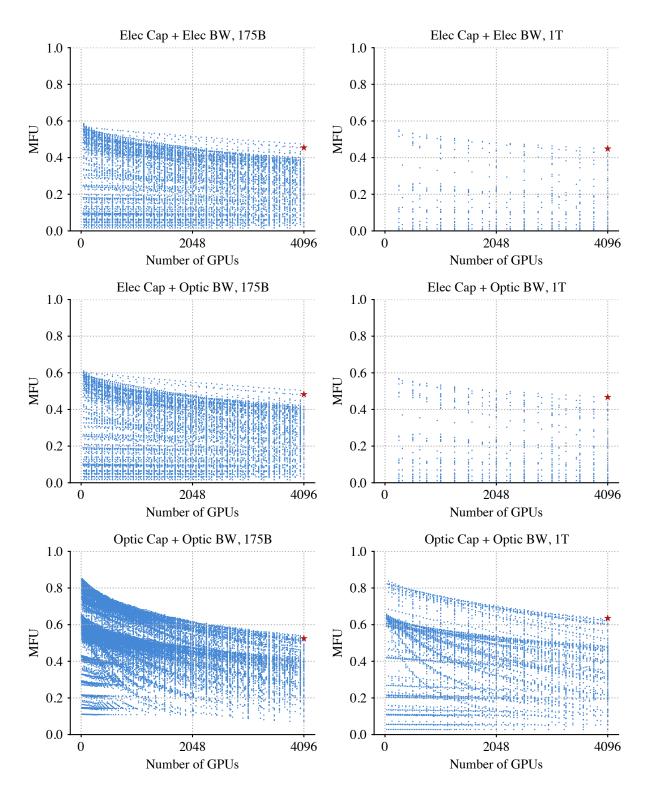

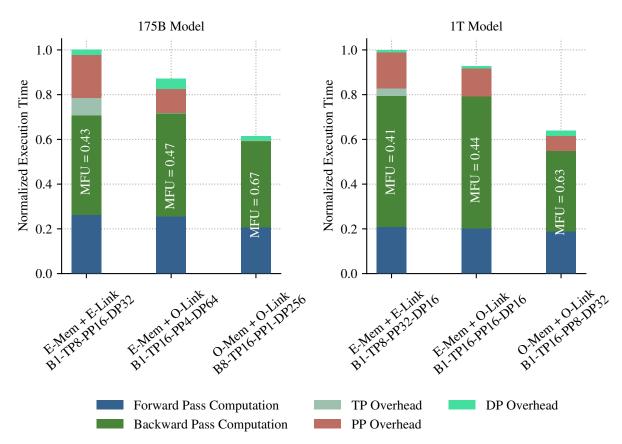

| 7.16 | Optimal Mappings for LLM Training                                     |

### LIST OF TABLES

| 2.1 | Comparison with Prior Art                          | 19 |

|-----|----------------------------------------------------|----|

| 2.2 | PyOCN Multi-Level Simulation                       | 26 |

| 3.1 | Analytical Modeling Results                        | 40 |

| 3.2 | Post-Place-and-Route Macro Results                 | 47 |

| 4.1 | Comparison of Data Transfer Interfaces             | 63 |

| 5.1 | Shape of intermediate Tensors in Transformer Layer | 72 |

| 5.2 | Comparison Against Real Hardware Results           | 87 |

#### LIST OF ABBREVIATIONS

OCN on-chip network

LLM large language model

CIFER coherent interconnect and FPGA enabling reuse

PIPES photonic in package for extreme scalability

ASIC application-specific integrated circuit

**FPGA** field-programmable gate array

GPU graphics processing unit

TPU tensor processing unit

MCM multi-chip module

RTL register-transfer level

DDR double data rate

DIMM dual inline memory module

GDDR graphics double data rate

HBM high bandwidth memory

TSV through-silicon via

**PCIe** peripheral component interconnect express

SoC system-on-chip

FL functional level

CL cycle level

PL physical level

eFPGA embedded FPGA

LLC last-level cache

**TRI** transaction response interface

MDU multiply-division unit FPU floating-point unit LUT look-up table

BSV Bluespec SystemVerilog

IR intermediate representation

FLOP floating-point operation

MFU model FLOPs utilization

EIC electrical interface chiplet

PIC photonic interface chiplet

CW continuous-wave

TX transmitter

RX receiver

TRX transceiver

**UCIe** universal chiplet interconnect express

**PHY** physical layer

**AIB** advanced interface bus

**PRBS** pseudo-random binary sequence

**AFE** analog front end

**SPI** serial peripheral interface

# CHAPTER 1 INTRODUCTION

The slowdown of Moore's Law and the end of Dennard scaling have fundamentally reshaped the landscape of computing. For decades, these two principles drove consistent improvement in single-chip performance by enabling more transistors to fit within the same area and improving the power efficiency per transistor. However, as physical and technical limits have been reached, the exponential gains in performance from these traditional scaling methods have diminished. This shift has compelled the industry to explore new strategies for enhancing performance, placing greater emphasis on *parallelism*. Modern computing systems, ranging from supercomputers to edge devices, now require more innovative design solutions to meet the demands of increasingly complex and data-intensive workloads.

One of the key strategies to address the limitations of traditional scaling is the adoption of *manycore architectures*, which integrate a large number of simple, lightweight processing cores on a single chip. Examples include thread-parallel manycore processors such as Epiphany-V [Olo16] and Celerity [RZAH+19b], as well as data-parallel manycore processors such as graphics processing units (GPU) [nvi20, nvi23] and tensor processing units (TPUs) [JKL+23]. Manycore systems can scale to hundreds or even thousands of cores, enabling massive parallelism and significantly higher throughput for data-intensive workloads. However, the efficiency of manycore architectures hinges on the ability to move data efficiently across the chip, making the design of scalable, high-performance on-chip networks (OCNs) essential.

While on-chip interconnects are critical for efficient data movement within the compute chip, off-chip interconnects play an equally important role in connecting these processors to external components, such as memory, storage, and other compute chips. Off-chip interconnects, including *memory interconnects* that connect processing units to external memory and *system interconnects* that connect multiple compute chips or systems, enable scalable and distributed compute systems by facilitating high-bandwidth, low-latency communication between multiple chips. These interconnects can range from short-reach connections spanning a few millimeters, such as the die-to-die interconnects in modern multi-chip modules (MCM), to long-reach connections covering up to a few kilometers, such as optical links in data center networks. The effectiveness of these distributed systems depends heavily on the design of scalable, high-performance off-chip interconnects that can handle the increasing demands of data movement across components.

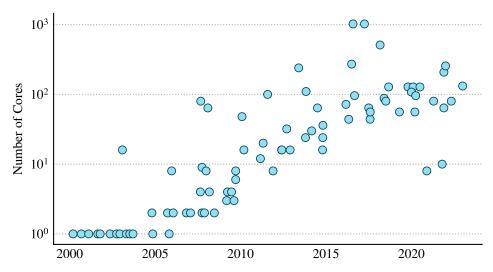

**Figure 1.1: Trend of Processor Core Count** – The figure illustrates the core count of selected processors from 2000 to 2020. The data is partially collected by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, C. Batten, and K. Rupp [Rup24].

In this chapter, I provide an overview of the challenges and opportunities in scaling on-chip and off-chip interconnects, highlighting the importance of efficient data movement in modern computing systems. Section 1.1 first discusses the trend of on-chip interconnects and then introduces the methodology and architecture challenges in designing scalable, high-performance on-chip networks. Section 1.2 first discusses the trend of off-chip interconnects, including *memory interconnects* and *system interconnects*, and then presents the methodology and architecture challenges in designing scalable, high-performance off-chip interconnects. Section 1.3 provides an overview of the thesis. Section 1.4 discusses the collaboration, previous publications, and funding sources related to the work presented in this thesis.

### 1.1 On-Chip Interconnects

As the computing industry seeks to overcome the limitations of traditional scaling, manycore architectures have emerged as a prominent solution. Over the past decades, there has been a steady trend towards increasing the core counts in processors, driven by the need for greater parallelism to handle the growing computational demands of modern workloads. Compared to general-purpose multi-cores, the manycore approach can improve throughput and energy efficiency per unit area, particularly for highly parallel workloads. As is illustrated in Figure 1.1, the core count in pro-

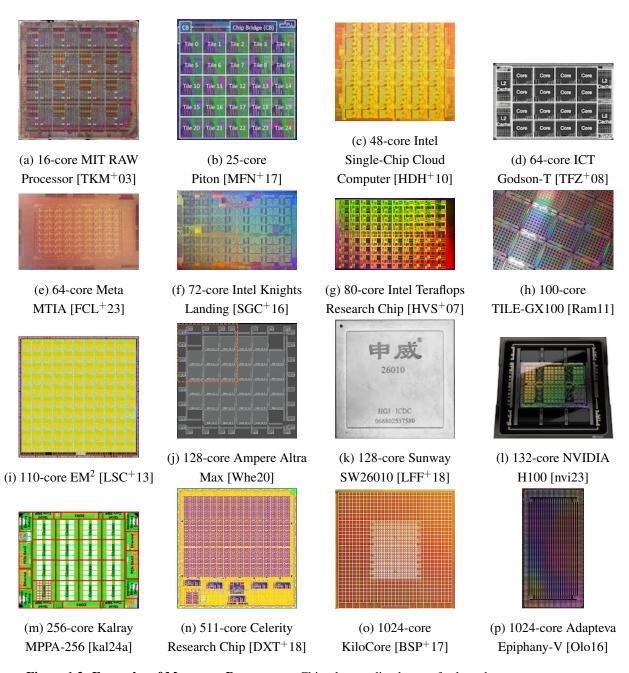

Figure 1.2: Examples of Manycore Processors – Chip plots or die photos of selected manycore processors.

cessors has scaled dramatically in the past two decades, reaching hundreds and even a thousand in recent years.

Figure 1.2 shows various examples of manycore processors that have been designed and manufactured over the years. Early *thread-parallel* manycore research prototypes integrated up to 110 cores within a single die. The MIT RAW processor [TKM+03] integrated 16 simple cores connected by a 4 × 4 mesh OCN. The Intel Teraflops research chip [HVS+07] contained 80 tiles arranged as a 10 × 8 mesh OCN. The Intel Single-Chip Cloud Computer (SCC) [HDH+10] was a manycore processor with 48 cores connected by a 4 × 6 mesh OCN. The 110-core Execution Migration Machine (EM²) [LSC+13] demonstrated a directory-less shared-memory manycore with a 10 × 11 mesh OCN. Over time, the industry has adopted the manycore approach as well. Examples include the 64-core Tile64 [BEA+08], the 72-core Knights Landing [SGC+16], the 100-core Tile GX100 [Ram11], the 128-core Ampere Altra Max [Whe20], and the 128-core Sunway SW26010 [LFF+18]. Recent research prototypes have scaled core counts to over a thousand cores, such as the 1000-core KiloCore [BSP+17], the 1024-core Epiphany-V [Olo16], and the 4096-core Manticore [ZSB21].

Data-parallel manycore processors are also widely adopted by the industry, with GPUs being the most prominent example. GPUs usually have around a hundred cores (known as stream multiprocessors in NVIDIA GPUs and compute units in AMD GPUs), and they are capable of supporting thousands of concurrent hardware threads. In addition to GPUs, there are also custom accelerators designed for specific workloads, such as the Google TPU [JKL+23], Meta MTIA [FCL+23], Kalray MPPA-256 [kal24a], and Tenstorrent Grayskull [kal24b]. These custom accelerators typically incorporate multiple processing elements (PEs) arranged into a 2D systolic array.

The effectiveness of manycore systems relies heavily on efficient on-chip data movement, making the design of scalable, high-performance OCNs critical. However, achieving scalability and high-performance in OCN design presents substantial challenges, both in methodology and architecture.

**Methodology Challenge** – Developing on-chip interconnects involves overcoming several methodological challenges, particularly in the design, testing, and evaluation of networks. The design space for OCNs is vast, encompassing various factors such as topology, routing algorithms, flow control mechanisms, and physical design considerations. Exploring this design space requires a unified approach that can model, simulate, and evaluate OCNs across different levels of abstrac-

tion, from functional models to cycle-accurate simulations and hardware implementations. However, existing tools often struggle to balance the need for rapid design-space exploration with the accuracy required for hardware-level evaluation. For example, many widely used on-chip network simulators use cycle-level modeling for early design-space exploration and verifying cycle-level behavior [APM+12, AKPJ09, CHB+10, JBM+13, TB12, LSC+10]. However, these simulators do not support register-transfer-level (RTL) modeling and cannot easily generate synthesizable Verilog, which is essential for accurate evaluation of area, energy, and timing. OCN generators use RTL modeling to accurately characterize area, energy, and timing, but they lack the high-level design abstractions that enable fast design-space exploration [CP04, PH13, KK17]. This gap creates challenges in assessing trade-offs between performance, area, and energy consumption early in the design process, making it difficult to iterate and refine OCN designs efficiently. To address these challenges, this thesis presents a unified framework that seamlessly integrates modeling, testing, and evaluation to support the development of scalable and robust OCNs.

Architecture Challenge – A notable gap exists a noticeable gap between the theoretical advancements in OCN design and their practical implementation in manycore processors. While research literature has proposed numerous innovative solutions to improve OCN performance, such as novel flow-control schemes [KPKJ07, MWM04, PD01], custom circuits [KS08, CPK<sup>+</sup>13], and novel network topologies [BD06, BD06, KBD07, GHKM09, GHKM11], most manycore processors still adopt a simple 2D-mesh OCN topology [BEA<sup>+</sup>08, WGH<sup>+</sup>07, MFN<sup>+</sup>17, LSC<sup>+</sup>13, BSP<sup>+</sup>17, Whe20, Hal20, RZAH<sup>+</sup>19b], even though it is well known that the high diameter of 2D-mesh topologies can significantly increase packet latency and thus reduce system-level performance [DT04]. The key reason is that implementing manycore processors relies on a tiled physical design methodology, yet these novel solutions are often incompatible with this approach. To bridge this gap, this thesis explores practical architectures that can reduce the network diameter while remaining compatible a tiled physical design methodology.

### **1.2** Off-Chip Interconnects

As the number of cores within a single chip continues to scale, the demand for higher memory bandwidth has risen sharply to ensure that compute cores receive sufficient data. Additionally, modern data-intensive workloads, such as large language model (LLM) training, require a substan-

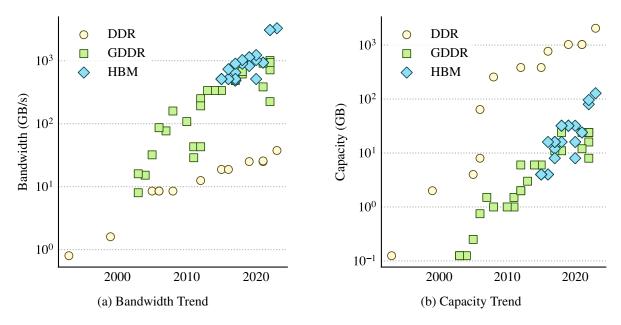

**Figure 1.3: Trend of Per-Device Memory Bandwidth and Capacity** – This plot shows how the per-device memory bandwidth and capacity of different memory technologies scale over time. Data is collected from [tec24b, tec24a]

tial amount of memory capacity. This has driven the need for off-chip *memory interconnects* that can provide high bandwidth and are easy to expand memory capacity. Meanwhile, while tremendous efforts have been made to scale up single-chip performance, the physical limitations of chip design, such as reticle size, mean that further gains are increasingly difficult. Therefore, scalable, high-performance *system interconnects* that can enable efficient scale-out of distributed compute systems has become increasingly critical.

For off-chip *memory interconnects*, a key tension exists between achieving high bandwidth and maintaining scalable memory capacity. As illustrated in Figure 1.3(a) and Figure 1.3(b), both the bandwidth and capacity of off-chip memory have improved significantly over the years across various technologies, each enabled by different types of interconnects and offering unique trade-offs. Double data rate (DDR) memory is typically integrated on separate circuit boards known as dual inline memory modules (DIMMs), which are installed on the motherboard of a compute node. This setup allows for flexible memory expansion, but the off-chip interconnect between the compute chip and the DIMMs limits bandwidth compared to more integrated memory technologies. Graphics double data rate (GDDR) memory, on the other hand, is integrated on the same board as the compute chip and is positioned close to its chip package. This shorter off-chip connection allows for higher bandwidths compared to DDR, making GDDR well-suited for bandwidth-hungry workloads such as graphics processing. However, expanding the memory capacity of GDDR is

**Figure 1.4: Trend of Off-Chip Interconnect Bandwidth –** This plot shows how the bandwidth of selected off-chip interconnect technologies scales over time. Data is adapted from various online sources [Sha22, inf24, nvl24]

less flexible than DDR. High bandwidth memory (HBM) is a more recent memory technology and takes integration a step further by being tightly integrated within the same package as the compute chip. HBM is connected to the compute chip via short-reach high-density chiplet I/Os which enables significantly higher bandwidths compared to DDR and GDDR, making it indispensable for modern data-intensive applications. Although HBM achieves higher memory density compared to DDR and GDDR by leveraging advanced technologies such as 3D stacking and through-silicon vias (TSVs), the number of HBM stacks that can be integrated within a single package is fundamentally limited by the perimeter of the compute chip. This limitation makes it challenging to scale the memory capacity of HBM-based memory systems.

For off-chip *system interconnects*, a key tension exists between high bandwidth and link reach, which is closely related to the scalability of the interconnect. As illustrated in Figure 1.4, system interconnect technologies such as Peripheral Component Interconnect Express (PCIe), InfiniBand, and NVLink address specific requirements based on different use cases, and they have seen significant increase in bandwidth over the years. PCIe is commonly used for connecting different components, such as CPU, GPU, network cards, and storage devices. While PCIe has seen steady bandwidth improvements over the years, from a few GB/s in the late 1990s to 128 GB/s in the latest PCIe 6.0 standard, it is mostly limited to short-reach connections within a server node. InfiniBand is widely used for interconnecting different compute nodes over a long distance. While its bandwidth of InfiniBand has scaled similarly over the years, reaching up to 25 GB/s per port in the lasted

**Figure 1.5: Tension in Off-Chip Interconnect Technologies –** Conceptual illustration of the tension in off-chip interconnect technologies.

XDR version, the bandwidth offered by InfiniBand is still lower than short-reach interconnects like PCIe. Since the 2010s, the rise of deep learning and AI workloads demanding high throughput has led to the development of specialized high-bandwidth interconnects like NVLink, offering up to 900 GB/s per GPU. However, the limited link reach of NVLink restricts its scalability, and it is primarily used for tightly-coupled GPUs within a single node (e.g., DGX H100).

Figure 1.5 conceptually illustrates the tensions in various memory interconnect and system interconnect technologies. These tensions give rise to challenges in scaling off-chip interconnects, both in methodology and architecture.

Methodology Challenge – Developing an accurate model for large-scale distributed systems is challenging primarily due to the complex interactions between interconnected components. Unlike on-chip networks, where interactions are confined within a single chip, off-chip interconnects must manage data transfer across multiple devices, including CPUs, GPUs, memory modules, and storage units, often spanning multiple compute nodes. Modeling such a diverse range of interactions is difficult, as it involves considering multiple layers of communication across various interconnects in the system. Additionally, large-scale distributed systems with multiple compute nodes and sophisticated interconnects are not readily accessible to most researchers, making it challenging

to calibrate models against real hardware performance. This thesis focuses on the methodology challenge of modeling distributed LLM training.

Architecture Challenge – The design of off-chip interconnects involves navigating trade-offs between many aspects, such as latency, bandwidth, energy efficiency, and scalability. Modern workloads, however, demand high performance across almost all these metrics. Optimizing one of these aspects usually often comes at the expense of others. For instance, HBM-based memory systems, enabled by tightly integrated memory interconnect, offer exceptional bandwidth but suffer from limited memory capacity. High-bandwidth system interconnects such as NVLink come at the cost of limited scalability. Emerging technologies, such as tightly integrated silicon photonics, present opportunities to break some of these trade-offs. This thesis investigates the use of copackaged optics to break these traditional trade-offs, advancing interconnect designs to meet the demands of future large-scale, high-performance workloads.

#### 1.3 Thesis Overview

This thesis explores new methodologies, architectures, and silicon prototypes to address the challenges of scaling both on-chip and off-chip interconnects in modern computing systems. The work is divided into two main parts: the first focuses on OCNs for manycore architectures, while the second addresses off-chip interconnects, particularly for machine learning workloads. By presenting comprehensive frameworks and practical design solutions, this thesis aims to improve the scalability, performance, and efficiency of interconnects, and demonstrate their feasibility through silicon prototypes.

Chapter 2 presents PyOCN, a unified Python-based framework for modeling, testing, and evaluating OCNs. PyOCN enables rapid design-space exploration of OCNs by providing a library of highly parametrized router and network components, which can be easily configured and composed to form complex network topologies with various routing algorithms and flow control mechanisms.

Chapter 3 proposes a tiled physical design methodology for implementing low-diameter OCNs, which closes the gap between theoretical principle and practical implementation. I, concurrently with the work by Jung et. al [JDZ<sup>+</sup>20], propose the ruche channel to fully exploit the VLSI wiring capability in modern technology nodes. It demonstrates that low-diameter OCNs for manycore processors can be realized by adapting mesh/torus topologies with concentration and ruche channels.

Through analytical modeling and realistic layout-level evaluations, I demonstrate that 2D-mesh topologies with modest concentration factors and modest length ruche channels can significantly reduce network diameter at similar area and bisection bandwidth.

Chapter 4 presents the CIFER chip tape-out, in which PyOCN was used for developing OCNs for different use cases. This chapter discusses the CIFER architecture, the OCN implementations, as well as the findings and reflections I made during the tape-out process.

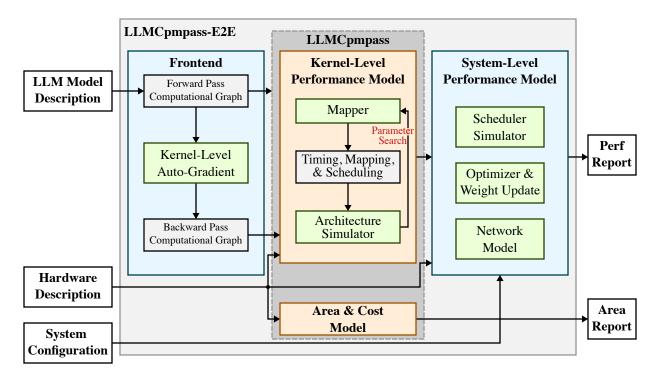

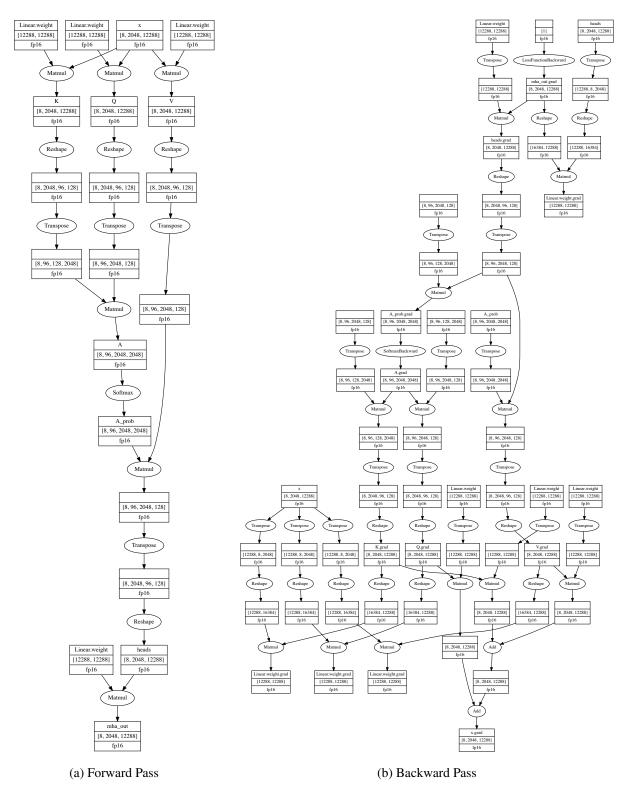

Chapter 5 introduces LLMCompass-E2E, a performance evaluation framework for large-scale distributed training workloads. LLMCompass-E2E is built on top of the existing LLMCompass framework, which provides kernel-level performance model for inference. By incorporating a kernel-level compute graph intermediate representation (IR), kernel-level auto-gradient, and a pipeline scheduler simulator, LLMCompass-E2E effectively supports modeling the end-to-end distributed training performance on a given compute system.

Chapter 6 proposes optically connected multi-stack HBM modules that leverage co-packaged silicon photonics interconnect. The proposed design extends the HBM memory system off the compute interposer, circumventing the chip packaging constraint and allowing more HBM stacks to be connected to the compute chip while also improving off-chip bandwidth. Evaluations using LLMCompass-E2E show significant improvements in training and inference efficiency for large-scale large language models (LLMs).

Chapter 7 presents the PIPES silicon photonic tape-out, which validates the proposed off-chip interconnect in Chapter 6. This chapter details the PIPES system architecture as well as the design, implementation, and verification of the electrical interface chiplet (EIC).

Chapter 8 concludes the thesis by summarizing the contributions of this thesis and discussing future research directions. The primary contributions of this thesis are as follows:

- I develop PyOCN, a unified Python-based framework for modeling, testing, and evaluating on-chip networks that enables rapid design-space exploration.

- I propose and evaluate practical OCN topologies that reduce the network diameter while remaining practical to implement using a tiled physical design methodology.

- I demonstrate the benefits of PyOCN through the CIFER chip tape-out, highlighting practical design trade-offs and optimizations.

- I develop LLMCompass-E2E, a performance evaluation framework for large-scale distributed training workloads.

- I propose and evaluate the use of co-packaged silicon photonic interconnect to scale the memory capacity and bandwidth of HBM-based memory systems, which are essential for LLM workloads.

- I demonstrate a practical implementation of the proposed co-packaged silicon photonic interconnect through the PIPES tape-out.

## 1.4 Collaboration, Previous Publications, and Funding

This thesis would not have been possible without the support and mentorship of my advisor, Christopher Batten, as well as the collaboration of my colleagues at Cornell University and external partners. Throughout my Ph.D. journey, Christopher Batten was a constant source of inspiration and guidance, consistently shaping the direction and depth of my research. His feedback, along with our countless discussions, played a crucial role in refining my ideas and driving my work forward.

I was one of the core contributors to the PyMTL3 project, where I collaborated closely with Shunning Jiang and Peitian Pan to design and implement the PyMTL3 framework from scratch. Shunning Jiang led the project, spearheading the design and implementation of key components, including the core DSL, the pass mechanism, the scheduling and simulation passes, and the initial PyMTL3 standard library. Peitian Pan was responsible for designing and implementing the translation mechanism, enabling extensible conversion from the PyMTL3 DSL to various backends. I focused on developing the method-based interfaces, mixed-level modeling, the parameter mechanism within the DSL, and contributed to the creation of several IPs using PyMTL3. Shunning Jiang led the paper we published at IEEE Micro in 2020 [JPOB20].

I co-led the PyH2 (Python Hypothesis for Hardware) project with Shunning Jiang. Zac Hatfield-Dodds, the creator of the Hypothesis framework, provided valuable feedback and guidance on the integration of Hypothesis with PyMTL3. I carried out the initial pathfinding of PyH2. I worked on leveraging Hypothesis to effectively test hardware design generators, with the help of Cheng Tan. Peitian Pan and Kaishuo Cheng led the work on generating random instruction sequences to

automatically test processors. Xiaoyu Yan and Eric Tang led a case study on testing a PyMTL3 cache generator with PyH2. Yixiao Zhang contributed to exploring Hypothesis stateful testing for hardware data structures. Peitian Pan developed a random bug injector for evaluating PyH2. Shunning Jiang led the paper we published at IEEE Design & Test in 2020 [JOP<sup>+</sup>20].

I led the PyOCN project. I implemented the initial version of the PyOCN framework from scratch. Cheng Tan joined the project later and contributed to the development of several router components and network topologies. Shunning Jiang provided support and guidance on the PyMTL3 integration. Peitian Pan provided support on PyMTL3 translation which was essential for generating synthesizable Verilog. Christopher Torng and Shady Agwa helped with setting up the ASIC toolflow for area, energy, and timing analysis. Cheng Tan led the paper we published at ICCD 2019 [TOJ<sup>+</sup>19].

I led the tiled OCN project. I pushed various router and channel designs through the ASIC flow and built analytical models showing trade-offs in latency, bandwidth, and area. I designed and implemented the RTL model for the routers, hard macros, and networks. I conducted post-place-and-route evaluations for a variety of hard macros and network topologies. Shady Agwa provided guidance on hierarchical physical design and supported the chip-level results. I led the publication of our work at NOCS 2020 [OAB20].

I was a key contributor to the CIFER chip tape-out presented in Chapter 4. The CIFER project was a collaborative effort between Professor David Wentzlaff's research group at Princeton University and Professor Christopher Batten's research group at Cornell University. The Princeton team, including Ting-Jung Chang, Ang Li, Fei Gao, Georgios Tziantzioulis, Jinzheng Tu, Kaifeng Xu, Paul Jackson, August Ning, Grigory Chirkov, Marcelo Orenes-Vera, and Jonathan Balkind, led the overall project and was in charge of developing the Ariane tile, developing the embedded FPGA, top-level integration, physical design, and post-silicon testing. The Cornell team was in charge of developing the TinyCore cluster and the OCN. Tuan Ta led the TinyCore cluster development. He developed the TinyCore RTL model. Xiaoyu Yan, and Eric Tang developed the software-managed coherent cache in the TinyCore cluster, with help and guidance from Moyang Wang. Moyang Wang led the development of a task-parallel runtime system for the TinyCore cluster, with support from Tuan Ta. Shady Agwa and I assisted in setting up gate-level testing and helped with preliminary timing and area analysis by pushing the TinyCore cluster through an ASIC flow. I led the development of the tile-level OCN as well as the OCNs within the TinyCore

cluster. With tremendous help from Jonathan Balkind, I successfully integrated PyOCN into the OpenPiton framework. Fei Gao and Professor David Wentzlaff provided valuable feedback and guidance on the OCN design and timing optimization. Ting-Jung Chang and Ang Li led the papers we published at CICC and SSCL in 2023 [CLG<sup>+</sup>23, LCG<sup>+</sup>23].

I was a key contributor to the LLMCompass-E2E framework, which was an extension of the LLMCompass framework. I worked closely with the first author of LLMCompass, Hengrui Zhang from Professor David Wentzlaff's group to extend the original LLMCompass framework to support end-to-end distributed training performance modeling. Hengrui Zhang provided guidance on the LLMCompass framework and we had many productive discussions on distributed LLM training. I refactored the original LLMCompass software model and added a kernel-level compute graph IR. I implemented kernel-level auto-gradient in LLMCompass. I re-engineered the frontend of the framework to be more automated. I implemented an event-driven simulator for generating pipeline schedules which is critical for modeling the pipeline parallelism. I implemented network models for simulating the communication overhead for data parallelism and pipeline parallelism. I added support for modeling different activation recomputation strategies.

I led the optically connected HBM project. I had a lot of useful brainstorming sessions with Austin Rovinski at the beginning of the project. Yuyang Wang and Songli Wang taught me a lot about silicon photonics. Hengrui Zhang provided support on LLMCompass and we had many useful discussions on the system design. I implemented the optically connected HBM model in LLMCompass-E2E and conducted various experiments to explore its benefit in both LLM training and inference. I led our paper submission to IEEE CAL. Professor David Wentzlaff and Austin Rovinski provided valuable feedback on the paper.

I was a key contributor to the PIPES silicon photonic tape-out, presented in Chapter 7. PIPES was led by Intel and was a collaborative effort between Professor Keren Bergman's research group at Columbia University, Professor Alyosha Molnar's research group at Cornell University, and Professor Christopher Batten's research group at Cornell University. Kaveh Hosseini and Tim Tri Hoang from Intel led the overall project and provided valuable feedback and support throughout the project. The Columbia team led the development of the PIC and the Cornell teams led the development of the EIC. For Professor Keren Bergman's group, Songli Wang and Asher Novick led the development of the modulators in the PIC. Robert Parsons led the development of the ring filters in the PIC and wafer-level testing. Songli Wang and Yuyang Wang led the development of the

interleavers and de-interleavers in the PIC. For Professor Alyosha Molnar's group, Hamilton Lee and Luke James designed the offset DAC. Daria Sansoterra worked on current mirrors. Christine Ou, Devesh Khilwani, and Sunwoo Lee led the development of the TRX unit in the EIC. I coled the EIC top-level integration and physical design with Austin Rovinski. I implemented the RTL model of the EIC, including an SPI configuration unit, a configuration network, an AIB controller, AIB interface units, and TRX interface units. Austin Rovinski implemented the RTL model of the mesochronous buffer. I led the EIC top-level pre-silicon verification. Ching-Chi Chang provided guidance on setting up the test bench and helped significantly with debugging the AIB unit. I worked closely with Christine Ou and Devesh Khilwani to design a digital testing interface for the TRX unit. I implemented most of the testing infrastructure and the test cases. Nicholas Cebry also contributed many test cases to pre-silicon verification. I co-led the top-level AISC flow and physical design of the EIC with Austin Rovinski. I worked closely with Christine Ou and Devesh Khilwani to create a mixed-signal characterization flow. I implemented the hard macros for AIB interface units and TRX interface units. Khalid Al-Hawaj helped with initial ASIC flow pathfinding. The physical design of the EIC could not have been done without Austin Rovinski's contribution to power planning, I/O placement, redistribution-layer (RDL) routing, and design rule violations fixing. Sung-Gun Cho from Intel also helped significantly with the ASIC flow. Sung-Gun Cho, Sunwoo Lee, and Austin Rovinski made tremendous contributions to fixing the design rule violations. I led the post-silicon testing of the crossbar unit in the EIC. I developed all the post-silicon testing infrastructure and test cases. I verified the SPI configuration unit on an FPGA before the chip was taped out. I conducted unit testing of the crossbar unit. I worked closely with Christine Ou and Devesh Khilwani to conduct integration testing of the crossbar unit and TRX unit. I worked closely with Songli Wang and Yuyang Wang to conduct integration testing of the EIC and PIC.

This thesis was supported in part by DARPA POSH Award #FA8650-18-2-7852, DARPA PIPES Award HR00111920014, DARPA CHIPS Award HR00111830002, DARPA SDH Award #FA8650-18-2-7863, NSF EVE Award #CCF-2008471, NSF PPoSS Award #CCF-2118709, equipment, tool, and/or physical IP donations from Intel, Xilinx, Synopsys, Cadence, and ARM. The U.S. Government is authorized to reproduce and distribute reprints for Government purposes notwithstanding any copyright notation thereon. Any opinions, findings, and conclusions or rec-

ommendations expressed in this publication are those of the author(s) and do not necessarily reflect the views of any funding agency.

# PART I SCALING ON-CHIP INTERCONNECTS

The first part of this thesis focuses on addressing the methodology and architecture challenges in scaling on-chip interconnects. As the demand for processing power continues to grow, manycore architectures have emerged as a solution to enhance parallelism and throughput within a single chip. However, the efficiency of these architectures is heavily dependent on the performance of on-chip interconnects, which play a critical role in facilitating data movement between cores. Scaling on-chip interconnects to accommodate increasing core counts while maintaining low latency, high bandwidth, and energy efficiency poses significant challenges. Part I of the thesis addresses these challenges by presenting new methodologies and architectures that enhance the scalability and performance of OCNs. Chapter 2 presents PyOCN, a unified framework for modeling, testing, and evaluating on-chip interconnects. Chapter 3 proposes practical low-diameter network topologies along with a tiled physical design methodology to effectively implement them and explores their trade-offs using PyOCN. Finally, Chapter 4 details the CIFER chip tape-out, a heterogeneous manycore processor implemented using a tiled physical design methodology and validates the feasibility of the PyOCN framework.

#### CHAPTER 2

# METHODOLOGY: A UNIFIED FRAMEWORK FOR ON-CHIP NETWORKS

There is a growing interest in the open-source hardware movement to amortize non-recurring engineering costs by using plug-and-play system-on-chip (SoC) designs, where the communication among different components is provided by an on-chip interconnection network. Unfortunately, building an on-chip network (OCN) that is suitable for a specific SoC design requires the exploration of a large number of design options and involves diverse research methodologies to evaluate performance, area, energy, and timing. In this chapter, I present PyOCN, a unified framework that vertically integrates multiple research methodologies to enable productively exploring the OCN design space. PyOCN is the first comprehensive framework for modeling (e.g., functional-level, cycle-level, and register-transfer-level), testing (e.g., unit testing, integration testing, and property-based random testing), and evaluating (e.g., simulating, generating, and characterizing) on-chip interconnection networks. We use a case study based on a 64-terminal butterfly network to illustrate the key features of PyOCN and to demonstrate the framework's potential in productively modeling, testing, and evaluating OCNs. PyOCN is further used in developing the OCNs in Chapter 3 and Chapter 4.

### 2.1 Introduction

On-chip networks (OCNs) play a significant role in chip design across many different domains. Embedded SoCs can include tens of homogeneous or heterogeneous cores to meet performance and power requirements [Gre11, TKMP18], high-end cloud servers can include tens to hundreds of cores to enable high-performance computing [Bol12, WKP11], and accelerators can include hundreds of processing elements for domain-specific computing [KTK<sup>+</sup>18, CKES16, CDS<sup>+</sup>14, KSK18]. At the same time, the costs of chip design and verification are rising. In response, there is growing interest in open-source hardware design based on plug-and-play SoC frameworks, where the communication between components is provided by an on-chip interconnection network.

Unfortunately, building an OCN that is suitable for a specific SoC design requires exploring a large design space (e.g., network size, channel bandwidth, topologies, routing algorithms, flow control schemes, arbitration techniques, physical floorplanning, and wire routing) using a combina-

tion of high- and low-level modeling to accurately estimate performance, area, energy, and timing. For example, OCN cycle-level simulators are widely used today and provide rich configuration options for early-stage design-space exploration [APM+12, AKPJ09, CHB+10, JBM+13, TB12]. However, the convenience in using CL models must be balanced against decreased accuracy and no path to real hardware implementations. There are a number of OCN register-transfer-level (RTL) generators that produce synthesizable Verilog to drive an evaluation of area, energy, and timing [cor19,fle19,CP04,PH13,KK17,FFDMS14]. These low-level generators can be difficult to use and lack support for fast simulation. Some OCN design frameworks combine various research methodologies together to facilitate design space exploration [BJM+05,PCSV08]. However, area, energy, and timing characterization in these frameworks is often based on high-level first-order modeling. There is a growing need for a vertically integrated OCN framework that can effectively characterize performance, area, energy, and timing across a large design space.

This paper presents PyOCN, a unified framework for modeling, testing, and evaluating on-chip interconnection networks. The concrete contributions of this work are the following: (1) PyOCN enables multi-level modeling to facilitate rapid design-space exploration and OCN implementation; (2) PyOCN provides sophisticated test harnesses for testing OCN designs modeled at different abstraction levels; (3) PyOCN can simulate OCNs at various abstraction levels, generate synthesizable Verilog, and drive a commercial standard-cell-based toolflow for characterizing OCN area, energy, and timing.

#### 2.2 Related Work

Table 2.1 summarizes the state-of-the-art OCN research methodologies and compares them to PyOCN.

#### 2.2.1 Modeling OCNs

Existing state-of-the-art OCN simulators struggle to balance rapid design-space exploration (requiring high-level design abstractions) and accurate estimation of area, energy, and timing (requiring low-level detailed modeling).

|            |                                    | Modeling           |                                                                  |                                       |    |    |     |    | Testing | g    | Evaluating |      |             | Open-         |        |

|------------|------------------------------------|--------------------|------------------------------------------------------------------|---------------------------------------|----|----|-----|----|---------|------|------------|------|-------------|---------------|--------|

|            | Framework                          | Lang.              | Topology                                                         | Routing                               | FL | CL | RTL | PL | Unit    | Int. | PBT.       | Sim. | RTL<br>Gen. | ASIC<br>Char. | source |

| ion        | BookSim2<br>[JBM <sup>+</sup> 13]  | C++                | Xbar, Ring, (C)Mesh,<br>Butterfly, Torus, Tree                   | DOR,<br>Customized                    | Θ  | •  | Θ   | Θ  | Θ       | Θ    | Θ          | •    | Θ           | Θ             | •      |

| Simulation | Garnet<br>[AKPJ09]                 | C++,<br>Python     | Xbar, Mesh,<br>Customized                                        | DOR,<br>Customized                    | Θ  | •  | Θ   | 0  | Θ       | •    | 9          | •    | Θ           | 9             | •      |

|            | Noxim<br>[CMM <sup>+</sup> 05]     | SystemC            | Mesh, Butterfly,<br>Wireless                                     | DOR, Odd-Even,<br>Dyad routing        | Θ  | •  | Θ   | 0  | 0       | •    | 0          | •    | Θ           | •             | •      |

|            | FlexNoC<br>[fle19]                 | ?                  | Application-<br>specific                                         | n/a                                   | Θ  | Θ  | •   | Θ  | ?       | ?    | ?          | •    | •           | 0             | Θ      |

| Generation | NoCGEN<br>[CP04]                   | HDL                | Mesh, Customized topology                                        | DOR routing                           | Θ  | Θ  | •   | 0  | ?       | ?    | ?          | •    | •           | 0             | Θ      |

| Ger        | Connect<br>[PH13]                  | BSV                | Customized topology                                              | Customized routing                    | Θ  | Θ  | •   | 0  | ?       | ?    | ?          | •    | •           | 9             | •      |

|            | OpenPiton<br>[BMF <sup>+</sup> 16] | Verilog            | Xbar,<br>Mesh                                                    | DOR routing                           | Θ  | 0  | •   | 0  | Θ       | •    | 0          | •    | •           | •             | •      |

|            | Netmaker<br>[net19]                | System-<br>Verilog | Mesh                                                             | DOR routing                           | Θ  | Θ  | •   | 0  | 0       | •    | 0          | •    | •           | 0             | •      |

|            | OpenSMART<br>[KK17]                | BSV<br>Chisel      | Mesh, Customized topology                                        | DOR, Source routing                   | Θ  | Θ  | •   | 0  | •       | •    | 0          | •    | •           | 0             | •      |

|            | OpenSoC Fabric<br>[FFDMS14]        | Chisel             | Mesh, Flattened<br>butterfly                                     | DOR routing,<br>Concentration         | Θ  | •  | •   | 0  | •       | •    | 0          | •    | •           | 0             | •      |

|            | DSENT<br>[SCK <sup>+</sup> 12]     | C++                | n/a                                                              | n/a                                   | Θ  | Θ  | Θ   | Θ  | Θ       | Θ    | Θ          | Θ    | Θ           | •             | •      |

| Charact.   | Orion2.0<br>[KLPS09]               | C++                | n/a                                                              | n/a                                   | Θ  | Θ  | Θ   | 9  | Θ       | Θ    | Θ          | Θ    | Θ           | •             | •      |

|            | COSI<br>[PCSV08]                   | C++                | Application-<br>specific                                         | n/a                                   | 9  | •  | •   | •  | Θ       | Θ    | 9          | •    | •           | •             | •      |

|            | NetChip<br>[BJM <sup>+</sup> 05]   | SystemC            | Application-<br>specific                                         | n/a                                   | Θ  | •  | •   | 0  | ?       | ?    | ?          | •    | •           | •             | Θ      |

|            | PyOCN                              | PyMTL              | Xbar, Ring, (C)Mesh,<br>Butterfly, Torus,<br>Customized topology | DOR, Source,<br>Customized<br>routing | •  | •  | •   | •  | •       | •    | •          | •    | •           | •             | •      |

**Table 2.1:** Comparison with Prior Art – Different state-of-the-art research methodologies for designing OCNs, which are categorized into three groups (i.e., Simulation, Generation, and Characterization).  $\bigcirc$ ,  $\bigcirc$ , and  $\bigcirc$  indicate the corresponding feature is not supported, partially supported, and fully supported, respectively. For example, OpenSoC Fabric can generate synthesizable Verilog ( $\bigcirc$ ) but relies on VCS for simulation ( $\bigcirc$ ). In contrast, the simulation in PyOCN allows the test bench to be written in Python and eliminates any semantic gap. Lang. = language; FL = functional level; CL = cycle level; RTL = register-transfer level; PL = physical level; Unit = unit testing; Int. = integration testing; PBT. = property-based random testing; Sim. = simulation; RTL Gen. = RTL generation; ASIC Char. = ASIC characterization.

Cycle-Level Modeling – Many widely used on-chip network simulators use CL modeling for early design-space exploration while verifying functional- and cycle-level behavior [APM<sup>+</sup>12, AKPJ09, CHB<sup>+</sup>10, JBM<sup>+</sup>13, TB12, LSC<sup>+</sup>10]. Unfortunately, these simulators do not support RTL modeling and cannot easily generate synthesizable Verilog, which is essential for accurate evaluation of area, energy, and timing. As an exception, Noxim [CMM<sup>+</sup>05] is a cycle-level OCN simulator developed in SystemC with some capacity for power estimation. All basic elements of the OCN in Noxim are also modeled in VHDL and are synthesized with a 65 nm CMOS standard cell library at 1GHz to provide statistical power analysis.

**Register-Transfer-Level Modeling** – On the other hand, OCN generators use RTL modeling to accurately characterize area, energy, and timing, but they lack the high-level design abstractions that enable fast design-space exploration [CP04, PH13, KK17]. For example, OpenS-MART [KK17] is an OCN RTL generator for a wide range of different network configurations. Unfortunately, simulating generated RTL can easily limit rapid design-space exploration over large parameter space.

**Physical-Level Modeling** – Finally, OCN frameworks rarely take physical-level (PL) modeling considerations into account (e.g., macro- and micro-floorplanning), which is critical for effectively building complex OCNs. One exception is SUNMAP [MM04], which enables PL modeling in OCN generation and uses a floorplanning algorithm [AM03] to minimize the estimated area and wire lengths for specific applications.

#### 2.2.2 Testing OCNs