# Accelerating AWP-ODC for Large-scale Earthquake Simulations Using MVAPICH2

*Akash Palla<sup>1</sup>, Shijie Wang<sup>1</sup>, Shuzheng Zhang<sup>1</sup>, Yifeng Cui<sup>2</sup>*

<sup>1</sup>*University of California, San Diego, <sup>2</sup>San Diego Supercomputer Center*

## Summary

Accurate simulation of earthquake scenarios is essential for advancing seismic hazard analysis and risk mitigation strategies. At the San Diego Supercomputer Center (SDSC), our research focuses on optimizing the performance and reliability of large-scale earthquake simulations using the AWP-ODC software. By implementing GPU-aware MPI calls, we enable direct data processing within GPU memory, eliminating the need for explicit data transfers between CPU and GPU. This GPU-aware MPI achieves nearly ideal parallel efficiency at full scale across both Nvidia and AMD GPUs, leveraging the MVAPICH-Plus 4.0 support on Frontier at Oak Ridge National Laboratory (ORNL) and Vista at the Texas Advanced Computing Center (TACC).

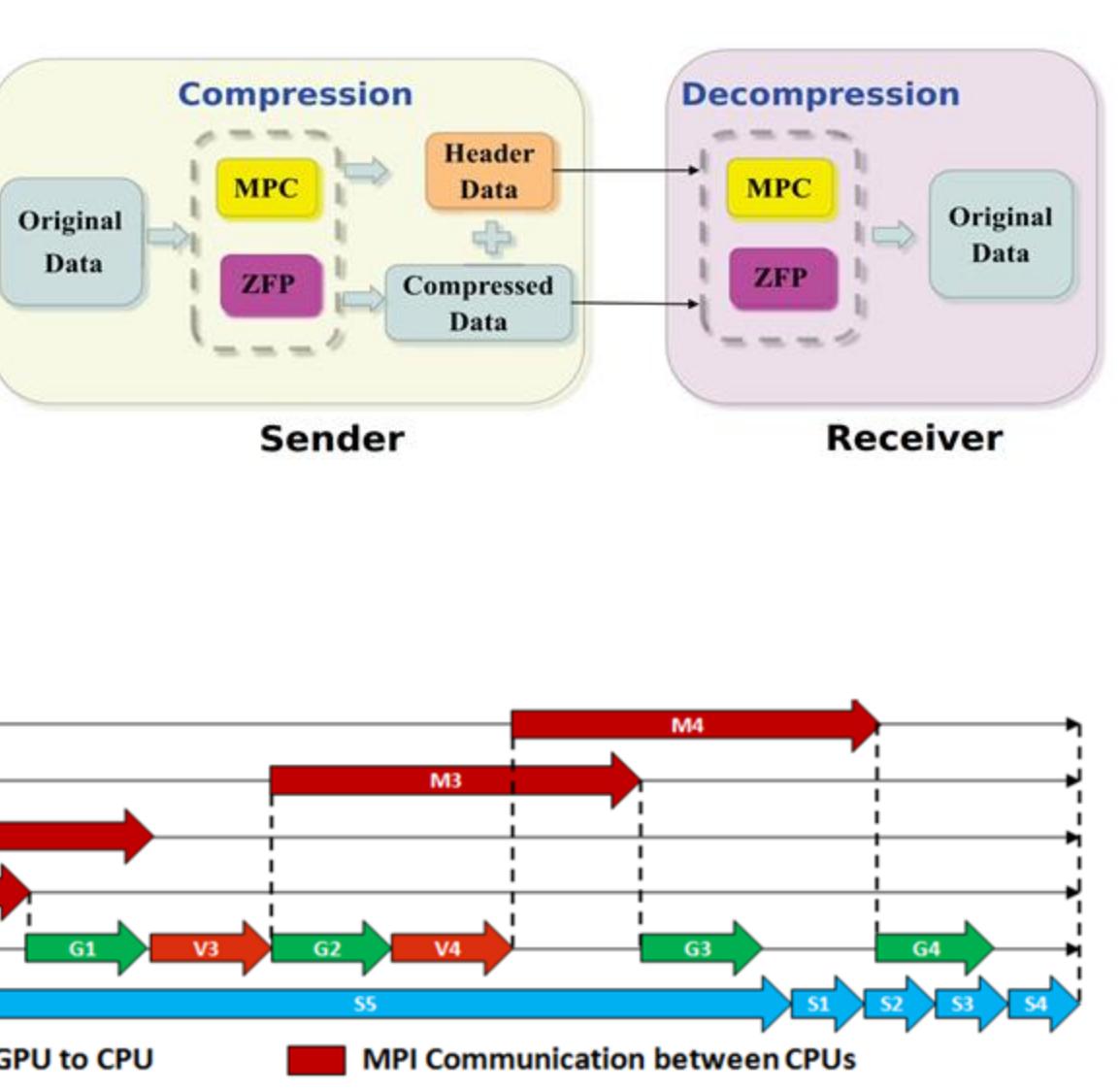

We utilized the MVAPICH-Plus 4.0 compiler to enable on-the-fly ZFP compression, which significantly enhanced inter-node communication efficiency - a critical improvement given the communication bottleneck inherent in large-scale simulations. Our GPU-aware AWP-ODC versions include linear forward, topography and nonlinear Iwan-type solvers with discontinuous mesh support.

On the Frontier system with MVAPICH 4.0, Hip-aware MPI calls on AMD's MI250X GPUs deliver nearly ideal weak-scaling speedup up to 8,192 nodes for both linear and topography versions. On TACC's Vista system, CUDA-aware MPI calls on GH200 GPU substantially outperform their non GPU-aware counterparts across all three solver versions. Our results highlight the importance of MPI library MVAPICH support for accelerating and scaling earthquake simulations.

## Accelerating AWP-ODC with GPU-Aware on OLCF Frontier MI250X

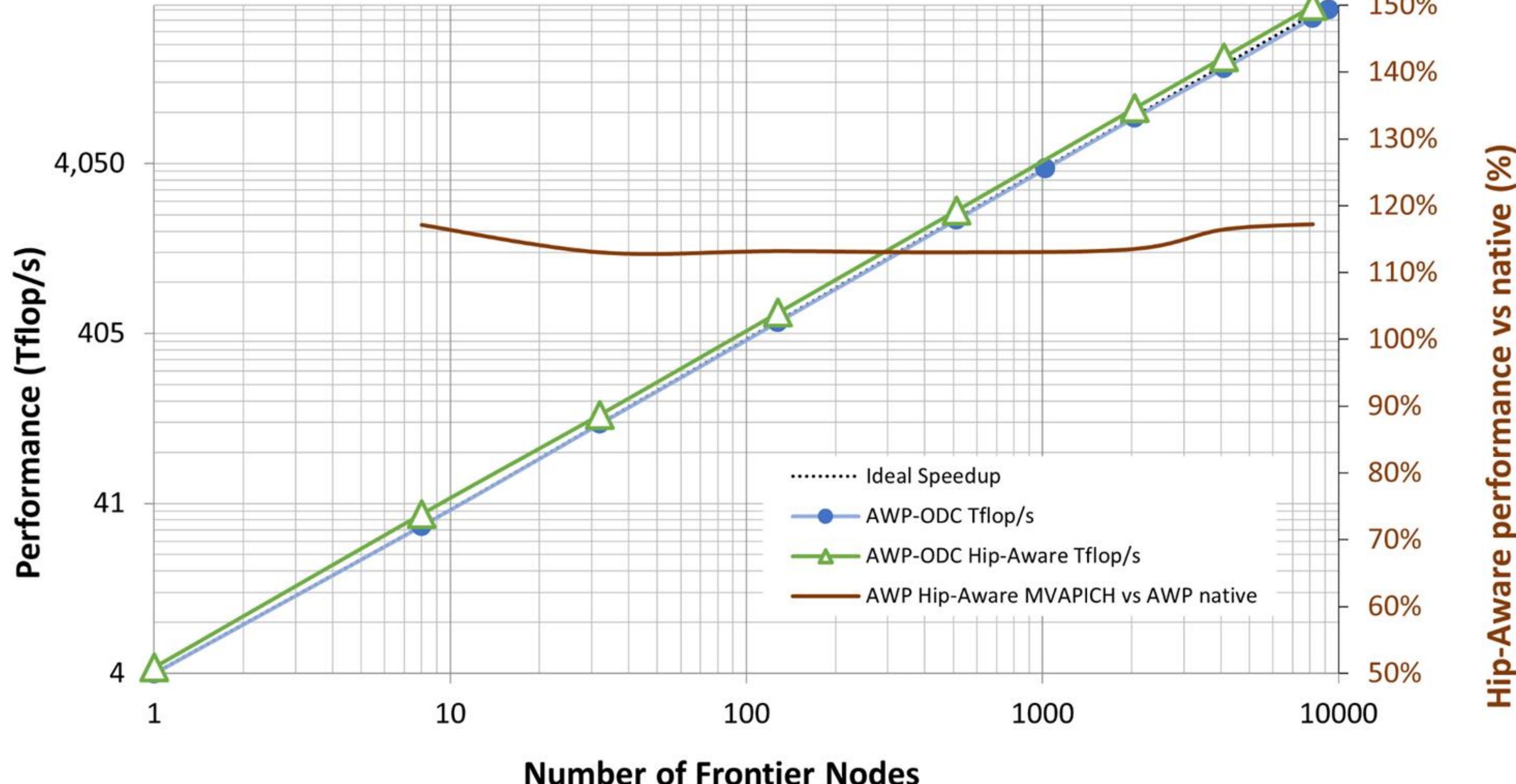

Frontier<sup>7</sup> at ORNL is the current No. 2 system in the June 2025 TOP500 list. This system is based on the AMD Instinct GPUs and EPYC CPUs, and it is the first US system with a peak performance exceeding one ExaFlop/s<sup>5</sup>. By porting AWP-ODC linear code to HIP, we saw performance uplifts with MVAPICH-Plus 4.0 using HIP-Aware GDR on the MI250X GPU nodes. We observed consistent speedup when compared to the native code in weak scaling tests, especially pronounced in larger and full-machine scales.

AWP-ODC performance with MVAPICH on OLCF Frontier

| Frontier | AWP Native (MVAPICH) |                     |             | AWP hip-aware (MVAPICH) |                     |                | Frontier |

|----------|----------------------|---------------------|-------------|-------------------------|---------------------|----------------|----------|

|          | AWP Tflop/s          | Parallel efficiency | AWP speedup | frontier Tflop/s        | Parallel efficiency | AWP enhanced % |          |

| nodes    |                      |                     |             | frontier                | Parallel            | AWP enhanced % | GCDs     |

| 1        | 4.05                 | 100.00%             | 8           | 4.39                    | 100.0%              | 8              | 64       |

| 8        | 29.88                | 100.00%             | 8           | 34.99                   | 100.0%              | 8              | 117.1%   |

| 16       |                      |                     |             |                         |                     |                | 128      |

| 32       | 119.07               | 99.62%              | 32          | 134.58                  | 96.2%               | 31             | 113.0%   |

| 64       |                      |                     |             |                         |                     |                | 256      |

| 128      | 473.58               | 99.06%              | 127         | 536.16                  | 95.8%               | 123            | 113.2%   |

| 256      |                      |                     |             |                         |                     |                | 1024     |

| 512      | 1,890.00             | 98.83%              | 506         | 2,136.19                | 95.4%               | 488            | 113.0%   |

| 1024     | 3,782.54             | 98.90%              | 1013        |                         |                     |                | 4096     |

| 2048     | 7,536.58             | 98.53%              | 2018        | 8,556.30                | 95.5%               | 1956           | 113.5%   |

| 4096     | 14,690.31            | 96.02%              | 3933        | 17,103.55               | 95.5%               | 3910           | 116.4%   |

| 8192     | 29,168.14            | 95.33%              | 7809        | 34,185.33               | 95.4%               | 7816           | 117.2%   |

Weak-scaling test benchmark results for AWP-ODC linear code performance on ORNL Frontier using MVAPICH-Plus 4.0 at a scale of 600x560x200 per node of 8 MI250X each. A GDR with ZFP version was also tested at lower node counts, but no improvement was found over GDR alone, as the faster NIC on Frontier provides up to 800 Gbps of bandwidth<sup>3</sup>, rendering the transfer of uncompressed data to be faster than the compression and decompression speed.

## Acknowledgements

Shijie Wang and Shuzheng Zhang acknowledges the support provided by the MUG'25 Conference through the travel grant through funding from the U.S. NSF. We thank for the funding supports provided by the NSF under Award # 2311833, the NSF CSA program under Award #2139536, and SCEC RSA #162830509. The authors thank Dr. Ossian O'Reilly of AMD for providing HIP porting advice as well as providing help in debugging the CUDA-Aware implementation for topography code, and Prof. DK Panda NOWL team of OSU, including Lang Xu, along with Dr. Te-Yang Yeh of SDSU, for CUDA-Aware and on-the-fly message compression support. The authors thank Dr. Sameer Shende in providing technical guidance in using TAU profiling to identify bottlenecks of AWP-ODC. The authors acknowledge OLCF for INCITE allocation; TACC for Vista allocation and CSA allocation.

## References

- [1] Cui, Y., D. Roten, A. Palla, A. Govind, S. Callaghan, M. Norman, L. Koesterke, W. Zhang and P. Maechling. Progress of porting AWP-ODC to next generation HPC architectures and a 4-Hz Iwan-type nonlinear dynamic simulation of the ShakeOut scenario on TACC Frontera, Sept 11-13, Palm Springs, 2023.

- [2] Cui, Y., Extreme-scale Earthquake simulation with MVAPICH, MUG'23, Columbus, Aug 21-23, 2023.

- [3] OLCF Frontier User Guide: <https://www.olcf.ornl.gov/frontera/>

- [4] TACC Vista User Guide: <https://docs.tacc.utexas.edu/hpc/vista/>

- [5] Q. Zhou, C. Chu, N. S. Kumar, P. Kousha, S. M. Ghazimirsaeed, H. Subramoni and D. K. Panda. Designing High-Performance MPI Libraries with On-the-fly Compression for Modern GPU Clusters\*, 2021.

- [6] Dhabaleswar K. (DK) Panda (OSU), Co-PIs: Sameer Shende (UO), Ahmad Abdelfattah (UTK), Yifeng Cui (SDSC). CSSI Frameworks: Performance Engineering Scientific Applications with MVAPICH and TAU using Emerging Communication Primitives, NSF SSPI Meeting, Jul 27-29, Denver, 2025.

## Accelerating Iwan AWP-ODC with ZFP Compression on TACC Vista GH200

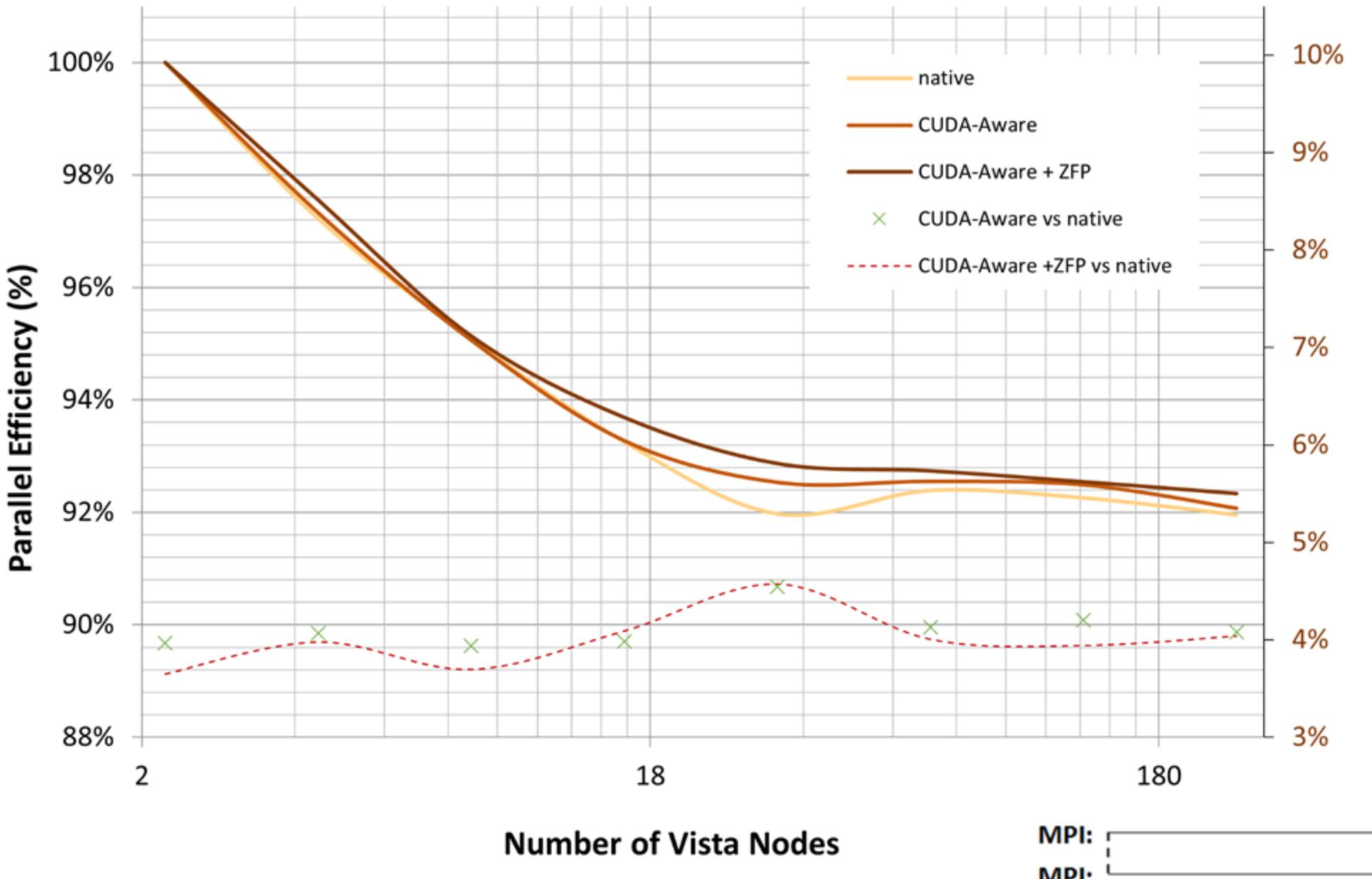

We have implemented the CUDA version of AWP-ODC with Iwan landscape modeling that can run on TACC Vista with GH200 GPUs. CUDA-aware feature has been implemented to the Iwan version of AWP-ODC, leveraging GPU-Direct RDMA (GDR) for enhanced data transfer efficiency between GPUs. We tested AWP-ODC-Iwan with on-the-fly ZFP compression feature of Mvapich-Plus 4.0 and verified its correctness. With the use of ZFP compression and CUDA-Aware MPI calls, AWP-ODC is able to achieve a maximum of 4.1% enhanced performance as shown in the table below.

Vista at TACC is a next-generation, AI-focused supercomputer that bridges TACC's CPU-based Frontera system and the upcoming Horizon exascale system. It is built around ARM-based NVIDIA Grace Hopper (GH200) and dual Grace Superchip nodes, and the nodes are interconnected through Infiniband network<sup>4</sup>.

Iwan AWP-ODC benchmarks on TACC Vista with 45x45x80,128,192 per GPU

| Vista | AWP Native (MVAPICH) |            |                     | AWP GDR (MVAPICH) |                     |             | AWP GDR (MVAPICH ZFP) |                     |             |

|-------|----------------------|------------|---------------------|-------------------|---------------------|-------------|-----------------------|---------------------|-------------|

|       | nodes                | vista time | parallel efficiency | vista time        | parallel efficiency | % vs native | vista time            | parallel efficiency | % vs native |

| 1     | 0.0328               | 100.00%    | 0.0326              | 100.00%           | 3.46%               | 100.00%     | 0.0317                | 100.00%             | 3.15%       |

| 2     | 0.0338               | 97.22%     | 0.0335              | 97.32%            | 3.57%               | 100.00%     | 0.0335                | 97.55%              | 3.48%       |

| 4     | 0.0347               | 95.09%     | 0.0343              | 95.06%            | 3.44%               | 100.00%     | 0.0344                | 95.13%              | 3.19%       |

| 8     | 0.0355               | 93.26%     | 0.0349              | 93.27%            | 3.48%               | 100.00%     | 0.0349                | 93.68%              | 3.59%       |

| 16    | 0.0362               | 91.98%     | 0.0352              | 92.53%            | 4.04%               | 100.00%     | 0.0352                | 92.86%              | 4.07%       |

| 32    | 0.0367               | 92.39%     | 0.0352              | 92.55%            | 3.63%               | 100.00%     | 0.0353                | 92.73%              | 3.51%       |

| 64    | 0.0365               | 92.26%     | 0.0352              | 92.49%            | 3.70%               | 100.00%     | 0.0353                | 92.54%              | 3.44%       |

| 128   | 0.0366               | 92.26%     | 0.0352              | 92.49%            | 3.70%               | 100.00%     | 0.0354                | 92.33%              | 3.54%       |

| 256   | 0.0367               | 91.96%     | 0.0354              | 92.07%            | 3.58%               | 100.00%     | 0.0354                | 92.33%              | 3.54%       |

AWP-ODC-Iwan Parallel Efficiency with MVAPICH on TACC Vista

In contrast to the performance of AWP-ODC-Iwan on OLCF Frontier with MI250X GPUs, AWP-ODC-Iwan gained less performance on TACC Vista using GPU-Aware MPI calls. This is primarily due to faster data transfer between CPU and GPU connected via 900 GB/s NVLink<sup>4</sup> in Vista's GH200 node, compared to the 36 GB/s Infinity Fabric<sup>3</sup> in Frontier's MI250X node. Faster data transfer lowers the effect for eliminating explicit data transfer between CPU and GPU.

On-the-fly ZFP Message Compression in Mvapich-Plus 4.0 MPI Library<sup>5</sup>

\*Diagram made by Zhou, Q et al<sup>5</sup>

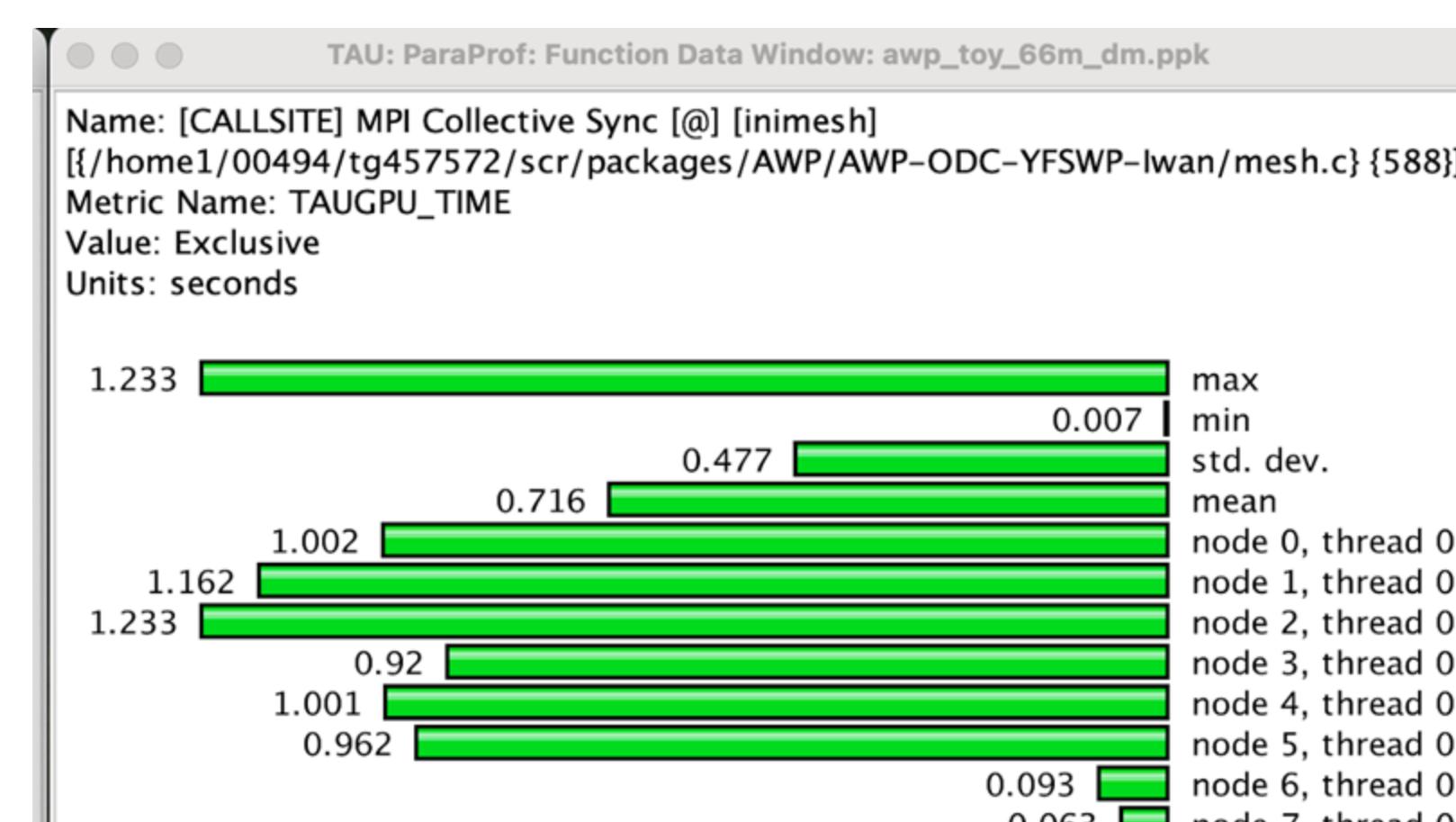

TAU Profiling result of MPI Calls in Iwan AWP-ODC<sup>6</sup> (courtesy of Dr. Shende, UO)

Profiling AWP-ODC Iwan testcase on Vista at TACC with TAU showing the time spent in a collective operation stalled at an MPI Barrier call across multiple MPI ranks<sup>6</sup>.

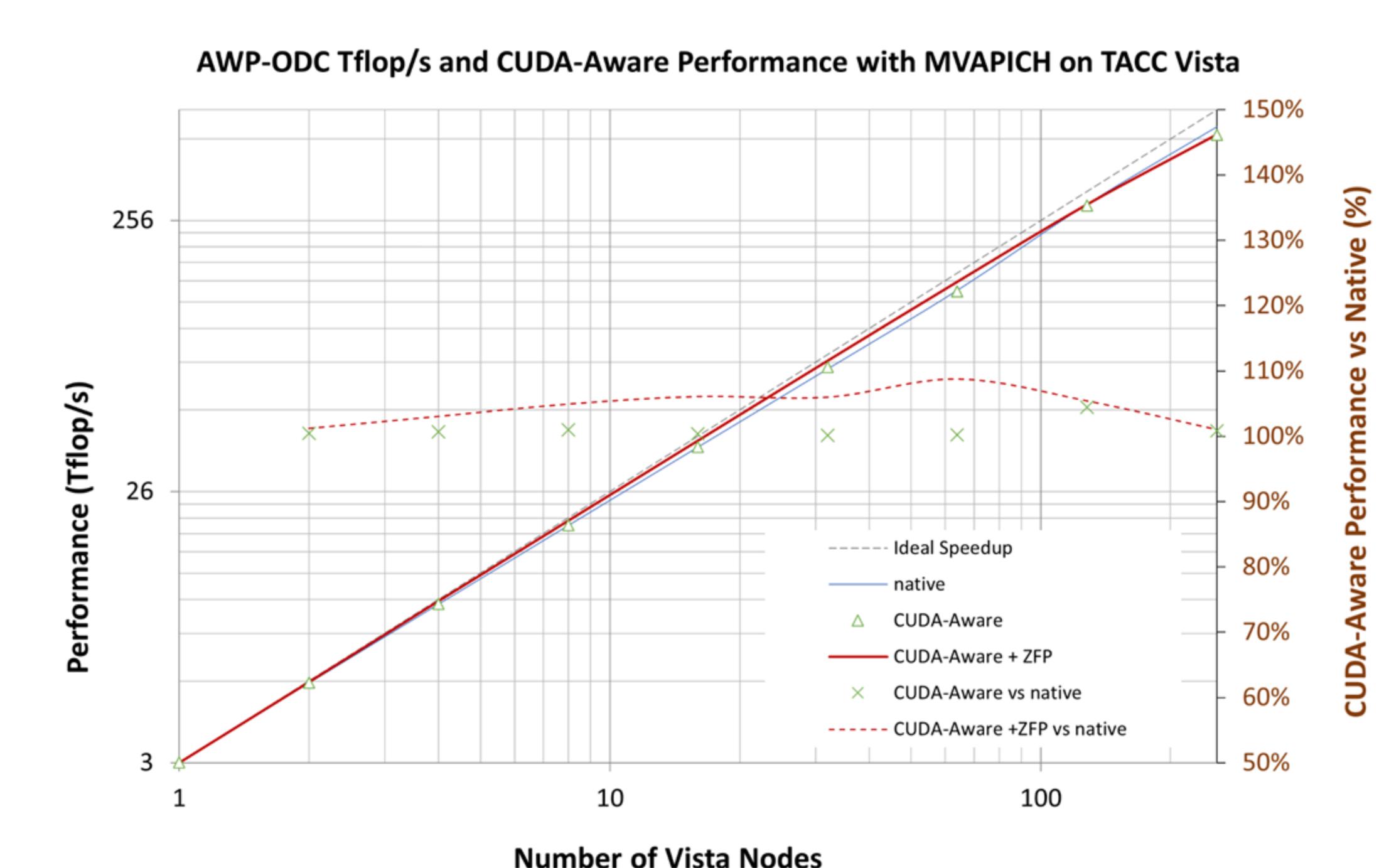

## Accelerating Linear AWP-ODC with ZFP Compression on TACC Vista GH200

We have implemented the CUDA version of linear AWP-ODC that can run on TACC Vista with GH200 GPUs. GPU-aware feature has been implemented to the linear version of AWP-ODC, leveraging GPU-Direct RDMA (GDR) for enhanced data transfer efficiency between GPUs. We tested AWP-ODC-Iwan with on-the-fly ZFP compression feature of Mvapich-Plus 4.0 and verified its correctness.

Linear AWP-ODC on TACC Vista, with 82% parallel efficiency on 256-nodes scale.

Linear AWP-ODC Benchmarks on TACC Vista with 45x45x80,128,192 per GPU

| Vista | AWP Native (MVAPICH) |               |                     | AWP GDR (MVAPICH) |                     |             | AWP GDR (MVAPICH ZFP) |                     |             |

|-------|----------------------|---------------|---------------------|-------------------|---------------------|-------------|-----------------------|---------------------|-------------|

|       | nodes                | vista Tflop/s | parallel efficiency | vista Tflop/s     | parallel efficiency | % vs native | vista Tflop/s         | parallel efficiency | % vs native |

| 1     | 2.57                 |               |                     | 2.57              |                     |             | 2.56                  |                     | </td        |