**Systems for electromigration study under frequency effect and non-uniform thermal effect:

design, fabrication, and testing**

by

**Srijita Patra**

A dissertation submitted to the graduate faculty

in partial fulfillment of the requirements for the degree of

**DOCTOR OF PHILOSOPHY**

Major: Electrical Engineering

Program of Study Committee:

Ratnesh Kumar, Major Professor

Long Que

Mani Mina

Meng Lu

Cheng Huang

The student author, whose presentation of the scholarship herein was approved by the program of

study committee, is solely responsible for the content of this dissertation.

The Graduate College will ensure this dissertation is globally accessible and will not permit

alterations after a degree is conferred.

Iowa State University

Ames, Iowa

2024

Copyright © Srijita Patra, 2024. All rights reserved.

## **DEDICATION**

*To my family, friends who held me up over the years with their endless love*

*Deeply grateful to God for blessing me with this life*

## TABLE OF CONTENTS

|                                                                           | Page |

|---------------------------------------------------------------------------|------|

| LIST OF FIGURES .....                                                     | v    |

| ACKNOWLEDGMENTS .....                                                     | viii |

| ABSTRACT.....                                                             | ix   |

| CHAPTER 1. GENERAL INTRODUCTION.....                                      | 1    |

| 1.1 <i>Background</i> .....                                               | 1    |

| 1.2 <i>Motivation for this work</i> .....                                 | 2    |

| 1.3 <i>Thesis Organization</i> .....                                      | 3    |

| 1.4 <i>References</i> .....                                               | 4    |

| CHAPTER 2. ELECTROMIGRATION: A REVIEW, WITH OVERVIEW OF OTHER IC FAILURES |      |

| 2.1 <i>Abstract</i> .....                                                 | 5    |

| 2.2 <i>Introduction: Various IC Failures</i> .....                        | 6    |

| 2.2.1. Hot Carrier Injection (HCI) .....                                  | 8    |

| 2.2.2. Bias Temperature Instability (BTI) .....                           | 9    |

| 2.2.3. Time Dependent Dielectric Breakdown (TDDB) .....                   | 10   |

| 2.2.4. Soft Error Rate (SER) .....                                        | 11   |

| 2.3 <i>Electromigration</i> .....                                         | 13   |

| 2.3.1. EM Fundamentals .....                                              | 14   |

| 2.3.2. Grain and Surface Boundary Effects .....                           | 16   |

| 2.3.3. EM Flux Divergence Effects.....                                    | 18   |

| 2.3.4. Current Distribution Effects.....                                  | 19   |

| 2.4 <i>Electromigration Quantifications</i> .....                         | 20   |

| 2.4.1. Black's Model .....                                                | 20   |

| 2.4.2. EM Induced Material Transport Equations.....                       | 22   |

| 2.4.3. Blech's Model .....                                                | 25   |

| 2.4.4. Kirchheim's Model .....                                            | 28   |

| 2.4.5. Korhonen's Model .....                                             | 31   |

| 2.4.6. EM Void Induced Effects .....                                      | 37   |

| 2.4.6.1. .....                                                            | 37   |

| 2.5 <i>Other Stress Effects on EM</i> .....                               | 39   |

| 2.5.1. Thermal Migration (TM) .....                                       | 39   |

| 2.5.2. Stress Migration (SM).....                                         | 40   |

| 2.5.3. Frequency Effects on EM .....                                      | 42   |

| 2.6. <i>EM Reduction Methodology</i> .....                                | 44   |

| 2.6.1. Reservoir Effects .....                                            | 44   |

| 2.6.2. Double/Multiple Vias .....                                         | 45   |

| 2.7. <i>EM Tools For Physical Design Flow</i> .....                       | 46   |

| 2.8. <i>Conclusion</i> .....                                              | 48   |

|                                                                       |    |

|-----------------------------------------------------------------------|----|

| 2.9 <i>References</i> .....                                           | 50 |

| CHAPTER 3. NOVEL TEST CHIPS FOR ELECTROMIGRATION FAILURE              |    |

| CHARACTERIZATION FROM DC TO GHz FREQUENCIES .....                     | 62 |

| 3.1 <i>Abstract</i> .....                                             | 62 |

| 3.2 <i>Introduction</i> .....                                         | 62 |

| 3.3 <i>Circuit Based EM Structures</i> .....                          | 65 |

| 3.3.1 Unidirectional Pulsed DC Test Structure .....                   | 68 |

| 3.3.2 Bidirectional Pulsed AC Test Structure.....                     | 69 |

| 3.4 <i>Testing Methodology</i> .....                                  | 71 |

| 3.5 <i>Measurement Results and Discussion</i> .....                   | 72 |

| 3.5.1 On Die Heater Thermal Simulation .....                          | 72 |

| 3.5.2 On Die Heater Measurement .....                                 | 72 |

| 3.5.3 Stress Temperature Consistency Test.....                        | 73 |

| 3.5.4 EM DUT Failure Under Pulsed DC Stress .....                     | 74 |

| 3.5.5 Physics Explanation of EM DUT MTTF Under Pulsed DC Stress ..... | 77 |

| 3.5.6 EM DUT Failure Under Pulsed AC Stress.....                      | 78 |

| 3.6 <i>Conclusion</i> .....                                           | 78 |

| 3.7 <i>References</i> .....                                           | 79 |

| CHAPTER 4. NON-UNIFORM HEATING INDUCED ELECTROMIGRATION FAILURE       |    |

| CHARACTERIZATION USING LASER.....                                     | 82 |

| 4.1 <i>Abstract</i> .....                                             | 82 |

| 4.2 <i>Introduction</i> .....                                         | 82 |

| 4.3 <i>Non- Uniform Heating Based Electromigration</i> .....          | 84 |

| 4.4 <i>Traditional EM Test Structure</i> .....                        | 86 |

| 4.5 <i>Laser based Spot- Heating Set Up</i> .....                     | 87 |

| 4.6 <i>Results and Discussions</i> .....                              | 89 |

| 4.7 <i>Conclusion</i> .....                                           | 95 |

| 4.8 <i>References</i> .....                                           | 95 |

| CHAPTER 5. GENERAL CONCLUSION .....                                   |    |

|                                                                       | 97 |

## LIST OF FIGURES

|                                                                                                                                                                                                                                                                                        | Page      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| <i>Figure 2.1. Classical bathtub failure rate curve observed in semiconductor industries .....</i>                                                                                                                                                                                     | <i>7</i>  |

| <i>Figure 2.2. HCI mechanism in a semiconductor device (NMOS) .....</i>                                                                                                                                                                                                                | <i>9</i>  |

| <i>Figure 2.3. NBTI mechanism in a PMOS device .....</i>                                                                                                                                                                                                                               | <i>10</i> |

| <i>Figure 2.4. TDDB effect in devices .....</i>                                                                                                                                                                                                                                        | <i>11</i> |

| <i>Figure 2.5. Neutron and alpha based SER mechanism .....</i>                                                                                                                                                                                                                         | <i>12</i> |

| <i>Figure 2.6. Two factors influence the metal ions (Cu) constituting the lattice of the interconnect material; EM is the result of the prevailing force, the transfer of momentum from electrons moving within the applied electric field E .....</i>                                 | <i>15</i> |

| <i>Figure 2.7. Hillock and void formations in metal interconnect due to EM (left, photography courtesy of G. H. Bernstein und R. Frankovic, University of Norte Dame) .....</i>                                                                                                        | <i>16</i> |

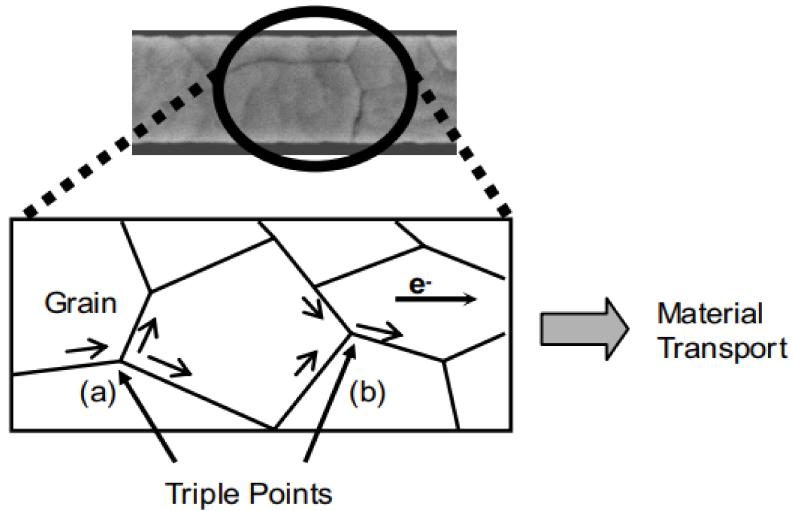

| <i>Figure 2.8. Movement of metal atoms via various diffusion paths .....</i>                                                                                                                                                                                                           | <i>17</i> |

| <i>Figure 2.9. Paths of diffusion at triple junctions result in the formation of (a) voids (b) hillocks</i>                                                                                                                                                                            | <i>18</i> |

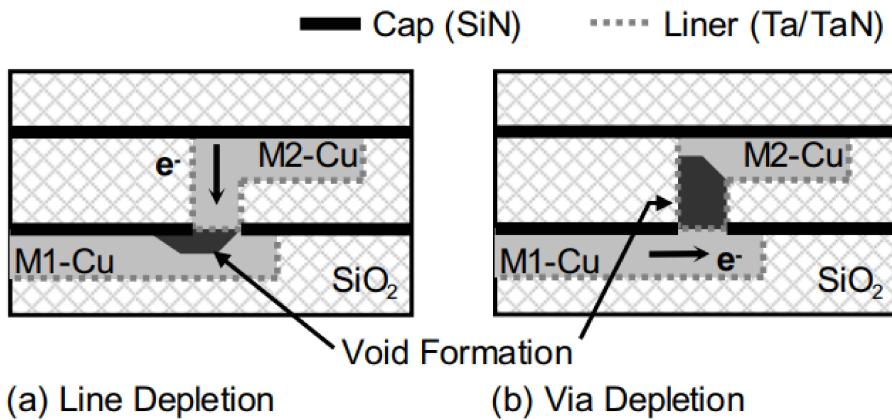

| <i>Figure 2.10. Depletion of lines and vias in metal line .....</i>                                                                                                                                                                                                                    | <i>19</i> |

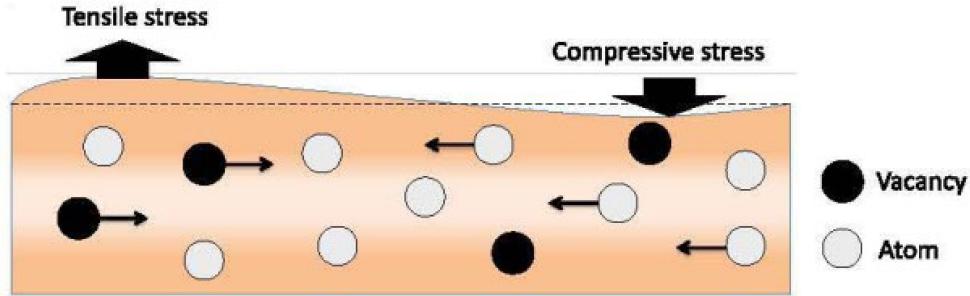

| <i>Figure 2.11. Stress migration is a byproduct of EM and involves the migration of vacancies. It occurs in response to a hydrostatic stress gradient and acts as a back stress opposing the effect of forward migration caused by EM .....</i>                                        | <i>25</i> |

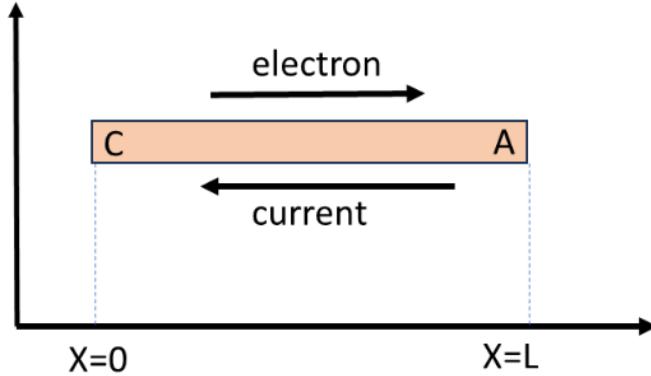

| <i>Figure 2.12. A two-terminal metal line with electron flow and current flow indicated by the arrow. ....</i>                                                                                                                                                                         | <i>26</i> |

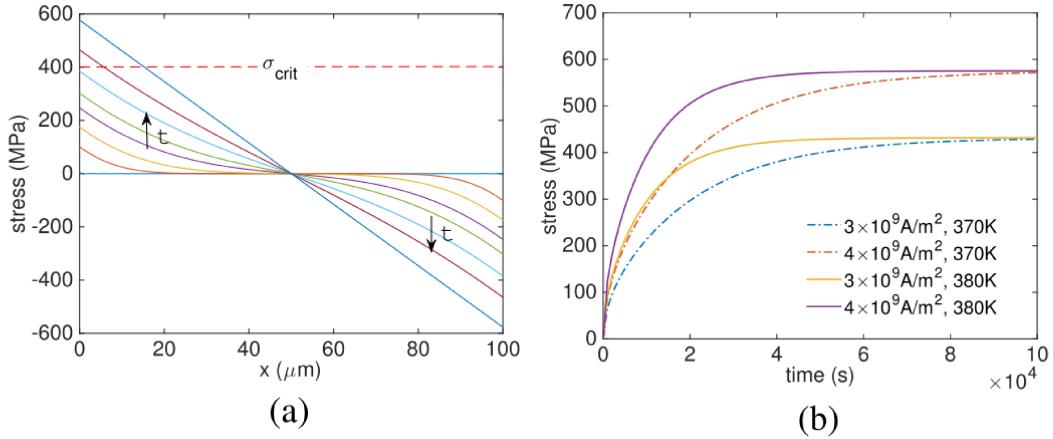

| <i>Figure 2.13. Development of hydrostatic stress within the wire, (a) at cathode, (b) over time when subjected to varying current densities and temperatures, assuming no initial stress .....</i>                                                                                    | <i>35</i> |

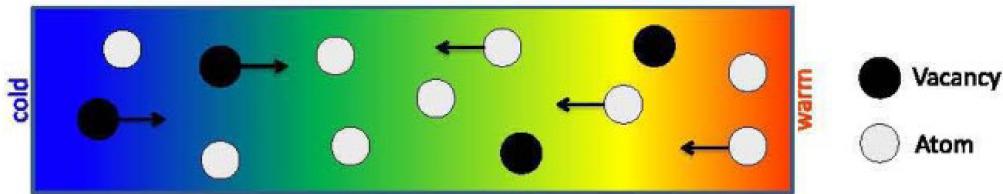

| <i>Figure 2.14. Thermal migration (TM) involves the movement of atoms and vacancies, leading to mass transport from one localized region to another, similar to EM, but TM is driven by a thermal gradient, as opposed to an electrical potential gradient in the case of EM .....</i> | <i>40</i> |

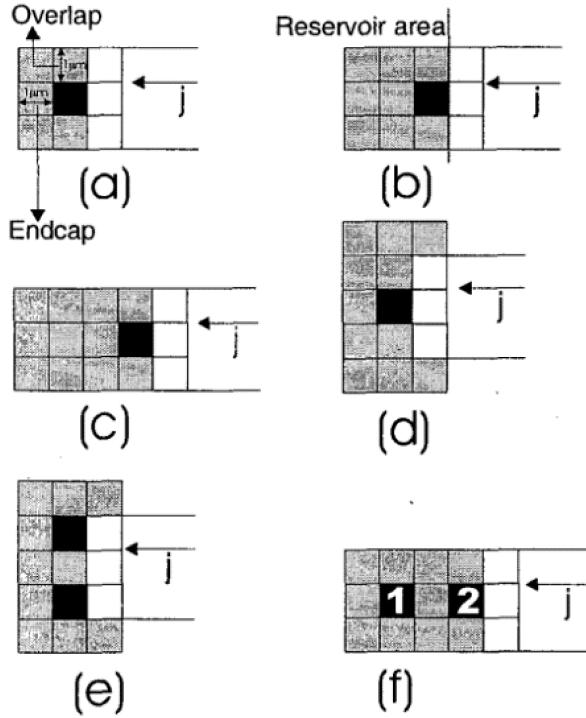

| <i>Figure 2.15. Metal-Via structures with single and two via contacts while reservoir area and overlap are varying. The reservoir is placed upstream with respect to the electron flow .....</i>                                                                                       | <i>45</i> |

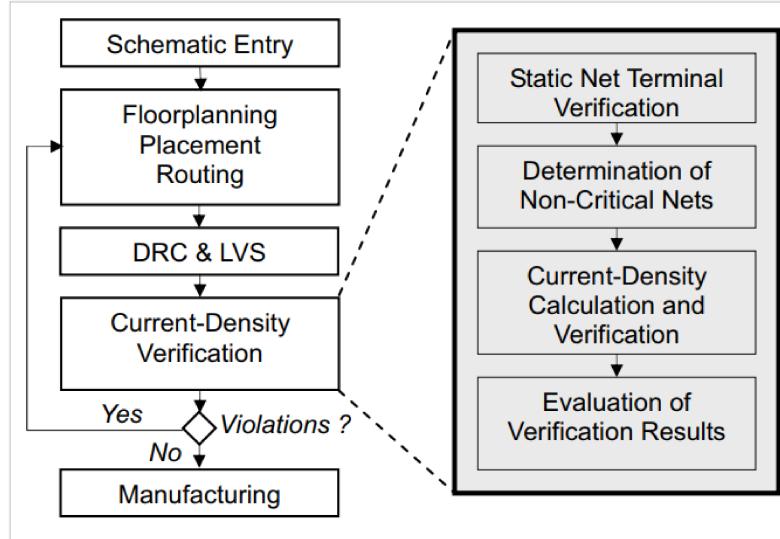

| <i>Figure 2.16. EM failure check via Current density verification flow.....</i>                                                                                                                                                                                                        | <i>47</i> |

|                                                                                                                                                                                                                                                                                                                                                                                               |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

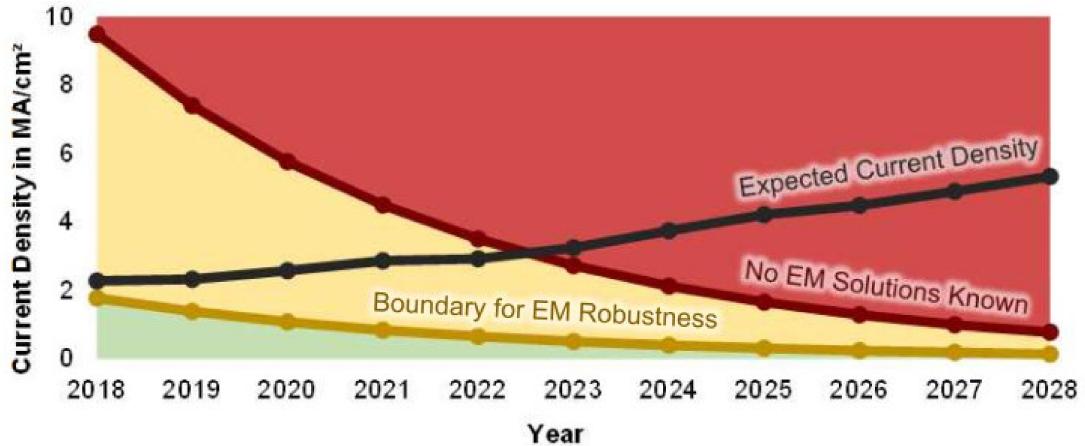

| <i>Figure 2.17. Current densities and electromigration (EM) boundary values were forecasted in the 2015 ITRS [108]. The green area represents a zone with no risk of EM degradation, while the yellow area indicates where EM degradation is possible but manageable. In the red area, however, EM degradation occurs, and no known solutions exist for designing EM-robust layouts. ....</i> | 49 |

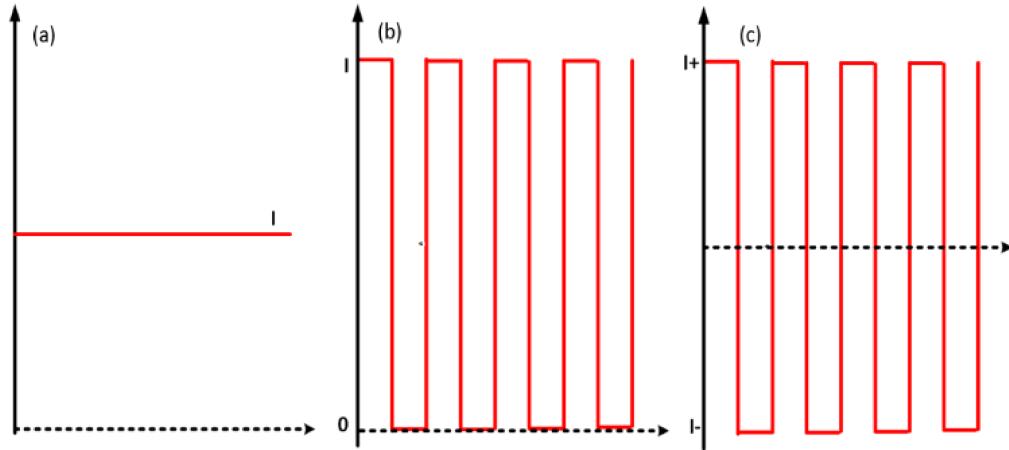

| <i>Figure 3.1. EM stress used in our testing (a) DC current (b) unidirectional pulsed DC current (pulsed DC) with 50% duty cycle (c) bidirectional pulsed AC (pulsed AC) current with 50% duty cycle. ....</i>                                                                                                                                                                                | 65 |

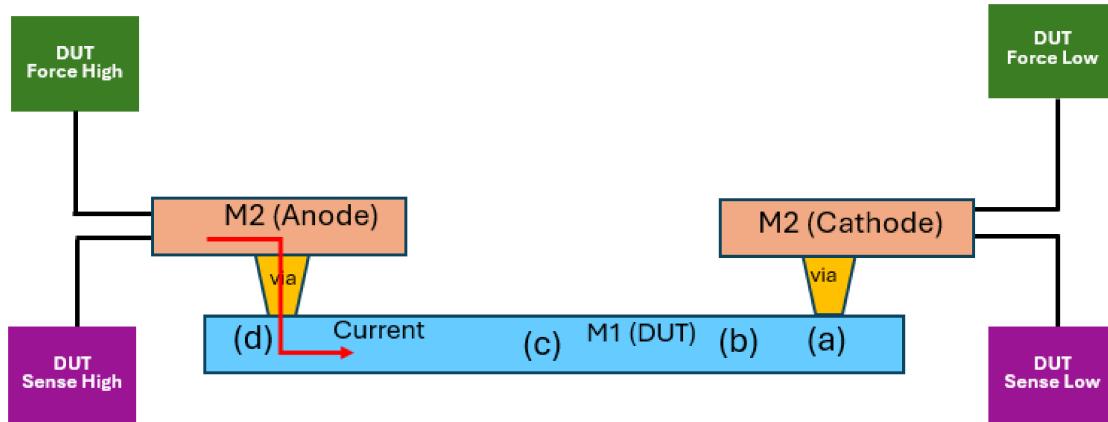

| <i>Figure 3.2. EM DUT configuration, current from CMOS circuit arrives at anode and flowing to cathode. ....</i>                                                                                                                                                                                                                                                                              | 66 |

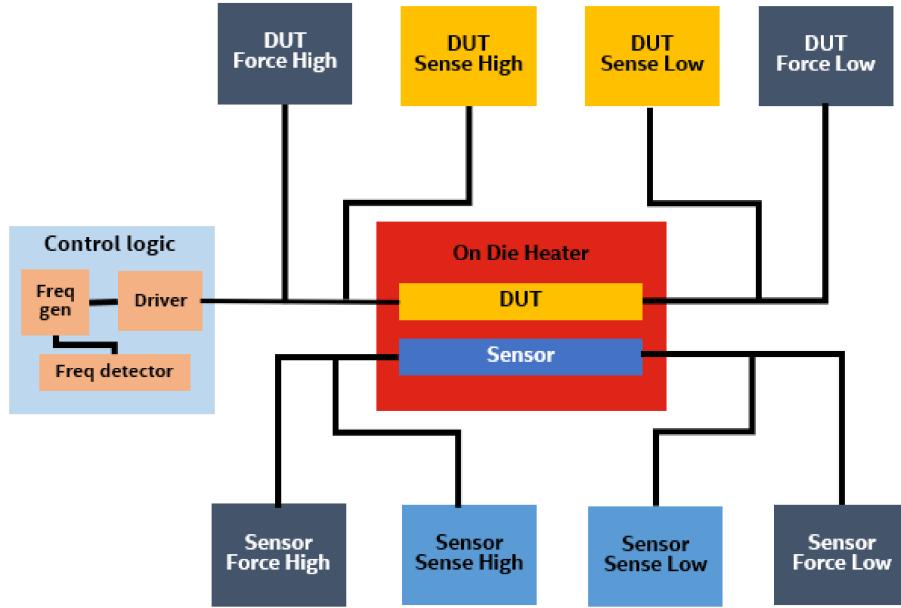

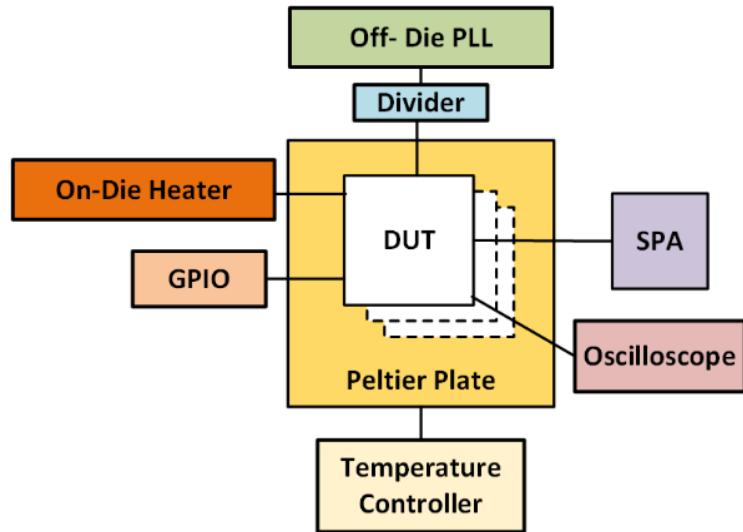

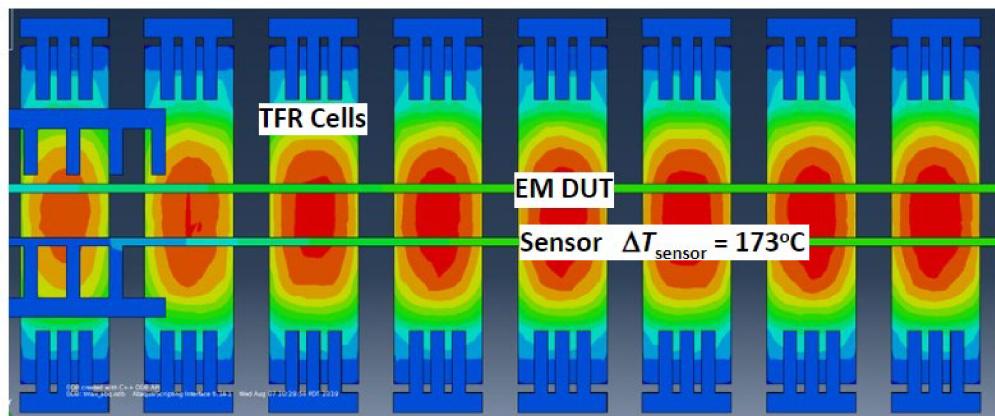

| <i>Figure 3.3. EM DUT and metal sensor placed on top of on-die heater, where CMOS logic circuits are kept in safe distance. Four-point Kelvin connections are used for DUT and sensor resistance measurement. ....</i>                                                                                                                                                                        | 67 |

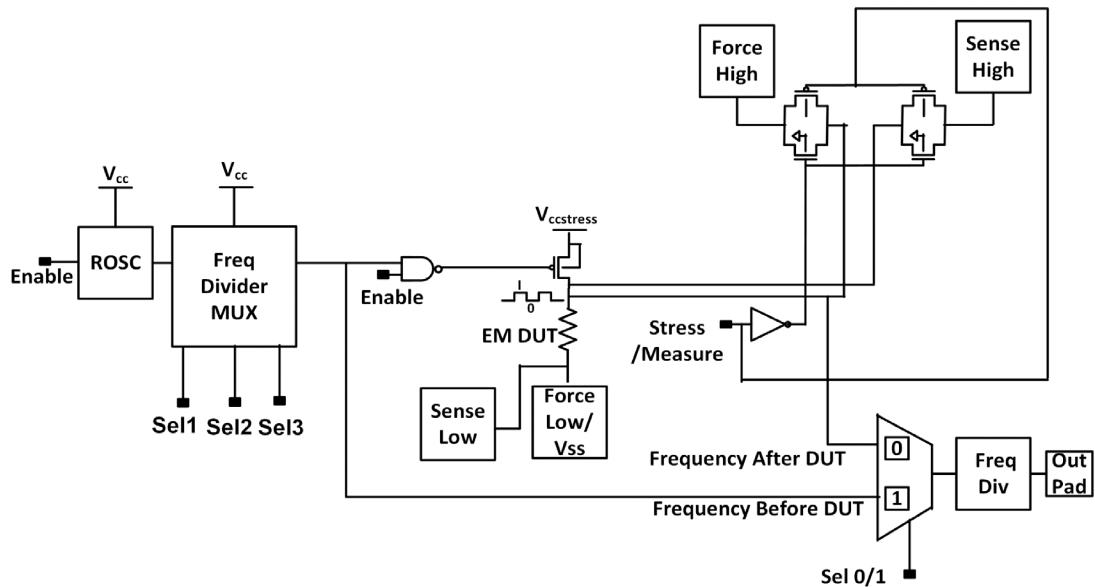

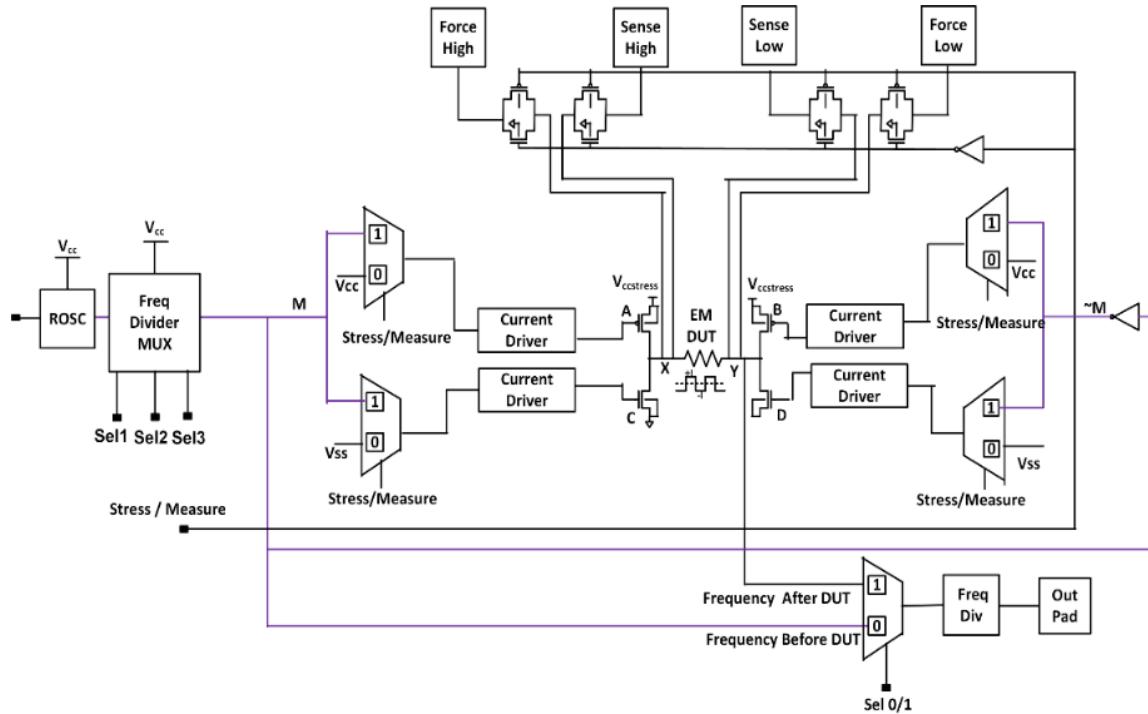

| <i>Figure 3.4. EM test structure to work under pulsed DC stress. ....</i>                                                                                                                                                                                                                                                                                                                     | 68 |

| <i>Figure 3.5. EM test structure to work under pulsed AC stress. ....</i>                                                                                                                                                                                                                                                                                                                     | 70 |

| <i>Figure 3.6. Test boards used for packaged test structures. ....</i>                                                                                                                                                                                                                                                                                                                        | 71 |

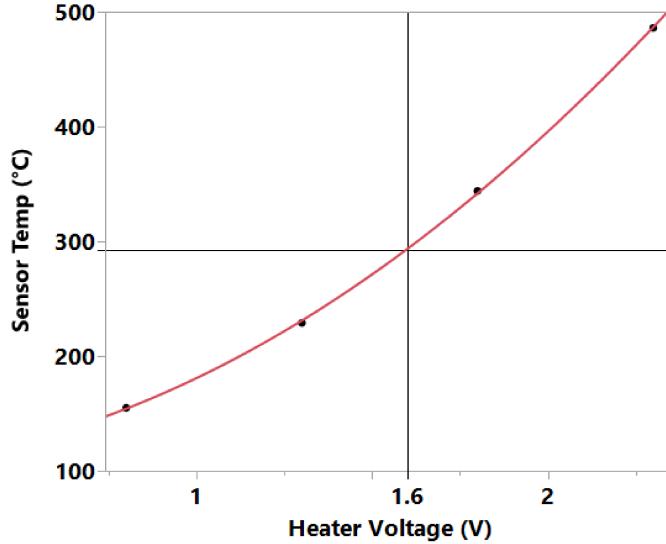

| <i>Figure 3.7. Thermal simulation results of the TFR on-die heater and its thermal impact on the EM DUT and the metal sensor. ....</i>                                                                                                                                                                                                                                                        | 72 |

| <i>Figure 3.8. Sensor temperature with respect to TFR on-die heater voltage at the Peltier plate temperature of 120 °C. ....</i>                                                                                                                                                                                                                                                              | 73 |

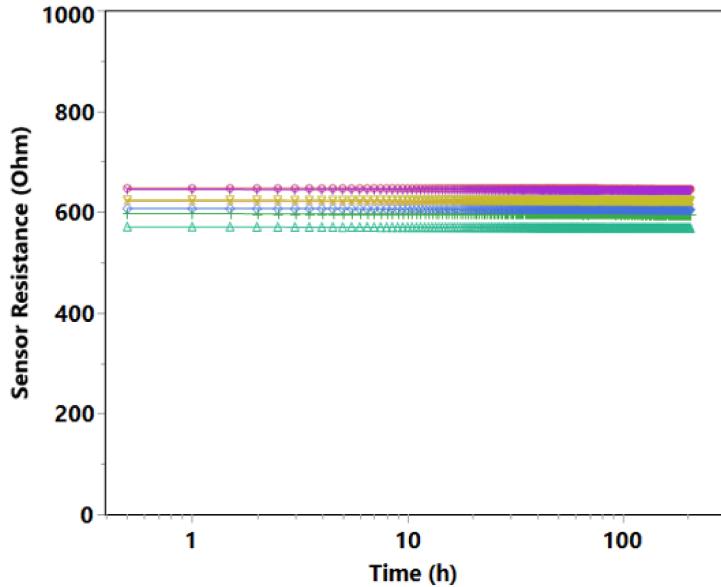

| <i>Figure 3.9. Resistance of metal sensor during EM MTTF measurements. ....</i>                                                                                                                                                                                                                                                                                                               | 74 |

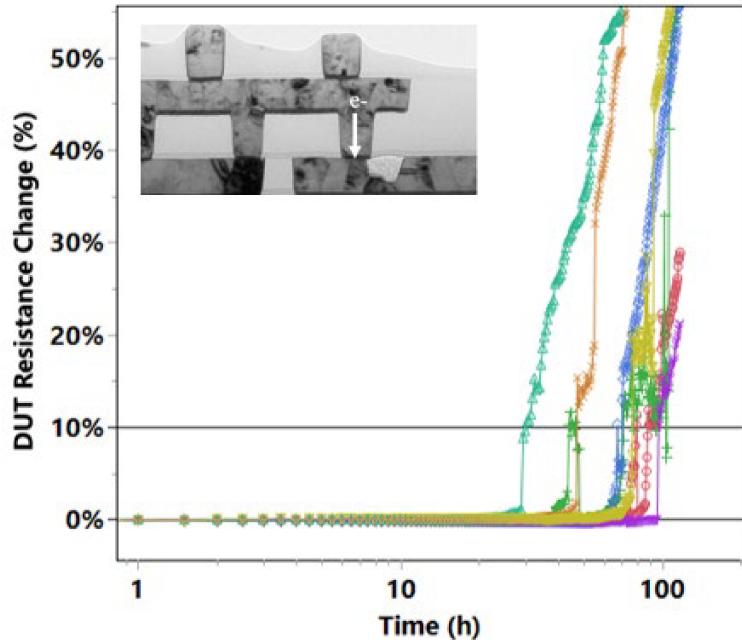

| <i>Figure 3.10. A time profile of resistance changes during pulsed DC stressing at a frequency of 1 GHz with a 50% duty factor. TEM image of this EM failure is included as an inset. ....</i>                                                                                                                                                                                                | 75 |

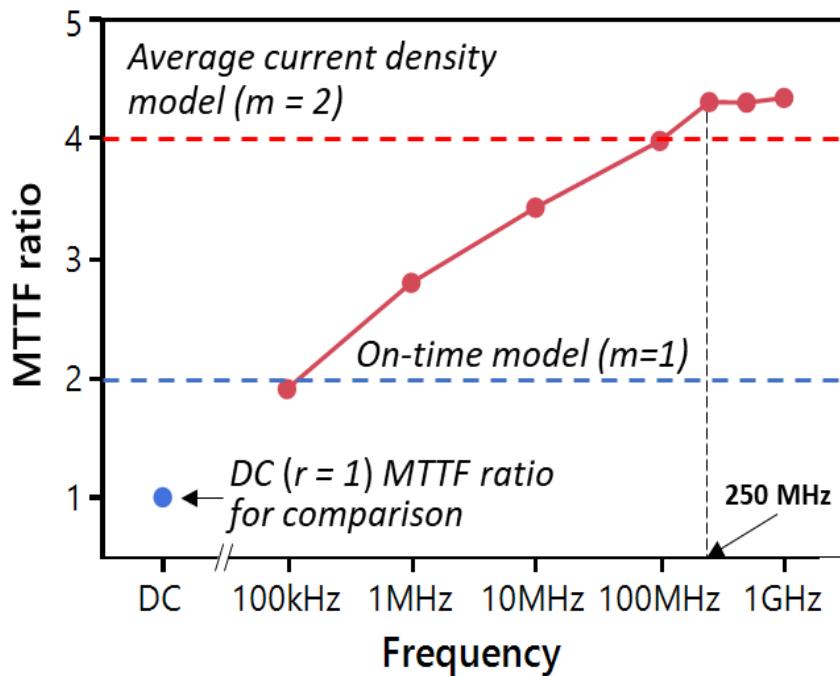

| <i>Figure 3.11. MTTF ratios to DC MTTF with respect to frequency. Both on-time model and average current density model (<math>m = 2</math>) lines are also plotted. ....</i>                                                                                                                                                                                                                  | 76 |

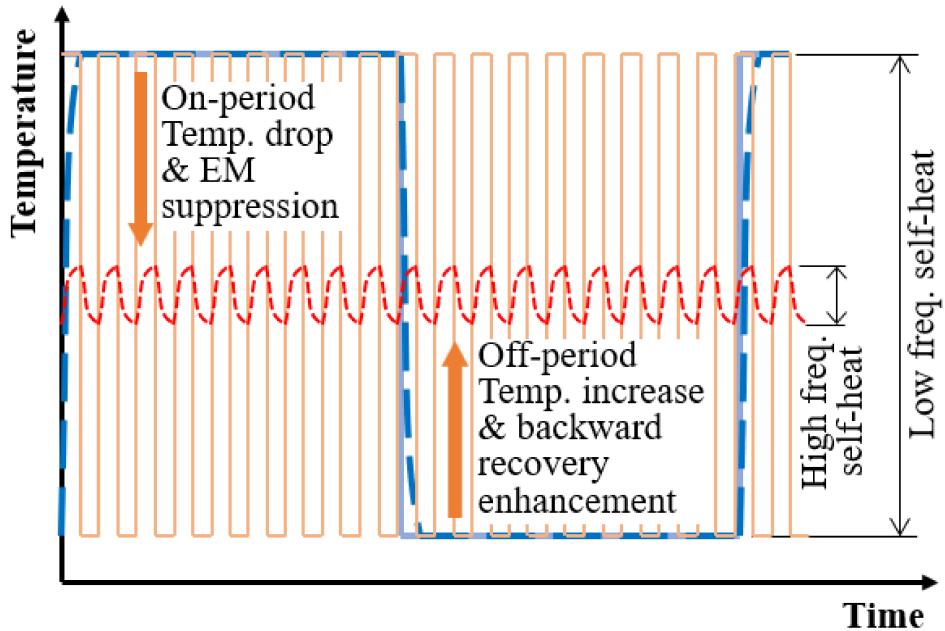

| <i>Figure 3.12. Comparison of temperature swings (dashed lines) under unidirectional pulse stress (solid lines) between low- and high-frequency. ....</i>                                                                                                                                                                                                                                     | 78 |

| <i>Figure 4.1. EM DUT configuration, current from SMU is coming to anode and flowing to cathode side. ....</i>                                                                                                                                                                                                                                                                                | 86 |

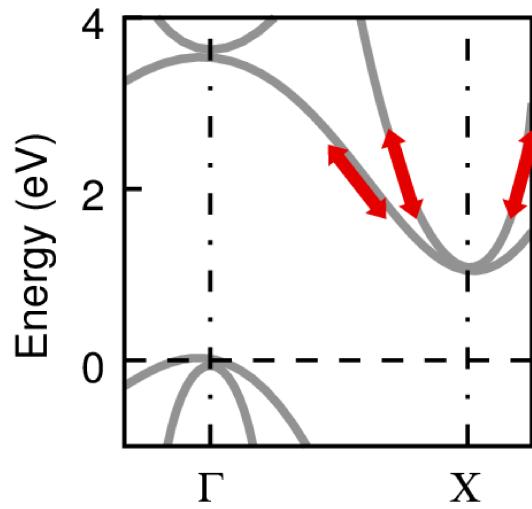

| <i>Figure 4.2. Inter-band thermal laser process. ....</i>                                                                                                                                                                                                                                                                                                                                     | 87 |

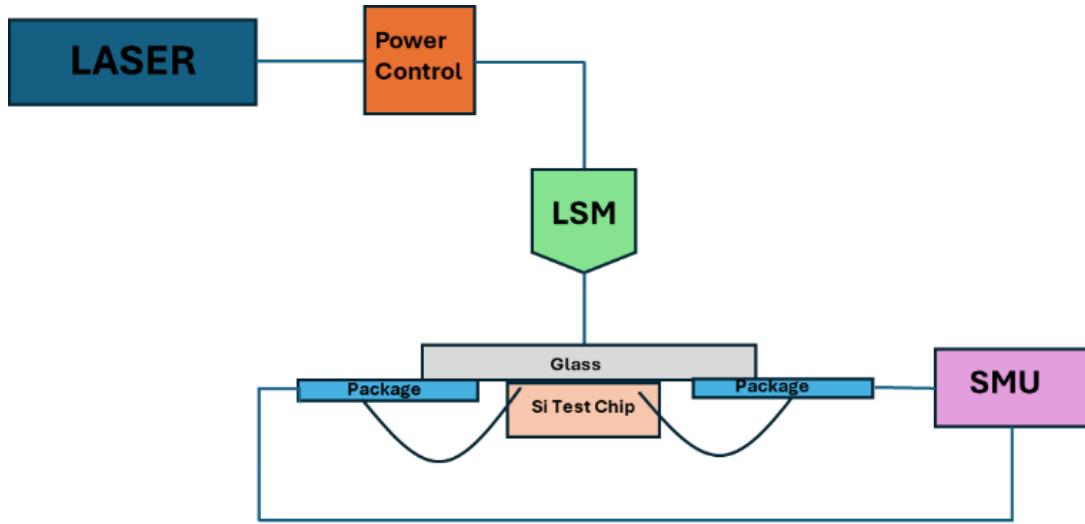

| <i>Figure 4.3. Laser with a power control and LSM to locally heat up the packaged silicon through a glass opening. SMU serves as a source of current to the DUT, and it measures the voltage, current, and resistance of the DUT. ....</i>                                                                                                                                                    | 89 |

|                                                                                                                                                            |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

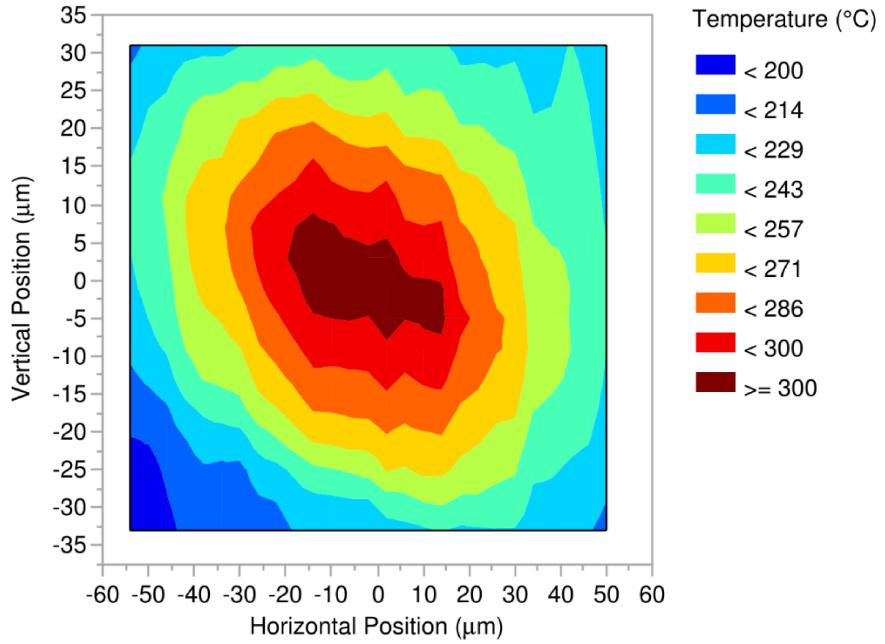

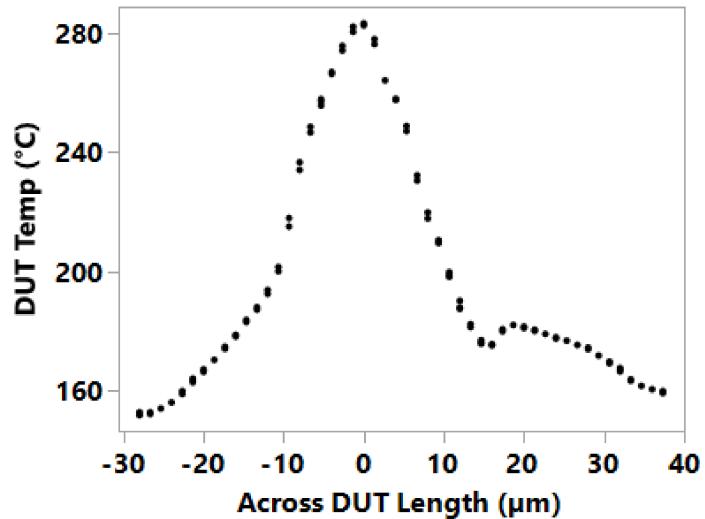

| <i>Figure 4.4. Thermal spatial profile of the test structure by laser scanning.....</i>                                                                    | 90 |

| <i>Figure 4.5. Cross section of thermal spatial profile across the DUT.....</i>                                                                            | 90 |

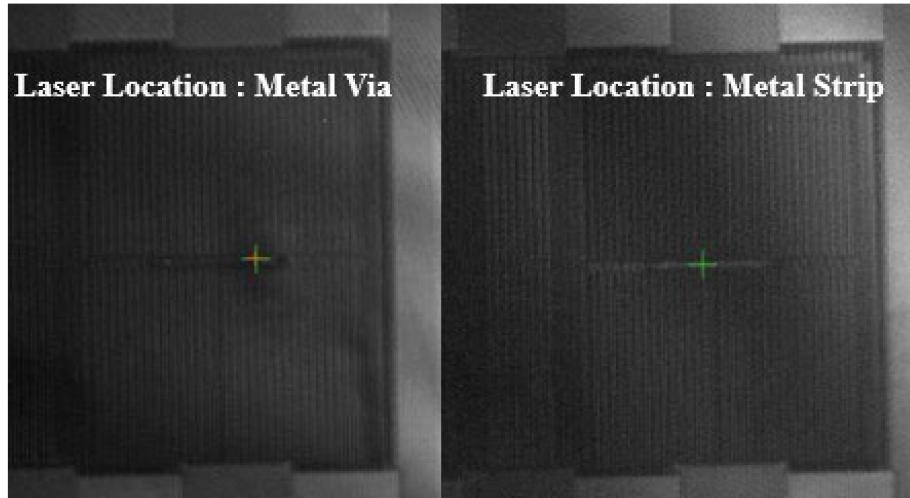

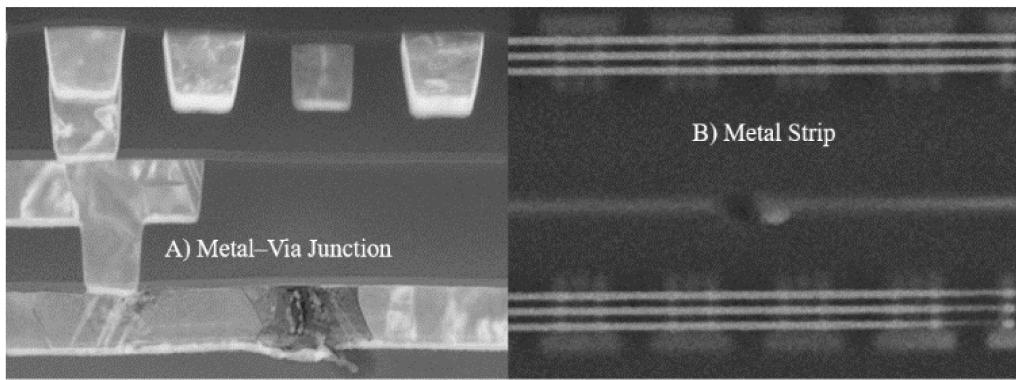

| <i>Figure 4.6. Laser location on the metal-via junction (left) and metal strip (right). .....</i>                                                          | 91 |

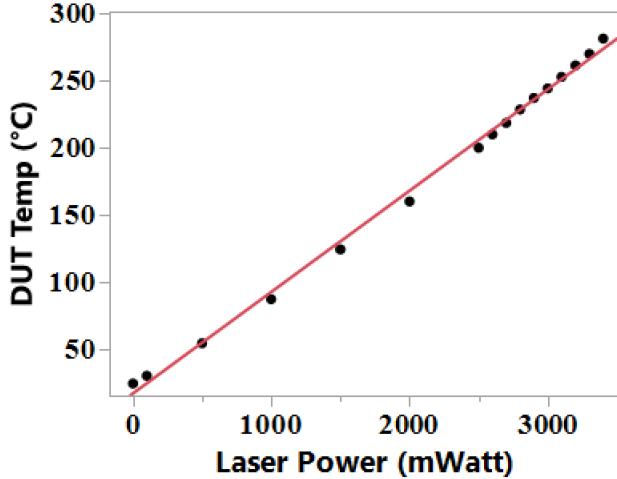

| <i>Figure 4.7. DUT temperature vs laser power, calibrated before starting the stress.....</i>                                                              | 92 |

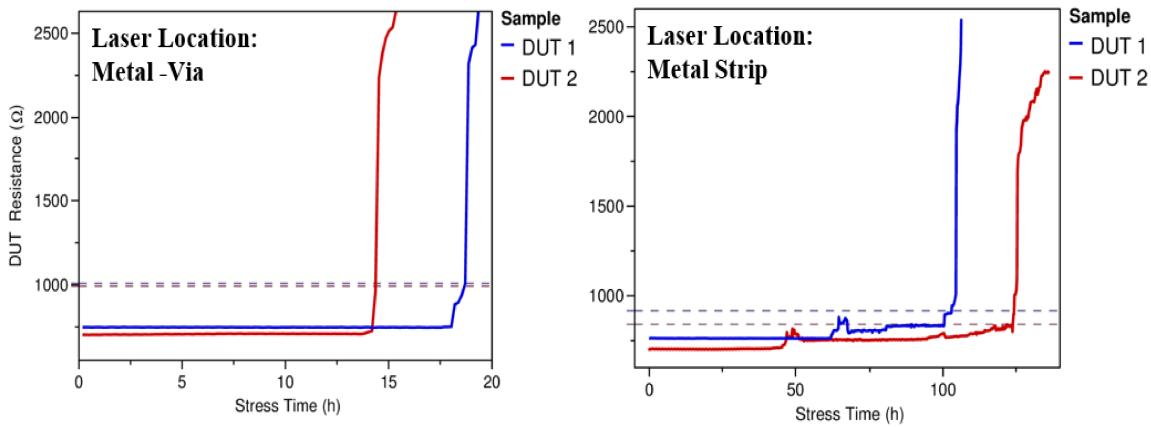

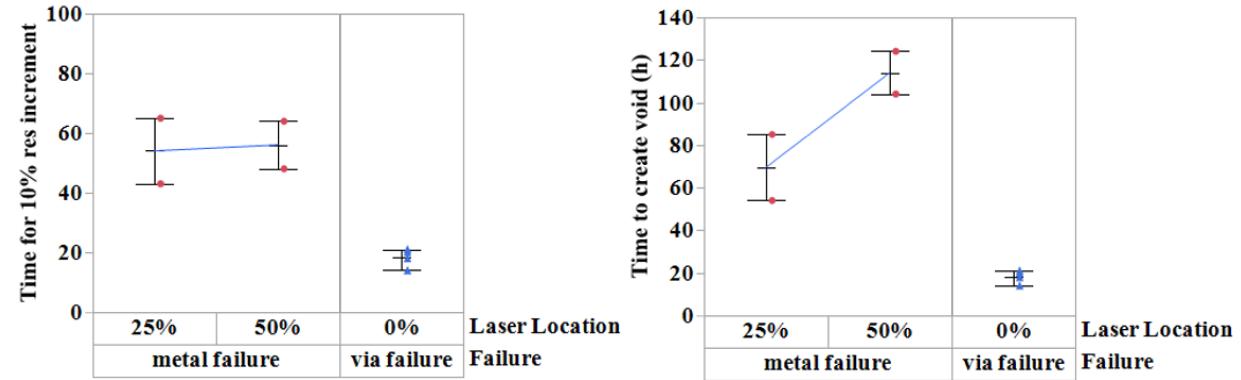

| <i>Figure 4.8. DUT Resistance failure over time: metal-via junction (left) and metal strip (right). .....</i>                                              | 93 |

| <i>Figure 4.9. TEM images of void formations a) metal-via junction, b) on metal strip. ....</i>                                                            | 93 |

| <i>Figure 4.10. Time taken for 10% increment of DUT resistance versus time taken to generate void as a function of the laser injection locations. ....</i> | 95 |

## ACKNOWLEDGMENTS

First and foremost, I am immensely grateful to my advisor, Dr. Ratnesh Kumar, his constant support, patience, guidance, technical expertise, and contribution of time to make my PhD experience educational, rewarding and fulfilling. I benefited by the high standards he has set and will continue to live up to them as I continue my career in industry.

I am profoundly grateful for the enduring support and guidance of my mentor, Dr. Ricardo Ascazubi, my manager in Intel Corporation. His technical expertise, mentorship and encouragement have been invaluable, instrumental in my PhD journey.

I would like to thank the members of my doctoral final defense committee: Dr. Long Que, Dr. Mani Mina, Dr. Meng Lu, Dr. Cheng Huang. I appreciate them taking time out of their busy schedules to critique my work and providing valuable guidance.

I am wholeheartedly grateful to Intel corporation for giving me the opportunity to pursue my doctoral study. I am grateful for the constant support from my skip level manager Dr. Balkaran Gill in Intel. I would like to thank all my colleagues in my workplace who supported me throughout this journey. I also extend my thanks to all my colleagues in Dr. Kumar's research group.

I am thankful to my friends who always hold my back: Archana, Vineet, Neelam, Edwin, Shruti, Sheshank.

Lastly, I want to thank my family for all their love and encouragement. Thank you to my parents Swapna Kumar Patra, Swapna Patra, my sister Semanti Patra for everything you have done to raise me up and support me in all my pursuits. A special thanks to my grandmother Sudha Ghorai for being my inspiration since childhood. I am blessed for the enormous support from my husband Siva Konduri. I am also thankful for the mammoth support from my in-laws Visweswara Vara Prasad Konduri, Kanya Kumari Konduri and my brother- in- law Pavan Konduri.

## ABSTRACT

The semiconductor industry has made great strides in recent times. On-chip integrated circuits are built using many discrete CMOS (complementary metal oxide semiconductor) devices that perform various functional operations. Today, an entire multicore processor can be built on a single piece of silicon. This massive downscaling has been possible due to miniaturization of the silicon MOS transistor in very large scale integration (VLSI). Any IC's lifetime is a function of both device and interconnect wear out.

The conventional approach to ensuring product's thermal reliability involves conducting accelerated aging tests, exposing a product to elevated temperatures and voltages (also known as a stress test or High Temperature Operating Life (HTOL) test) for a duration that estimates the product's entire lifespan under normal usage conditions by the customer.

Electromigration (EM) is the transport of conductor metal atoms caused by the momentum transfer from the conducting electrons. As device sizes shrink, it becomes possible to increase the number of devices per unit area, enhancing device density and causing higher current density within the device, which in turn raises operating temperatures non-uniformly within the ICs. Further, the need for high-speed operation results in a higher frequency switching that has its own ramifications towards heating pattern. These factors collectively contribute to making electromigration a significant challenge for the reliability of contemporary ICs.

Before working on new test structures to detect EM failure under high frequency and non-uniform heating effect, an elaborate literature review is pursued to understand the complex electromigration physics and to understand the previous work which are done to study EM failure under low to high frequency effect. We have designed novel test chips fabricated using Intel's 22FFL process technology to assess EM impact on failure rate of high current densities on Cu-based metallurgies. We have demonstrated the ability for these circuits to characterize direct

current (DC), unidirectional pulsed DC as well as bidirectional pulsed AC stress EM effects up to GHz frequencies. Heater structure design enables localized thermal stress up to 300 °C and is compatible with high-speed CMOS logic infrastructure. Time dependent modulation of the EM effects is studied on 90p Cu alloy metallurgy and results are presented for the first time.

The demand of increased accelerated temperature with a spot heating capability motivated us to pursue a novel method of laser based electromigration testing. This approach facilitates the analysis of thermal effects in two keyways: (1) it confirms the adequacy of the test temperature with high precision, and (2) it assesses the temperature-related aging and susceptibility of specific IP blocks within the silicon. Our method provides both high spatial precision and rapid testing, as a few days of laser-induced temperature stress reproduces the effects of multiple years of regular usage, while the rest of the chip remains unaffected and continues to operate normally. As per our knowledge, this is the first time a non-uniform temperature based electromigration effects are made possible and the corresponding results are depicted.

## CHAPTER 1. GENERAL INTRODUCTION

### 1.1 Background

In semiconductor world, the CMOS devices face reliability issues such as bias temperature instability (BTI), hot carrier injection (HCI), time-dependent dielectric breakdown (TDDB), soft error rate (SER) which create increased circuit delay, soft break down, hard failure of the devices. Whereas back-end metal interconnects face the electromigration and thermal migration failures.

Electromigration (EM) refers to the movement of metal atoms within a conductor, driven by the momentum transfer from the electron flow. When electric field is applied, current flows through a metal interconnect, and two forces are exerted on its metal ions, the first force is the electrostatic force caused by the electric field in the same direction of electric field, and the second force is the wind force generated by the momentum transfer between the conducting electrons and metal ions in the metal line in the direction of electron. When resulting force is higher than activation energy, then metal ions start to diffuse from negatively biased cathode node to positively biased anode node of the interconnect, after a significant diffusion, a void creates at cathode and hillock generates at anode [1], [2]. This phenomenon is called electromigration (EM), which is described elaborately in chapter 2.

The semiconductor industry has advanced significantly in recent years. On-chip integrated circuits are constructed using numerous discrete CMOS (complementary metal oxide semiconductor) devices that carry out various functional tasks. Nowadays, a complete multicore processor can be fabricated on a single silicon chip. This substantial reduction in size has been achieved through the miniaturization of silicon MOS transistors in very large-scale integration (VLSI). The lifespan of any integrated circuit is influenced by the wear and tear of both the devices and the interconnects.

The increase in number of devices significantly increases the current density. This, in turn, has heightened the risk of BEOL (Back-End-of-Line) connectivity failures and consequently shortened the lifespan due to electromigration (EM).

### 1.2 Motivation for this work

Despite decades of research on electromigration (EM) in the context of technology scaling, its behavior under unidirectional pulsed DC, bidirectional pulsed AC currents, and under non-uniform heat conditions remains not fully understood.

With the rise of high-speed applications in circuits, any delay caused by increased metal interconnect resistance due to electromigration (EM) significantly impacts product performance. Additionally, the combination of high-density currents and increased joule heating in advanced technologies like FinFET (Fin Field-Effect Transistor) has sparked renewed interest in studying pulsed DC and pulsed AC EM, particularly for high-speed circuits. Three main challenges to pursue high frequency-based EM study are, stressing interconnect at 1) high frequency 2) high temperature, and 3) high current. As per our knowledge, this is the first work to report GHz frequency effect in EM failure. To achieve this, an on- die ring oscillator (ROSC) is used which can generate MHz to GHz on chip frequencies. For low frequency (kHz to MHz range) test, an off-chip phase locked loop (PLL) circuit is used. Both on-die, and off-die frequencies are inserted through same digital logic circuit to stress the metal interconnect. The other challenge is, to sustain the CMOS circuit functionalities, the ambient temperature cannot cross more than 120 °C, hence an on-die stable heater is required with a standoff distance from the active circuit to generate the accelerated heat locally to stress the metal interconnect.

To achieve high current during stress, an innovative test chip is designed with digital logic circuit and large sized current driver, also the metal interconnect is protected from parasitic capacitance effect during stress.

Fortunately, this work could overcome all the challenges and the novel test chips could generate the EM failure trend with respect to DC to GHz frequencies. Design details and tests results are described in chapter 3.

Other than current density, electromigration failure depends on the temperature. The equipment utilized for stressing products, such as tester cards and reference design PCB (printed circuit board), have a finite capacity for power delivery. An increased power demand during stress testing can strain these power delivery systems. This issue restricts the highest possible temperature that can be used for stress conditions. Also, no mechanism exists to perform non-uniform or spot heating that arise in practical settings.

To understand the non-uniform localized temperature effect on EM failure, a laser-based test is performed. To our knowledge, this is the first reported laser based electromigration failure result, which show EM failure depends on the laser location, as thermal migration has a key role to play when the stress temperature is non-uniform. The detailed laser-based EM failure work is explained in chapter 4.

### **1.3 Thesis Organization**

This thesis is organized with following four chapters, chapter 2, chapter 3 and chapter 4 represent the work submitted to three journals.

Chapter 2 describes the in-depth survey of the several papers on electromigration and various aging phenomena, this literature survey is submitted as a review paper in a journal. The chapter begins with a brief overview of reliability failures in integrated circuits (ICs) and provides an in-depth discussion on electromigration (EM) failures in metal interconnects. For the latter, we begin by reviewing the fundamentals of electromigration. In addition to discussing the widely used Black's model and Blech's model for characterizing EM failures, we also summarize more advanced models by Kirchheim and Korhonen. These advanced models are particularly relevant

for modern high-speed IC applications, as they account for the opposing forces on EM during the on and off periods of pulsed inputs. We also cover techniques to mitigate the effects of EM and mention industry-based tools used to detect EM issues during the design phase.

Chapter 3 describes the design, fabrication and testing of novel test chips which are uniquely capable to generate pulsed DC and AC stress over a wide frequency range, from DC to 100 kHz to 1 GHz for detecting EM failure of an interconnect. The test chip is fabricated using Intel's 22FFL technology. Additionally, a thin film resistor (TFR) on-die heater is incorporated to provide stable and consistent thermal conditioning up to approximately 300 °C. The unique testing capability is described. The frequency-dependent EM mean time to failure (MTTF) trend is experimentally demonstrated. It is a collaborative work between Intel corporation and Iowa state university.

Chapter 4 describes very first non-uniform heat based electromigration data. The non-uniform heat is generated by using continuous wave-based laser on an EM test structure (metal interconnect) fabricated using Intel's 22FFL technology. The laser is focused on metal-via junction and on the metal strip. The EM failure mode signatures show dependency on the heating locations. The void generations captured by TEM (transmission electron microscopy) images confirm the EM failure locations. EM test structure, laser set up, physics behind testing, silicon data, TEM images are presented. It is a collaborative work between Intel corporation and Iowa state university.

#### 1.4 References

- [1] J. Lienig, "Electromigration and Its Impact on Physical Design in Future Technologies," ISPD, Mar. 24–27, 2013, pp. 33-40.

- [2] J. Lienig et al., "Toward Security Closure in the Face of Reliability Effects," ICCAD Special Session Paper, ICCAD, Munich, Germany, Nov. 2021, pp. 1-9.

## CHAPTER 2. ELECTROMIGRATION: A REVIEW, WITH OVERVIEW OF OTHER IC FAILURES

Srijita Patra, Ratnesh Kumar

Department of Electrical and Computer Engineering

Iowa State University, Ames, Iowa, USA

Modified from a manuscript under review in

IEEE Transactions on Device and Materials Reliability

### 2.1 Abstract

Electromigration (EM) is the transport of conductor metal atoms caused by the momentum transfer from the conducting electrons. As the integrated circuits (ICs) are shrinking in size, resulting in the continuous downsizing of interconnect cross-sections, the new challenges are encountered, particularly in the form of electromigration (EM) in circuit interconnections. It is widely recognized that the risks associated with electromigration due to the decreasing size of structures will become more pronounced in the future. Consequently, there has been a substantial surge in the adoption of electromigration-conscious design strategies over the past few years. To ensure the production of functional circuits in progressively smaller dimensions, a substantial boost in investment towards methodologies that enhance EM-related reliability is imperative. The important integrated circuit EM-affiliated failure mechanisms are reviewed in this paper. The fundamental physics behind the electromigration is discussed followed by the factors impacting electromigration. This review paper serves to showcase the importance of complex electromigration physics as the semiconductor industry is moving towards high-speed and shrinking-size applications. Also, it outlines the high frequency effects and various solution approaches and tools.

## 2.2 Introduction: Various IC Failures

The semiconductor industry has made great strides in recent times. On-chip integrated circuits are built using many discrete CMOS (complementary metal oxide semiconductor) devices that perform various functional operations. Today, an entire multicore processor can be built on a single piece of silicon. This massive downscaling has been possible due to miniaturization of the silicon MOS transistor in very large scale integration (VLSI). Any IC's lifetime is a function of both device and interconnect wear out.

With feature size reduction, fabricating CMOS devices with high perfection becomes very challenging. During and after manufacturing of the small devices, more defects are observed, making the devices more susceptible to various in-field failures. This causes device performance to degrade over time, even failing completely pre-maturely before its intended lifetime [1]. With shrinking device size, the device characteristics incur increased variability which leads to larger spreads in delay, leakage/power, and loss of robustness [2].

In this review paper we briefly overview the reliability failures in ICs and comprehensively discuss the electromigration (EM) failure in metal interconnects. For the latter, we start with reviewing electromigration fundamentals. Along with most used Black's model and Blech's model to characterize EM failures, we also summarize more advanced models of Kirchheim and Korhonen, which are relevant for today's high speed IC applications to capture opposing forces on EM during the on- versus the off-periods of pulsed inputs. We also mention the techniques to reduce EM effect, and the industry-based EM tools to detect EM issues during design phase. A handful recent review papers on electromigration [3], [4], [5]-[10] have shared useful information on EM fundamentals, EM physics, but they did not discuss other IC failures mechanisms along with above mentioned EM related topics in a single review paper.

With nano-sized transistors, keeping high performance under low power reliability becomes a significant obstacle to further CMOS scaling as technology nodes continue to shrink. As per constant-electric field scaling principles [11], the power-supply voltage of the MOS transistor is reduced with the continued scaling down of device dimensions to retain same level of heating. Yet although an individual transistor is consuming very little power per switching, when billions of them switching at very high speed, the overall power dissipation becomes a challenge.

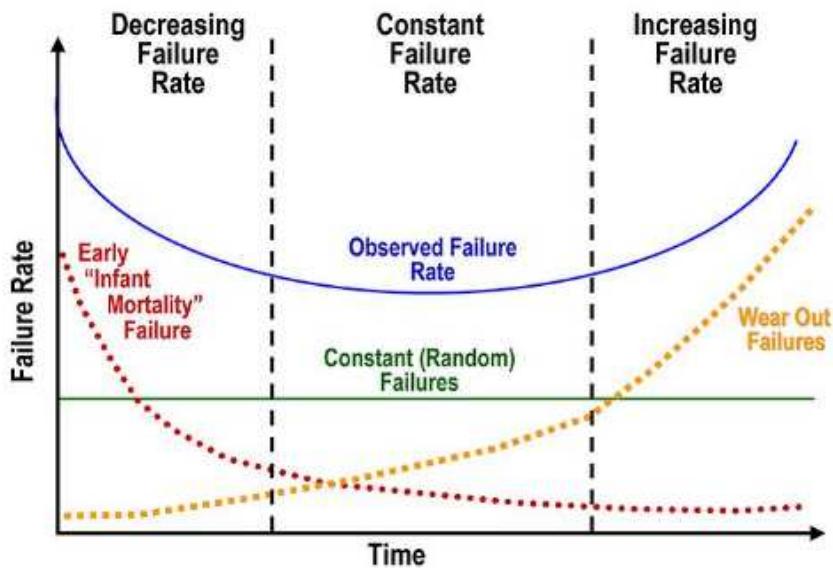

Figure 2.1. Classical bathtub failure rate curve observed in semiconductor industries [16].

Hot carriers' injection (HCI), bias temperature instability (BTI), and time dependent dielectric breakdown (TDDB) are the most prominent reliability mechanisms causing transistor aging [12], [13]. Electromigration (EM), stress migration (SM) and thermal migration (TM) are critical defect mechanisms causing metal interconnects failure [3]. Soft error rate (SER) is another distinctive defect mode for an IC under radiation environment [14]. Therefore, these mechanisms need to be studied thoroughly to obtain accurate overall reliability while designing robust circuits.

The failure rate of any integrated circuit (IC) during its lifetime is historically modeled by a “bathtub curve” [15], [16] shown in Fig. 2.1. The “bathtub” curve consists of 3 characteristic regions. The initial segment of the curve, characterized by a declining failure rate, is referred to as early failure or infant mortality failure, which is typically associated with manufacturing defects (e.g. patterning defects). Burn-In test, which is an accelerated stress-based screening, is used to filter out the ICs with congenital defects.

The central portion is known as the useful life period. In this phase, the ICs are shipped to customers, failure rate is largely constant, but certain random failures can occur due to environmental conditions (noise, radiation, current, temperature, etc.). The final segment of the curve represents wear-out failures, characterized by the highest failure rate due to acceleration of failure mechanisms.

### 2.2.1. Hot Carrier Injection (HCI)

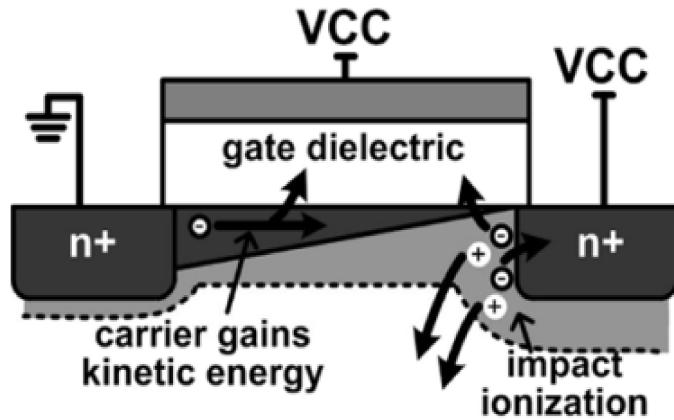

In negative-channel metal oxide semiconductor (NMOS) devices, charge carriers are electrons whereas in positive-channel metal-oxide semiconductor (PMOS) devices, charge carriers are holes. As charge carriers move along the channel from the source to the drain in a device, the electric field causes carriers to gain kinetic energy and become “hot”, also creating secondary carriers through impact ionization [13], as shown in Fig. 2.2. Eventually, a few of these primary or secondary energetic carriers acquire enough energy to surpass the energy barrier between silicon (Si) and silicon dioxide ( $\text{SiO}_2$ ) [17]. As a result, these high-energy carriers, known as hot carriers, are injected into the gate oxide layer. This injection leads to the accumulation of trapped charges at the interface between the silicon substrate and the gate dielectric, as well as within the bulk of the dielectric material. This phenomenon changes the device characteristics such as threshold voltage, transconductance, saturation current, and gradually the device degrades. Hot Carrier

injection (HCI) is directly associated with the channel length, the thickness of the oxide layer, and the power supply voltage of the device [18].

Figure 2.2. HCI mechanism in a semiconductor device (NMOS) [13].

### 2.2.2. Bias Temperature Instability (BTI)

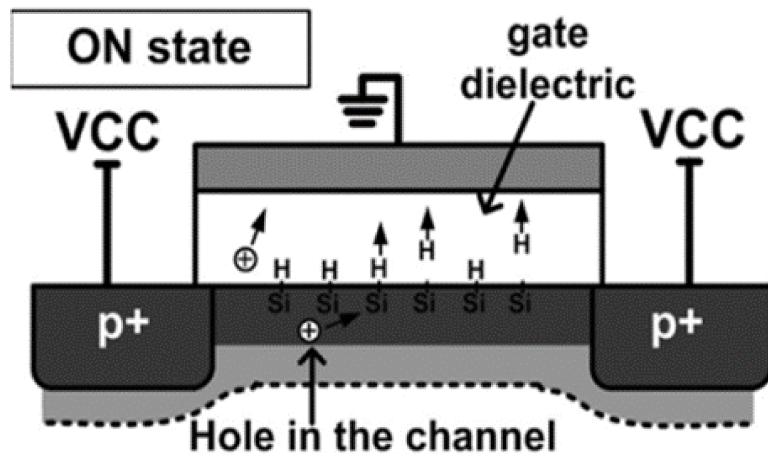

The bias temperature instability in a transistor is characterized by a change in its threshold voltage ( $V_{th}$ ) due to voltage stress. In PMOS transistors, the threshold voltage is associated with a negative gate bias, making negative bias temperature instability (NBTI) a more significant issue than positive bias temperature instability (PBTI). Conversely, for NMOS transistors, PBTI is of greater concern than NBTI.

PMOS transistor operating under negative gate bias, in the strong inversion region but with a zero or very low lateral electric field ( $V_{DS} \approx 0$ ), holes from the PMOS transistor accumulate at the Si- $\text{SiO}_2$  interface and eventually some of these charges get trapped in the oxide layer and/or the disruption of silicon-hydrogen (Si-H) bonds at the interface between the silicon and oxide leads to the creation of interface traps [13], [19], [20] shown in Fig. 2.3. The formation rate of these interface traps is hastened by elevated temperatures and the duration of the stress applied. The

presence of these traps results in an increase in the absolute value of the threshold voltage ( $V_{th}$ ) for PMOS transistors. Upon removal of the stress, the PMOS device begins a "recovery" phase, during which the trapped holes begin to release, and/or the freed hydrogen species start to diffuse back toward the substrate-dielectric interface. This diffusion process allows for the annealing of the previously broken silicon-hydrogen (Si-H) bonds, which in turn reduces the absolute value of the threshold voltage. But if the shift in the threshold voltage surpasses a certain specified limit, then the device is considered to have failed [19], [20]. PBTI in NMOS devices was not found critical in silicon dioxide dielectrics but for high- $\kappa$  gate stacks, PBTI became a reliability concern [21].

Figure 2.3. NBTI mechanism in a PMOS device [13].

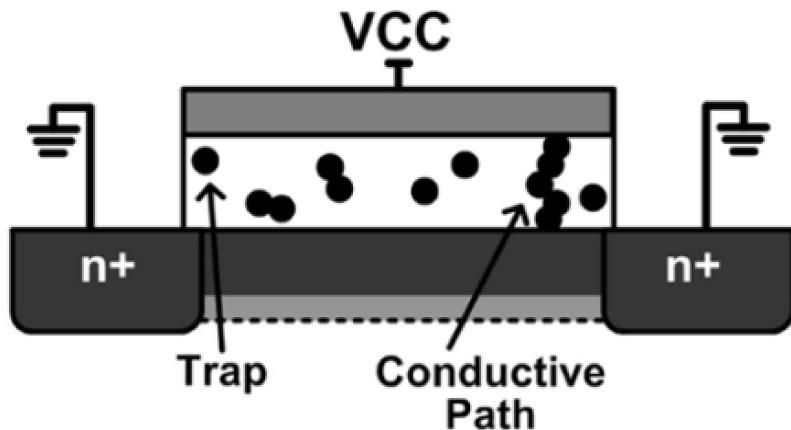

### 2.2.3. Time Dependent Dielectric Breakdown (TDDB)

TDDB occurs when a device fails due to carrier tunneling through the gate oxide to substrate. Transistors under constant voltage stress, generate electron or hole injection into the gate oxide which form the defects, such as oxygen vacancies or traps (see Fig. 2.4). Over time, these trapped carriers combine to create a conductive pathway through the dielectric stack, ultimately

leading to the breakdown of the gate oxide. With the reduction of the gate dielectric thickness to the nanometer scale, a lower critical density of traps is sufficient to form a low-resistance robust conducting pathways allowing significant current to flow through the oxide leading overheating and irreversible damage to the dielectric layer [13], [18].

Through the introduction of high- $\kappa$  dielectrics, TDDB effect is reduced, but it's still a reliability concern [22]. The most practiced test to study the TDDB behavior is "constant stress" [23], applied in the form of constant voltage lower than the breakdown voltage of the oxide, and leakage current of the transistor is monitored. The observed time to break down the oxide is called the time-to-failure for TDDB.

Figure 2.4. TDDB effect in devices [13].

#### 2.2.4. Soft Error Rate (SER)

In sequential or memory elements, soft errors affect the state of the data (rather the parameter of a device). SER is caused by random radiation events occurring naturally in the terrestrial environment. When a particle of ionizing radiation hits the silicon substrate of a transistor, it generates pairs of electrons and holes. The movement of created electron-hole pairs through processes like diffusion and drift, results in the accumulation of electric charge at the drain

terminal of the transistor [24], [25]. The collected charge eventually induces a temporary disturbance at the drain node of the transistor causing a change in the data state, called soft error. A transient disturbance in a sequential circuit is referred to as a single event transient (SET), while a similar disturbance that occurs in a memory element and disrupts the stored information is known

as a single event upset (SEU). In a terrestrial environment, soft errors can occur due to alpha particles emitted from the packaging materials of electronic devices and due to neutrons, that originate from cosmic particles. Alpha particles, being a form of ionizing radiation, can directly create electron-hole pairs, as depicted in Fig. 2.5. Neutrons, in contrast, cause soft errors indirectly by interacting with the atomic nuclei of the materials in the transistor. This interaction is also illustrated in Fig. 2.5.

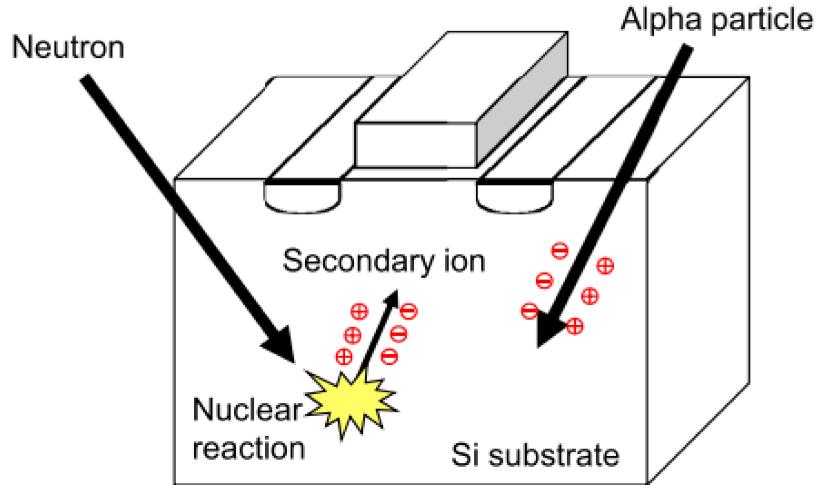

*Figure 2.5. Neutron and alpha based SER mechanism [26].*

The nuclear reaction initiated by the neutrons produces charged secondary particles such as protons, alpha particles, and heavy ions [26]. The likelihood of a circuit experiencing a soft error is influenced by several factors: the energy of the incoming particle, the precise location where the particle strikes, the geometry of the affected circuit element, and the overall design of

the circuit. The product of the power supply voltage and the capacitance of that node is defined as critical charge,  $Q_{\text{crit}}$ . SER can be prevented if  $Q_{\text{crit}}$  of the particle struck node is high [27]. Higher  $Q_{\text{crit}}$  is better to prevent the SER but it also means slower circuit and higher power dissipation. As the feature size of chips and the supply voltage are reduced, the critical charge ( $Q_{\text{crit}}$ ) decreases. Thus, the significance of soft errors increases with the downsizing of the chip technology. Redundant circuits in a chip also help to avoid the SER effect.

Aside from the reliability mechanisms related to front-end failures of an IC, the back-end the back-end failure mechanisms such as electromigration as well as stress-migration and thermal-migration have impacts on the lifetime of metal interconnects, and thereby that of the IC itself.

### 2.3 Electromigration

In the recent scaled technology nodes, electromigration induced back-end-of-line (BEOL) connectivity failure is a matter of frequent concern. Electromigration is a failure mechanism dependent on current density, frequency, and temperature. With miniaturization of device sizes, the increment of device density is feasible, but it also causes high current density and high operating temperature of the ICs, whereas high speed poses high frequency of switching. These make electromigration become a challenging reliability issue for today's IC [28].

Digital and analog circuits operate under DC current or time varying current, creating power/heat on the device and the interconnect network, which can get very high. A proper operation of the semiconductor devices depends on the robust power distribution. When designing an interconnect/power grid, two crucial design factors are: resistive drop and EM reliability, which must be properly considered [29]. A resistive drop can assure that devices do not overheat while receiving enough voltage, whereas a strong EM reliability prevents void formation in vias and lines that would otherwise raise resistance at various nodes/interconnects of the power grid over the course of the product's lifetime. Various simulation and modeling technologies are available

for power grid design [30]. Due to its extremely high levels of redundancy and dynamic current redistribution, accurate EM measurement of an interconnect grid is not a simple operation.

Time varying currents with unidirectional pulses and bidirectional AC currents also flow through the interconnect nets and devices. Such currents are also becoming critical because of high-speed circuits usage and their rising root mean square (RMS) values [31]. A section of this paper discusses the time varying stress effects on EM.

### 2.3.1. EM Fundamentals

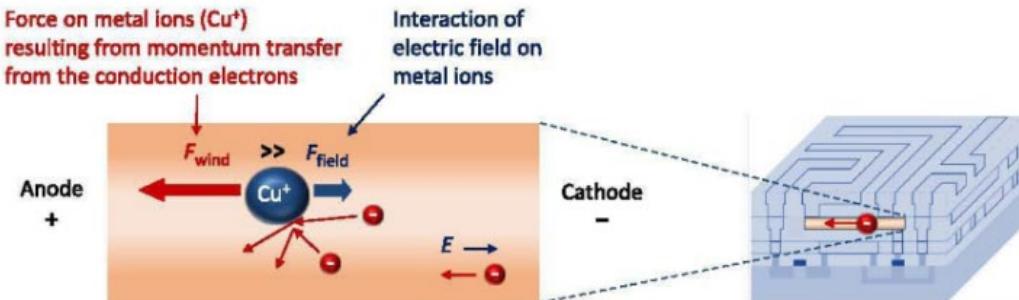

When electric field is applied, current flows through a metal interconnect, and two forces are exerted on its metal ions: The first is the electrostatic force  $F_{field}$  caused by the electric field,  $E$ , in the same direction of electric field, and the second force  $F_{wind}$  is generated by the momentum transfer between the conducting electrons and metal ions in the metal line shown in Fig. 2.6. The resulting force,  $F_{res}$  is [32]:

$$F_{res} = F_{field} + F_{wind} = e(Z_e - Z_p)E = eZ^*j\rho \quad (2.1)$$

where  $e$  is electric charge of ions,  $Z_p$ ,  $Z_e$  are the valences for the wind and electrostatic force respectively.  $Z^* = Z_p - Z_e$  is the effective charge number of the material,  $j$  is the current density, and  $\rho$  is the resistivity of the material. The force exerted by the electron wind is the primary force experienced by the atomic ions, leading to their migration toward the anode (positively biased). When the resulting force exceeds the activation energy ( $E_a$ ) of metal interconnect, metal ions ( $\text{Cu}^+$ ) start to diffuse from cathode (negatively biased) to anode in the direction of  $F_{wind}$  (direction of electron motion) shown in Fig. 2.6. Over time,  $F_{wind}$  moves a significant number of interconnect material atoms from their original positions, creating voids at cathode and hillocks at anode in the metal interconnect, and eventually electrical failure [32], [33].

The resulting atomic flux,  $J$ , due to electromigration, [34] is defined as in (2.2), where  $F_{res}$  is the resulting EM force from (2.1),  $C_a$  is the concentration of diffusing atoms,  $D_a$  is atomic diffusivity,  $k_B$  is the Boltzmann constant and  $T$  is the absolute temperature:

$$J = \frac{C_a D_a}{k_B T} F_{res} = \frac{C_a D_a}{k_B T} e Z^* j \rho \quad (2.2)$$

If the material transport occurred uniformly across every part of the metal line, then the quantity of material being replenished would equal the amount being removed, leading to no net alteration in the metal line's density or thickness. However, the metal interconnects within a fabricated integrated circuit (IC) chip comprise numerous features that introduce non-uniformities. Some of the dominant reasons for inhomogeneous EM are i) varying cross section of the metal and as a result, varying current densities, ii) variability in the lattice properties, iii) preexisting impurities in the metal line, iv) temperature distribution variation, v) generated mechanical tension gradients, and vi) directional changes of current in the metal line [28].

Figure 2.6. Two factors influence the metal ions ( $Cu$ ) constituting the lattice of the interconnect material; EM is the result of the prevailing force, the transfer of momentum from electrons moving within the applied electric field  $E$  [33].

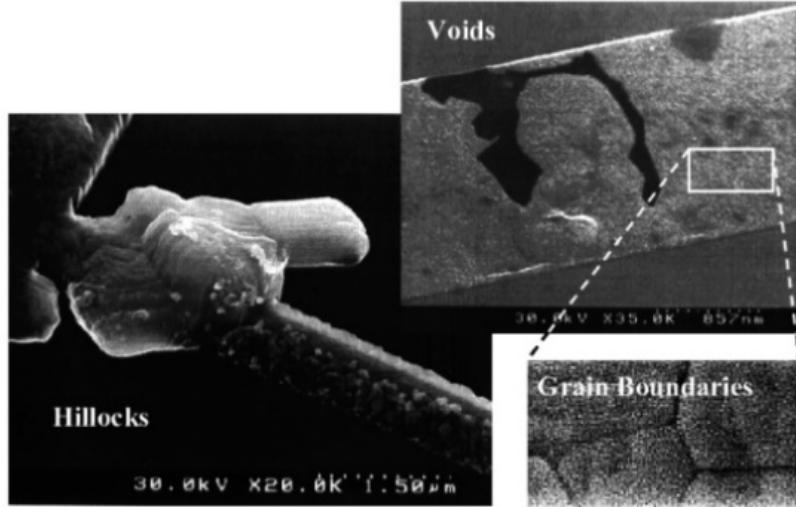

The presence of inhomogeneities leads to divergence in the diffusion process, which can ultimately cause the metal to deplete, forming voids, or to accumulate, leading to the creation of hillocks. Voids create open circuit and hillocks cause short circuit shown in Fig. 2.7. Whisker

formation is another crystalline, metallurgical phenomenon due to EM, causing growth of tiny, filiform hairs atop a metallic surface. Whiskers create short circuits and arcing in electronic circuits [28], [35].

*Figure 2.7. Hillock and void formations in metal interconnect due to EM (left, photography courtesy of G. H. Bernstein und R. Frankovic, University of Norte Dame) [35].*

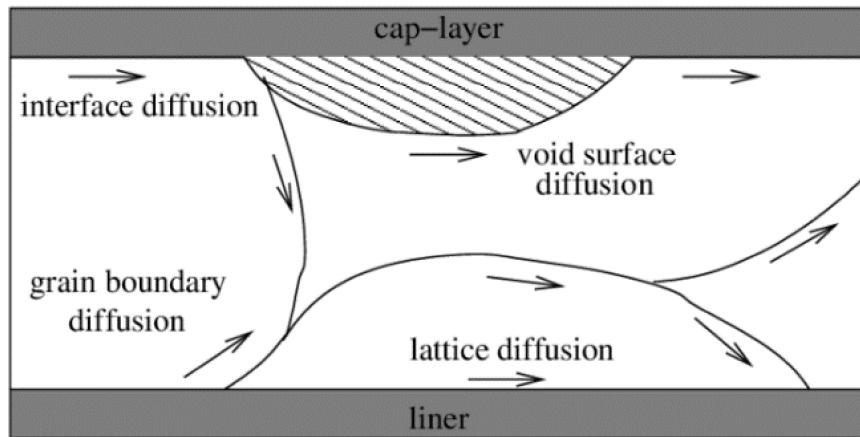

### 2.3.2. Grain and Surface Boundary Effects

The material selected for fabricating interconnects affects electromigration. The most critical characteristic of a conductive material that has a significant impact on electromigration is its activation energy,  $E_a$ . The activation energy is determined by the bond strength within the metal's crystal lattice structure [36]. The activation energy for the bulk diffusion (lattice diffusion) is higher than for grain-boundary diffusion and surface diffusion. Consequently, it is predominantly the grain boundaries that act as the pathways for diffusion in electromigration as shown in Fig. 2.8. Hence, the susceptibility to electromigration in the interconnect lattice is defined by the density and orientation of the grain boundaries [37]-[40].

The rate of atomic transport is significantly influenced by the grain size, which determines the extent of the grain boundary area in a metal line. The grain structure inside metal lines can differ from one location to another, a variation that originates from the metal deposition process.

Figure 2.8. Movement of metal atoms via various diffusion paths [41].

A region with fine-grained structure provides a greater number of grain boundaries for atomic migration compared to a region with a coarse-grained structure. Therefore, an accumulation of atoms occurs when atomic migration is directed from a fine-grained region toward a coarser-grained region. Conversely, void formation occurs when atoms migrate from a coarse-grained region to a fine-grained region. The driving force behind electromigration is primarily perpendicular to the grain boundaries [28], [4].

Bamboo or near-bamboo type crystal lattices (shown in Fig. 2.9) possess fewer grain boundaries that are aligned with the direction of the current flow. The absence of continuous paths along grain boundaries for diffusion aids in reducing the transport of atoms along these boundaries [41], [42]. In these structures, EM damage tends to occur at the points where grain boundaries branch off or join. Such points are called “triple points” [28], [41].

By selecting a suitable barrier material for the metal, the activation energy for surface diffusion can be increased discouraging such diffusion. A barrier layer is a thin layer on metal interconnect and helps preventing metal from diffusing into the dielectric layer at high temperature. Therefore, a barrier layer must have a high stability and good adhesion to both metal and the dielectric layer. The widely used barrier layer for Cu is tantalum/tantalum nitride (Ta/TaN) [43].

Figure 2.9. Paths of diffusion at triple junctions result in the formation of (a) voids (b) hillocks [40].

Inhibiting one diffusion mechanism, shifts the burden to other diffusion mechanisms creating alternative damage scenarios [44]. As an example, using copper as metal interconnect instead of aluminum, reduces grain-boundary diffusion, but it increases surface diffusion. By using suitable barrier layers, if surface diffusion is reduced, the grain-boundary diffusion takes over. Thus, the material layers used inside any ICs have a complex impact on EM failures [45], [46].

### 2.3.3. EM Flux Divergence Effects

When there is a disparity in diffusion rates between two materials, it leads to a divergence in atomic flux at their interface. When current flows from a material with higher diffusivity to one

with lower diffusivity, atom accumulation occurs at the interface between the two materials. Conversely, when the current flows from a material with lower diffusivity to one with higher diffusivity, voids tend to form at the interface [49]. EM induced degradation not only depends on grain structure's composition and size affecting diffusivity, but also by the direction in which the current flows. [28], [4], [41]. When electrons move from a via to a metal line, line depletion can occur due to the restricted flow of material caused by the cap and liner layers (Fig. 2.10 (a)). In contrast, when electron flows from a metal line to a via, a void develops resulting in via depletion. Since the metal line width is higher with respect to via width, the current density inside a via is higher, causing a higher EM damage inside a via (Fig. 2.10 (b)).

Figure 2.10. Depletion of lines and vias in metal line [41].

### 2.3.4. Current Distribution Effects

An uneven distribution of current exacerbates the effects of electromigration and the creation of empty spaces (similar as Kirkendall effect). The development of voids results in localized irregularities in current density, and the heightened resistance around the voids triggers additional localized temperature increases, further expediting void formation. Conversely, localized reductions in current density can result in the deposition of migrated atoms, leading to a

further decrease in current density, additional material deposition, and the formation of hillocks, which can potentially lead to short circuits [48].

A non-uniform distribution of current density is sometimes called current crowding. It typically happens in regions with reduced resistance, particularly in localized areas, or in regions where the electric field strength is concentrated, such as at the boundaries of layers [43]. For example, when a current passes through a contact barrier, such as the metal/TiN interface near both the cathode and anode ends, the current crowding occurs, and this is influenced not just by the resistances of the metal and TiN materials but also by the contact resistance at their interface. A higher contact resistance results in reduced current crowding [49].

## 2.4 Electromigration Quantifications

Diffusion models are used to characterize the divergence in the material flow, which enables to understand the expected locations of material accumulation and depletion and the expected location of initial damage.

### 2.4.1. Black's Model

Based on empirical studies, in 1960, J.R. Black [50]-[53] was first to predict the lifespan of a metal line when exposed to electromigration. It was considered that the mean time to failure, MTTF, is inversely proportional to the rate of the mass transport,  $R_m$

$$MTTF \propto \frac{1}{R_m} \quad (2.3)$$

and the rate of the mass transport is proportional to the momentum transfer between thermally activated ions and conducting electrons:

$$R_m \propto n_e \Delta p N_a \quad (2.4)$$

where  $n_e$  is the density of conducting electrons,  $\Delta p$  is the momentum transfer from the electrons to the metal atoms, and  $N_a$  is the density of thermally activated ions. Furthermore, assuming that

both the electron density as well as the momentum transfer are proportional to the current density,  $j$ ,

$$n_e \propto j, \Delta p \propto j \quad (2.5)$$

and as activated ions follow an Arrhenius equation,

$$N_a \propto \exp\left(\frac{-E_a}{k_B T}\right) \quad (2.6)$$

the mean time to failure is modeled as:

$$\text{MTTF} = \frac{A}{j^2} e^{\frac{E_a}{k_B T}} \quad (2.7)$$

where  $A$  is a constant which comprises the material properties and the geometry of the interconnect,  $E_a$  is the activation energy,  $T$  is the absolute temperature, and  $k_B$  is Boltzmann's constant. It was found that not every experimental outcome followed (2.8); however, a fit could be achieved by introducing a variable exponent for the current density. Therefore, Black's equation was modified to [54]: and as activated ions follow an Arrhenius equation,

$$\text{MTTF} = \frac{A}{j^n} e^{\frac{E_a}{k_B T}} \quad (2.8)$$

where  $n$  is current density exponent, which can be experimentally determined. When  $n = 1$ , it represents a void growth phase where a pre-existing void is present, and for a void nucleation phase,  $n=2$  where a void is created due to a critical stress [53]. To evaluate the time to failure of any metal interconnect, empirically validated Black's equation has been predominately used within the EM community.

Black's equation measures MTTF of any metal interconnect under pure DC stress, however this equation has limitation when the EM stress is either unidirectional pulse DC or bidirectional AC. Moreover, it does not take into consideration the transitions between various materials and the conditions at the boundary layers [55]. Furthermore, parameters  $A$ ,  $n$  and  $E_a$  are technology

specific. A major limitation is that it is mainly intended for linear interconnects and might not be effectively applicable to complex network paths that include changes in direction. As a result, a few physics-based electromigration (EM) compact models have been recently introduced. These models explicitly describe void nucleation and evolution [56]-[58], which account for the time-dependent degradation of resistance in interconnect wires.

Physics-based electromigration modeling entails the use of a one-dimensional diffusion-drift equation. To solve this equation, it is necessary to have knowledge of the initial conditions, boundary conditions, transport parameters for the atomic species involved, the geometry of the structure, and the conditions under which the testing is conducted.

#### 2.4.2. EM Induced Material Transport Equations

Electromigration is a kinetic process involving the net transport of metal atoms over macroscopic distances, driven by the interplay between two competing mechanisms: diffusion and migration. Since atomic migration occurs through a vacancy exchange mechanism, it is appropriate to describe material transport in terms of vacancy flux. The vacancy flux is in the opposite direction to the atomic transport [59], [60].

Diffusion is a non-equilibrium process that stops once the system achieves full thermodynamic equilibrium. The laws of diffusion are mathematical equations that describe how the rate of diffusion is related to the concentration gradient causing the mass transfer [60], [66].

Vacancies flow from high concentration regions to low concentration regions. According to Fick's first law, the flux of vacancies resulting from diffusion in any region of the metal line,  $J_{v(D)}$  is directly proportional to the gradient of the vacancy concentration  $C_v$ , [60] as expressed by:

$$J_{v(D)} = -D_v \frac{\partial C_v}{\partial x} \quad (2.9)$$

where  $D_v$  is the vacancy diffusion coefficient or vacancy diffusivity. Diffusion coefficients are related to temperature by the Arrhenius law [63], [64],

$$D_v = D_0 \exp\left(-\frac{E_a}{k_B T}\right) \quad (2.10)$$

where  $D_0$  is the diffusion coefficient, and  $E_a$  represents the activation energy for electromigration.

The electromigration driving force  $F_{res}$ , as discussed in section 2.3.1, acts on vacancies and induces an additional velocity component,  $v_d$  for the diffusing species, aligned with the direction of the force. Utilizing the Nernst-Einstein relationship, the drift velocity is expressed as [63], [64]:

$$v_d = m \times E \equiv \left(D_v \frac{eZ^*}{k_B T}\right) \times (\rho j), \quad (2.11)$$

where  $m$  denotes the mobility and  $E$  the electric field, and the vacancy flux due to electromigration,  $J_{v(EM)}$  is derived as follows [60]:

$$J_{v(EM)} = C_v v_d = C_v D_v \frac{eZ^* \rho j}{k_B T} \quad (2.12)$$

Under stress-assisted diffusion conditions, the migration process combines with diffusion. Vacancies tend to diffuse in one direction, while their migration under the influence of the electromigration force occurs in the opposite direction. Therefore, the net vacancy flux  $J_v$  in any part of the metal line due to the competition of Fickian diffusion and electromigration is given by [60],

$$J_v = J_{v(D)} + J_{v(EM)} = -D_v \frac{\partial C_v}{\partial x} + C_v D_v \frac{eZ^* \rho j}{k_B T} \quad (2.13)$$

Diffusion and electromigration fluxes lead to a redistribution of the vacancies in the metal line, causing divergence in vacancy flux, denoted as  $\nabla \cdot J_v$ . Since vacancy concentration is not a

conserved quantity, the continuity equation for vacancy conservation is described by Fick's second law, which is given by [53], [64]:

$$\frac{\partial C_v}{\partial t} = - \nabla \cdot J_v + G \quad (2.14)$$

where  $G$  is the source/sink term that represents the creation and annihilation of vacancies at specific sites within the metal line. These sites include grain boundaries, extended defects, and interfaces. Vacancies will accumulate if the divergence operator has a positive sign, and they will deplete if it has a negative sign.

Equations (2.13) and (2.14) are the fundamental continuum model equations that describe the behavior of vacancy concentration, accounting for the accumulation or depletion of vacancies due to diffusion and electromigration, as well as the effects of vacancy generation and annihilation, along an interconnect line.

Electromigration causes vacancies to drift toward the cathode end of an interconnect line, leading to a buildup of vacancies in that area. At the same time, this process results in a depletion of vacancies at the anode end. The lattice around a vacancy is slightly relaxed, so when vacancies accumulate, it results in a contraction of volume at the cathode. On the other hand, the depletion of vacancies causes the volume to expand at the anode end [28], [33], [64]. Due to the constraints imposed by the surrounding layers, such as the capping layer, barrier layer, and passivation in copper dual-damascene interconnects, the volumetric changes caused by vacancy accumulation and depletion cannot be fully accommodated. This leads to the development of a hydrostatic stress gradient within the metal line. At the cathode end, tensile stress is generated, while at the anode end, compressive stress develops, as shown in Fig. 2.11. This stress gradient acts as a back stress force that counteracts the forward atom migration driven by electromigration, ultimately reducing the overall diffusion flow [28], [33], [64].

Figure 2.11. Stress migration is a byproduct of EM and involves the migration of vacancies. It occurs in response to a hydrostatic stress gradient and acts as a back stress opposing the effect of forward migration caused by EM [33].

#### 2.4.3. Blech's Model

Blech [59]-[60] conducted an experiment involving the deposition of conductor islands onto a titanium nitride (TiN) film. These islands were subjected to high current density. Given that the conductor resistivity was significantly lower than that of the TiN layer, the high flow of current through the conductor stripe resulted in the movement of the stripe's ends.

Blech noted that, only the upstream end (relative to the electron flow) of the line exhibited movement with drift velocity mentioned in (2.11). Additionally, he observed that the movement of the upstream end ceased when the stripe reached a specific reduced length. Furthermore, he found that no drift was detectable below a certain threshold current density. These observations were formalized by taking into account the vacancy flux resulting from electromigration and the gradient of hydrostatic stress [34], [63] as captured by,

$$J_v = \frac{C_v D_v}{k_B T} \left( e Z^* j \rho - \Omega_a \frac{\partial \sigma}{\partial x} \right) \quad (2.15)$$

where  $J_v$  is the resulting vacancy flux, result of the applied electric field and gradient of hydrostatic stress,  $\Omega_a$  is atomic volume,  $\sigma$  is hydrostatic stress,  $\partial \sigma / \partial x$  is the gradient of the hydrostatic stress,

$x$  is the distance along the metal line in the direction of the electron flow, with  $x = 0$  at the cathode as shown in Fig. 2.12.

Figure 2.12. A two-terminal metal line with electron flow and current flow indicated by the arrow.

The equation suggests that a gradient in hydrostatic stress acts as a counterforce to electromigration. Therefore, electromigration comes to a halt when the opposing stress gradient, commonly referred to as "back stress," balances the electromigration driving force, resulting in a zero net flow, or  $J_v = 0$ . This equilibrium state is known as the "Blech Condition", defined by [61]:

$$\frac{\partial \sigma}{\partial x} = \frac{eZ^*j\rho}{\Omega_a} \quad (2.16)$$

Integrating (2.16) over the length of the interconnect, the stress expression becomes [65]:

$$\sigma(x) = \sigma_0 + \frac{eZ^*j\rho}{\Omega_a} x \quad (2.17)$$

where  $\sigma_0$  is the stress at  $x = 0$ . The equation demonstrates that when the backflow flux, caused by stress gradients, is equal to the electromigration flux, the stress exhibits a linear variation along the length of the line. Considering that the conductor line can withstand a maximum stress of  $\sigma_{\max}$ , a critical product of current density and interconnect length can be expressed as follows [59], [65]:

$$(jL)_{\text{Blech}} = \frac{\Omega_a(\sigma_{\max} - \sigma_0)}{eZ^*\rho j} \quad (2.18)$$

This critical  $jL$  product is called “Blech product”. The electromigration halts when the product of  $j$  and  $L$  falls below the critical value shown by the right-hand side of (2.16). If EM stops before the critical compressive stress,  $\sigma_{crit}$  required for failure at the anode, the segment becomes immune to failure and hence ‘immortal’. The Blech effect [60] or the Blech immortality condition are common names for this phenomenon. The critical "Blech product" for contemporary copper interconnects falls within the range of 2000 to 10000 amperes per centimeter (A/cm) [66]-[68]. Based on (2.16), a critical line length can be determined for a given current density  $j$ , ensuring that shorter lines are not susceptible to electromigration-induced failure. This is commonly referred to as the "Blech Length", represented by:

$$L_{Blech} = \frac{\Omega_a(\sigma_{crit} - \sigma_0)}{eZ^* \rho j} \quad (2.19)$$

Likewise, with a specified line length  $L$ , the maximum allowable current density, below which electromigration failure does not occur, is given by:

$$j_{Blech} = \frac{\Omega_a(\sigma_{crit} - \sigma_0)}{eZ^* \rho L} \quad (2.20)$$

One significant implication of the Blech effect is that during electromigration assessments, the  $jL$  product must be substantially higher than the critical product ( $jL$ )<sub>Blech</sub> for the particular test structure. Failure to meet this criterion can lead to delayed failures in the test structure, thus providing a misleading sense of safety [60], [65]. Furthermore, it is important to recognize that residual stresses arising from the fabrication process reduce the amount of stress needed for electromigration to reach the maximum threshold that the line can withstand. As a result, this leads to reduced values for the Blech length and the maximum permissible current density outlined in (2.19) and (2.20), respectively [60], [65].

#### 2.4.4. Kirchheim's Model

In the study by Blech, discussed in Section 2.4.3, it was discovered that electromigration induces back stresses, which can potentially delay device failure. The nature and origin of the back stress, however, were not clearly understood.

Kirchheim [53] was the first to incorporate the effect of transient back stress buildup in grain boundaries during electromigration which is caused by the transport and annihilation and production of vacancies. Self-consistent equations were derived describing vacancy electromigration through a grain boundary and the associated stress evolution.

Kirchheim proposed that when a vacancy, induced by electromigration, moves to the grain boundary, the neighboring atoms in the grain adjust or relax in response to the presence of the vacancy, which can result in a change in the volume of the grain by a fraction  $f$ , where  $f$  is the ratio of the volumes occupied by vacancies,  $\Omega_v$ , and lattice atoms,  $\Omega_a$  ( $f = \Omega_v/\Omega_a$ );  $f$  is called as relaxation factor, ( $0 < f < 1$ ) [56]. This change in the grain volume causes hydrostatic stress gradient, to change by a factor of  $f$ . The gradient of the mechanical stress serves as an additional driving force in the total vacancy flux equation mentioned before in (2.13), modified vacancy flux equation is expressed as:

$$J_v = J_{v(D)} + J_{v(EM)} + J_{v(\sigma)} = -D_v \frac{\partial C_v}{\partial x} + C_v D_v \frac{eZ^* \rho j}{k_B T} - \frac{C_v D_v}{k_B T} f \Omega_a \frac{\partial \sigma}{\partial x} \quad (2.21)$$

Where  $\sigma$  is the spherical part of the mechanical stress tensor. The first term on the right-hand side of (2.21) is due to the driving force of vacancy concentration gradient, the second term is due to the electric field, and the third term is due to the vacancy-induced stress gradient. Considering a vacancy sink/source as described in (2.14), the continuity equation can be rewritten as:

$$\frac{\partial C_v}{\partial t} = -\nabla \cdot J_v + G = -\frac{\partial}{\partial x} \left[ -D_v \left( \frac{\partial C_v}{\partial x} - \frac{eZ^* j \rho}{k_B T} C_v + \frac{f \Omega_a}{k_B T} C_v \frac{\partial \sigma}{\partial x} \right) \right] - \frac{C_v - C_{veq}}{\tau_s} \quad (2.22)$$

The last term  $(C_v - C_{veq})/\tau_s$  describes the annihilation or production of vacancies, in which  $\tau_s$  is the relaxation time. The equilibrium vacancy concentration,  $C_{veq}$  in a grain boundary is defined as [53],

$$C_{veq} = C_{v0} \exp \left[ \frac{(1-f)\Omega_a \sigma}{k_B T} \right] \quad (2.23)$$

where  $C_{v0}$  is the equilibrium vacancy concentration, in the absence of stresses. A change in vacancy generation produces the volumetric strain in a grain which is expressed as [56]:

$$\frac{\Delta V}{V} = (1-f)\Omega_a \frac{\delta}{d} \Delta C_v \quad (2.24)$$

where  $(1-f)\Omega_a$  is the volume change due to lattice relaxation, when a vacancy is considered as a substitutional atom,  $\delta$  is the grain boundary thickness,  $d$  is the grain diameter, and  $\Delta C_v$  is the generated vacancy concentration. The strain rate is given by [50]:

$$\frac{1}{V} \frac{\partial V}{\partial t} = (1-f)\Omega_a \frac{\delta}{d} \left( \frac{C_v - C_{veq}}{\tau_s} \right) \quad (2.25)$$

Applying Hooke's law ( $\partial\sigma = B \partial V/V$ ), where  $B$  is the effective elastic bulk modulus for the material that surrounds the interconnect, the stress rate evolution is given by [56]:

$$\frac{\partial \sigma}{\partial t} = B(1-f)\Omega_a \frac{\delta}{d} \left( \frac{C_v - C_{veq}}{\tau_s} \right) \quad (2.26)$$

By coupling the stress development equation (2.26) with the vacancy concentration dynamics equation (2.22) along the metal line, analytical solutions can be derived that relate the mechanical stress to the production/annihilation of vacancies at the grain boundary for several limiting cases. Additionally, Kirchheim identified three phases in the evolution of vacancy concentration and stress, which play a crucial role in understanding the electromigration phenomenon in 3D interconnects [60].

In summary, in Kirchheim's Model,  $\sigma(x, t), J_v(x, t), C_v(x, t)$  are computed by solving trinity of (2.21), (2.22), (2.26), and from which the nucleation and failure times can be computed.

**Void nucleation time and location:**  $(x_{nuc}, t_{nuc}) := \arg \min_t \max_x \sigma(x, t) > \sigma_{critical}$ , i.e., it finds earliest time for which exists a location where stress exceeds a critical value.

**Void growth time and location (which can also be viewed as failure time and location):**  $(x_g, t_g) := \arg \min_t \max_x V(x, t) > V_{critical}$ , where  $V(x, t)$  is the void volume at  $t$  and  $x$ . I.e., it finds the earliest time for which exists a location where void volume exceeds a critical value. (Need a relation to map  $\sigma, J_v, C_v$  to  $V$  to then compute  $t_g$  and  $x_g$ .)

Keeping in mind that  $B$  is determined by the elastic moduli and the dimensions of the refractory metal liner, the dielectric diffusion barrier, and the dielectric material, its magnitude may vary along the length of the interconnect, especially in the vicinity of the anode and cathode. It's crucial to recall that the elastic bulk moduli of low- $\kappa$  dielectrics are considerably lower than that of  $\text{SiO}_2$  (by roughly a factor of 10). Equation (2.26) demonstrates the relationship between stress buildup and the deviation of vacancy concentration from its equilibrium state, highlighting the significant impact of  $\tau_s$  on stress development. It is essential to understand that this model accounts for different mechanisms of vacancy generation or annihilation, encompassing processes that take place within the grain boundary, at adjacent grain boundaries, or at dislocations located within the bulk of the grain. These mechanisms result in vacancy relaxation times,  $\tau_s$  to be of smaller, median, or larger values. Equations (2.22) and (2.26) form a nonlinear system of differential equations which require numerical solutions. Nevertheless, Kirchheim derived analytical solutions for certain limiting cases, identifying three main stages in the evolution of vacancies and stress [53], [56].

The initial phase denotes a short duration with very low initial stress. As a result, the equilibrium vacancy concentration remains unchanged, and the vacancy concentration continues to evolve until it reaches a condition of quasi-steady state. This quasi-steady-state phase is prolonged, characterized by only slight variations in vacancy concentration, while stress levels