# Electrical Safe Operating Area and Latent Damage of SiC Low-Voltage nMOS Under TLP and VF-TLP Stresses

Pengyu Lai<sup>ID</sup>, Hui Wang, H. Alan Mantooth<sup>ID</sup>, *Fellow, IEEE*, and Zhong Chen<sup>ID</sup>, *Member, IEEE*

**Abstract**—In this article, transmission line pulse (TLP) and very fast TLP (VF-TLP) systems were utilized to characterize the electrical safe operating areas (SOAs) and latent damage of silicon carbide (SiC) low-voltage nMOS devices to investigate their electrostatic discharge (ESD)-related reliability performance. The gate oxide breakdown voltages of SiC nMOS with varying gate oxide thickness were measured by dc, TLP, and VF-TLP. The TLP and VF-TLP waveforms at breakdown points were also presented and discussed. ESD capability of SiC nMOS devices with gate lengths varying from 1 to 6  $\mu\text{m}$  was also characterized by TLP and VF-TLP. Their ESD behaviors and failure mechanisms were discussed. Scanning electron microscopy (SEM) and technology computer-aided design (TCAD) simulations were also carried out to understand the failure mechanism. At last, the ESD-induced latent damage on SiC nMOS was characterized. A decrease in threshold voltage and an increase in drain leakage current were observed with the increase in stress cycles. The latent damage is mainly due to the gate oxide injected carriers during the avalanche operation and can be recovered after 200 °C anneal.

**Index Terms**—CMOS devices, electrostatic discharge (ESD), latent damage, low-voltage silicon carbide (SiC), safe operating area (SOA).

## I. INTRODUCTION

SILICON carbide (SiC) is a promising semiconductor material for high-voltage (HV) and high-temperature applications due to its wide bandgap, low intrinsic carrier concentration, and high thermal conductivity [1]. In order to further improve the high-temperature performance of electronic systems, a variety of integrated circuits (ICs) have been designed and manufactured in SiC-based bipolar and CMOS technologies [2], [3], [4], [5], [6]. Although these ICs are capable of operating up to 600 °C, their reliability

Received 19 July 2024; revised 10 September 2024; accepted 1 October 2024. Date of publication 22 October 2024; date of current version 2 December 2024. This work was supported in part by the National Science Foundation under Award 2131972 and in part by the Army Research Laboratory under Contract W911NF2120231. The review of this article was arranged by Editor D. Sheridan. (*Corresponding author: Zhong Chen.*)

The authors are with the Department of Electrical Engineering and Computer Science, University of Arkansas, Fayetteville, AR 72701 USA (e-mail: chenz@uark.edu).

Color versions of one or more figures in this article are available at <https://doi.org/10.1109/TED.2024.3475997>.

Digital Object Identifier 10.1109/TED.2024.3475997

is not sufficiently explored yet. Among reliability issues, electrostatic discharge (ESD) has been identified as one of the most significant concerns for modern ICs and electronic systems. As a result, a few SiC-based ESD protection devices have been proposed and investigated to improve the reliability of SiC ICs [7], [8], [9], [10], [11]. For example, Lai et al. [7] reported an HV silicon-controlled rectifier (HV-SCR) structure that was fabricated by a 4H-SiC bipolar-CMOS-DMOS (BCD) process. The HV-SCR shows a relatively higher failure current compared to SiC nMOS and LDMOS. Furthermore, Do et al. [8], [9], [10], [11] also proposed SiC-based gate-body-floating nMOS (GBFNMOS), high-holding floating gate nMOS (HHFGNMOS), low-voltage SCR, and lateral insulated-gate bipolar transistor-based SCR (LGBT-SCR) for ESD protection. High failure current and reliable thermal performance were observed in these devices.

Besides the development of SiC-based ESD protection devices, the ESD-related reliability of the devices under protection (e.g., CMOS devices) needs to be studied. For conventional silicon (Si) based CMOS devices, their electrical safe operating area (SOA, e.g., gate oxide breakdown and drain–source failure current) and latent damage induced by ESD stresses are usually investigated to evaluate their reliability [12], [13], [14], [15], [16], [17], [18]. Weir et al. [12], Malobabic et al. [13], and Wu and Rosenbaum [14] investigated Si-based gate oxide reliability under ESD conditions. Transmission line pulse (TLP) and very fast TLP (VF-TLP) were utilized to characterize the oxide breakdown voltage, and various models were proposed to analyze the failure mechanism. Amerasekera et al. [15] characterized and analyzed the parasitic n-p-n of Si-based nMOS in the 0.2  $\mu\text{m}$  CMOS process. A methodology was proposed to improve the drain–source failure current ( $I_{t2}$ ) of short-channel and thin-oxide nMOS devices. Cester et al. [16], Huh et al. [17], and Groeseneken [18] studied the latent damage of Si nMOS devices under ESD stresses. The transconductance, saturation current, and drain–source leakage current showed significant degradation after nondestructive ESD stresses. On the other hand, very few researches have been carried out on the ESD-related reliability of SiC-based devices. Phulpin et al. [19] investigate the ESD robustness of SiC-based MESFETs. A Zener diode and a Schottky diode were embedded in the SiC MESFETs to increase the drain–source  $I_{t2}$ . In previous

work [20], we reported ESD characteristics of 15 V SiC nMOS in the Raytheon high-temperature SiC (HiTSiC) process to explore ESD robustness. The SOAs of low-voltage SiC nMOS devices with varying channel widths, gate lengths, and gate bias conditions were characterized by a TLP system. However, the gate oxide breakdown voltage, failure mechanisms, and latent damage of the SiC low-voltage nMOS have not been sufficiently analyzed.

In this article, a systematic study of ESD reliability was conducted on SiC-based low-voltage nMOS devices. TLP and VF-TLP were utilized to stress the devices. The research is divided into six sections. In Section II, the gate oxide breakdown of SiC nMOS with varying oxide thickness under dc, TLP, and VF-TLP stresses are reported. In Section III, the drain–source  $I_{ds}$  of SiC nMOS devices with varying gate lengths and gate bias conditions are presented. Scanning electron microscopy (SEM) and technology computer-aided design (TCAD) simulations were carried out to analyze the failure mechanism. The latent damage of SiC low-voltage nMOS devices is investigated in Section IV. Repetitive TLP and VF-TLP pulses were applied to the drain terminals of the nMOS devices. Drain–source current was characterized after the stresses to analyze the latent damage. Finally, the discussion and conclusion are provided in Sections V and VI.

## II. GATE OXIDE BREAKDOWN UNDER ESD STRESSES

Gate dielectric breakdown is one of the most important reliability concerns for MOS devices. Scores of researchers argued that the oxide reliability for SiC-based MOS devices was worse than that for Si counterparts due to the low conduction-band offset of the SiC-SiO<sub>2</sub> interface [21], [22]. However, some researchers claimed that the gate oxide breakdown voltage could be further improved [23]. Therefore, in order to demonstrate the SOAs of SiC CMOS devices under ESD conditions, gate oxide breakdown voltage needs to be investigated.

### A. Experimental Setup

Gate oxide breakdown of SiC-based lateral nMOS devices was characterized by dc, TLP, and VF-TLP systems. For dc characterization, a Keithley 2450 source measure unit (SMU) was utilized as the voltage source and current meter. For TLP and VF-TLP measurements, an ES620 system by ESDEMC was implemented. The rise times of the TLP and VF-TLP pulses are 10 ns and 100 ps, and the pulse widths of the TLP and VF-TLP are 100 and 10 ns, respectively. The waveforms were captured by a Keysight MSO-6004A oscilloscope. The gate leakage current was measured at 2 V bias after each TLP and VF-TLP pulse to monitor the device failure point. The failure points (i.e., the breakdown points of the gate oxide in this section) of the devices are defined at which the dc gate leakage current increases by over 100%.

SiC nMOS devices with varying gate oxide thickness of 35, 50, and 80 nm were characterized. The nMOS devices with 35 nm gate oxide thickness were fabricated by Raytheon HiTSiC CMOS process, and their recommended supply voltage is 15 V [24]. The nMOS devices with gate oxide

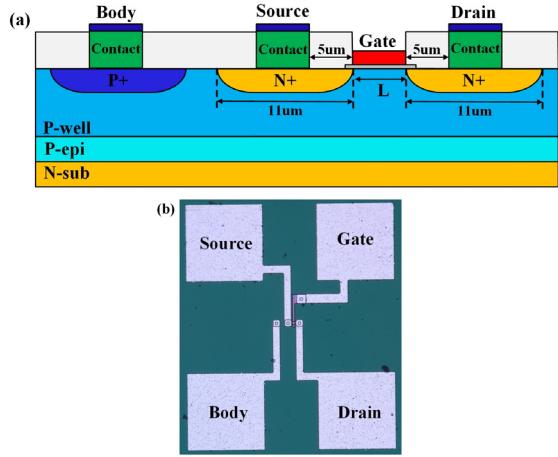

Fig. 1. (a) Cross-sectional view and (b) layout view of the measured SiC nMOS.

thicknesses of 50 and 80 nm were fabricated by the 4H-SiC BCD process of Fraunhofer Institut für Integrierte Systeme und Bauelementetechnologie (IISB) in Germany [25]. The recommended supply voltages for the nMOS with 50 and 80 nm gate oxide are 20 and 30 V, respectively. Fig. 1(a) and (b) shows the cross-sectional view and layout view of the nMOS. N-type polysilicon was deposited on the gate oxide as the gate terminal. Nickel/aluminum alloy is used as the contact silicide for N+ regions. The three processes provide nMOS devices with a minimum gate length ( $L$ ) of 1  $\mu$ m, and the channel width and  $L$  of the nMOS devices measured in this section are 3 and 1  $\mu$ m. The stresses were applied to the gate terminals of the devices, and drain, source, and body terminals were grounded during the measurements.

### B. Experimental Results

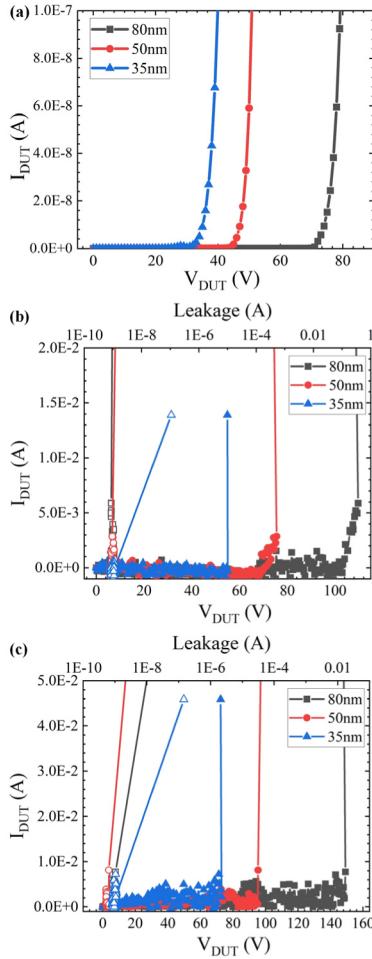

Fig. 2(a)–(c) shows the  $I$ – $V$  curves of SiC nMOS gate oxide under dc, TLP, and VF-TLP stresses. The data with solid symbols correspond to the  $I_{DUT}$  and  $V_{DUT}$ , and the data with open symbols corresponds to the gate leakage current after each TLP (or VF-TLP) pulse. The oxide breakdown voltage decreases with the increase of the pulselength due to the cumulative damage of longer pulses. The breakdown voltages of 50 nm gate oxide under TLP and VF-TLP stresses are 75.5 and 95.4 V, respectively. Meanwhile, the breakdown voltage of the gate oxide increases with the oxide thickness. For example, the breakdown voltage under TLP stresses from 55 to 109.7 V with the oxide thickness varying from 35 to 80 nm. Anode-hole injection model is usually utilized to illustrate and analyze the oxide breakdown [12], [26]. During the pulse stresses, electrons and holes tunnel through the oxide region, and a portion of the tunneling holes generate defects in the oxide. When a critical number of defects is generated, the oxide is bridged by overlapping defects, which triggers the breakdown. This can be expressed as [12] and [26]

$$T_{BD} = \left( \frac{N_{BD}}{k} \right)^{1/n} \frac{1}{J_h} \quad (1)$$

where  $T_{BD}$  is the time to break down,  $N_{BD}$  is critical defect density,  $n$  is trap generation rate,  $J_h$  is hole current density, and

Fig. 2. SiC nMOS gate oxide  $I$ - $V$  curves under (a) dc, (b) TLP, and (c) VF-TLP stresses.

Fig. 3. Voltage and current waveforms of 50 nm gate oxide breakdown under (a) TLP and (b) VF-TLP stresses.

$k$  is lattice-hole generation coefficient which increases with the increase of oxide electric field. The increase of the oxide thickness decreases the oxide electric field. Therefore, nMOS devices with thicker oxide show higher breakdown voltages.

Fig. 3 shows the voltage and current waveforms of 50 nm SiC nMOS gate oxide breakdown under TLP and VF-TLP

stresses. As shown in Fig. 3(a), the oxide failure takes place at  $\sim 69$  ns after the initial occurrence of the TLP pulse. The voltage drops from  $\sim 78$  to  $\sim 55$  V, and the current increases from  $\sim 0.05$  to  $\sim 0.3$  A. After the hard failure, the leakage current increases from  $\sim 900$  to  $\sim 10 \mu$ A [Fig. 2(b)]. Similar behaviors were observed under VF-TLP conditions [Fig. 3(b)].

### III. ESD CAPABILITY OF SiC nMOS WITH PARASITIC N-P-N

The ESD performance of nMOS devices is strongly related to their parasitic lateral n-p-n bipolar junction transistors (BJTs), especially when implemented as output buffers. ESD generates a high voltage that reaches the avalanche breakdown voltage of the drain-substrate junction of nMOS devices. The avalanche-generated current then forward-biases the base-emitter junction of the parasitic n-p-n (i.e., substrate-source junction of the nMOS) in the nMOS device, and the parasitic n-p-n is turned on. The nMOS may show a voltage drop due to the turn-on of the parasitic n-p-n, which is the so-called snapback. It has been demonstrated that the current gain of the parasitic n-p-n affects the operation of the nMOS under ESD conditions, such as the snapback holding voltage ( $V_h$ ) as well as the trigger voltage ( $V_{t1}$ ) and  $I_{t2}$  [27]. Therefore, SiC nMOS devices with associated lateral n-p-n were characterized by TLP and VF-TLP in this section to investigate their ESD-related SOAs.

#### A. Experimental Setup

SiC lateral nMOS devices that were fabricated by the 4H-SiC BCD process of Fraunhofer IISB were characterized by TLP and VF-TLP systems. The gate oxide thickness of the devices is 50 nm, and the  $L$  of the devices varies from 1 to 6  $\mu$ m. All the devices are one-finger with a channel width of 100  $\mu$ m. The TLP and VF-TLP pulses were applied to the drain terminals of the devices with the gate, source, and body grounded. The rise time and pulselength of the TLP and VF-TLP are the same as the setup in Section II. The leakage current was measured with a 10 V bias to monitor the failure of the devices. After the device failure, drain-source leakage current with gate and body floating and drain-gate leakage current with source and body floating were measured to investigate the failure mode. SEM was utilized to observe the failure points. The 2-D TCAD simulations were carried out by Synopsys Sentaurus to understand the failure mechanisms. SiC nMOS devices with varying gate bias voltages ( $V_G$ ) were also characterized by TLP and VF-TLP.

#### B. SiC nMOS With Gate Grounded

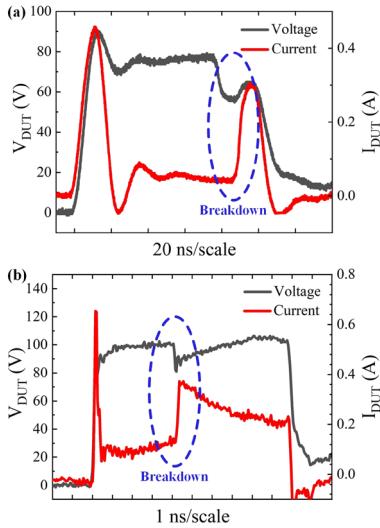

Fig. 4 shows the TLP and VF-TLP characterizations of SiC nMOS with  $L$  varying from 1 to 6  $\mu$ m. The devices did not show snapback behaviors as Si-based nMOS devices. The snapback of the nMOS is strongly related to the current gain ( $\beta$ ) of the parasitic lateral n-p-n bipolar transistor. The requirement of the snapback is defined as [27]

$$\beta(M - 1) > 1 \quad (2)$$

Fig. 4. (a) TLP and (b) VF-TLP characterization results of SiC nMOS with varying  $L$ .

where  $M$  is the multiplication factor of the avalanche. The current gain of an n-p-n is determined by intrinsic doping concentrations, minority diffusion constants, and widths of base and emitter regions [28]. Compared to commonly used Si-based nMOS, since SiC nMOS devices have a stronger bandgap narrowing effect [29], lower minority carrier mobility [30], and wider base regions (i.e.,  $L$ ), the current gain of the parasitic n-p-n is too low to show snapback behaviors. In addition, the  $I_{t2}$  of the nMOS with  $1\mu\text{m}$   $L$  under TLP stress is  $\sim 162$  mA, and it decreases to  $\sim 132$  mA when the  $L$  increases to  $2\mu\text{m}$ . This is because the increase of  $L$  increases the ON-resistance and failure voltage ( $V_{t2}$ ). The device failure is mainly caused by the thermal limit of the reversed p-n junction (i.e., drain to substrate junction). The increase of  $V_{t2}$  increases the junction power, which generates more heat in the junction region and decreases the  $I_{t2}$  [31]. Additionally, for VF-TLP measurements, the  $I_{t2}$  of the nMOS with  $1\mu\text{m}$   $L$  is  $\sim 341$  mA, and it decreases to  $\sim 243$  mA when the  $L$  increases to  $2\mu\text{m}$ . Due to the decrease of the pulselength, less heat was generated in the device junction, which increases the  $I_{t2}$ .

It should be noted that the  $I_{t2}$  of the nMOS with  $L$  of  $6\mu\text{m}$  under both TLP and VF-TLP stresses is much lower than that of short-channel nMOS devices (i.e.,  $L < 2\mu\text{m}$ ). In order to figure out the failure mode, the drain-source leakage current and drain-gate leakage current were measured after the device failure. Table I lists the leakage current of the failure devices at  $10\text{ V}$  bias. The drain-gate leakage current of the nMOS with  $6\mu\text{m}$   $L$  is higher than  $10\text{ nA}$ . This indicates that the failure of the devices is due to gate oxide breakdown instead of junction thermal runaway. This may be an important difference between SiC

TABLE I

SiC NMOS LEAKAGE CURRENT AFTER TLP AND VF-TLP FAILURE

| Gate length       | TLP             |               | VF-TLP          |               |

|-------------------|-----------------|---------------|-----------------|---------------|

|                   | Drain to source | Drain to gate | Drain to source | Drain to gate |

| 1 $\mu\text{m}$   | 1.82E-6         | 1.5E-10       | 5.44E-3         | 1.66E-10      |

| 1.5 $\mu\text{m}$ | 4.01E-4         | 1.86E-10      | 7.91E-5         | 1.48E-10      |

| 2 $\mu\text{m}$   | 1E-4            | 1.6E-10       | 2.64E-5         | 1.5E-10       |

| 6 $\mu\text{m}$   | 1.1E-10         | 7.97E-8       | 1.72E-10        | 9.28E-4       |

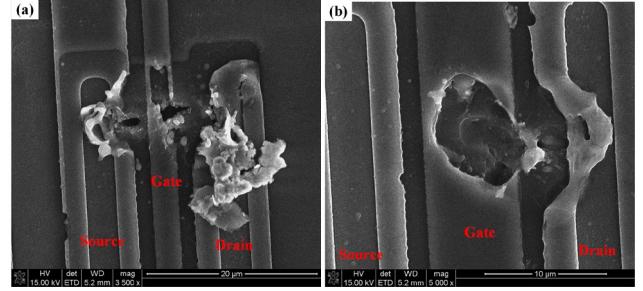

Fig. 5. SEM photographs of SiC nMOS with (a)  $1\mu\text{m}$   $L$  and (b)  $6\mu\text{m}$   $L$  after TLP failure.

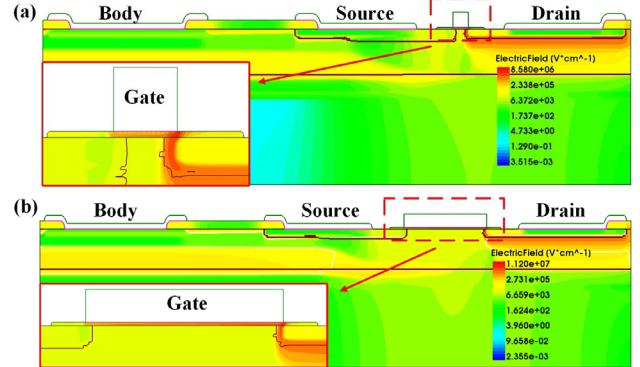

Fig. 6. Simulated electric field distribution of SiC nMOS with (a)  $1\mu\text{m}$   $L$  and (b)  $6\mu\text{m}$   $L$  at failure voltages.

and Si nMOS devices as the gate oxide breakdown under this condition occurs when the gate oxide is thinner than  $3\text{ nm}$  for Si-based nMOS [15]. Since SiC nMOS devices do not show snapback behaviors, the failure threshold of long-channel devices is determined by the gate oxide breakdown.

SEM was utilized to observe the damages of the TLP on the SiC nMOS devices. The SEM photographs of SiC nMOS devices with 1 and 6  $\mu\text{m}$   $L$  are shown in Fig. 5. The thermal filament of 1  $\mu\text{m}$  SiC nMOS spreads from the drain contact to the source contact while the filament defect is only observed on drain and gate terminals for 6  $\mu\text{m}$   $L$  SiC nMOS. This also verifies that the early failure of the long-channel nMOS (i.e.,  $L = 6\mu\text{m}$ ) is due to the gate oxide breakdown.

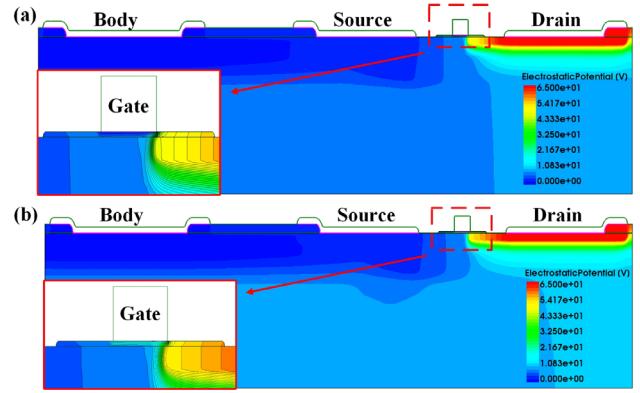

TCAD simulations were carried out by Sentaurus to understand the failure mode of the nMOS devices. In order to increase the simulation precision Monte-Carlo-based ion implantation was performed to form the p-well, N+, and P+ regions. The ion implantation profiles were extracted from the real process. Transient-based ESD simulations were performed by Sentaurus Device to extract the electric field distribution of the SiC nMOS. Fig. 6 shows the simulated electric field

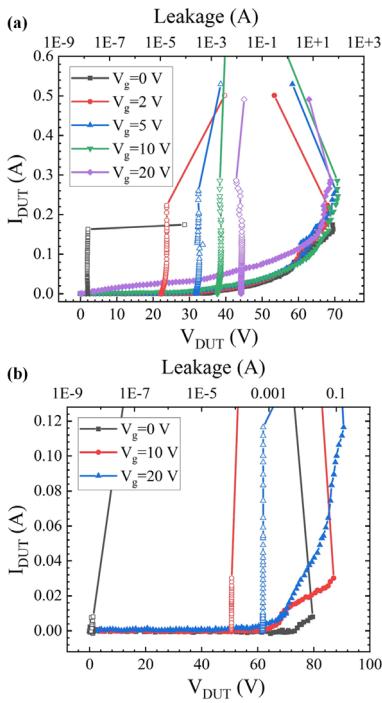

Fig. 7. TLP characterization results of SiC nMOS of (a)  $1\text{ }\mu\text{m}$   $L$  and (b)  $6\text{ }\mu\text{m}$   $L$  with varying  $V_G$ .

distribution of the SiC nMOS at the failure voltages (i.e., drain voltage of 70 and 80 V for  $L$  of 1 and  $6\text{ }\mu\text{m}$  respectively). The electric field in the gate oxide of  $1\text{ }\mu\text{m}$   $L$  nMOS is  $\sim 8.5\text{ MV/cm}$  while it is  $\sim 11.2\text{ MV/cm}$  for the  $6\text{ }\mu\text{m}$   $L$  nMOS.

### C. SiC nMOS With Gate Bias ( $V_G$ )

For gate-controlled devices (e.g., nMOS, LDMOS, and gate-controlled SCR), the ESD behaviors are related to the gate bias voltage.  $V_G$  provides seed current to the substrate, which helps trigger the parasitic n-p-n and reduces  $V_{t1}$  [27]. Besides, it turns on the inversion channel of nMOS, which helps discharge the ESD current and increases  $I_{t2}$  [32]. Therefore, the 1 and  $6\text{ }\mu\text{m}$   $L$  nMOS devices with gate bias were characterized by the TLP system. The TLP measurement results are shown in Fig. 7. For the nMOS with  $1\text{ }\mu\text{m}$   $L$ ,  $I_{t2}$  increases from  $\sim 162$  to  $\sim 285\text{ mA}$  when  $V_G$  increases to  $10\text{ V}$ , and it shows little change when  $V_G$  increases to  $20\text{ V}$ . This is similar to conventional Si-based nMOS [32]. For the nMOS with  $6\text{ }\mu\text{m}$   $L$ ,  $I_{t2}$  increases from  $\sim 8$  to  $\sim 116\text{ mA}$  when  $V_G$  increases to  $20\text{ V}$ . The increase of  $V_G$  reduces the drain-gate voltage drop, which increases  $V_{t2}$  and  $I_{t2}$ .

## IV. ESD-INDUCED LATENT DAMAGE ON SiC nMOS

Besides the hard failure caused by ESD stresses, latent damage induced by nondestructive ESD stresses also needs to be studied since CMOS devices showed degradation after nondestructive ESD stresses [16], [17], [18]. Therefore, in this section, TLP and VF-TLP stresses were applied to SiC nMOS devices to investigate ESD-induced latent damage.

### A. Experimental Setup

SiC lateral nMOS devices that were fabricated by the 4H-SiC BCD process of Fraunhofer IISB were characterized

by TLP and VF-TLP systems. For each experiment, three identical devices were characterized. Since the results are very similar, only one of the devices is presented in this article. The gate oxide thickness, gate length, and width of the SiC nMOS devices are  $50\text{ nm}$ ,  $1\text{ }\mu\text{m}$ , and  $100\text{ }\mu\text{m}$ , respectively. The rise times and pulse widths of the TLP and VF-TLP were kept the same as the setup in Sections II and III, and the drain leakage current was monitored at  $10\text{ V}$ . Repetitive TLP and VF-TLP pulses were stressed to the drain terminals of the devices with the device source and body grounded. The pulses were kept at voltage levels which generate 60% of the device  $I_{t2}$ . After the stress cycles of 10, 50, 100, 200, 500, and 1000 pulses, the devices were cooled down for 5 min to eliminate heat accumulation. Then TLP (or VF-TLP)  $I$ - $V$  curves, drain current versus gate voltage (i.e.,  $I_D$ - $V_G$ ) curves, and leakage current were measured. The  $I_D$ - $V_G$  curves were characterized by a Keysight B1505 curve tracer, and the drain leakage current was extracted at  $10\text{ V}$  by a Keithley 2450 SMU. Finally, the devices were annealed for  $10\text{ h}$  at  $200\text{ }^\circ\text{C}$  in a high-temperature oven (i.e., Fisher Scientific 650-126). Then the TLP (or VF-TLP)  $I$ - $V$  curves,  $I_D$ - $V_G$  curves, and leakage current of the devices were measured after  $10\text{ h}$  cooled down to observe whether the latent damage could be recovered. In addition, in order to compare the latent damage between the SiC and Si, a Si-based 5 V nMOS device that was fabricated on a  $0.18\text{ }\mu\text{m}$  BCD process was also characterized. The gate oxide thickness, gate length, and width of the device are  $14\text{ nm}$ ,  $1\text{ }\mu\text{m}$ , and  $100\text{ }\mu\text{m}$ . For the convenience of the measurement, a silicide block layer was applied to the drain of the Si nMOS to increase  $I_{t2}$ . The experimental conditions for the Si nMOS were the same as the SiC nMOS except that the drain leakage current was monitored and measured at  $5\text{ V}$ . Moreover, the drain-gate leakage current of the SiC and Si nMOS devices was also measured with varying drain voltage ( $V_D$ ). The measurements were carried out by a Keysight B1505 curve tracer, and the voltage was applied to the drain terminals with gate, body, and source terminals grounded.

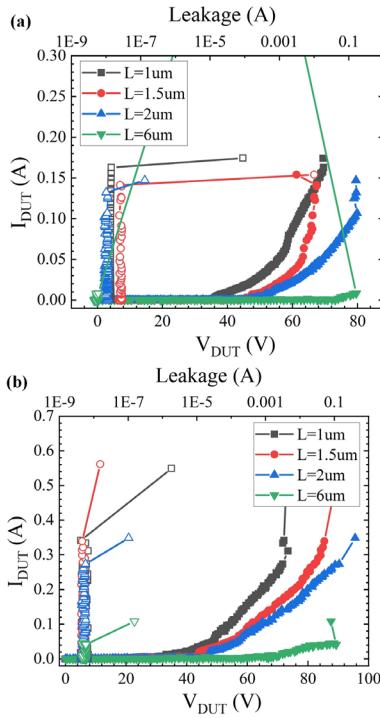

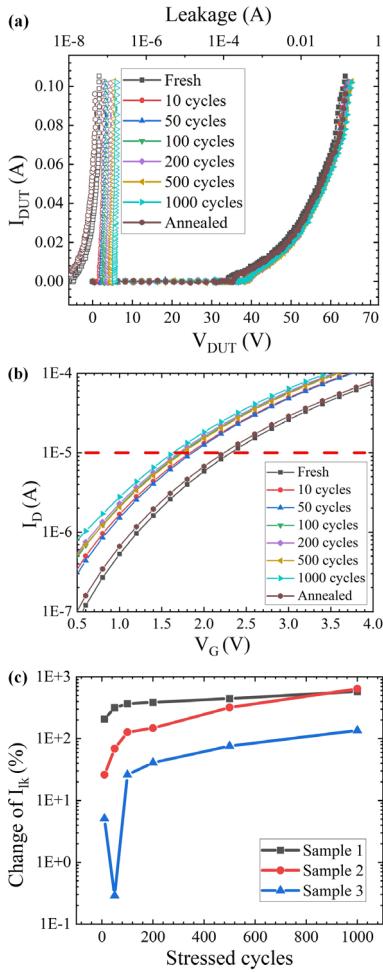

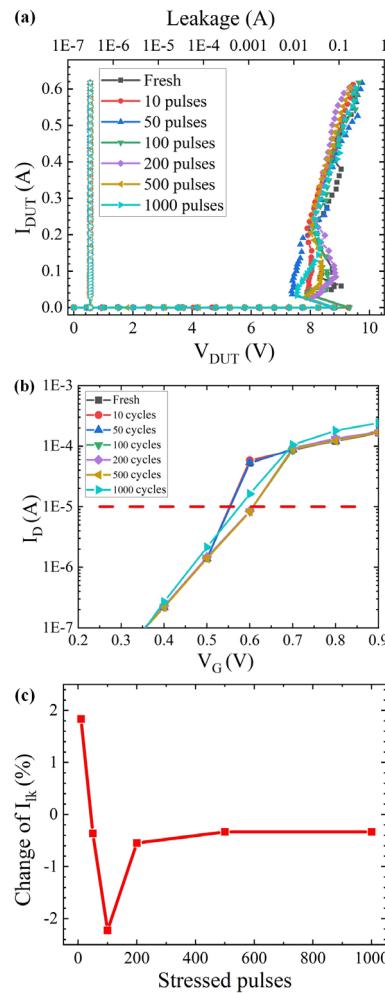

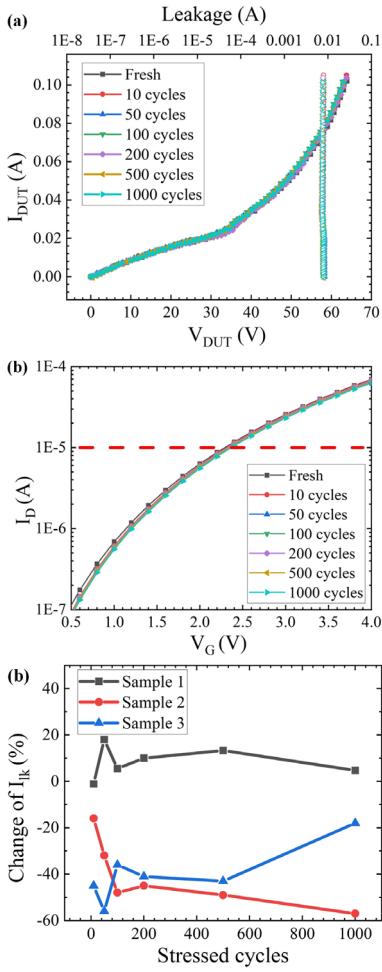

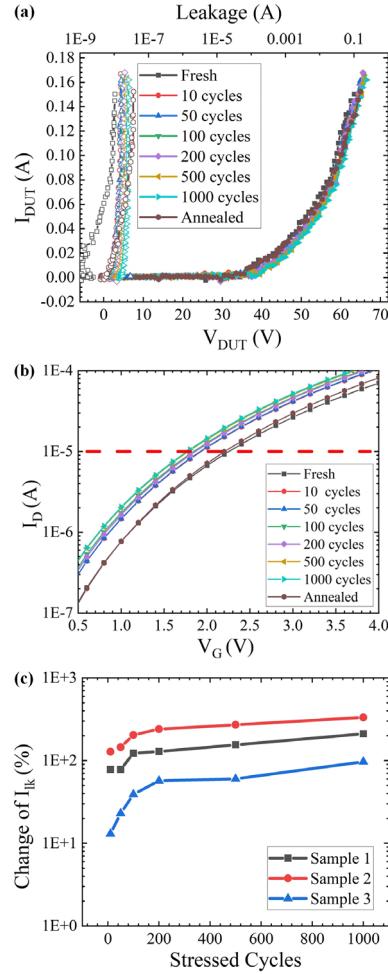

### B. Repetitive TLP Stresses on SiC ggNMOS

The variation of the SiC gate-ground nMOS (ggNMOS) after TLP stresses is shown in Fig. 8. The trigger voltage,  $V_{t1}$ , of the device increases from  $34.1$  to  $38.6\text{ V}$  after ten cycles of stresses. Then  $V_{t1}$  shows little change after 1000-cycle stresses.  $V_{t1}$  was recovered to  $35.6\text{ V}$  after the anneal. Additionally, little degradation was observed on the ON-resistance of the device. The  $I_D$ - $V_G$  curves are shown in Fig. 8(b) to compare the threshold voltage ( $V_{th}$ ) at which the drain current reaches  $0.1\text{ }\mu\text{A}/\mu\text{m}$  (i.e.,  $10\text{ }\mu\text{A}$  for nMOS with  $100\text{ }\mu\text{m}$  width). The threshold voltage shows an evident shift (i.e., from  $2.4$  to  $2\text{ V}$ ) after ten-cycle stresses and a slight decrease from ten cycles to 1000 cycles. After  $200\text{ }^\circ\text{C}$  anneal,  $V_{th}$  recovers to  $2.3\text{ V}$ . The drain leakage current,  $I_{lk}$ , shifts of the measured devices are shown in Fig. 8(c). The drain leakage current keeps increasing with the stressing cycles. After 1000 cycles of stresses, the leakage current increases by over 500% for Sample 1 and Sample 2.

During the avalanche operation, hot electrons and holes, especially in the gate-drain overlap region, can gain sufficient

Fig. 8. Variation of SiC ggNMOS after TLP stresses (a) TLP curves, (b)  $I_D$ – $V_G$  curves, and (c) drain leakage current.

energy to surmount or tunnel through the gate oxide due to the strong vertical electric fields. This generates oxide traps, interface traps, and trapped charges, which reduces  $V_{th}$  and increases drain–source leakage current,  $I_{lk}$  [28]. After annealing, the trapped charges were recovered by thermal emission [28]. As a result, the  $V_{th}$  increases to 2.3 V. It should be noted that although the  $V_{t1}$  was also recovered by the annealing process, it may not be due to the trapped charges. This needs further investigation.

In order to compare the latent damage between SiC and Si devices, a Si-based nMOS was also characterized by the TLP system. Fig. 9 shows the variation of the Si ggNMOS after TLP stresses. The TLP  $I$ – $V$  curves,  $I_D$ – $V_G$  behaviors, and leakage current show little change after 1000 cycles of TLP stresses. This may be because the Si nMOS has lightly doped drain (LDD) implant regions and a low  $V_h$  (i.e.,  $\sim 8$  V), which leads to fewer carrier injection into the gate oxide region compared to the SiC nMOS.

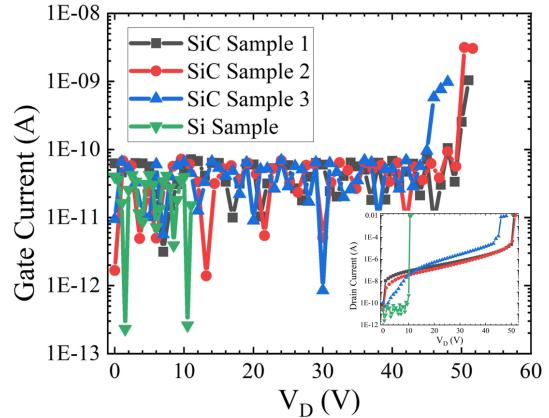

The transient drain–gate leakage current is difficult to monitor under TLP stresses. Thus, drain–gate leakage currents with varying  $V_D$  of the SiC and Si nMOS devices were measured by a curve tracer (i.e., dc conditions). Since the devices are easy to be destroyed under dc conditions, the drain current was limited to 10 mA. Fig. 10 shows the drain–gate leakage

Fig. 9. Variation of Si ggNMOS after TLP stresses (a) TLP curves, (b)  $I_D$ – $V_G$  curves, and (c) drain leakage current.

Fig. 10. Drain–gate leakage current with varying  $V_D$ .

current versus  $V_D$ , and the inset shows the total drain current versus  $V_D$ . It should be noted that the measured drain–gate leakage currents are negative while the absolute values were plotted. As shown in Fig. 10, the drain–gate leakage currents of SiC and Si devices are lower than 100 pA before the avalanche breakdown. When  $V_D$  reaches the avalanche breakdown voltage (i.e.,  $\sim 50$  V in the inserted figure), the drain–gate currents of the SiC nMOS devices show a significant increase,

Fig. 11. Variation in 20 V gate-bias SiC nMOS (a) TLP curves, (b)  $I_D$ – $V_G$  curves, and (c) drain leakage current after TLP stresses.

which indicates strong carrier injection into the gate oxide. On the other hand, since the breakdown voltage (i.e., 10.5 V) and  $V_h$  [i.e., 8 V in Fig. 9(a)] of the Si nMOS are much lower than the SiC nMOS, the drain-gate leakage current shows little change after avalanche breakdown. Therefore, little latent damage was observed in the Si nMOS. Moreover, besides the lower breakdown voltage and  $V_h$ , the Si nMOS has LDD implant regions, which may also reduce the carrier injection [18].

### C. Repetitive TLP Stresses on Gate-Bias SiC nMOS

Fig. 11 shows the variation in the TLP  $I$ – $V$  curves,  $I_D$ – $V_G$ , and leakage current of SiC nMOS with 20 V  $V_G$  after repetitive TLP stresses. The TLP  $I$ – $V$  curves and  $V_{th}$  of the device show little change after 1000 cycles of stresses. The leakage current shifts less than 60%. TCAD simulations were carried out by Sentaurus. Fig. 12 shows transient ESD simulation results of the electric potential distribution in the SiC nMOS with 0 and 20 V  $V_G$ . The simulated  $V_D$  was 65 V. As shown in the figures, the electric potential in the channel region is  $\sim$ 10–20 V. Therefore,  $V_G$  decreases the drain–gate voltage drop and electric field in the gate oxide. This leads to less carrier injection.

Fig. 12. Simulated electric potential distribution of  $1\ \mu\text{m}$   $L$  SiC nMOS with (a) 0 V  $V_G$  and (b) 20 V  $V_G$ .

Fig. 13. Variation in SiC ggNMOS (a) VF-TLP curves, (b)  $I_D$ – $V_G$  curves, and (c) drain leakage current after VF-TLP stresses with 0 V  $V_G$ .

### D. Repetitive VF-TLP Stresses on SiC ggNMOS

The variation of the SiC ggNMOS after VF-TLP stresses is shown in Fig. 13. The results are similar to the gate-ground SiC nMOS after TLP stresses. The  $V_{th}$  of the nMOS increases from 39 to 43 V after ten-cycle stresses and is recovered to 39.1 V by the annealing process. The shifts of the  $V_{th}$  and  $I_{Lk}$  are mainly caused by the generation of the trapped charges

Fig. 14. Gate oxide breakdown voltage versus gate oxide thickness.

in the oxide traps and interface traps during the avalanche operation. The  $V_{th}$  decreases from 2.4 to 2 V after ten-cycle stresses and shows a slight decrease with the stressing cycles. The degradation was also recovered by annealing. Since the pulselwidth of the VF-TLP is shorter than that of the TLP, fewer carriers were injected into the gate oxide region. As a result, it shows less degradation of  $I_{lk}$  (i.e., from 100% to 300%) compared to the TLP measurements.

## V. DISCUSSION

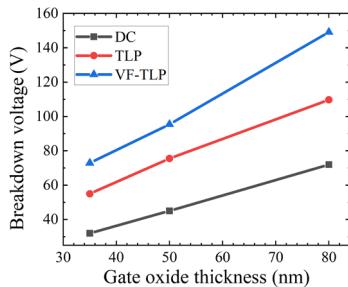

### A. Gate Oxide Breakdown

The gate dielectric breakdown voltage of nMOS devices is critical as it defines the up boundary of the SOA and ESD design window. Fig. 14 shows the gate breakdown voltage versus the gate oxide thickness of SiC nMOS devices. The results are average values extracted from three samples. The gate breakdown voltages under dc, 100 ns TLP and 10 ns VF-TLP conditions are  $\sim 0.9$ ,  $\sim 1.48$ , and  $\sim 1.95$  V/nm, respectively. It should be noted that the gate breakdown voltage under 100 ns TLP conditions of conventional Si-based nMOS devices is  $\sim 2.1$  V/nm [12], [33], [34], which is 1.4 times of SiC nMOS. With the scale-down of SiC CMOS processes, the gate oxide reliability issues of thin-oxide SiC CMOS devices are expected to be more challenging than Si counterparts unless the quality of the gate oxide can be improved in the future.

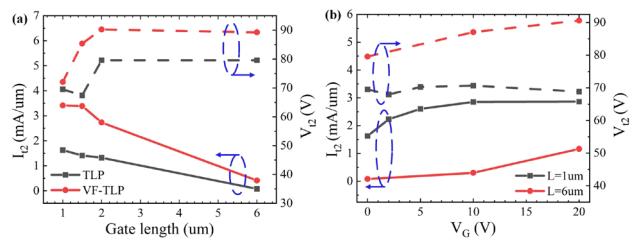

### B. Failure Current and Voltage

SOA of nMOS under ESD conditions is strongly related to  $I_{t2}$  and  $V_{t2}$  since the performance of the ESD protection devices is determined by the nMOS devices under protection. Fig. 15(a) shows the SiC nMOS  $I_{t2}$  per  $\mu\text{m}$  and  $V_{t2}$  versus  $L$  under TLP and VF-TLP stresses. These values can be utilized to design the output nMOS width for the robustness of ESD protection. Moreover, the  $I_{t2}$  of SiC nMOS is much lower than that of silicide-block nMOS based on Si (i.e.,  $I_{t2} > 5$  mA/ $\mu\text{m}$ ) [27]. Therefore, it is worth studying the SOA of silicide-block nMOS devices on SiC in future work. On the other hand, the  $V_{t2}$  of SiC nMOS is much higher than Si nMOS. This may make the effective ESD protection of the SiC nMOS easier compared to Si as the requirement of the ESD protection devices is [27]

$$V_{tmax\_ESD} > V_{t2} + R_s I_{t2} \quad (3)$$

where  $V_{tmax\_ESD}$  is the greater trigger voltage and failure voltage of the ESD protection device,  $R_s$  is the series resistor,

Fig. 15. SiC nMOS  $I_{t2}$  and  $V_{t2}$  versus (a)  $L$  and (b)  $V_G$  under TLP and VF-TLP stresses.

and  $I_{t2}$  and  $V_{t2}$  are the failure current and voltage of the device under protection (i.e., the SiC nMOS in this case).

Fig. 15(b) shows the SiC nMOS  $I_{t2}$  per  $\mu\text{m}$  and  $V_{t2}$  versus  $V_G$  under TLP stresses. For nMOS with 1  $\mu\text{m}$   $L$ ,  $I_{t2}$  increases from 1.6 to 2.9 mA/ $\mu\text{m}$  with  $V_G$  increasing from 0 to 10 V while  $V_{t2}$  shows little change. This indicates that SiC nMOS with gate coupling circuitry may be an option for the ESD protection of output nMOS devices in the future.

## VI. CONCLUSION

The electrical SOA under ESD conditions of 4H-SiC low-voltage nMOS has been investigated. SiC nMOS device gate oxide breakdown voltages, failure current with parasitic n-p-n, and latent damage have been characterized by TLP and VF-TLP systems. TLP and VF-TLP waveforms at the oxide breakdown points are also presented and discussed.

In addition, the ESD capability of SiC nMOS devices with parasitic n-p-n BJTs has also been characterized by TLP and VF-TLP. The nMOS devices did not show snapback behaviors due to the low current gain of the parasitic n-p-n. The long-channel nMOS (i.e.,  $L > 2 \mu\text{m}$ ) showed early failure under both TLP and VF-TLP measurements. It has been demonstrated that the failure threshold of long-channel SiC nMOS devices is determined by the gate oxide breakdown since they do not show snapback behaviors. SEM and TCAD simulations were also utilized to illustrate this phenomenon.

At last, the ESD-induced latent damage on the SiC nMOS has been studied. Degradation was observed on SiC ggNMOS under repetitive TLP and VF-TLP stresses. This is because hot carriers were injected into the gate oxide during the avalanche operation, which generated trapped charges and affected the threshold voltage and leakage current. The latent damage was recovered by 200 °C anneal as trapped charges were reemitted in high-temperature conditions. Meanwhile, SiC nMOS devices with 20 V  $V_G$  showed little degradation under repetitive TLP stresses.

In general, a few ESD-related performances of SiC low-voltage nMOS devices may need attention, such as the nonsnapback behaviors, the failure threshold, and the latent damages, since they are different from the conventional Si-based nMOS.

## REFERENCES

- [1] N. Kaminski, "State of the art and the future of wide band-gap devices," in *Proc. 13th Eur. Conf. Power Electron. Appl.*, 2009, pp. 1–9.

- [2] S. Roy et al., "Silicon carbide bipolar analog circuits for extreme temperature signal conditioning," *IEEE Trans. Electron Devices*, vol. 66, no. 9, pp. 3764–3770, Sep. 2019, doi: 10.1109/TED.2019.2928484.

- [3] H. Elahipanah, S. Kargarrazi, A. Salemi, M. Östling, and C.-M. Zetterling, "500°C high current 4H-SiC lateral BJTs for high-temperature integrated circuits," *IEEE Electron Device Lett.*, vol. 38, no. 10, pp. 1429–1432, Oct. 2017, doi: [10.1109/LED.2017.2737558](https://doi.org/10.1109/LED.2017.2737558).

- [4] P. G. Neudeck, G. M. Beheim, and C. S. Salupo, "600°C logic gates using silicon carbide JFETs," in *Proc. Government Microcircuit Appl. Conf.*, 2000, pp. 421–424.

- [5] N. Kuhns et al., "Complex high-temperature CMOS silicon carbide digital circuit designs," *IEEE Trans. Device Mater. Rel.*, vol. 16, no. 2, pp. 105–111, Jun. 2016, doi: [10.1109/TDMR.2016.2530664](https://doi.org/10.1109/TDMR.2016.2530664).

- [6] L. Di Benedetto, G. D. Licciardo, and A. Rubino, "Experimental results on lateral 4H-SiC UV photodiodes," in *Proc. 7th IEEE Int. Workshop Adv. Sensors Interfaces (IWASI)*, Jun. 2017, pp. 252–254, doi: [10.1109/IWASI2017.7974264](https://doi.org/10.1109/IWASI2017.7974264).

- [7] P. Lai et al., "Area-efficient silicon carbide SCR device for on-chip ESD protection," *IEEE Trans. Electron Devices*, vol. 69, no. 6, pp. 3022–3028, Jun. 2022, doi: [10.1109/TED.2022.3166471](https://doi.org/10.1109/TED.2022.3166471).

- [8] K.-I. Do, B.-S. Lee, and Y.-S. Koo, "Study on 4H-SiC GGNMOS based ESD protection circuit with low trigger voltage using gate-body floating technique for 70-V applications," *IEEE Electron Device Lett.*, vol. 40, no. 2, pp. 283–286, Feb. 2019, doi: [10.1109/LED.2018.2885846](https://doi.org/10.1109/LED.2018.2885846).

- [9] K.-I. Do, B. Lee, S. G. Kim, and Y.-S. Koo, "Design of 4H-SiC-based silicon-controlled rectifier with high holding voltage using segment topology for high-voltage ESD protection," *IEEE Electron Device Lett.*, vol. 41, no. 11, pp. 1669–1672, Nov. 2020, doi: [10.1109/LED.2020.3022888](https://doi.org/10.1109/LED.2020.3022888).

- [10] K.-I. Do, J.-I. Won, and Y.-S. Koo, "A 4H-SiC MOSFET-based ESD protection with improved snapback characteristics for high-voltage applications," *IEEE Trans. Power Electron.*, vol. 36, no. 5, pp. 4921–4926, May 2021, doi: [10.1109/TPEL.2020.3032917](https://doi.org/10.1109/TPEL.2020.3032917).

- [11] K.-I. Do, S.-H. Jin, B.-S. Lee, and Y.-S. Koo, "4H-SiC-based ESD protection design with optimization of segmented LIGBT for high-voltage applications," *IEEE J. Electron Devices Soc.*, vol. 9, pp. 1017–1023, 2021, doi: [10.1109/JEDS.2021.3121212](https://doi.org/10.1109/JEDS.2021.3121212).

- [12] B. E. Weir, C.-C. Leung, P. J. Silverman, and M. A. Alam, "Gate dielectric breakdown in the time-scale of ESD events," *Microelectron. Rel.*, vol. 45, nos. 3–4, pp. 427–436, Mar. 2005, doi: [10.1016/j.microrel.2004.12.004](https://doi.org/10.1016/j.microrel.2004.12.004).

- [13] S. Malobabic, D. F. Ellis, J. A. Salcedo, Y. Zhou, J. -J. Hajjar, and J. J. Liou, "Gate oxide evaluation under very fast transmission line pulse (VFTLP) CDM-type stress," in *Proc. 7th Int. Caribbean Conf. Devices, Circuits Syst.*, Cancun, Mexico, 2008, pp. 1–8, doi: [10.1109/ICCDCS.2008.4542669](https://doi.org/10.1109/ICCDCS.2008.4542669).

- [14] J. Wu and E. Rosenbaum, "Gate oxide reliability under ESD-like pulse stress," *IEEE Trans. Electron Devices*, vol. 51, no. 7, pp. 1192–1196, Jul. 2004, doi: [10.1109/TED.2004.829894](https://doi.org/10.1109/TED.2004.829894).

- [15] A. Amerasekera, V. Gupta, K. Vasanth, and S. Ramaswamy, "Analysis of snapback behavior on the ESD capability of sub-0.20  $\mu\text{m}$  NMOS," in *Proc. 37th Annu. IEEE Int. Rel. Phys. Symp.*, San Diego, CA, USA, Mar. 1999, pp. 159–166, doi: [10.1109/RELPHY.1999.761608](https://doi.org/10.1109/RELPHY.1999.761608).

- [16] A. Cester et al., "ESD induced damage on ultra-thin gate oxide MOSFETs and its impact on device reliability," in *Proc. 43rd Annual IEEE Int. Rel. Phys. Symp.*, Apr. 2005, pp. 84–90, doi: [10.1109/RELPHY.2005.1493068](https://doi.org/10.1109/RELPHY.2005.1493068).

- [17] Y. Huh et al., "A study of ESD-induced latent damage in CMOS integrated circuits," in *Proc. 36th Annu. IEEE Int. Rel. Phys. Symp.*, Mar. 1998, pp. 279–283, doi: [10.1109/relphy.1998.670562](https://doi.org/10.1109/relphy.1998.670562).

- [18] G. V. Groeseneken, "Hot carrier degradation and ESD in submicrometer CMOS technologies: How do they interact?" *IEEE Trans. Device Mater. Rel.*, vol. 1, no. 1, pp. 23–32, Mar. 2001, doi: [10.1109/7298.946457](https://doi.org/10.1109/7298.946457).

- [19] T. Phulpin et al., "Contribution to silicon-carbide-MESFET ESD robustness analysis," *IEEE Trans. Device Mater. Rel.*, vol. 18, no. 2, pp. 214–223, Jun. 2018, doi: [10.1109/TDMR.2018.2817255](https://doi.org/10.1109/TDMR.2018.2817255).

- [20] D. T. Jarard, S. Ahmed, T. Vrotsos, and Z. Chen, "Electrical safe operating area of low-voltage silicon carbide NMOS transistors," in *Proc. IEEE 4th Workshop Wide Bandgap Power Devices Appl. (WiPDA)*, Nov. 2016, pp. 236–241, doi: [10.1109/WiPDA.2016.779945](https://doi.org/10.1109/WiPDA.2016.779945).

- [21] R. Singh and A. R. Hefner, "Reliability of SiC MOS devices," *Solid-State Electron.*, vol. 48, nos. 10–11, pp. 1717–1720, Oct. 2004.

- [22] A. K. Agarwal, S. Seshadri, and L. B. Rowland, "Temperature dependence of fowler-nordheim current in 6H- and 4H-SiC MOS capacitors," *IEEE Electron Device Lett.*, vol. 18, no. 12, pp. 592–594, Dec. 1997, doi: [10.1109/55.644081](https://doi.org/10.1109/55.644081).

- [23] L. C. Yu, G. T. Dunne, K. S. Matocha, K. P. Cheung, J. S. Suehle, and K. Sheng, "Reliability issues of SiC MOSFETs: A technology for high-temperature environments," *IEEE Trans. Device Mater. Rel.*, vol. 10, no. 4, pp. 418–426, Dec. 2010, doi: [10.1109/TDMR.2010.2077295](https://doi.org/10.1109/TDMR.2010.2077295).

- [24] D. T. Clark et al., "High temperature silicon carbide CMOS integrated circuits," *Mater. Sci. Forum*, vols. 679–680, pp. 726–729, Mar. 2011, doi: [10.4028/www.scientific.net/msf.679-680.726](https://doi.org/10.4028/www.scientific.net/msf.679-680.726).

- [25] J. Weisse, H. Mitlehner, L. Frey, and T. Erlbacher, "Design of a 4H-SiC RESURF n-LDMOS transistor for high voltage integrated circuits," *Mater. Sci. Forum*, vol. 963, pp. 629–632, Jul. 2019, doi: [10.4028/www.scientific.net/msf.963.629](https://doi.org/10.4028/www.scientific.net/msf.963.629).

- [26] M. Alam, B. Weir, J. Bude, P. Silverman, and A. Ghetti, "A computational model for oxide breakdown: Theory and experiments," *Microelectronic Eng.*, vol. 59, nos. 1–4, pp. 137–147, Nov. 2001, doi: [10.1016/s0167-9317\(01\)00657-8](https://doi.org/10.1016/s0167-9317(01)00657-8).

- [27] A. Amerasekera and C. Duvvury, *ESD in Silicon Integrated Circuits*. New York, NY, USA: Wiley, 1995, doi: [10.1016/s0026-2714\(96\)90047-5](https://doi.org/10.1016/s0026-2714(96)90047-5).

- [28] Y. Taur and T. H. Ning, *Fundamentals of Modern VLSI Devices*. Cambridge, U.K.: Cambridge Univ. Press, 2013.

- [29] U. Lindefelt, "Doping-induced band edge displacements and band gap narrowing in 3C-, 4H-, 6H-SiC, and Si," *J. Appl. Phys.*, vol. 84, no. 5, pp. 2628–2637, Sep. 1998, doi: [10.1063/1.368374](https://doi.org/10.1063/1.368374).

- [30] F. Zhao, I. Perez, C.-F. Huang, J. Torvik, and B. VanZeghbroeck, "Analysis of transit times and minority carrier mobility in n-p-n 4H-SiC bipolar junction transistors," *IEEE Trans. Electron Devices*, vol. 52, no. 12, pp. 2541–2545, Dec. 2005, doi: [10.1109/TED.2005.859669](https://doi.org/10.1109/TED.2005.859669).

- [31] D. C. Wunsch and R. R. Bell, "Determination of threshold failure levels of semiconductor diodes and transistors due to pulse voltages," *IEEE Trans. Nucl. Sci.*, vol. NS-15, no. 6, pp. 244–259, Dec. 1968, doi: [10.1109/TNS.1968.4325054](https://doi.org/10.1109/TNS.1968.4325054).

- [32] O. Semenov, H. Sarbishae, and M. Sachdev, *ESD Protection Device and Circuit Design for Advanced CMOS Technologies*. Dordrecht, The Netherlands: Springer, 2008, pp. 13–14.

- [33] A. Ille et al., "Ultra-thin gate oxide reliability in the ESD time domain," in *Proc. Electr. Overstress/Electrostatic Discharge Symp.*, Tucson, AZ, USA, 2006, pp. 285–294.

- [34] M. Mergens et al., "Active-source-pump (ASP) technique for ESD design window expansion and ultra-thin gate oxide protection in sub-90 nm technologies," in *Proc. IEEE Custom Integr. Circuits Conf.*, Orlando, FL, USA, Oct. 2004, pp. 251–254, doi: [10.1109/CICC.2004.1358790](https://doi.org/10.1109/CICC.2004.1358790).