Compute-in-memory Circuits and Architectures for Efficient Acceleration of AI and

Data Centric Workloads

by

Amitesh Sridharan

A Dissertation Presented in Partial Fulfillment

of the Requirements for the Degree

Doctor of Philosophy

Approved June 2025 by the

Graduate Supervisory Committee:

Deliang Fan, Chair

Jae-sun Seo

Yu Cao

Jeff Zhang

ARIZONA STATE UNIVERSITY

August 2025

## ABSTRACT

Modern computing is increasingly driven by the explosive growth of data from applications such as Artificial Intelligence (AI), Machine Learning (ML), and Genomics. These workloads are inherently data-intensive, requiring fast and efficient processing of large datasets. Although scaling input data in AI applications continues to boost performance, traditional computing architectures have struggled to keep pace, creating a widening gap between data generation and processing capabilities.

This disparity stresses the three fundamental pillars of computing—storage, communication, and computation—impacting performance, energy efficiency, and cost. Conventional Von Neumann architectures, designed to maximize computational throughput, now face the “memory and power wall,” where compute units cannot fetch or process data fast enough to meet demand. As data movement becomes the dominant bottleneck, there is a clear need to pivot from compute-centric to memory-centric design approaches.

In-Memory Computing (IMC), or Compute-in-Memory (CIM), addresses these challenges by performing computation directly within memory, minimizing data movement and mitigating the memory wall.

This dissertation introduces a series of digital CIM circuits and architectures that significantly improve power, performance, and area (PPA) metrics for data-intensive workloads. It begins with a programmable CIM design that balances the flexibility of Central-Processing-Units(CPUs)/Graphics Processing Units(GPUs) with the efficiency of ASICs, enabling a broad class of applications. A prototype 28nm CMOS chip is then presented to accelerate general matrix-matrix multiplications (GEMMs) across various fixed-point precisions.

The focus then shifts to sparse GEMM acceleration. The first design demon-

strates how CIM tailored for channel decoders leverages both fixed and unstructured sparsity to outperform conventional designs. The second design, fabricated in 28nm CMOS, supports diverse unstructured sparse formats and integer precisions, efficiently targeting highly sparse deep neural networks (DNNs). The final design achieves state-of-the-art efficiency in compressed sparse GEMMs, supporting both integer and floating-point data types using shared hardware. It also integrates a RISC-V CPU to manage computation across diverse matrix sizes and model types.

Together, these contributions advance CIM as a scalable and efficient platform for future AI and data-centric systems.

## ACKNOWLEDGMENTS

I owe my deepest gratitude to my wife, Vaishali Sridhar, my parents, Meera Natarajan and Sridharan Kanakarajan, and my brother, Visvesh Sridharan, for their unwavering love, encouragement, and support throughout every stage of my Ph.D. journey. This dissertation is dedicated to them.

I am profoundly grateful to my advisor and committee chair, Dr. Deliang Fan, for his exceptional mentorship, insightful guidance, and constant encouragement during my doctoral studies. His support has been instrumental in shaping my research direction, refining my writing, and developing essential skills in time management and critical thinking. I am especially thankful for his patience, his belief in my potential, and his dedication to guiding me through each phase of my Ph.D. It has truly been an honor and privilege to be his student.

I would also like to express my heartfelt appreciation to Dr. Jae-sun Seo, a member of my Ph.D. advisory committee, for his outstanding mentorship and continued support. From the very beginning of my Ph.D., he has been a constant source of inspiration. I am sincerely grateful for the opportunities he provided, his thoughtful feedback, and, most importantly, for treating me as one of his own students. His influence has had a lasting impact on both my academic and personal growth, and I deeply aspire to follow the example he sets.

My sincere thanks go to Dr. Yu (Kevin) Cao and Dr. Jeff Zhang for their invaluable guidance throughout my research projects and for their generous service as members of my Ph.D. committee. I am also thankful to Dr. Bo Yuan, Dr. Shan X. Wang, Dr. Wilman Tsai, and Dr. Yiran Chen for their collaboration and insightful contributions, which have greatly enriched the scope and impact of my work. Additionally, I would like to thank Dr. Harsono Simka and Dr. Ming He from Samsung Semiconductor Inc.,

and Dr. Kerem Akarvardar and Dr. Xiaoyu Sun from TSMC Corporate Research, for their valuable feedback and technical mentorship during my summer internships. Their guidance has significantly shaped my research direction and professional development.

I am deeply indebted to my colleagues and collaborators Dr. Shaahin Angizi, Dr. Fan Zhang, Asmer Hamid Ali, Dr. Sai Kiran Cherupally, Dr. Jyotishman Saikia, Anupreetham, Md. Habibur Rahman, Dr. Adnan Siraj Rakin, Dr. Li Yang, Yongjae Lee, Yuan Liao, Dr. Shreyas Venkataramanaiah, Jingxing Li, Jingkai Guo, Yaotian Liu, Dr. Injune Yeo, Haotian Su, Boyang Cheng, Yucheng Wang, and Jiawei Hu—for their collaborative spirit, insightful discussions, and steadfast support throughout my Ph.D. Their friendship and contributions have been instrumental to both the progress and enjoyment of my graduate experience.

I also wish to thank my graduate advisors, Lynn Pratt and Ian James, for their continuous support with administrative matters and logistics. Their guidance ensured a smooth and productive academic journey.

Finally, I would like to thank my friend Magesh Sridhar for his encouragement and support. His positivity and friendship have meant a great deal to me and have played an important role in the successful completion of this dissertation.

This work is supported in part by the National Science Foundation under Grant No.2314591, No.2505326, No.2528723, No.2528767, and ASU.

## TABLE OF CONTENTS

|                                                                                                           | Page |

|-----------------------------------------------------------------------------------------------------------|------|

| LIST OF TABLES .....                                                                                      | ix   |

| LIST OF FIGURES .....                                                                                     | x    |

| CHAPTER                                                                                                   |      |

| 1 INTRODUCTION .....                                                                                      | 1    |

| 1.1 Today's Computing Limitations .....                                                                   | 1    |

| 1.2 Memory Centric Compute Paradigm .....                                                                 | 2    |

| 1.3 Thesis Organization .....                                                                             | 6    |

| 2 PROGRAMMABLE AND GENERIC PROCESSING-IN-SRAM AC-<br>CELERATOR .....                                      | 8    |

| 2.1 Introduction .....                                                                                    | 8    |

| 2.2 PSRAM Chip Circuit and Architecture .....                                                             | 11   |

| 2.3 Chip Measurement Results .....                                                                        | 15   |

| 2.3.1 Performance Measurements .....                                                                      | 15   |

| 2.3.2 Variability Analysis .....                                                                          | 16   |

| 2.4 Application Evaluation and Comparison .....                                                           | 18   |

| 2.4.1 Case Study 1: Bulk Bitwise Boolean Operations .....                                                 | 18   |

| 2.4.2 Case study 2: Binary Weight Neural Networks .....                                                   | 19   |

| 2.4.3 Case study 3: Data Encryption .....                                                                 | 22   |

| 2.5 Conclusion .....                                                                                      | 23   |

| 3 PRECISION SCALABLE IN-MEMORY COMPUTING MACRO WITH<br>BIT-PARALLEL INPUTS AND DECOMPOSABLE WEIGHTS ..... | 24   |

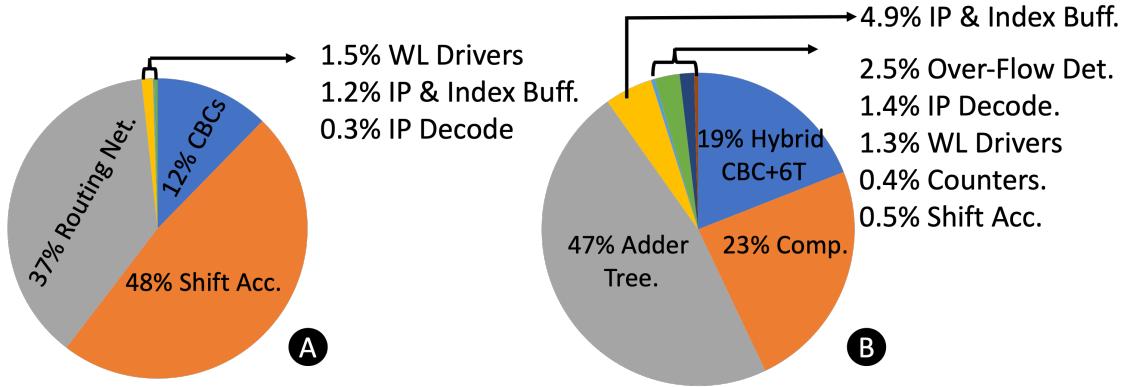

| 3.1 Introduction .....                                                                                    | 25   |

| 3.2 PS-IMC Macro Architecture .....                                                                       | 27   |

| CHAPTER                                                                                          | Page |

|--------------------------------------------------------------------------------------------------|------|

| 3.2.1 Bit-Cell Design .....                                                                      | 27   |

| 3.2.2 Carry Save Adder (CSA) Tree .....                                                          | 29   |

| 3.2.3 Decomposed Weight Precision Data-flow .....                                                | 30   |

| 3.2.4 Variable Shift Accumulator (VSA) for Precision Handling ..                                 | 32   |

| 3.3 Chip Measurement Results .....                                                               | 35   |

| 3.4 Conclusion .....                                                                             | 37   |

| 4 A FULLY DIGITAL SPARSE IN-MEMORY MATRIX VECTOR MULTIPLIER FOR COMMUNICATION APPLICATIONS ..... | 38   |

| 4.1 Introduction .....                                                                           | 39   |

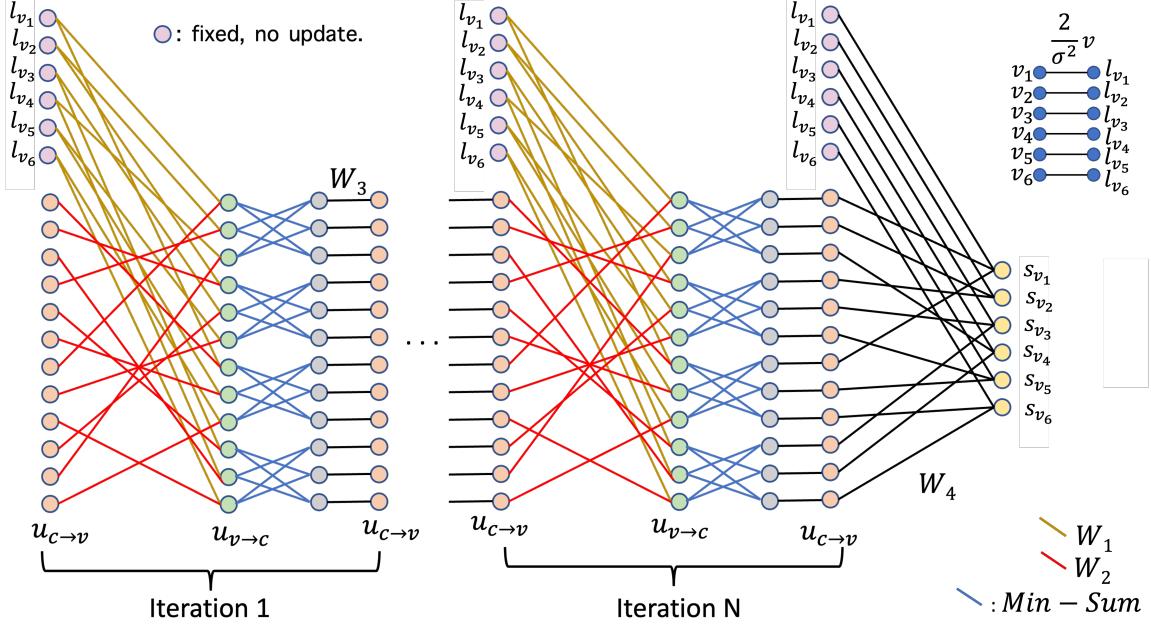

| 4.2 Neural BP Algorithm .....                                                                    | 41   |

| 4.3 Proposed <i>DSPIMM</i> Platform .....                                                        | 45   |

| 4.3.1 Architecture and Data Flow .....                                                           | 45   |

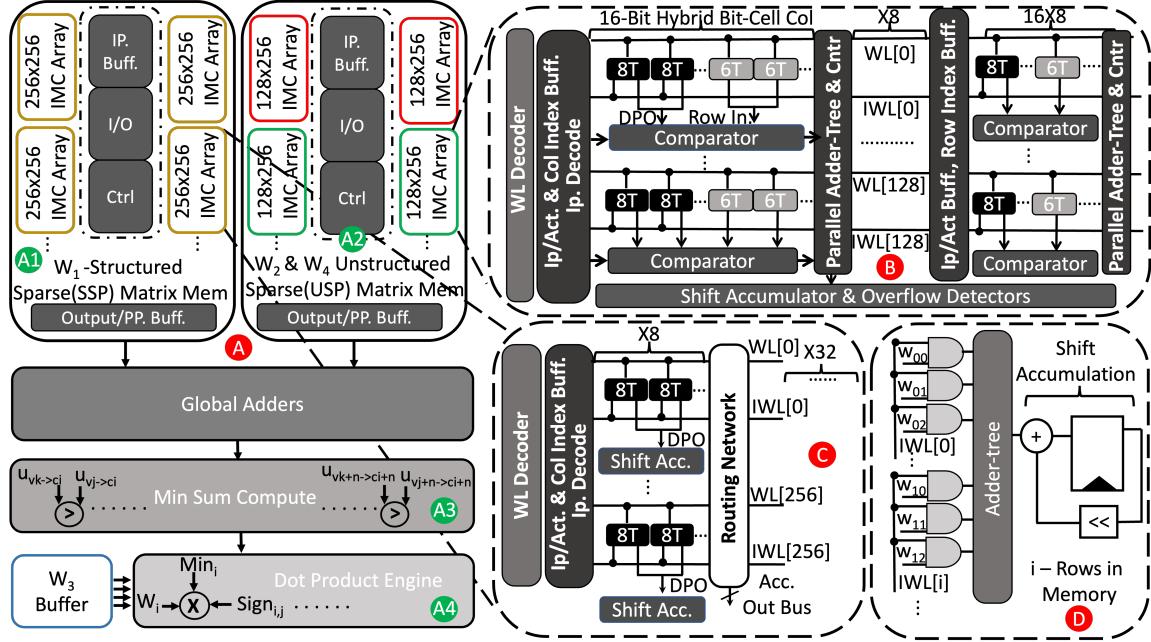

| 4.3.1.1 $W_1$ , Structured Sparse Matrix Memory .....                                            | 46   |

| 4.3.1.2 $W_2$ , Unstructured Sparse (USP) Matrix Memory .....                                    | 46   |

| 4.3.1.3 Global Addition .....                                                                    | 47   |

| 4.3.1.4 MinSum Compute and Dot Products .....                                                    | 47   |

| 4.3.1.5 $S_v$ Calculation .....                                                                  | 47   |

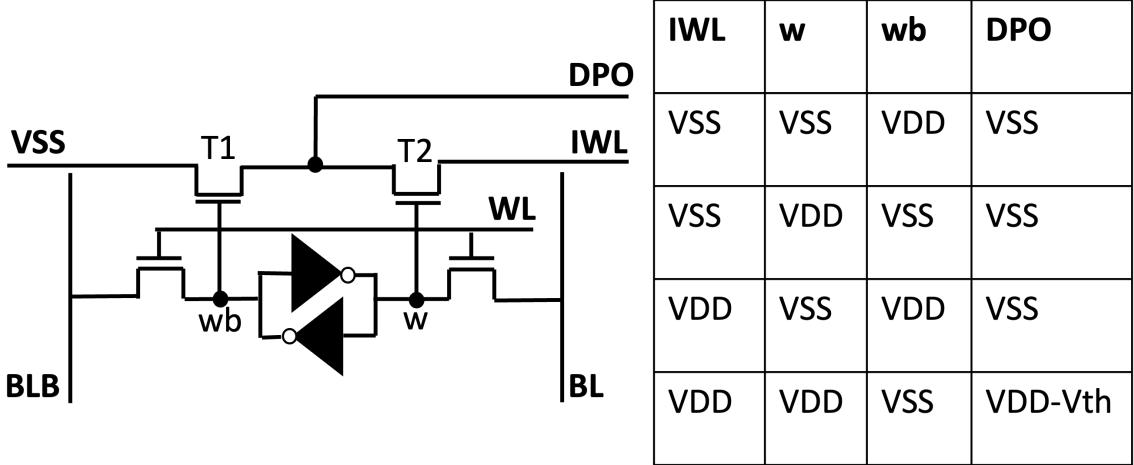

| 4.3.2 6+2T (8T) SRAM Bitcell Design for In-memory-computing                                      | 48   |

| 4.3.3 Bit-Serial Matrix Vector Multiplication (MVM) In-memory .                                  | 49   |

| 4.3.4 Structured Sparse Matrix Vector Multiplication (SSP-MVM)                                   | 50   |

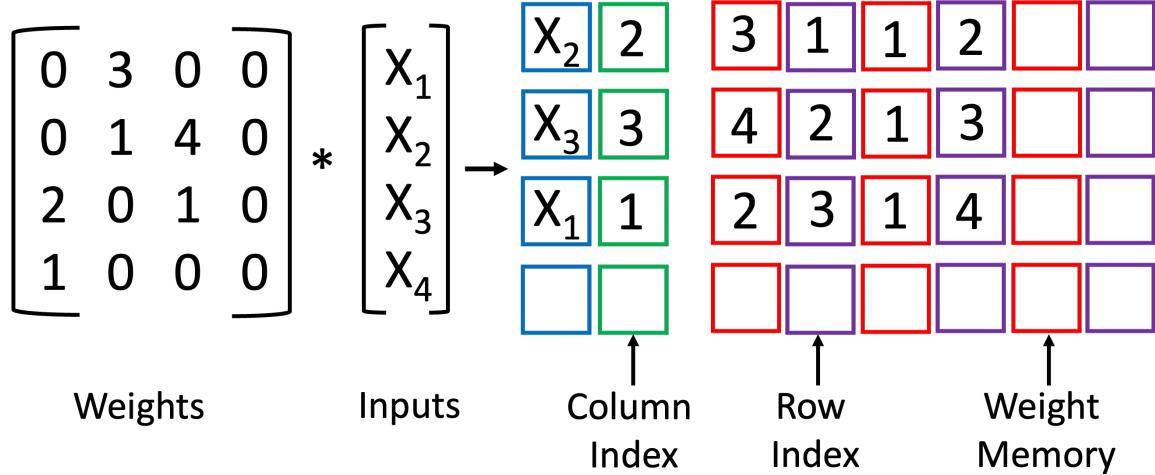

| 4.3.4.1 Greedy Weight Compression and Localization (GWCL) Algorithm for SSP-MVM .....            | 50   |

| 4.3.4.2 SSP-MVM In-Memory Compute Circuit and Architecture .....                                 | 51   |

| CHAPTER                                                                                        | Page |

|------------------------------------------------------------------------------------------------|------|

| 4.3.5 Unstructured Sparse Matrix Vector Mult. (USP-MVM) .....                                  | 52   |

| 4.3.5.1 Enhanced Greedy Algorithm for USP-MVM .....                                            | 52   |

| 4.3.5.2 USP-MVM IMC Circuit and Architecture .....                                             | 53   |

| 4.3.5.3 Overflows .....                                                                        | 54   |

| 4.4 Evaluation and Results .....                                                               | 55   |

| 4.4.1 Experiment Setup .....                                                                   | 55   |

| 4.4.2 Experiment Results .....                                                                 | 56   |

| 4.5 Conclusion .....                                                                           | 57   |

| 5 A SPARSITY AWARE IN-MEMORY-COMPUTING MACRO WITH<br>CONFIGURABLE SPARSE REPRESENTATIONS ..... | 59   |

| 5.1 Introduction .....                                                                         | 60   |

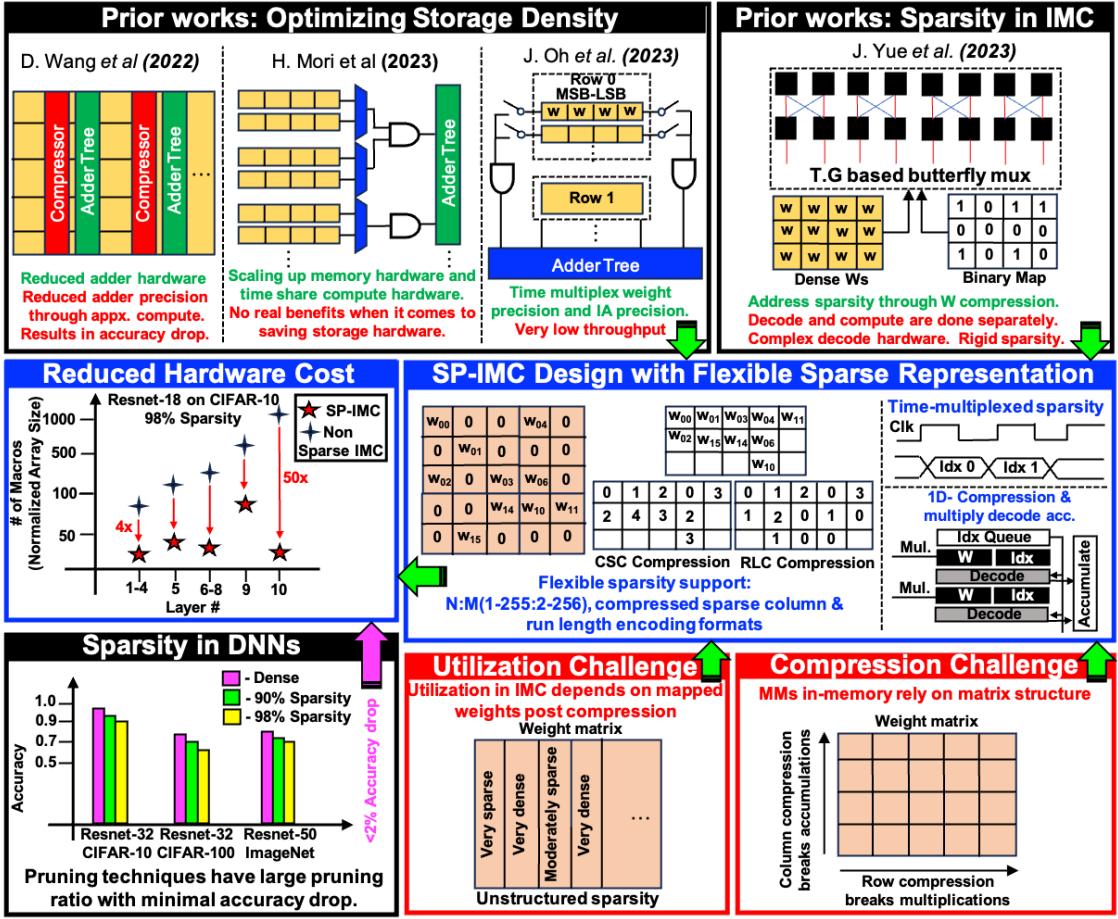

| 5.1.1 Background and Motivation .....                                                          | 60   |

| 5.1.2 Challenges and Benefits of Sparse Compute .....                                          | 61   |

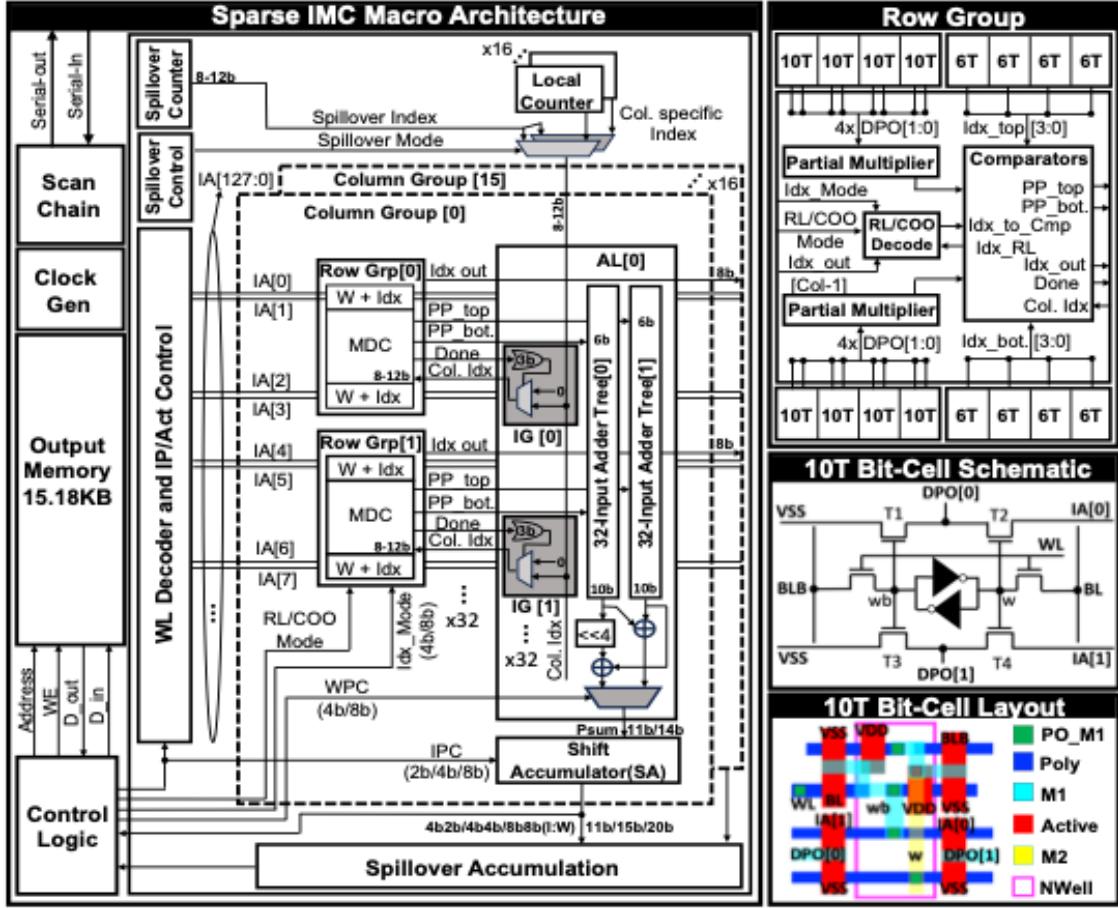

| 5.2 Circuit, Architecture and Operation .....                                                  | 63   |

| 5.2.1 SP-IMC Macro Architecture .....                                                          | 63   |

| 5.2.2 Bitcell Design .....                                                                     | 64   |

| 5.2.3 Sparse Compression Formats and Variable Sparsity Ratio...                                | 65   |

| 5.2.3.1 Compression Direction .....                                                            | 66   |

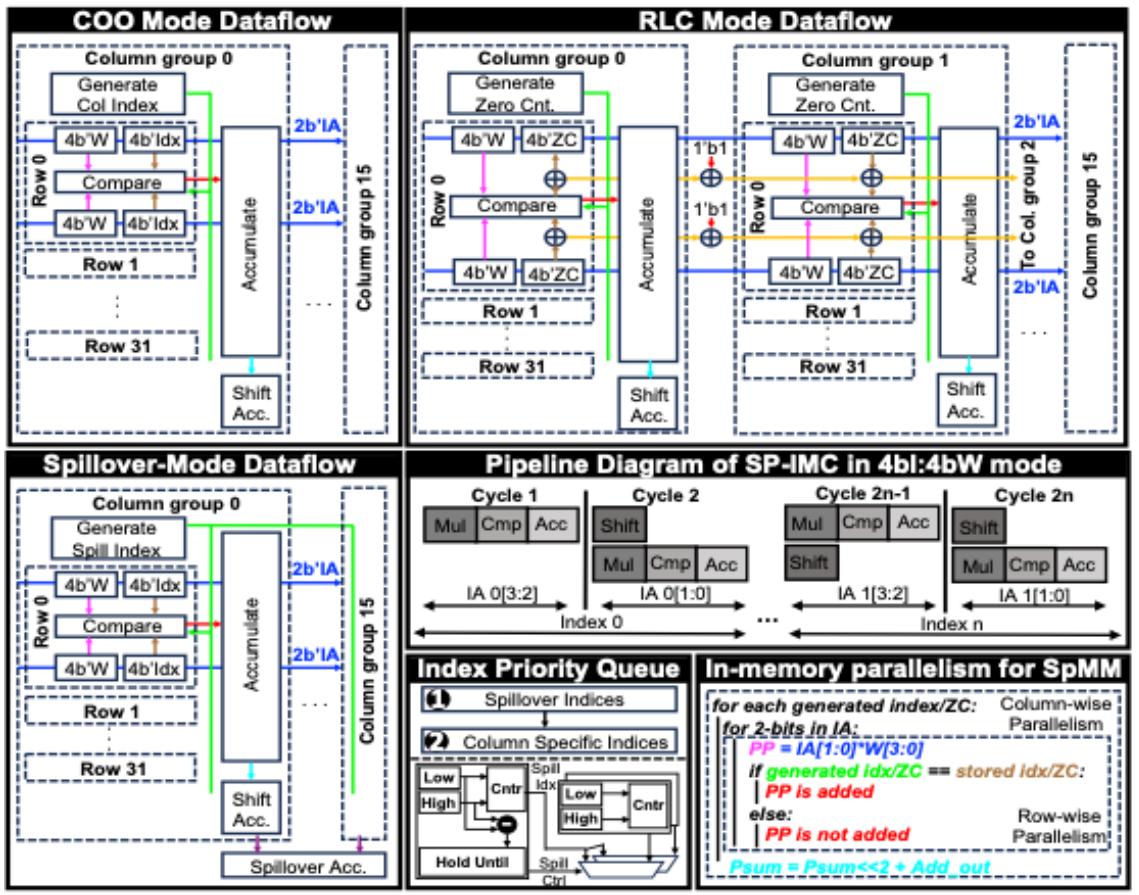

| 5.2.4 Dataflow and Pipeline .....                                                              | 67   |

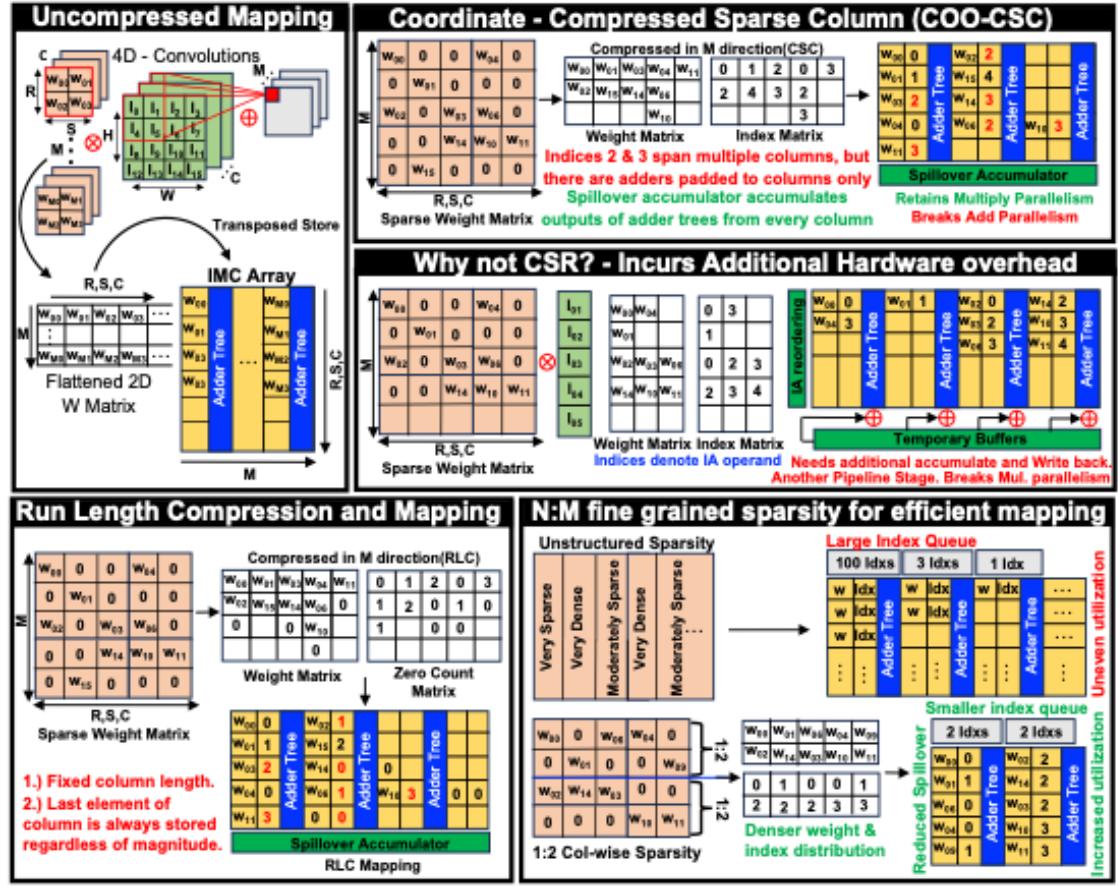

| 5.2.5 Mapping Compressed kernels .....                                                         | 68   |

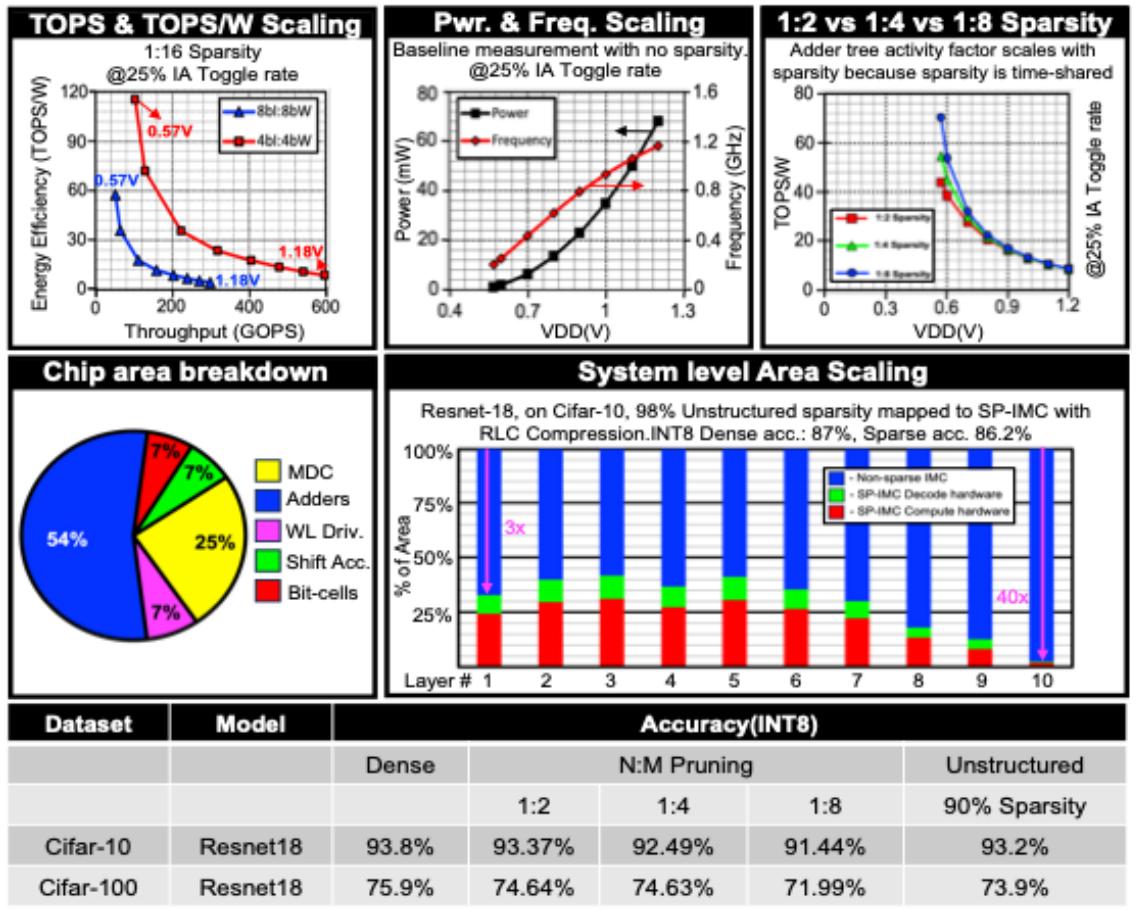

| 5.3 Experiment Results and Analysis .....                                                      | 69   |

| 5.3.1 Chip Measurements .....                                                                  | 69   |

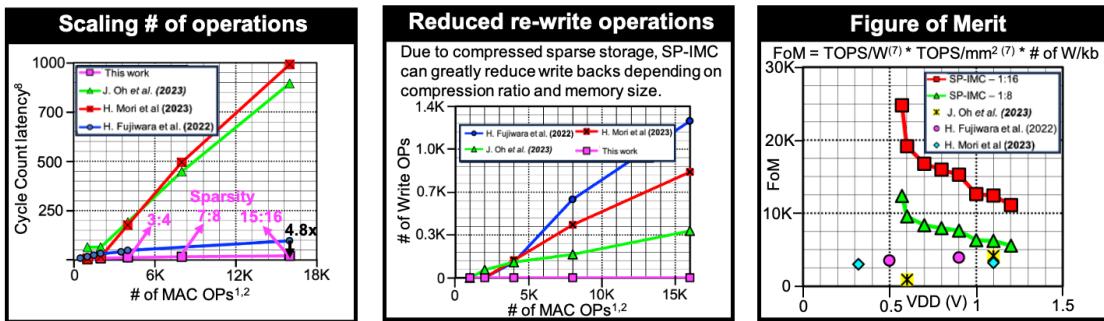

| 5.3.2 Comparison and Evaluation .....                                                          | 72   |

| 5.4 Conclusion .....                                                                           | 73   |

| CHAPTER                                                                                                    | Page |

|------------------------------------------------------------------------------------------------------------|------|

| 6 SPARSITY INTEGRATED COMPUTE-IN-MEMORY ACCELERATOR WITH A FUSED DOT-PRODUCT ENGINE AND A RISC-V CPU ..... | 75   |

| 6.1 Introduction .....                                                                                     | 77   |

| 6.2 Architecture and Operation .....                                                                       | 78   |

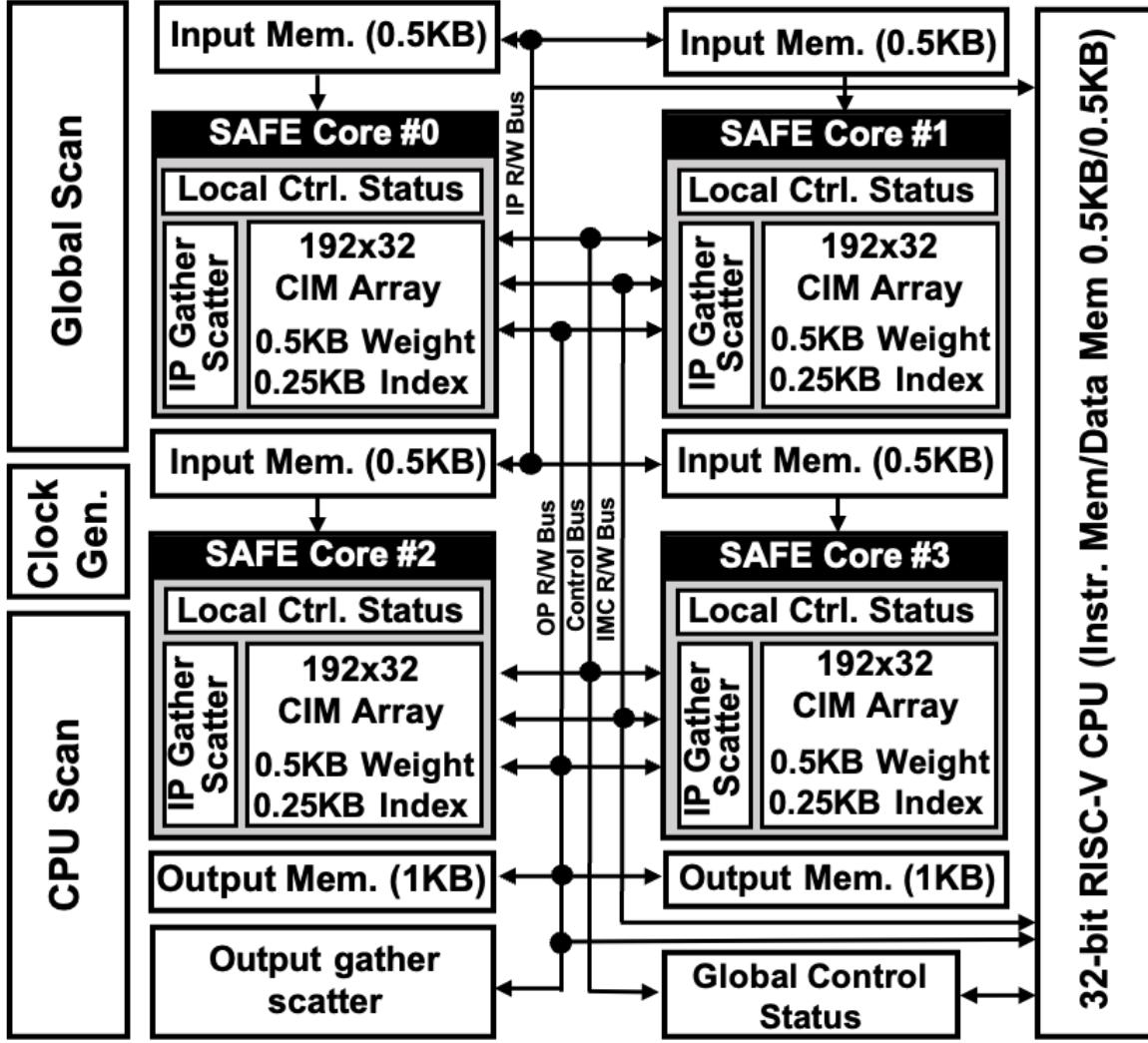

| 6.2.1 SAFER Chip Architecture .....                                                                        | 78   |

| 6.2.2 SAFE Macro Architecture.....                                                                         | 80   |

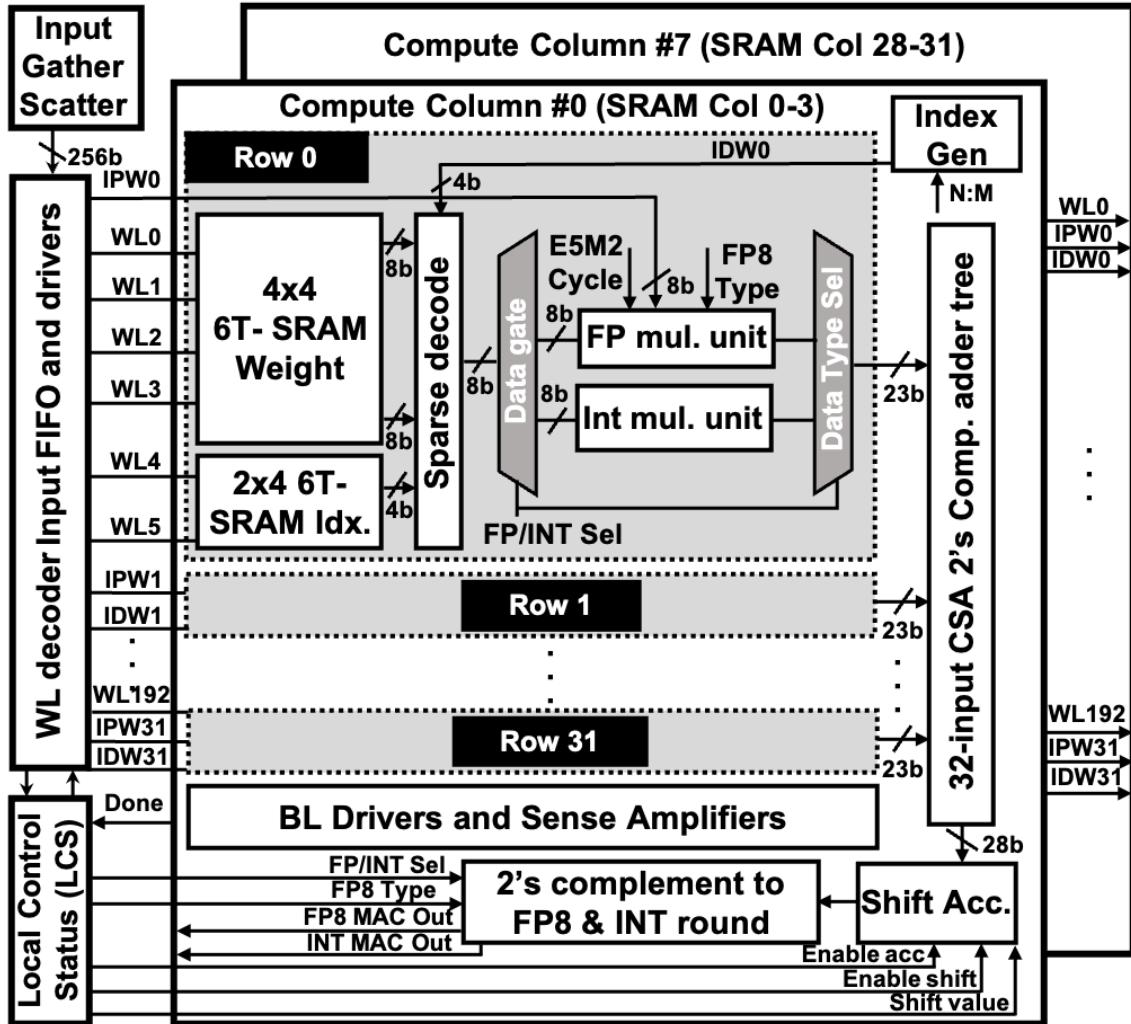

| 6.2.2.1 Compute Column (CC) .....                                                                          | 81   |

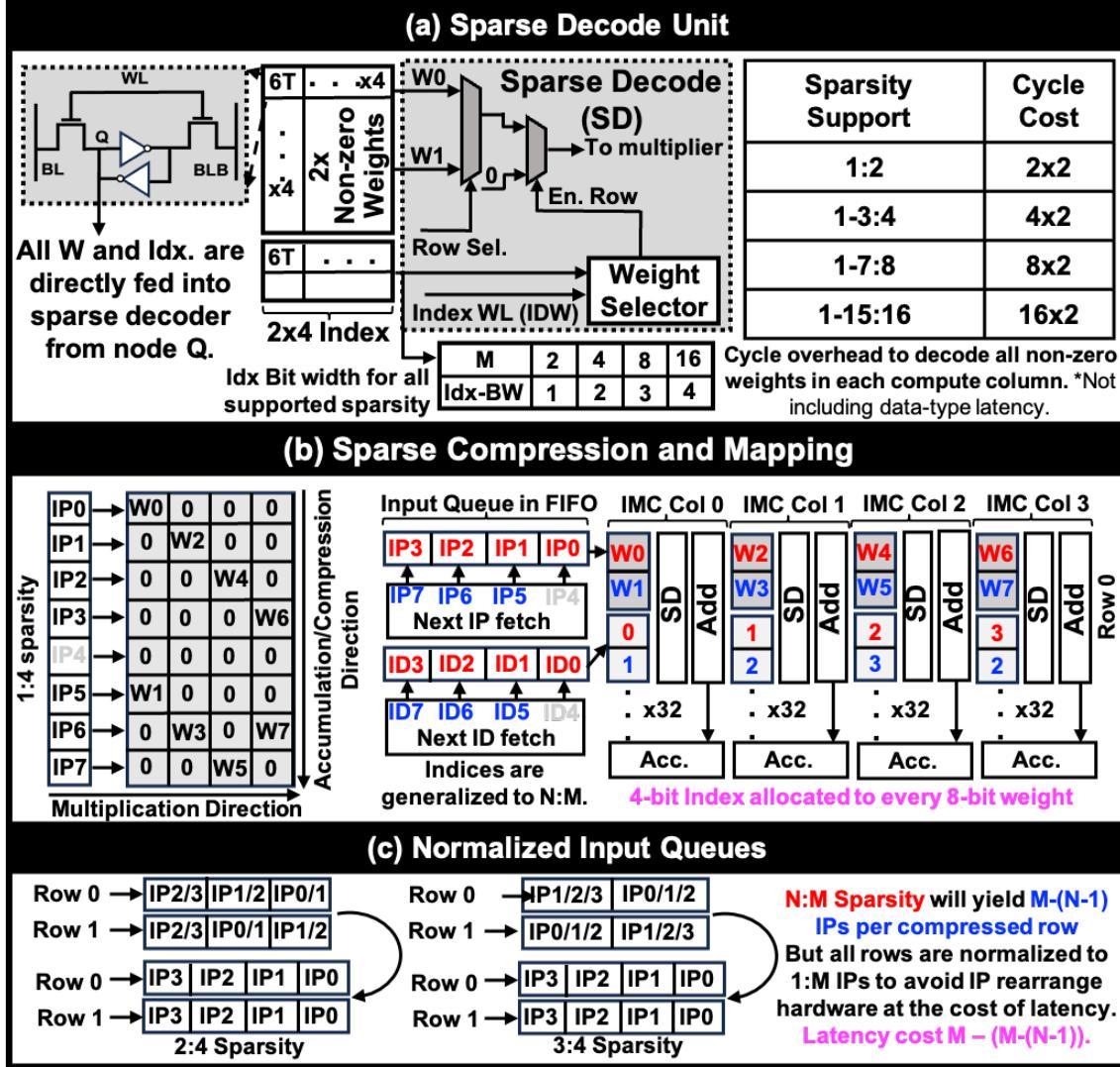

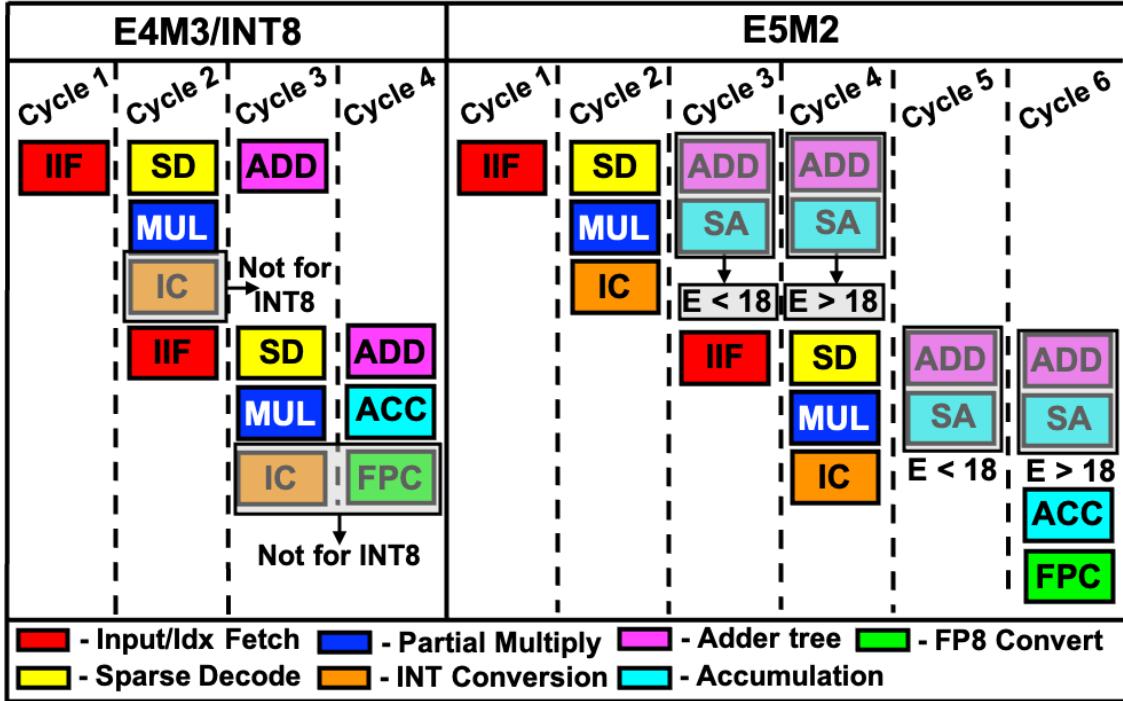

| 6.2.2.2 Sparse Decode Unit (SD).....                                                                       | 81   |

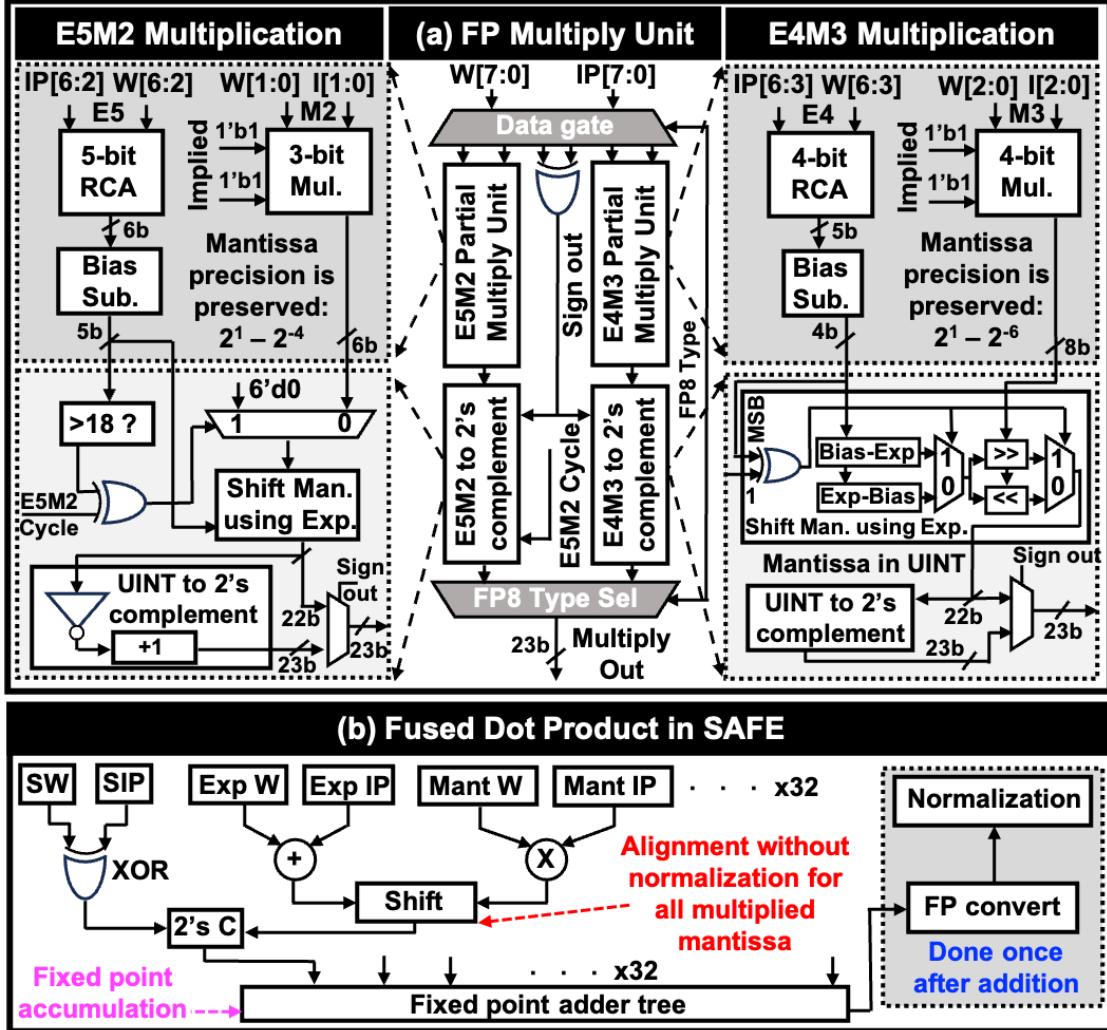

| 6.2.2.3 FP8 fused dot-product (FSD) and INT8 MAC .....                                                     | 83   |

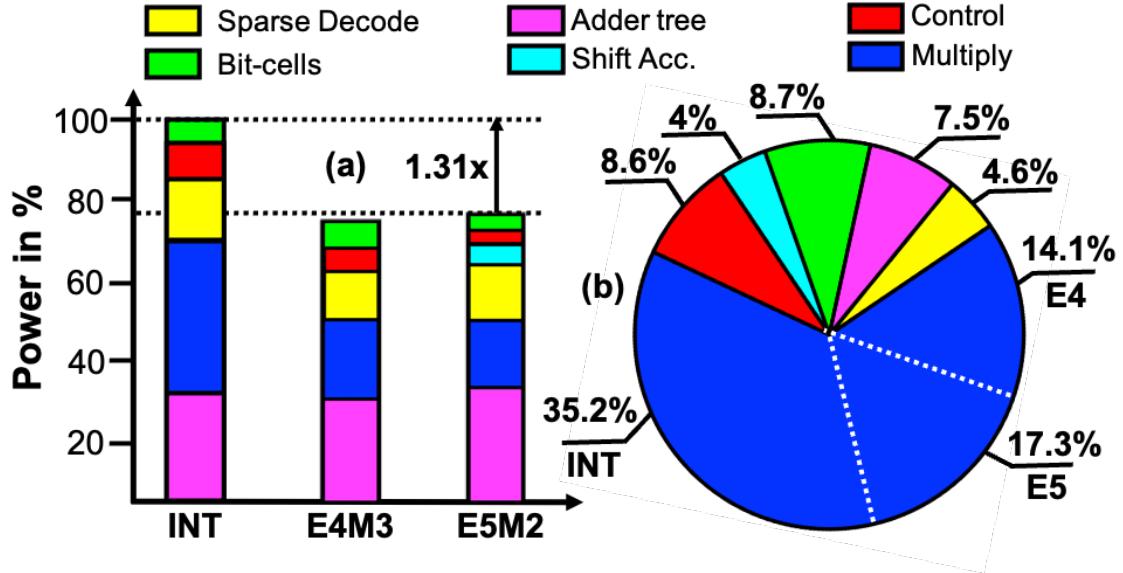

| 6.3 Chip Measurements and Results .....                                                                    | 84   |

| 6.4 Conclusion .....                                                                                       | 88   |

| 7 CONCLUSION .....                                                                                         | 91   |

| REFERENCES .....                                                                                           | 93   |

| APPENDIX                                                                                                   |      |

| A PREVIOUS PUBLISHED WORKS .....                                                                           | 100  |

| B PERMISSION STATEMENT FOR THE PREVIOUS PUBLISHED WORKS .....                                              | 102  |

## LIST OF TABLES

| Table                                                                                                    | Page |

|----------------------------------------------------------------------------------------------------------|------|

| 1. Measured Reference Voltage Ranges .....                                                               | 17   |

| 2. Latency Comparison of Vector Boolean Logic Operations Supported by PSRAM and Prior Accelerators ..... | 19   |

| 3. Comparison with State-of-the-art SRAM Based PIM Accelerators. ....                                    | 21   |

| 4. 128-bit AES Performance. ....                                                                         | 22   |

| 5. Comparison with Prior Digital IMC Works.....                                                          | 36   |

| 6. Power Breakdown .....                                                                                 | 56   |

| 7. GWCL Algorithm Memory Benefits(Excludes Index Memory) .....                                           | 57   |

| 8. Comparison with State-of-the-art SRAM Based IMC Accelerators .....                                    | 57   |

| 9. Comparison with Prior LDPC Implementations .....                                                      | 58   |

| 10. RISC-V Instruction Set Extensions .....                                                              | 80   |

| 11. AI Model Accuracy for Various Sparsity Ratios.....                                                   | 88   |

| 12. Comparison with State-of-the-art Fully Digital CIM Works.....                                        | 89   |

## LIST OF FIGURES

| Figure                                                                                                                                                                                | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1. PSRAM Chip with 8t SRAM Cell as the Operand Memory and the Proposed Single-cycle Logic-SA Design (Adapted from Sridharan <i>et al.</i> (2022a), with Permission). . . . .          | 12   |

| 2. In-memory Logic Simulation Waveforms. . . . .                                                                                                                                      | 14   |

| 3. PSRAM Chip Micrograph and Area Breakdown . . . . .                                                                                                                                 | 15   |

| 4. Frequency Scaling over Different Vdds (A), Static and Dynamic Power Consumption (B), Vref Scaling over Different Vdds (C), and Throughput Scaling over Different Vdds (D). . . . . | 16   |

| 5. Monte-carlo Simulations for Vref Separation Analysis . . . . .                                                                                                                     | 18   |

| 6. BWNN Hardware Mapping . . . . .                                                                                                                                                    | 20   |

| 7. (A) PSRAM Energy Consumption and (B) Processing Time for Running the Alexnet (Imagenet Dataset). . . . .                                                                           | 20   |

| 8. AES Block Diagram with the Gate Utilization. . . . .                                                                                                                               | 22   |

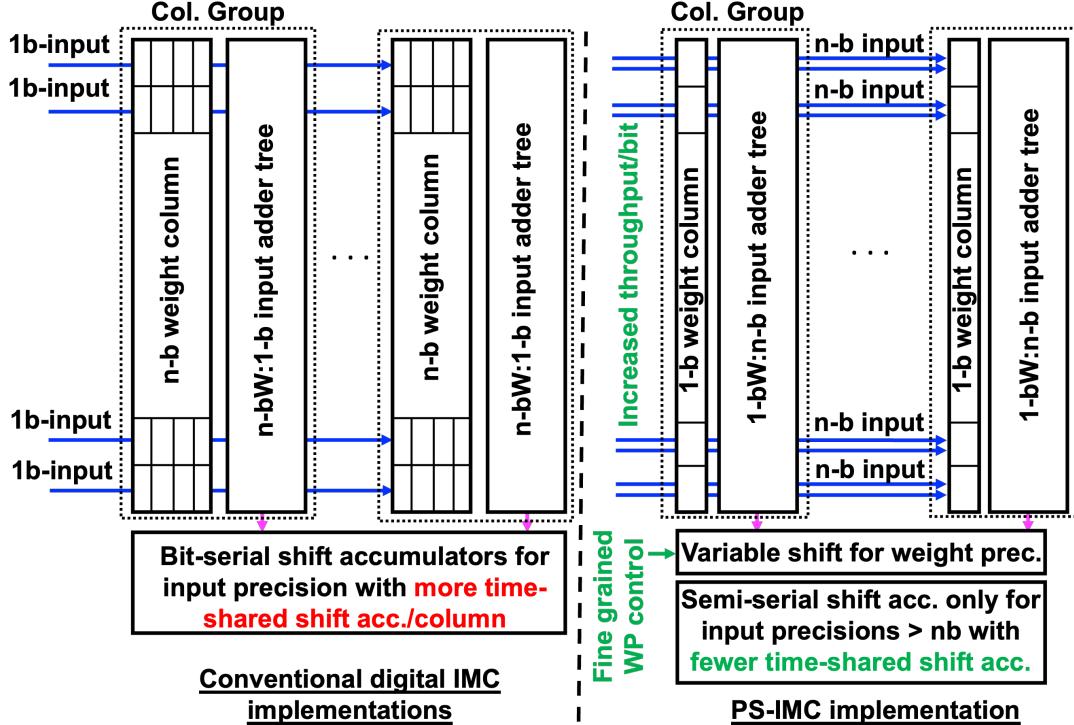

| 9. Comparison of Conventional Digital IMC Implementations Versus Proposed Throughput Oriented PS-IMC Implementation . . . . .                                                         | 26   |

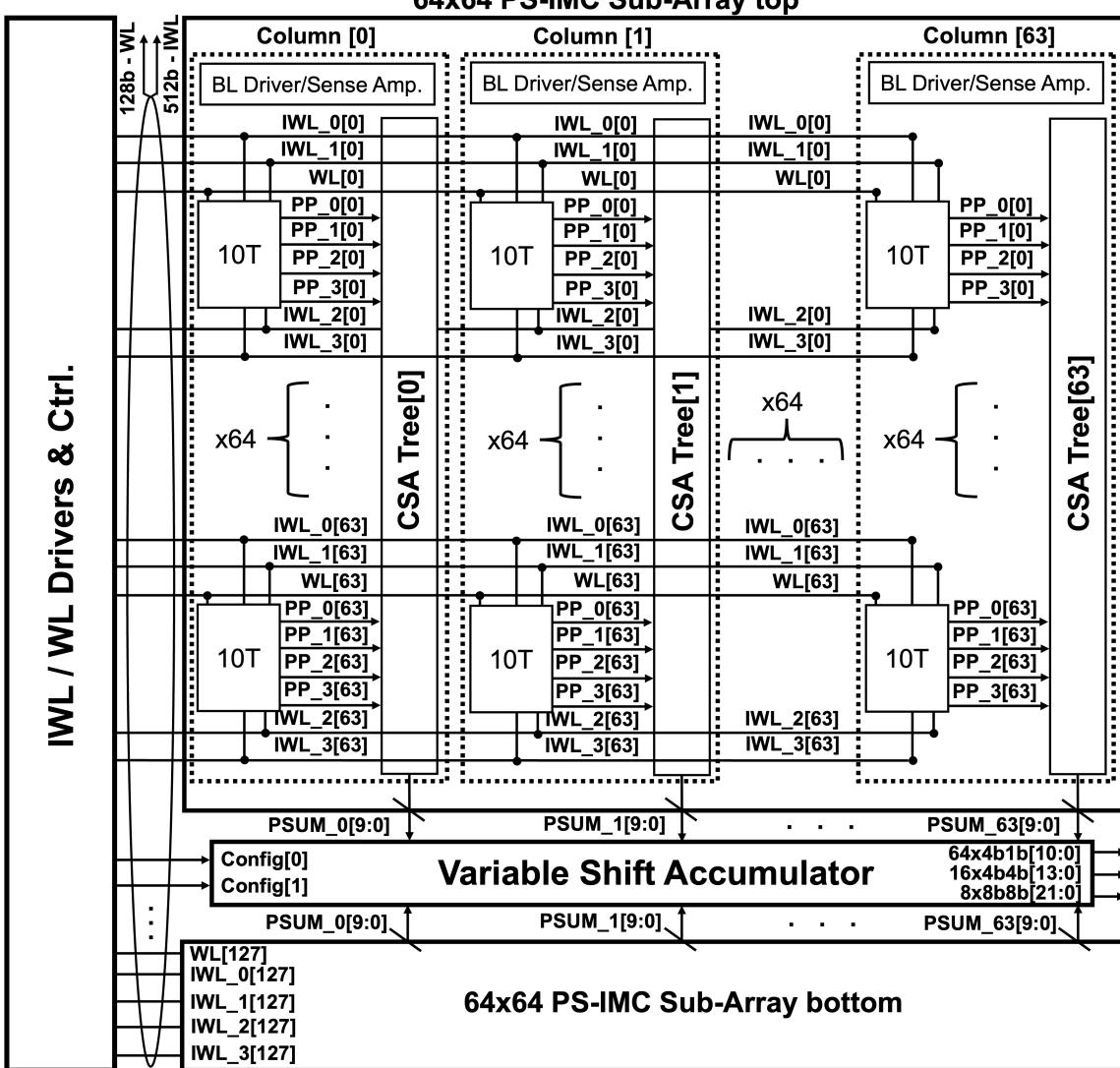

| 10. PS-IMC Macro Architecture Design. (Adapted from Sridharan <i>et al.</i> (2024a) with Permission) . . . . .                                                                        | 28   |

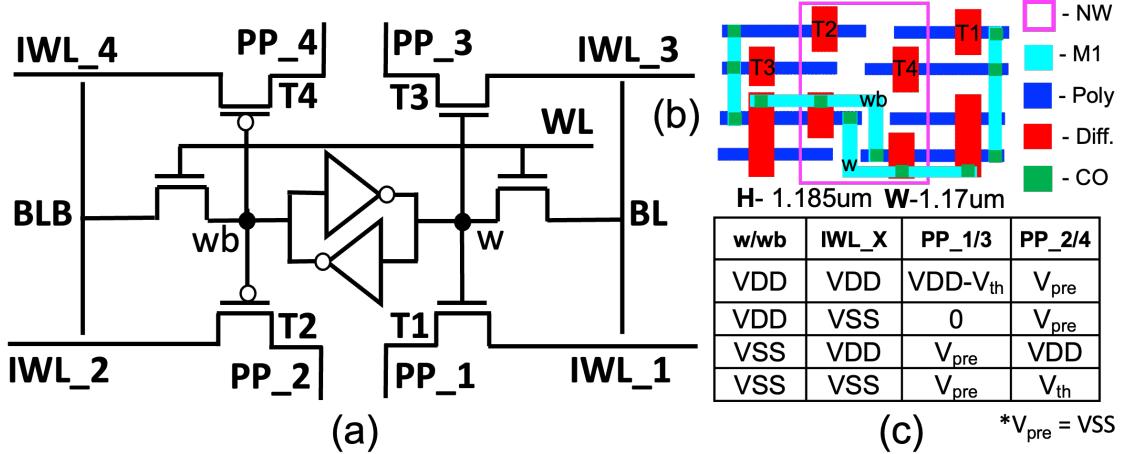

| 11. (A) Bit-cell Schematic, (B) Layout, and (C) Truth Table. . . . .                                                                                                                  | 29   |

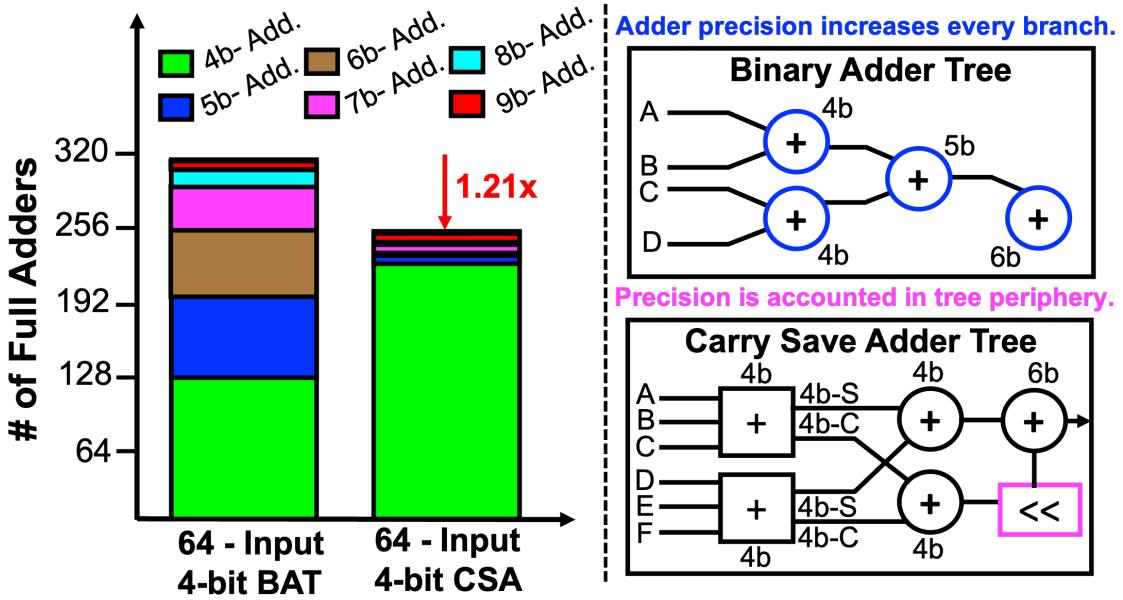

| 12. Precision Breakdown and Tree Structures of CSA and BAT . . . . .                                                                                                                  | 30   |

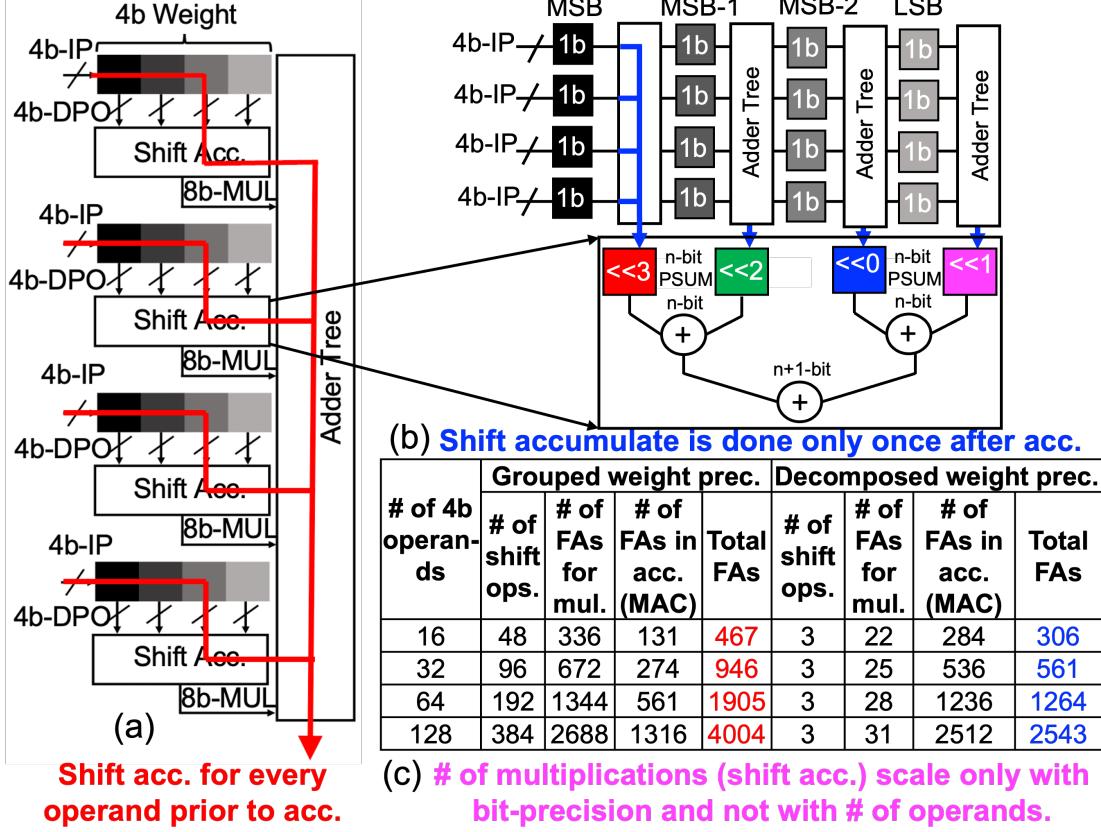

| 13. (A) Grouped Weight Precision, (B) PS-IMC's Decomposed Weight Precision, (C) Multiply and Accumulate Hardware Cost for 4-bit Operands . . . . .                                    | 32   |

| Figure                                                                                                                                                                                                                      | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

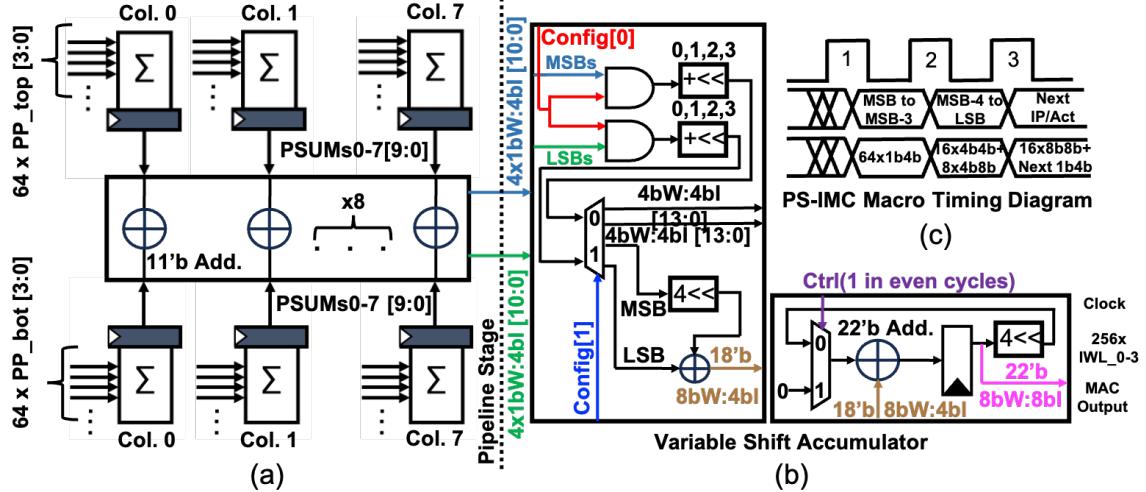

| 14. (A) Psum Reduction from Top and Bottom Sub-arrays, (B) Variable Shift Accumulator Micro-architecture, (C) Timing Diagram with the Total Number of Macs Performed in a Single PS-IMC Macro .....                         | 33   |

| 15. Throughput (TOPS) vs. Energy-efficiency (TOPS/W) for (a) 1bW:1/4bI, (B) 4bW:1/4bI, and (C) 8bW:1/4/8bI Modes. (D) Power and Frequency Scaling .....                                                                     | 34   |

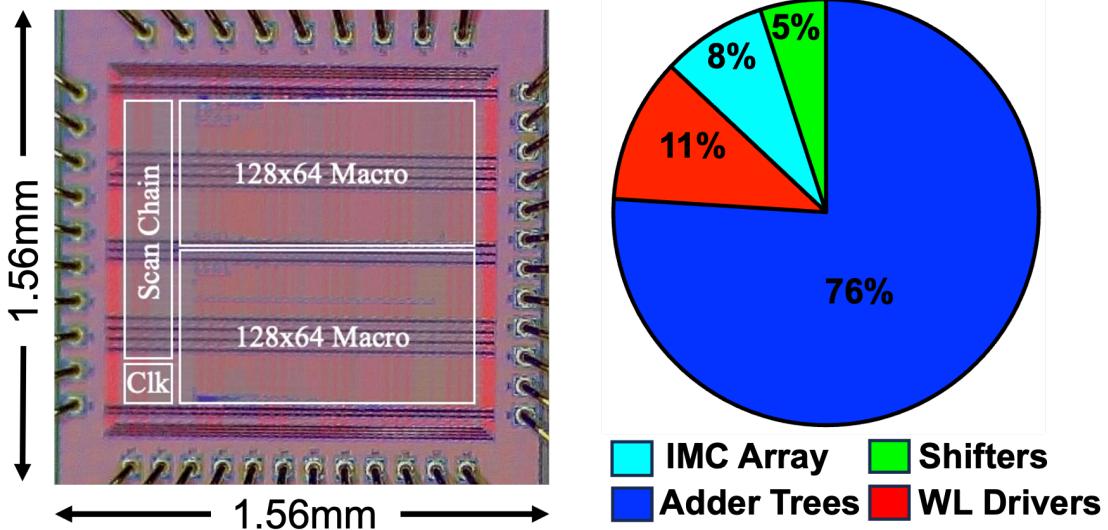

| 16. Die Micrograph (Left), and Area Breakdown (Right).....                                                                                                                                                                  | 35   |

| 17. Example of Neural-BP Decoding Procedure .....                                                                                                                                                                           | 42   |

| 18. (A) DSPIIMM Architecture (B) Unstructured Sparse Weight In-memory Compute (C) Structured Sparse Weight In-memory Compute (D) Data Flow of Bit-serial MVM. (Adapted from Sridharan <i>et al.</i> (2023) with Permission) | 45   |

| 19. (A) 6+2T(8T) Compute Bit-cell (B) Truth Table of 2T And/Dot-product ..                                                                                                                                                  | 48   |

| 20. EGWCL Algorithm Example .....                                                                                                                                                                                           | 50   |

| 21. Area Breakdown of (A) SSP Matrix Memory (B) USP Matrix Memory.....                                                                                                                                                      | 55   |

| 22. Current Sparse IMC Implementation Drawbacks, Benefits of Sparse Encoding, Challenges of Sparse Encoded Weights in IMC .....                                                                                             | 62   |

| 23. Overall Architecture of SP-IMC Macro, Bit-cell Schematic, Layout, and Micro-architecture of In-memory Decode Hardware. (Adapted from Sridharan <i>et al.</i> (2024b) with Permission) .....                             | 64   |

| 24. Dataflow of Various Modes in SP-IMC, Pipeline Diagram, Index Priority Queue, SpMM Parallelism in Memory .....                                                                                                           | 68   |

| 25. Mapping Methodologies for COO-CSC, RL, Why CSR Is Not IMC Friendly and Benefits of N:M Sparse Encoding.....                                                                                                             | 70   |

| Figure                                                                                                                                   | Page |

|------------------------------------------------------------------------------------------------------------------------------------------|------|

| 26. Chip Measurement Results, Accuracy Results of Pruned DNNs, Area Breakdown in Macro and System Level .....                            | 71   |

| 27. System Latency, Write Operations, Figure of Merit (FOM), and Comparison to Prior Digital IMCs .....                                  | 73   |

| 28. SAFER Chip Architecture .....                                                                                                        | 76   |

| 29. SAFE Core and Macro Architecture .....                                                                                               | 79   |

| 30. (A) Sparse Decode Unit, (B) Sparse Compression and Mapping, (C) Reducing Hardware Complexity by Normalizing Input Queue Length ..... | 82   |

| 31. (A) Floating-point Multiply Unit and (B) Fused Dot-product in SAFE .....                                                             | 84   |

| 32. Pipeline Diagram for a 1:2 Sparse Workload .....                                                                                     | 85   |

| 33. (A) SAFE Power, (B) Area Breakdown .....                                                                                             | 86   |

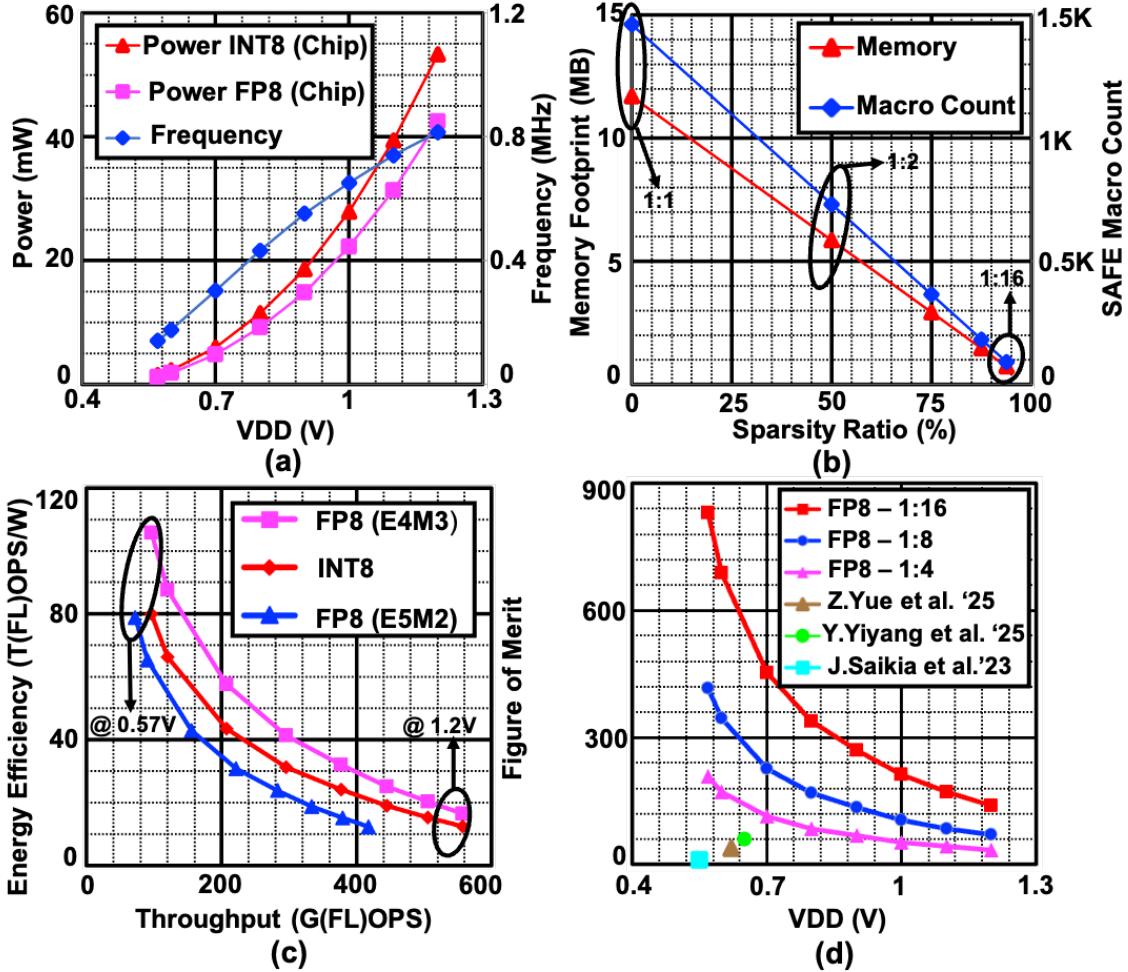

| 34. Power and Frequency Scaling (A), Sparsity Savings (B), Throughput and Energy Efficiency Scaling (C), Figure of Merit (D) .....       | 87   |

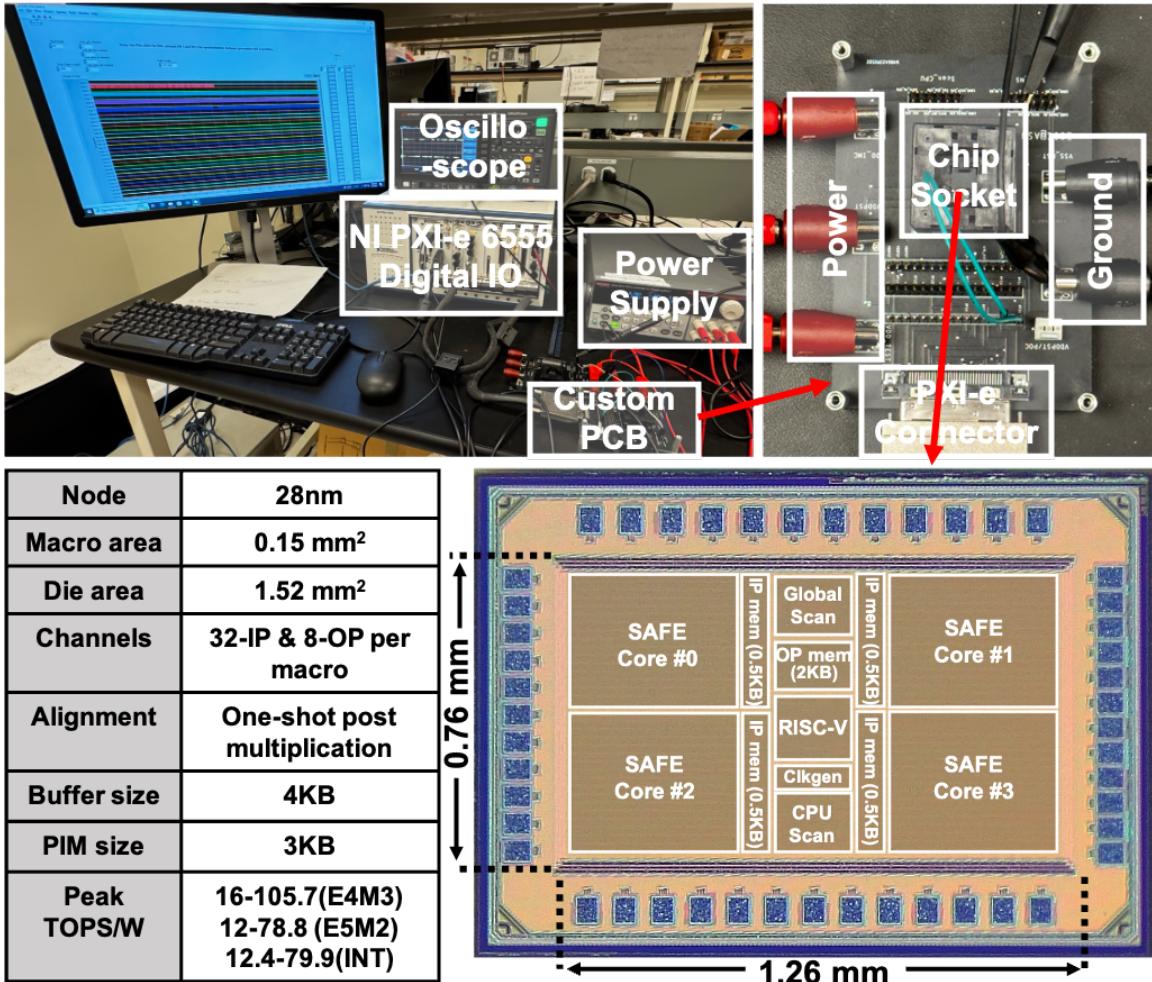

| 35. Testing Setup, Die-Micrograph and Chip Summary .....                                                                                 | 90   |

# Chapter 1

## INTRODUCTION

### 1.1 Today's Computing Limitations

Over the past several decades, compute performance was primarily limited by hardware capabilities, but this was consistently overcome by advances in transistor scaling, as described by Moore's Law (doubling the number of transistors per chip) and Dennard scaling (allowing for higher clock speeds and lower power per transistor as they shrank) However, as we approach the physical and thermodynamic limits of miniaturization, both Moore's Law and Dennard scaling have slowed significantly, making further gains increasingly difficult and expensive Das (2015).

At the same time, the traditional Von-Neumann computing paradigm faces inherent bottlenecks that are now more pronounced. The most significant is the Von-Neumann bottleneck, which arises from the separation of memory and compute units. In this architecture, data and instructions must travel back and forth across a shared bus, limiting throughput and causing the processor to idle while waiting for data transfers. As processor speeds have far outpaced improvements in memory bandwidth, this bottleneck has only worsened, especially for data-intensive applications like AI and large-scale data analytics. Additionally, the serial, step-by-step nature of Von-Neumann processors restricts their ability to efficiently handle highly parallel workloads, further limiting performance gains even as more cores are added. Attempts to mitigate these issues—such as using larger caches, branch prediction, and multi-core designs—have

provided incremental improvements but have not solved the fundamental architectural limitations.

The memory system which spans from fast SRAM caches to DRAM main memory and even to slower storage like SSDs is responsible for a disproportionate share of the system’s energy consumption, performance bottlenecks, reliability issues, and cost. As applications continue to evolve particularly in domains such as machine learning, genomics, graph processing, and large-scale data analytics they are becoming far more data intensive, exacerbating the pressure on memory systems. The result is a bottleneck between communication data path between the compute and memory. This bottleneck, known as the memory wall problem and results in substantial data movement overhead. A key observation from Mutlu (2018) highlights that, in a traditional CPU, the data movement required for a simple ADD operation can cost up to 115 $\times$  more than the computation itself.

## 1.2 Memory Centric Compute Paradigm

A promising solution to the memory wall problem is the Processing-in-Memory (PIM)—also referred to as Compute-in-Memory (CIM) or In-Memory Computing (IMC)—paradigm (Hereafter, the terms Processing-in-Memory (PIM), Compute-in-Memory (CIM), and In-Memory Computing (IMC) will be used interchangeably). This approach rethinks the traditional separation between computation and storage by placing computing elements as close to memory as possible, and in many cases, embedding them directly within the memory arrays. By doing so, it virtually eliminates the performance and energy bottlenecks caused by excessive data movement, addressing the issue from both circuit-level and architectural perspectives. Over the

past decade, numerous studies have demonstrated the effectiveness of this paradigm across various memory types including SRAMs Zhang *et al.* (2017); Yin *et al.* (2020); Jiang *et al.* (2020); Hu *et al.* (2025), DRAMs Zhang *et al.* (2021a); Li *et al.* (2017); Ahn *et al.* (2015); Seshadri *et al.* (2017), and even emerging non-volatile memory technologies like MRAMs Sridharan *et al.* (2022b); Zhang *et al.* (2024b) and RRAMs Zhang *et al.* (2024a); Wang *et al.* (2023). The benefits of applying a memory-centric computing model vary depending on the memory type as well as the underlying compute methodology whether analog or digital. The analog computing model as in Zhang *et al.* (2017); Jiang *et al.* (2020), map discrete numbers to the current domain and uses current summing to perform arithmetic instead of traditional digital gates. This has huge potential when it comes to reduced computation resources but it requires the use of ADCs/DACs which tradeoffs compute accuracy with power, performance, area as well as robustness and variability Seo *et al.* (2022). On the other hand we have digital compute paradigm which is similar to digital ASICs but here the memory centric paradigm is adopted by closely interleaving compute and memory by directly driving compute logic with static components thereby effectively moving a part if not most of the compute within the bit-cell or into the memory array. This eliminates the need for memory reads and writes for compute effectively matching the memory bandwidth with the memory size. This has much more practical viability and can achieve energy efficiency close to analog compute. This dissertation specifically focuses on exploring digital compute-in-memory circuits and how they can be effectively used to accelerate data-intensive applications.

The key contributions of this thesis are:

- We propose a programmable Processing-in-Memory (PIM) architecture that unifies PIM paradigm with flexible programmability. This design allows a single

memory-centric compute substrate to efficiently support and accelerate a wide range of data-intensive applications, rather than being limited to fixed-function accelerators.

- To demonstrate its practical viability, we implement and fabricate the programmable PIM design as a silicon prototype using 65nm CMOS technology. We then validate the architecture’s effectiveness by mapping representative applications directly onto the chip. Through real-time execution and benchmarking, we demonstrate significant performance and energy benefits, highlighting the practicality and generalizability of our programmable PIM compute approach.

- Given the dominance of AI as a data-intensive workload, we explore how different characteristics of AI/ML models—including model size, numerical precision, data types, and sparsity—interact and trade off with one another in the context of in-memory computing. We propose a suite of CIM architectures tailored to effectively handle these diverse requirements and to deliver real-time compute benefits.

- To enable scalable precision, we present PS-IMC (Precision-Scalable In-Memory Compute), a novel CIM architecture that supports bit-parallel multiply-accumulate (MAC) operations across multiple integer precisions. PS-IMC achieves high compute efficiency by dynamically adapting to different precision levels through intelligent resource sharing within the compute pipeline. This flexibility allows it to deliver one of the highest compute throughputs reported to date for a wide range of integer formats. The design is fabricated in 28nm CMOS technology and is benchmarked against state-of-the-art CIM macros, demonstrating its superior performance and precision scalability.

- To efficiently handle sparsity, we propose two CIM architectures: DSPIMM

and SP-IMC. These are among the first in-memory compute designs to support unstructured sparsity and can directly operate on compressed weight representations stored within the memory. This is made possible through a time-interleaved sparse decode methodology, which achieves the benefits of memory compression while significantly reducing decoding complexity and overhead.

- We validate the DSPIMM architecture by mapping a sparse communication-driven deep neural network (DNN) algorithm—specifically, the Neural Belief Propagation (Neural BP) algorithm—onto the hardware. We compare its performance against traditional ASIC implementations to demonstrate the advantages of in-memory execution for sparse models.

- In SP-IMC we further explore how the time shared sparse decode methodology can be configured to support multiple sparse compression formats and a wide range of sparsity ratios, all while preserving bit-parallel MAC support and offering robust compute efficiency across use cases. A prototype of the proposed architecture, fabricated in 28nm CMOS technology, demonstrates more than a 4-50 $\times$  reduction in compute resources required to run popular models such as ResNet, compared to baseline digital designs, highlighting the substantial benefits of CIM for real-world inference tasks.

- To address flexible data type support, we design a fused multiply-add (FMA) pipeline within the CIM fabric that can process both integer and floating-point formats across various precision levels. This allows hardware reuse across both INT8 and FP8 formats.

- We also explore an alternative semi-structured N:M sparsity methodology in CIMs, which offers a more hardware-friendly approach to sparse compute while

preserving high compression efficiency with better accuracy compared to a fully structured sparsity.

- To address the scalability of matrix operations across varying shapes and dimensions, we co-design a lightweight, custom RISC-V processor with our CIM macros. This hybrid architecture serves as a flexible controller to orchestrate data movement and computation across matrix tiles, enabling scalable and programmable matrix multiplication.

- All proposed features are integrated into a complete 28nm silicon prototype, and we perform comprehensive comparisons with state-of-the-art CIM designs to show that our system achieves best-in-class performance, power, and area efficiency.

### 1.3 Thesis Organization

The outline of this thesis is as follows:

- **Chapter 2** presents a programmable and generic SRAM (PSRAM) based Compute-in-memory macro prototyped in 65nm CMOS. This chapter goes over the memory-cell circuit design, macro architecture, variability analysis, chip measurement results, and case studies for power/performance characterization of prototype chip taped-out in commercial 65nm CMOS.

- **Chapter 3** presents a precision scalable Compute-in-memory macro prototyped in 28nm CMOS that proposes a hardware scaling methodology in CIM based design to accelerate variable fixed precision multiply-and-accumulate workloads primarily focused on accelerating matrix-vector multiplications. The CIM circuit

design, macro architecture, chip measurement results, workload characterizations and comparison with prior SoTA CIM designs are included in this chapter.

- **Chapter 4** presents a system level CIM based acceleration hardware for an AI based channel decoder primarily used in communication applications. This chapter elaborates on channel codes, AL based channel decoding algorithms, a sparse matrix multiplier design based on CIM, algorithm and hardware performance characterization and comparison with prior works.

- **Chapter 5** presents a prototype chip fabricated in 28nm CMOS that accelerates generic unstructured sparse matrix-vector multiplications using a digital Compute-in-Memory (CIM) architecture. This design explores the integration of multiple sparsity formats and compression ratios within a single, monolithic CIM framework, enabling broad applicability across diverse AI workloads. By directly computing on compressed representations we show how the proposed architecture achieves substantial reductions in compute resource usage for large-scale AI models.

- **Chapter 6** presents a digital CIM-based fused multiply-add (FMA) matrix-vector accelerator prototype chip that supports semi-structured sparsity and integrates a custom RISC-V CPU for efficient data movement. We demonstrate how the FMA pipeline is designed to handle both integer and floating-point workloads using shared hardware. We then evaluate the accelerator on various CNN and LLM models with different semi-structured sparsity formats, all supported natively in hardware. The chapter also explores the idea of how a RISC-V core can serve as a programmable controller to manage data flow across diverse AI workloads.

- **Chapter 7** concludes the dissertation.

## Chapter 2

### PROGRAMMABLE AND GENERIC PROCESSING-IN-SRAM ACCELERATOR

This chapter introduces a generic and programmable Processing-in-SRAM (PSRAM) accelerator chip that enables acceleration of a variety of data-intensive workloads. Built on an 8T-SRAM array, the proposed design is the first to support the full set of Boolean logic operations—including 2 and 3-input NOR, NAND, XOR—along with majority and full-adder operations, all executed in a single cycle reduced to just memory reads. This level of functionality and flexibility within a single PSRAM platform enables a broad range of compute-in-memory applications, including parallel vector processing, neural network acceleration, and data encryption. To demonstrate its capabilities, the PSRAM accelerator is implemented within a 16 Kb SRAM macro and fabricated in a 65nm CMOS process. The prototype chip operates at a frequency of 1.23 GHz, making it one of the fastest programmable in-memory computing systems reported to date. The chip achieves a peak system-level throughput of 1.2 TOPS and delivers an energy efficiency of 34.98 TOPS/W at 1.2V, across the complete set of supported 2- and 3-input Boolean logic functions.

#### 2.1 Introduction

Traditional Von Neumann computing architectures—such as central processing units (CPUs) and graphics processing units (GPUs)—have long been the backbone of general-purpose and high-performance computing. These platforms are valued for their programmability, flexibility, and ability to efficiently execute a broad spectrum of bit-

wise logic and arithmetic operations. However, as data-intensive applications continue to grow in both scale and complexity, these architectures increasingly face fundamental bottlenecks in-memory bandwidth and energy efficiency. The separation of memory and computation in Von Neumann systems results in frequent and energy-expensive data transfers between processing and storage units, which limits performance scalability and contributes significantly to power consumption. In response to these limitations, Processing-in-Memory (PIM) architectures have emerged as a promising alternative. By integrating computation capabilities directly within or near memory arrays, PIM designs aim to reduce data movement, lower energy consumption, and improve overall throughput. However, application-specific PIM architectures, while efficient for targeted tasks, often suffer from limited generality. These designs are typically optimized for a specific algorithm or application domain—such as convolutional neural networks or encryption—which makes them inflexible and unable to adapt to the fast-paced evolution of software workloads and algorithmic paradigms. As such, their utility diminishes when applied outside their narrowly defined operational scope, making them unsuitable for general-purpose use Biswas *et al.* (2018).

To overcome these limitations, recent research has focused on developing generic and programmable PIM architectures capable of supporting a wider range of applications. State-of-the-art designs, such as those presented in Wang *et al.* (2020), explore alternatives to conventional bit-parallel processing models by adopting bit-serial computing techniques. These approaches enable more compact and reconfigurable PIM implementations that support basic arithmetic and logic functions using a limited set of in-memory operations. Bit-serial methods decompose arithmetic computations into a sequence of Boolean operations executed over multiple cycles, which allows for flexible algorithm mapping without requiring extensive hardware specialization.

However, this added flexibility comes at the cost of increased latency and greater intermediate data movement. Since bit-serial implementations often require multiple compute cycles even for basic operations, they involve frequent read and write-back steps between memory cells and peripheral logic. This can negate some of the energy and performance benefits that PIM architectures are designed to deliver, especially in scenarios where high-throughput and low-latency computation are essential Biswas *et al.* (2018); Wang *et al.* (2020); Valavi *et al.* (2019); Zhang *et al.* (2018); Yue *et al.* (2020).

To address the limitations of existing application-specific and bit-serial programmable PIM designs, this work presents a programmable Processing-in-SRAM (PSRAM) accelerator that combines the high computational efficiency of in-memory processing with the flexibility of general-purpose programmability. Unlike prior works that are either limited to a narrow set of operations or require multiple compute cycles to implement basic logic functions, the proposed PSRAM supports a complete set of Boolean operations—including both 2-input and 3-input boolean logic operations (e.g., NOR, NAND, XOR), majority logic, and full adder functionality all executed within a single memory cycle. To the best of our knowledge, this is the first in-memory computing macro that realizes the complete set of logic functions in a single-cycle execution model.

This enables one of the fastest programmable in-memory computing systems reported to date, with the prototype design achieving a clock frequency of 1.23 GHz. The one-cycle logic execution model not only improves raw throughput but also addresses one of the major inefficiencies of previous programmable in-memory logic designs: redundant intermediate data write-back. In traditional multi-cycle PIM systems, more complex logic functions such as 3-input operations and full adders are

typically realized through a sequence of basic Boolean steps, requiring multiple cycles. Each cycle may involve reading and writing intermediate results to and from memory, incurring both latency and energy overheads. By integrating support for complex Boolean operations within a single memory cycle, PSRAM eliminates this overhead, substantially reducing both latency and dynamic energy consumption Biswas *et al.* (2018); Wang *et al.* (2020); Valavi *et al.* (2019); Zhang *et al.* (2018); Yue *et al.* (2020).

PSRAM accelerator is demonstrated across three distinct application domains to showcase its versatility and general-purpose programmability. First, it supports bulk bitwise vector operations, which are commonly used in data-intensive workloads such as search, database filtering, and bitmap indexing. Second, the architecture enables efficient low-precision deep learning acceleration, leveraging its Boolean and arithmetic capabilities to execute quantized neural network inference directly within memory. Finally, PSRAM is applied to cryptographic computation by supporting the Advanced Encryption Standard (AES) algorithm, illustrating its capacity to handle complex bit-manipulation and control flow patterns required in security applications.

## 2.2 PSRAM Chip Circuit and Architecture

PSRAM leverages the charge-sharing feature of the 8T-SRAM cell on Read Bit-Line (RBL) and elevates it to implement 2-input and 3-input Boolean logic between two or three selected rows in a single memory read cycle. The key idea comes from the observation that certain discharge rate on the precharged RBL is determined by the data value stored in the simultaneously selected memory cells attached to the same bit-line. For instance, by activating three memory rows via Read Word-Lines (RWL), e.g., RWL0-RWL2 (Fig. 1), if  $S_{0,0}$ ,  $S_{1,0}$ , and  $S_{2,0}$  memory cells all store ‘1’s, then

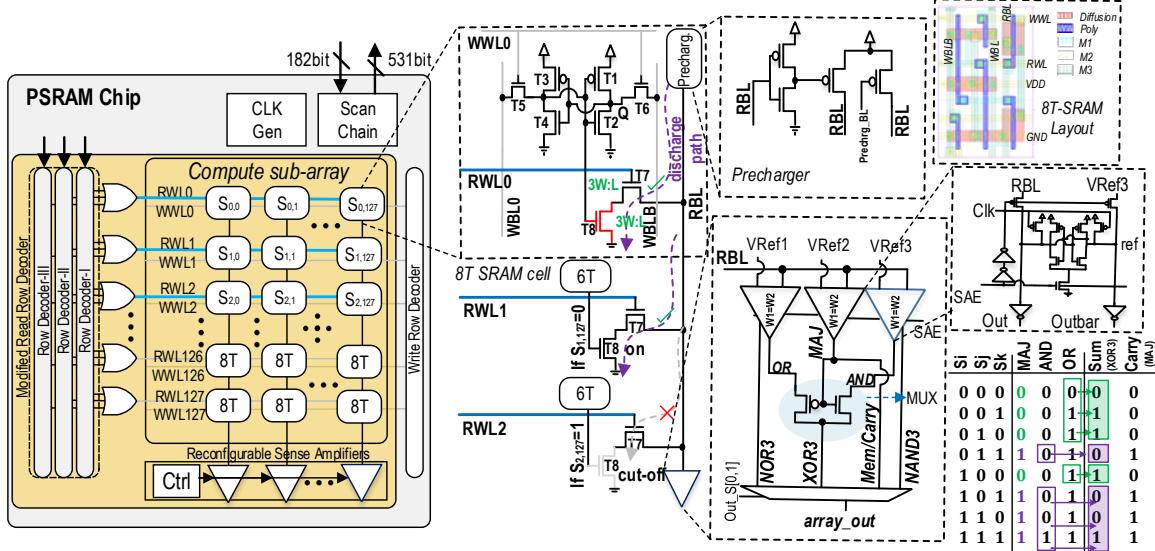

Figure 1. PSRAM Chip with 8t SRAM Cell as the Operand Memory and the Proposed Single-cycle Logic-SA Design (Adapted from Sridharan *et al.* (2022a), with Permission).

the read access transistors (T8) remain OFF, and the RBL precharged voltage does not discharge. On the other side, if all cells store ‘0’s, the RBL voltage will rapidly discharge through T8s. Similarly, based on different combinations of the values stored in those memory cells, the discharged voltage value will be different if sampled at a preset frequency, which could be sensed by our follow up ‘logic-SA’ design to implement different logic functions through selecting different voltage references. Theoretically, there will be four different voltage levels based on all possible combinations of three memory cell data in the same bit-line. In our design, to yield a sufficiently large sense margin, as shown in Monte Carlo simulations (Fig. 5), the read path transistor (T7 and T8) size is designed to be  $3\times$  as shown in Fig. 1. To implement a programmable logic function, a new re-configurable logic-SA is designed as in Fig. 1. It consists of three sub-SAs with voltage references (i.e.,  $V_{Ref1} < V_{Ref2} < V_{Ref3}$ ), each dedicated to distinct logic functions. In this way, by activating three memory rows (i.e., input operand vectors) at the same time, each sub-SA performs a neat voltage comparison between

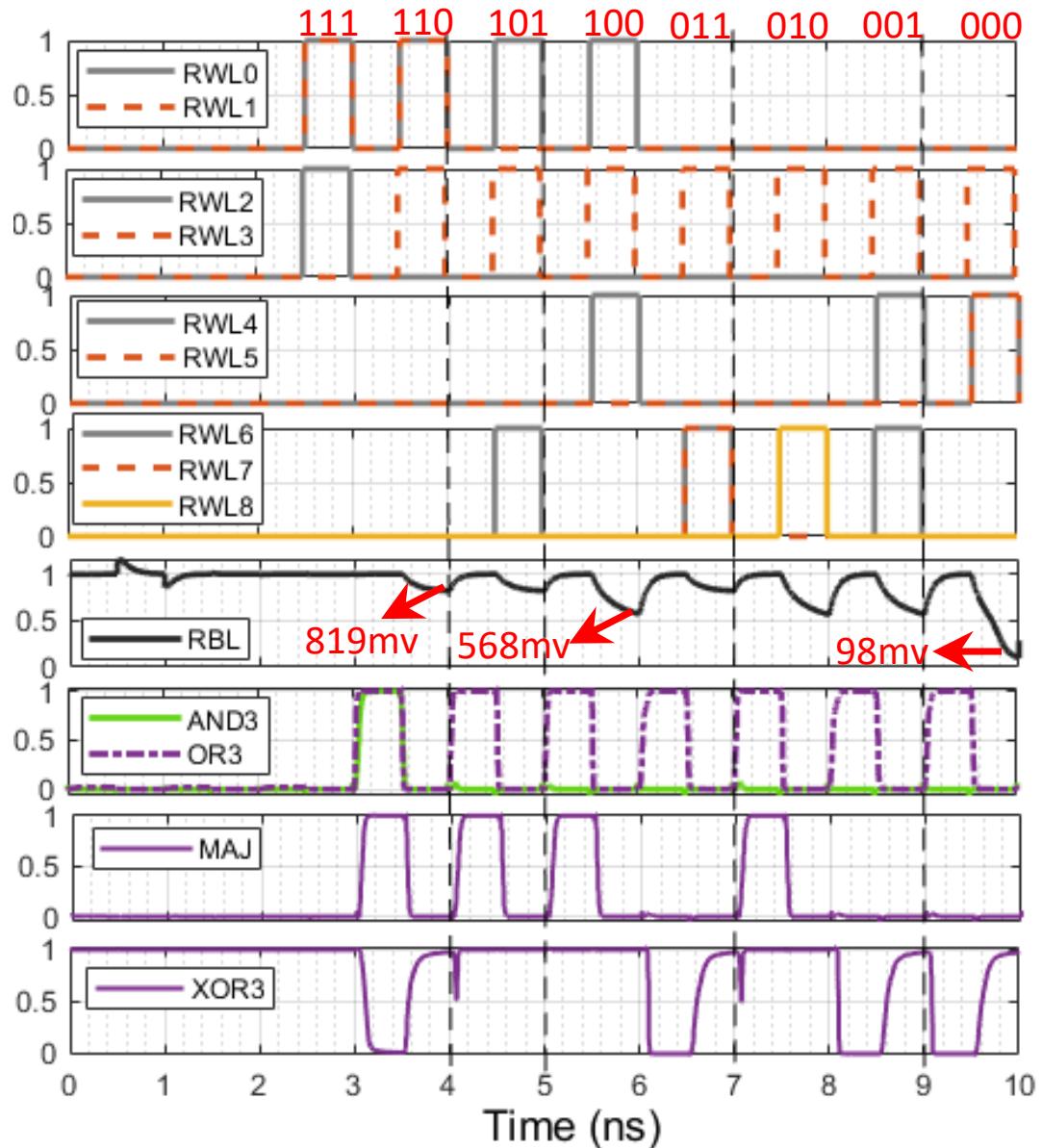

the reference voltage and the discharged RBL voltages (w.r.t. different discharge rate corresponding to stored memory cell data), which respectively generates (N)OR3, (MAJ)MIN, and (N)AND3 logic output (complementary SA), and more importantly, at the same time. A novel single-cycle in-SRAM XOR3 (full adder's Sum) logic is developed through an interesting observation as shown in the bottom-right truth table of Fig. 1. When the majority function (MAJ) output (green box in the truth table) is '0', the corresponding XOR3's output is the same as the OR3's output. When the majority function output is '1', XOR3's output can be achieved through AND3 as highlighted by the purple box. Based on our last paragraph description, our logic-SA could simultaneously get the OR3, MAJ and AND3 logic outputs, then we propose to design the XOR3 logic through a two-transistor 2:1 multiplexer (with MAJ output as the selector) circuit highlighted in the proposed reconfigurable logic-SA. The Boolean logic of in-memory XOR3 can be given as  $XOR3 = MAJ(S_i, S_j, S_k).AND(S_i, S_j, S_k) + MIN(S_i, S_j, S_k).OR(S_i, S_j, S_k)$ . In this way, assuming three vector operands are pre-stored in the memory, parallel in-memory full adder logic can be implemented for the first time in a single memory cycle, where MAJ and XOR3 outputs generate the carry-out and Sum signals, respectively. The two-input bit-wise operations will be readily implemented by initializing one row to '0'/'1'. All in-memory logic simulations are first shown in Fig. 2, showing corresponding functionality.

Figure 2. In-memory Logic Simulation Waveforms.

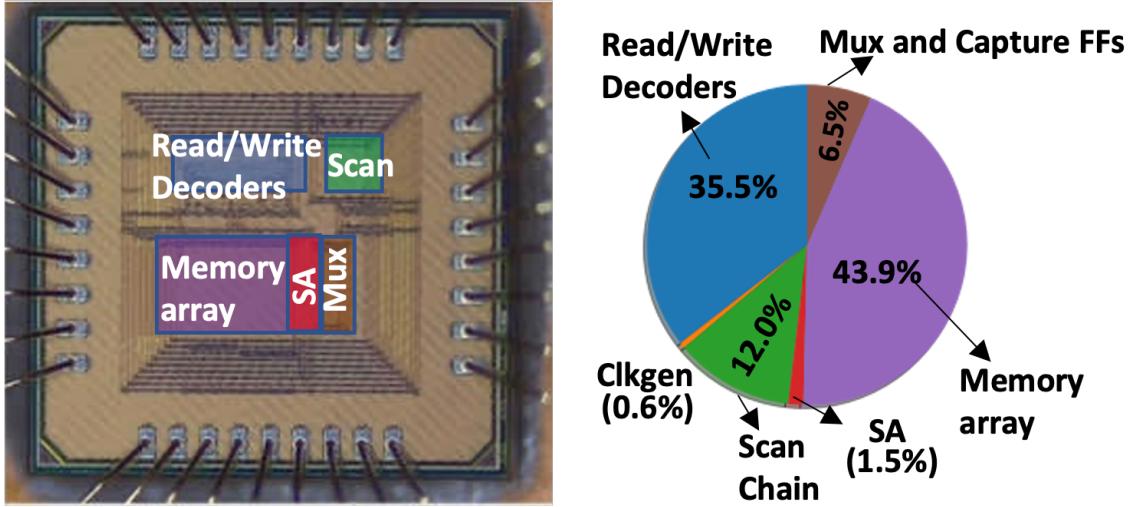

Figure 3. PSRAM Chip Micrograph and Area Breakdown

## 2.3 Chip Measurement Results

### 2.3.1 Performance Measurements

We prototyped the PSRAM macro ( $128 \times 128$ ) in TSMC 65nm CMOS (Fig. 3). The macro has a 2-KB/16Kb capacity and occupies  $0.17 \text{ mm}^2$  (with decoder) in the chip floorplan. The bit-cell has an area of  $4.56 \mu\text{m}^2$  ( $1080 F^2$  when scaled according to feature size), which is designed using logic rules. For efficient integration, the SAs are pitch matched w.r.t. the column and occupy 3.4% of the array size ( $0.082 \text{ mm}^2$ ). The complete core area breakdown is shown in Fig. 3. The PSRAM macro consumes 36 pJ (includes power consumed by all components on the die) and takes 813 ps to generate 512 outputs of the complete 3 input logic set (AND3, XOR3, OR3, MAJ). This represents a peak throughput of  $2 \times 128 \times 4 / 813\text{ps} = 1259.52 \text{ GOPs}$  at 1.2V supply and a compute density of 583.12 GOPS/mm<sup>2</sup>. PSRAM achieves a significant speedup of 4-157 $\times$  when compared to state-of-the-art in-memory computing works Biswas

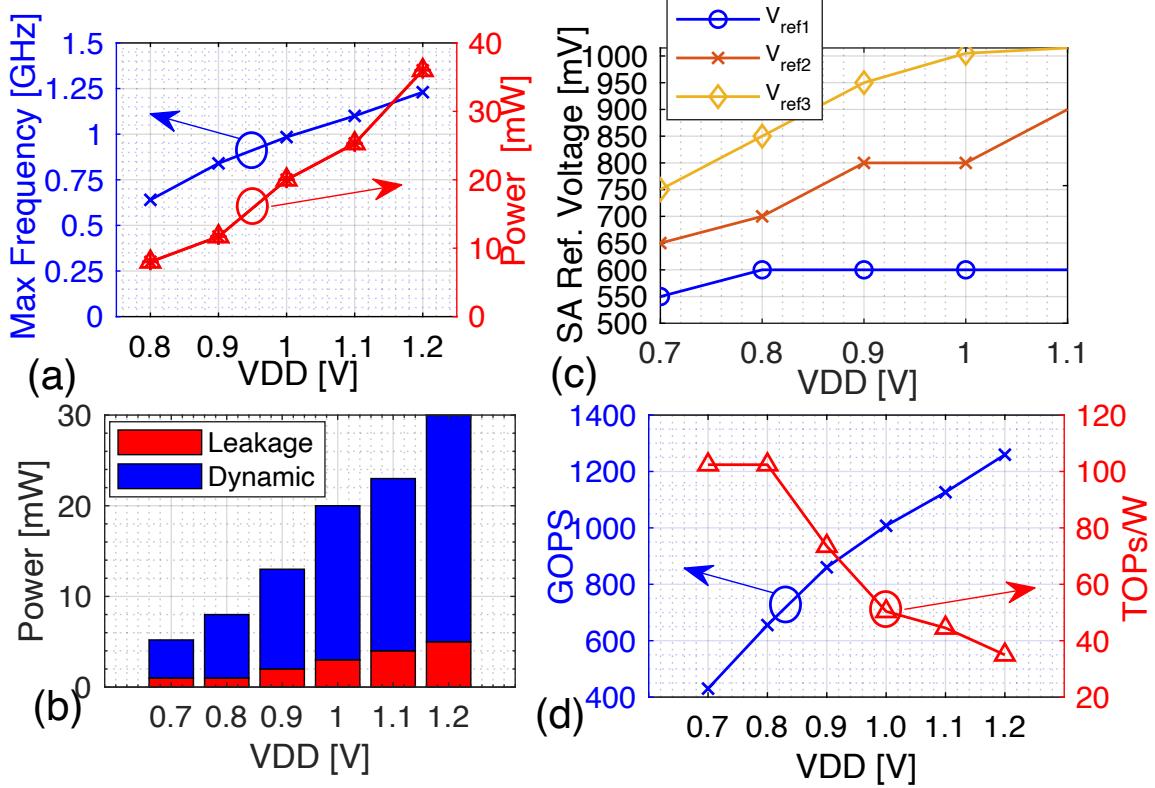

Figure 4. Frequency Scaling over Different Vdds (A), Static and Dynamic Power Consumption (B), Vref Scaling over Different Vdds (C), and Throughput Scaling over Different Vdds (D).

*et al.* (2018); Wang *et al.* (2020); Valavi *et al.* (2019); Zhang *et al.* (2018). We report the maximum frequency, power consumption, throughput w.r.t. different VDDs in Fig. 4.

### 2.3.2 Variability Analysis

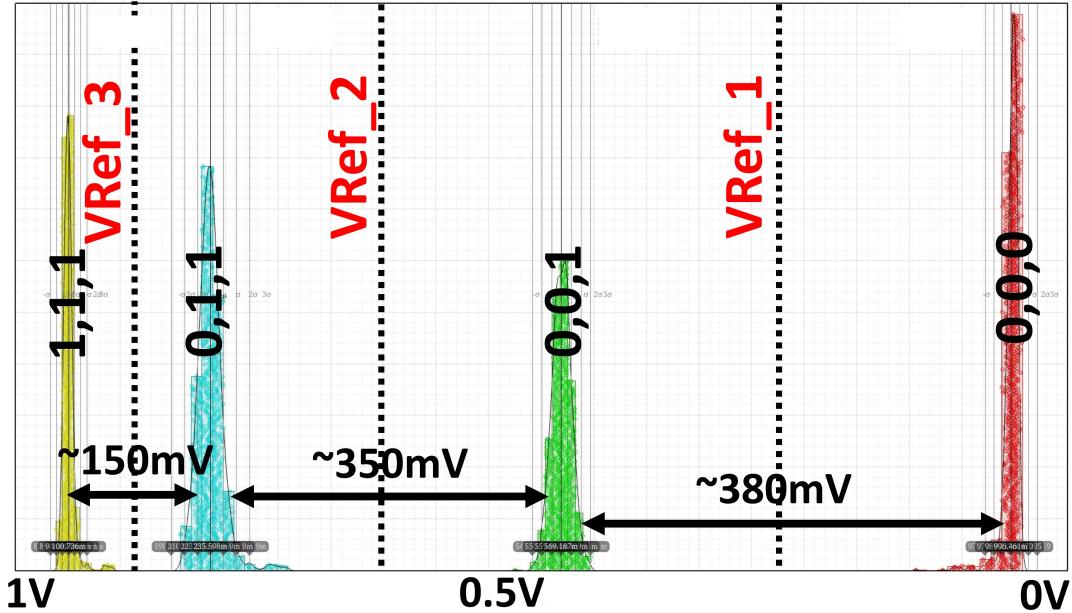

The RBL sense margins are first tested through post-layout Monte Carlo simulations in Cadence Spectre for the four possible sensing voltages, as shown in Fig. 5, where

Table 1. Measured Reference Voltage Ranges

| <b>VDD/V<sub>Ref</sub></b> | <b>V<sub>Ref1</sub> (V)</b> | <b>V<sub>Ref2</sub> (V)</b> | <b>V<sub>Ref3</sub> (V)</b> |

|----------------------------|-----------------------------|-----------------------------|-----------------------------|

| <b>0.7V @ 0.42GHz</b>      | <b>509m-546m</b>            | <b>603m-647m</b>            | <b>658m-693m</b>            |

| <b>0.8V @ 0.64 GHz</b>     | <b>452m-616m</b>            | <b>620m-733m</b>            | <b>745m-780m</b>            |

| <b>0.9V @ 0.84 GHz</b>     | <b>414m-661m</b>            | <b>669m-750m</b>            | <b>829m-889m</b>            |

| <b>1.0V @ 0.98GHz</b>      | <b>503m-711m</b>            | <b>735m-902m</b>            | <b>908m-995m</b>            |

| <b>1.1V @ 1.1GHz</b>       | <b>550m-754m</b>            | <b>760m-994m</b>            | <b>999m-1.083</b>           |

| <b>1.2V @ 1.23GHz</b>      | <b>554m-790m</b>            | <b>815m-1.08</b>            | <b>1.09-1.16</b>            |

the sensing margin is reported considering both process (inter-die) and mismatch variations (intra-die) for core VDD (1.0 V) at 1 GHz.

During the chip measurements, off-chip voltage references are provided ( $V_{Ref}$ ) to the SAs. To conduct the  $V_{Ref}$  variation analysis on chip, we test all 128 bit-lines, 100 times, for all possible bit value combinations in memory. 10 chips are tested and we report all the reference voltage ranges at different VDDs and the corresponding maximum frequencies with zero logic errors in Table 1. It is found that at lower voltages the maximum operating frequency is limited by the shrink of  $V_{Ref}$  ranges. A higher VDD also yields a larger sensing margin.

Figure 5. Monte-carlo Simulations for Vref Separation Analysis

## 2.4 Application Evaluation and Comparison

### 2.4.1 Case Study 1: Bulk Bitwise Boolean Operations

The PSRAM could be leveraged to implement bulk bitwise Boolean logic operations efficiently between vectors stored in the same memory sub-array. This can lead to efficient re-use of the internal memory bandwidth. Table 2 compares the latency for a set of vector operations of interest, implemented by three generic PIM designs. We achieve the best performance of each design, where input vectors  $A(a_0a_1\dots)$   $B(b_0b_1\dots)$  and  $C(c_0c_1\dots)$  are stored in separate rows of the memory. We draw two conclusions from Table 2. First, our PSRAM is the only design that supports a full-set of Boolean logic (both 2-input and 3-input) and integer operations. Second, due to the complexity

Table 2. Latency Comparison of Vector Boolean Logic Operations Supported by PSRAM and Prior Accelerators

| Parameters                      | Y. Zhang et al. (2018) | J. Wang et al. (2020) | PSRAM           |

|---------------------------------|------------------------|-----------------------|-----------------|

| Capacity (KB)                   | 8                      | 16                    | 2               |

| Technology (nm)                 | 40                     | 28                    | 65              |

| Frequency (GHz)                 | 0.029                  | 0.475                 | 1.23            |

| NOT (ns / # of Cycle)           | 34.72 / 1              | 2.1 / 1               | <b>0.81 / 1</b> |

| NAND2 (ns / # of Cycle)         | 34.72 / 1              | 2.1 / 1               | <b>0.81 / 1</b> |

| NAND3 (ns / # of Cycle)         | 69.44 / 2              | 4.2 / 2               | <b>0.81 / 1</b> |

| NOR2 (ns / # of Cycle)          | 34.72 / 1              | 2.1 / 1               | <b>0.81 / 1</b> |

| NOR3 (ns / # of Cycle)          | 69.44 / 2              | 4.2 / 2               | <b>0.81 / 1</b> |

| X(N)OR2 (ns / # of Cycle)       | 34.72 / 1              | 2.1 / 1               | <b>0.81 / 1</b> |

| XOR3 (ns / # of Cycle)          | 69.44 / 2              | 4.2 / 2               | <b>0.81 / 1</b> |

| Majority (ns / # of Cycle)      | n/a                    | n/a                   | <b>0.81 / 1</b> |

| FULL-ADD (ns / # of Cycle)      | 69.44 / 2              | 4.2 / 2               | <b>0.81 / 1</b> |

| FULL-SUB (ns / # of Cycle)      | 69.44 / 2              | 4.2 / 2               | <b>1.62 / 2</b> |

| ADD-RCA (4-bit) (ns # of Cycle) | n/a                    | n/a                   | <b>3.24 / 4</b> |

| ADD-CSA (4-bit) (ns # of Cycle) | n/a                    | n/a                   | <b>4.05 / 5</b> |

| ADD-Serial* (4-bit) (ns)        | 173.6                  | 10.5                  | <b>4.05</b>     |

| SUB-Serial† (4-bit) (ns)        | 312.48                 | 18.9                  | <b>7.29</b>     |

| MULT-Serial‡ (4-bit) (ns)       | 1180.48                | 71.4                  | <b>27.54</b>    |

| MULT-Serial (8-bit) (ns)        | 3541.44                | 214.2                 | <b>82.62</b>    |

of some operations (e.g., ADD/SUB/MULT), they cannot be implemented in a time-efficient manner by the prior designs Zhang *et al.* (2018); Wang *et al.* (2020), while PSRAM outperforms all prior works in latency.

#### 2.4.2 Case study 2: Binary Weight Neural Networks

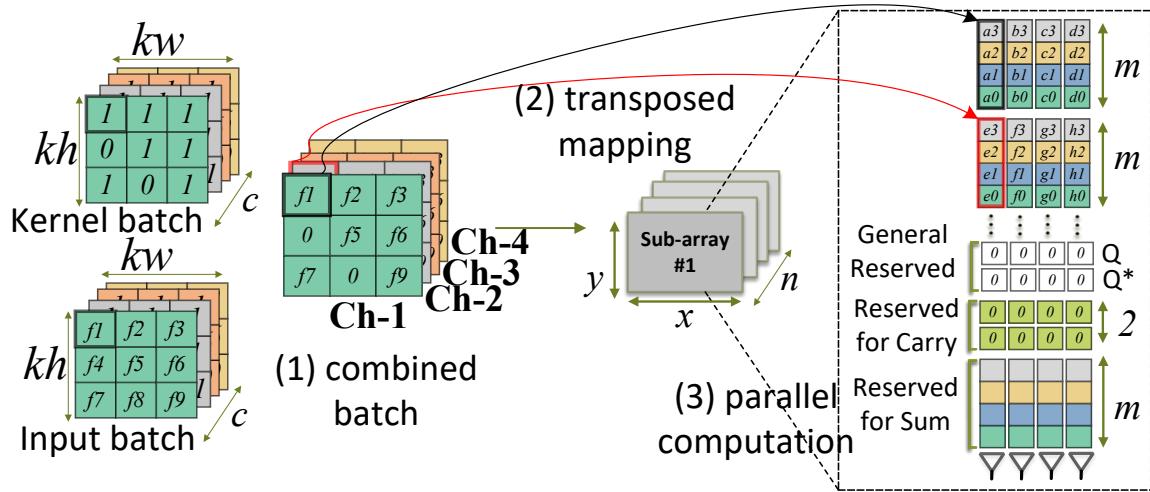

We also implement the binary-weight neural network (BWNN) with various weight configurations for AlexNet and report the energy, latency and other performance in Table 3 and Fig. 7. The general HW/SW framework developed for BWNN consists of image and kernel banks, and PSRAM sub-arrays. Weights and activation are

Figure 6. BWNN Hardware Mapping

Figure 7. (A) PSRAM Energy Consumption and (B) Processing Time for Running the Alexnet (Imagenet Dataset).

Table 3. Comparison with State-of-the-art SRAM Based PIM Accelerators.

| Reference                                         | PSRAM          | BWNN Accelerators       |                         | Generic Accelerators       |                        |

|---------------------------------------------------|----------------|-------------------------|-------------------------|----------------------------|------------------------|

|                                                   |                | A. Biswas et.al. (2018) | H. Valavi et al. (2019) | J. Yue et al. (2020)       | Y. Zhang et al. (2018) |

| Technology                                        | 65nm           | 65nm                    | 65nm                    | 28nm                       | 40nm                   |

| Bit cell Density                                  | 8T             | 10T                     | 8T                      | 8T Transposable            | 10T                    |

| Supply Voltage                                    | 0.8-1.2V       | 0.8-1.2V                | 0.68-1.2V               | 0.6 – 1.1V                 | 0.5-0.9V               |

| Max Frequency                                     | 1230MHz (1.2V) | 5MHz                    | 100MHz                  | 475MHz (1.1V)              | 28.8MHz (0.7V)         |

| SRAM Macro Size                                   | 2KB            | 2KB                     | 4.8KB                   | 16 KB                      | 8KB                    |

| Performance (GOPs)                                | 1259.52        | 8                       | 295                     | 32.7                       | 14.7                   |

| Performance per unit area (GOPs/mm <sup>2</sup> ) | 583.12         | 126                     | 23.4                    | 27.3                       | 70                     |

| Energy-Efficiency (TOPS/W)                        | 34.98          | 40.3                    | 20.6                    | 5.27 (add)<br>0.55 (mult.) | 31.28                  |

| Reconfigurable                                    | Programmable   | N/A                     | N/A                     | Programmable               | N/A                    |

constantly quantized to 1-bit and  $q$ -bit using the same method as Faraone *et al.* (2018), respectively, and then mapped to the parallel PSRAM sub-arrays. The top-1 accuracy after quantization on ImageNet dataset is reported in Fig. 7. For hardware mapping, considering  $n$ -activated PSRAM chips with the size of  $128 \times 128$  (Fig. 6), each sub-array can handle the parallel ADD/SUB (multiply-and-accumulate operations are converted to ADD/SUB in BWNNs) of up to 128 elements of  $m$ -bit ( $2m \leq 128$ ) and so accelerator could process  $n \times 128$  elements simultaneously within computational sub-arrays to maximize the throughput. The memory sub-array data mapping for PSRAM is depicted in Fig. 6. We reserve four rows for Carry results initialized by zero and up to 32 rows for Sum results. Every pair of corresponding elements to be added together is aligned in the same bit-line. Herein, channel 1 (Ch1) and Ch2 should be aligned in the same sub-array. With  $m=32$ -bit, Ch1 elements occupy the first 32 rows of the sub-array followed by Ch2 in the next 32 rows. The addition algorithm starts bit-by-bit from the LSBs of the two words and continues towards MSBs. For evaluation, a 7-layer BWNN is adopted with distinct weight configurations of <W:I>: <1:1>, <1:2>, <1:8>. Our evaluation result reported in Fig. 7 shows that PSRAM

Figure 8. AES Block Diagram with the Gate Utilization

Table 4. 128-bit AES Performance.

| Platforms               | #Cycles | Freq. (MHz) | Time ( $\mu$ S) (Norm.) | Energy (nJ) (Norm.) |

|-------------------------|---------|-------------|-------------------------|---------------------|

| Y. Zhang et al.(2018)   | 6358    | 24          | 265 (1x)                | 64.2 (1x)           |

| M. Hutter et al. (2011) | 5429    | 0.847       | 6410 (24x)              | 10259 (160x)        |

| PSRAM                   | 718     | 1230        | 0.58 (0.002x)           | 19.21(0.3x)         |

can process AlexNet on average with 35 mJ energy per inference and  $\sim 0.5$  ms latency. The process energy and latency include the amount required by multiple PSRAM chips working as a whole entity. More detailed performance comparison with other recent SRAM based PIM designs are reported in Table 3.

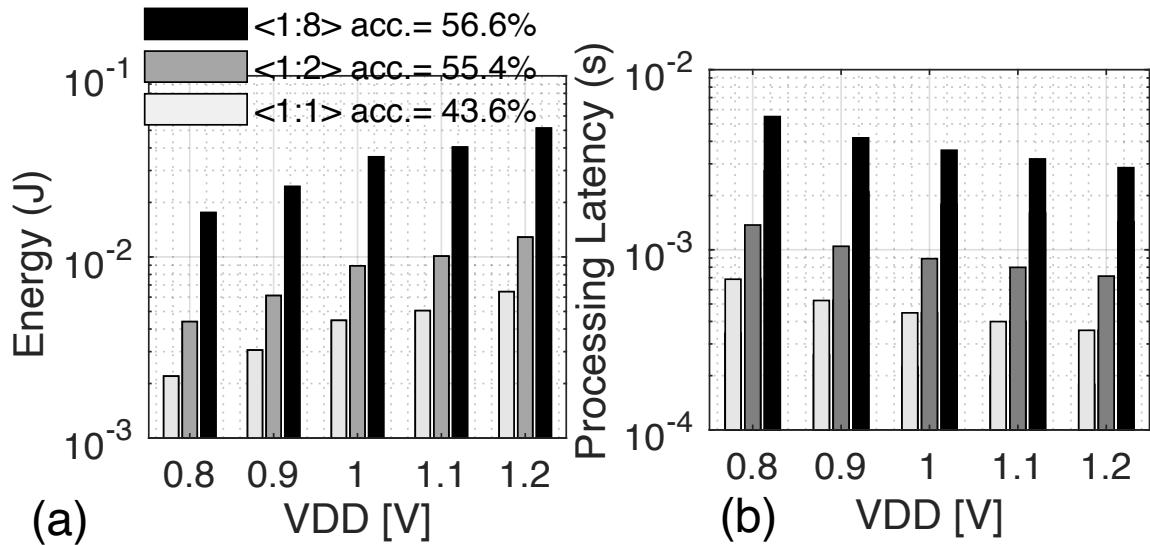

#### 2.4.3 Case study 3: Data Encryption

We further take the Advanced Encryption Standard (AES) data encryption algorithm as the third case-study. To facilitate working with input data (with a standard input length of 128 bits), each input byte data is distributed into 8-bit such that eight PSRAM sub-arrays are filled by  $4 \times 4$  bit-matrices Mathew *et al.* (2010). After mapping, PSRAM supports the required AES bulk bit-wise operations to accelerate

each transformations inside the memory. As shown in Fig. 8, all AES transformations are mainly based on (N)AND and XOR operations that are fully supported in PSRAM. In SubBytes, MixColumns, and AddRoundKey stages, parallel in-memory XOR2 and (N)AND2 operations contribute to more than 90% of the operations. In ShiftRows stage, state matrix will undergo a cyclical shift operation by a certain offset. We use the 128-bit AES software implementation as the baseline from Zhang *et al.* (2018), a 350nm ASIC Hutter *et al.* (2011), and a 40nm ASIC Zhang *et al.* (2018) designs for comparison. Table 4 shows that PSRAM achieves the highest speed-up over baseline. This mainly comes from the massively-parallel and high throughput XOR operation supported in PSRAM.

## 2.5 Conclusion

This chapter introduces a programmable PSRAM chip design in TSMC 65nm CMOS technology. For the first time, the PSRAM could execute a complete set of Boolean logic vector operations (i.e., NOR/NAND/XOR, both 2- and 3-input), majority, and full adder, all in a single memory cycle. The design is taped-out in 65nm CMOS and we demonstrate three case studies leveraging our PSRAM design on the prototype chip, including parallel vector operation, neural networks and data encryption.

## Chapter 3

### PRECISION SCALABLE IN-MEMORY COMPUTING MACRO WITH BIT-PARALLEL INPUTS AND DECOMPOSABLE WEIGHTS

AI is currently the most dominant class of data-intensive applications, with large-dimensional matrix multiplications forming the core of AI computation. As AI models evolve rapidly in size, architecture, and numerical precision, there is a growing demand for adaptable hardware accelerators capable of efficiently handling this diversity. While generic compute approaches—such as those discussed in the previous chapter—offer flexibility, they often suffer from high overhead when executing matrix-matrix operations. This is primarily due to their reliance on multiple bit-serial instructions to complete a single matrix multiplication, resulting in significant latency overhead. A more efficient alternative is the use of SIMD-style instructions, which allow entire matrix multiplications to be executed with minimal cycle count and reduced instruction complexity, making them better suited for high-throughput AI workloads Dally (2023). To address this we present a fully digital multiply and accumulate (MAC) in-memory computing (IMC) macro demonstrating one of the fastest flexible precision integer based MACs to date. The design boasts a new bit-parallel architecture enabled by a 10T bit-cell capable of four AND operations and a decomposed precision data-flow that decreases the number of shift-accumulate operations, bringing down the overall adder hardware cost by 1.57x whilst maintaining 100% utilization for all supported precision. It also employs a carry save adder tree that saves 21% of adder hardware. The 28nm prototype chip achieves a speed-up of

$2.6\times$ ,  $10.8\times$ ,  $2.42\times$ , and  $3.22\times$  over prior SoTA in 1bW:1bI, 1bW:4bI, 4bW:4bI, and 8bW:8bI MACs respectively.

### 3.1 Introduction

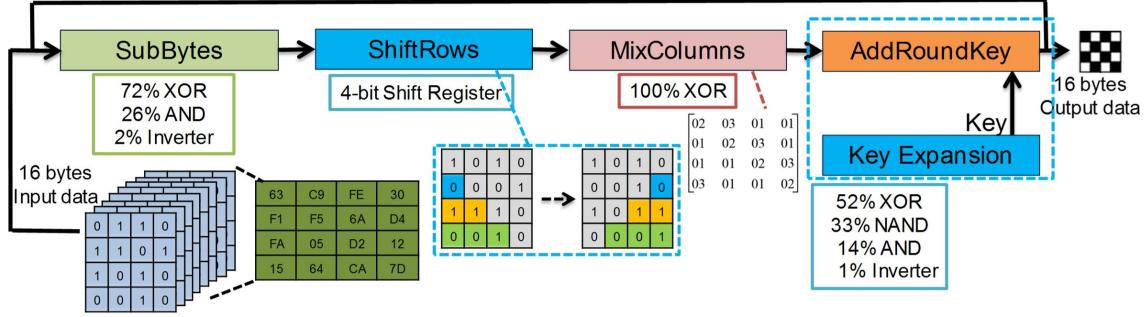

In-memory computing (IMC) has been widely investigated as a promising approach to accelerate AI workloads. There are mainly two prevalent IMC design paradigms, i.e., compute in analog or digital domain. Analog IMC has gained attention due to the large number of operations it can perform per watt as well as per unit area. But it faces significant drawback from computing accuracy standpoint. On the other hand, digital IMCs Fujiwara *et al.* (2022b); Lee *et al.* (2022); Chih *et al.* (2021); Mori *et al.* (2023b); Lin *et al.* (2023) are more akin to digital ASICs closely interleaving memory and logic units. Many recent digital IMC works demonstrate high throughput and energy efficiency compared to their analog counterparts, without any accuracy drop due to robust rail-to-rail logic operations. Convolutions are at the heart of deep learning algorithms and are the most compute intensive operations. They follow a multi-dimensional compute pattern, where the weights and inputs have five dimensions (2D kernel, input channel, output channel, and bit-width).

Typical IMC designs follow a weight stationary approach by storing flattened 5D weights ( $W$ ) in 2D-space. The 2D weight matrix is constructed by assigning output channels and bit-width to IMC rows (enabling parallel multiplications), the kernel dimensions and input channels to IMC columns (enabling parallel accumulations). The 5D-input feature maps (input/IP) are streamed from outside the memory onto the word-lines (WL) performing multiplications within the bit-cell. WLs being a limited resource (1-bit/cycle per WL in most cases), the 5D-input stream-in is time-

Figure 9. Comparison of Conventional Digital IMC Implementations Versus Proposed Throughput Oriented PS-IMC Implementation

multiplexed to just 1D-input/unit time. In this setup, the input bit-width is also unrolled in the time domain, hence a larger number of time-shared shift accumulations circuits are present. The overall system incurs a large latency overhead due to the bit-wise stream-in of inputs (latency overhead = (input precision)  $\times$  (# of inputs)). To maintain high throughput, large weight precision is typically addressed spatially by grouping several memory columns together. This in-turn reduces the flexibility to tune weight precision during inference. With the purpose of improving storage density, recent works Fujiwara *et al.* (2022b); Mori *et al.* (2023b); Oh *et al.* (2023b) attempted to time-share the compute hardware (adders, multipliers, etc.) with more memory cells at the cost of throughput. Considering that convolutions are compute bound, our approach is to maximize the throughput akin to Lee *et al.* (2022). However, Lee *et al.* (2022) requires weight and/or input replication to achieve full utilization for

different precision MACs. Fig. 9 illustrates the PS-IMC design and its advantages over prior works. Implemented in 28nm CMOS, PS-IMC achieves the highest throughput for all supported MAC precision (1/4/8-b Weight (W):1-8b Input (I)), the highest energy efficiency for 1bW:1bI and 1bW:4bI MACs and the highest normalized compute density (TOPS/mm<sup>2</sup>) for 8bW:8bI MACs.

### 3.2 PS-IMC Macro Architecture

Fig. 10 depicts the architecture diagram of the PS-IMC macro. We design the macro using a semi-bit-parallel architecture, i.e., the design is completely bit-parallel up to 4b-input, and a higher input precision will require time multiplexing (4b-input/unit time). There is a pipeline stage between the adder-tree and shifter to evenly distribute the critical path across two cycles. Hence, it takes two clock cycles to complete a MAC with a 4b-input and 4b-weight, three cycles for a MAC with 8b-input with 4b or 8b-weight, and only one clock cycle for a 4b-input and 1b-weight. We implement two  $128 \times 64$  PS-IMC macros on the prototype chip and each  $128 \times 64$  macro has two 64x64 sub-arrays stacked one on top of the other, with the variable shift accumulator (VSA) in the middle. Each column of the PS-IMC sub array has one 64-input 4-bit CSA tree and 64 10T-SRAM bit-cells.

#### 3.2.1 Bit-Cell Design

Fig. 11(A) and Fig. 11(B) show the proposed 10T bit-cell schematic and layout. Each bit-cell occupies  $1.38\mu m^2$  and is designed using logic rules. Each of the four

Figure 10. PS-IMC Macro Architecture Design. (Adapted from Sridharan *et al.* (2024a) with Permission)

additional transistors (T1-T4) perform a pass-gate based dot-product between 4b input streamed in through the input/IP word lines (IWLS) and the 1b weight and its complement stored on either side of the cross-coupled inverters. Each transistor (T1-T4) is allocated to one input bit-significance, and performs a 1bW:1bI dot-product. Thus, each bit-cell as a whole can perform a 1bW:4bI dot-product. Prior to compute, the Partial Product (PP) nets are precharged to VSS and the IWLS are held at VSS

Figure 11. (A) Bit-cell Schematic, (B) Layout, and (C) Truth Table.

until all the weight bits are written into the SRAM bit-cells. This avoids any erroneous compute when the stored bit is zero as the pass gates are controlled by the stored weights. Additionally, PP\_X requires precharge after a large time interval of  $0.5\mu s$ . This is dependent on the RC load on the PP\_X. We determine this precharge interval based on post layout simulations. The functionality of the pass-gate based AND operation is shown in the truth table in Fig. 11(C).

### 3.2.2 Carry Save Adder (CSA) Tree

Fig. 12 compares the precision breakdown of all branches in a binary adder tree (BAT) widely used in prior works Fujiwara *et al.* (2022b); Chih *et al.* (2021); Mori *et al.* (2023b) and a CSA tree of similar configuration used in this work. CSAs have been widely adopted in digital designs requiring multi-operand additions because of the significant reduction in the number of full adders and the speed-up they provide. CSAs isolate each operand into partial sums and carries which are accumulated in

Figure 12. Precision Breakdown and Tree Structures of CSA and BAT

parallel and the bit-precision is accounted for in the tree periphery. This utilizes fewer high-precision adders and thereby results in an overall reduction in the number of full adders, also resulting in a shorter critical path delay. For a 64-operand 4-bit configuration, the CSA requires 21% fewer full adders when compared to the BAT counterpart.

### 3.2.3 Decomposed Weight Precision Data-flow

Prior IMC designs Fujiwara *et al.* (2022b); Chih *et al.* (2021); Mori *et al.* (2023b) spatially encode multi-bit weight precision by grouping memory columns together, limiting weight precision flexibility. Sharma *et al.* (2018) proposes a hierarchical approach to achieve this by decomposing large adder and multiplier precision into smaller blocks that can be selectively tiled together. In this implementation, MACs

are performed in the traditional sense by completing multi-bit multiplication for each operand prior to accumulation. Given that different shift-add hardware is required to support flexible precision, Bit-Fusion trade-offs larger hardware overhead to support flexible precision. Ryu *et al.* (2022) overcomes this hardware cost by allocating a fixed bit-position to an entire PE (capable of small fixed-precision MACs across several operands). The support for flexible precision comes when fusing the PEs together, the partial sum from each PE is subject to a shift operation based on the allocated bit-position. However, this reduction in multiplication hardware comes at the cost of increased accumulation hardware, but given that multiplications are significantly more expensive to perform (a 4-bit multiplication requires 4 ANDs, 3 shifts, 2 4-bit additions and 1 5-b addition), the increase in accumulation hardware is easily off-set by reduced multiplication hardware. The lowest granularity of fixed precision MACs in each PE is 2-bit hence even Ryu *et al.* (2022) incurs a multiplication cost that scales with the number of operands.

With this as motivation, we design PS-IMC using a completely weight decomposed data-flow that un-groups all memory columns. Each memory column is allocated a weight bit-significance (for an  $n$ -b weight, the first column stores the MSB and the  $n^{th}$  column stores the LSB). The 1bW:4bI partial product generated by each bit-cell across all rows are accumulated first. After accumulation, each column is subjected to a shift operation depending on the bit-position. For example, considering a 4b weight, PPs from the MSB column will go through left-shift by 3 ( $<<3$ ) and as we move down the column the shift value decreases by 1 (Fig. 13(B)). By handling weight precision separately, the number of shift-accumulate operations remain constant regardless of the number of operands (Fig. 13(C)). Through this approach, considering a 4-bit precision and 128 operands, the total full-adder (FA) cost (multiplication +

Figure 13. (A) Grouped Weight Precision, (B) PS-IMC’s Decomposed Weight Precision, (C) Multiply and Accumulate Hardware Cost for 4-bit Operands

accumulation) is reduced by  $1.57\times$  and the number of shifts performed can be reduced by  $128\times$ .

### 3.2.4 Variable Shift Accumulator (VSA) for Precision Handling

PS-IMC supports a wide variety of MAC configurations (1b/4b/8b Weight and 1-8b Input). Fig. 14(b) shows the micro-architecture of the VSA. A VSA is padded to every 8 columns to support a maximum of 8b weight precision. Config[1:0] signals in the VSA control the bit-precision of the weights and inputs. The 1bW:4bI MACs

Figure 14. (A) Psum Reduction from Top and Bottom Sub-arrays, (B) Variable Shift Accumulator Micro-architecture, (C) Timing Diagram with the Total Number of Macs Performed in a Single PS-IMC Macro

are collected in the pipeline stage before VSA in the same cycle as the input stream in. These MACs are then gated by Config[0], which enables column-specific shifts ( $<<3$  for the 1<sup>st</sup> column and no shift for the last column) to obtain 4bW:4bI MACs. Every 8 columns generate two 4bW:4bI MACs of 14-bit precision and these MAC outputs are further gated by Config[1] to selectively shift accumulate one of the 4bW:4bI MAC output to obtain a larger 8bW:4bI MAC of 18-bit precision. An alternative approach to implement a large weight precision ( $>4b$ ) would be to subject each column to a variable shift (7b through 4b), but in this case, the un-selected shifters remain idle and each IMC column incurs a multiplexer overhead as opposed to only one de-multiplexer for every 4 IMC columns. Due to the bit-parallel nature of the 10T bit-cell, input precision of up to 4b can be handled in a single cycle without any time-multiplexing or special control. Only for input precision above 4b, multiplications are time-shared through shift-accumulators (Fig. 14(b)). The VSA is tailored to support input precision ranging from 1-nb for a n-bit W. As a result, the a

Figure 15. Throughput (TOPS) vs. Energy-efficiency (TOPS/W) for (a) 1bW:1/4bI, (B) 4bW:1/4bI, and (C) 8bW:1/4/8bI Modes. (D) Power and Frequency Scaling

time-shared shift-accumulator is only necessary once every  $n$  columns. This reduces the shift-accumulators/column since input precision is accounted with little (4b-8b) to no (1b-4b) time-multiplexing. PS-IMC macro has three pipeline stages. The first, second and third pipeline stages generate 64 4bI:1bW MACs, 16 4bI:4bW MACs and 8 8bI:8bW MACs respectively, as illustrated in Fig. 14(c) and (d).

Figure 16. Die Micrograph (Left), and Area Breakdown (Right)

### 3.3 Chip Measurement Results

PS-IMC is prototyped in TSMC 28nm CMOS. We implement two  $128 \times 64$  macros on the prototype chip, where each macro occupies  $0.32mm^2$ . The PS-IMC macro achieves the highest peak throughput/kb compared to all prior digital IMC works for 1bW:1-4bI (3.25 TOPS/Kb @ 1.2V), 4bW:1-4bI (406.3 GOPS/Kb @ 1.2V) and 8bW:4-8bI (135.4 GOPS/Kb @ 1.2V). It also achieves the highest energy efficiency for 1bW:4bI (1843 TOPS/W @ 0.56V) and 1bW:1bI (2385.7 TOPS/W @ 0.56V). The measurement condition is with 50% bit-wise weight sparsity and an average of 25% toggle rate for the inputs at 27°C. Input toggle rate has a linear dependence on power, where 25% decrease in toggling rate will yield about 8.7-13% increase in energy efficiency. For a lower input precision (<4b), we disable the IWLs depending on the precision (a 2bI would mean we disable IWL\_3 and IWL\_2). A 1bW:1bI MAC in PS-IMC achieves the same throughput as a 1bW:4bI, but due to the reduction in the number of active IWLs 1bW:1bI achieves a higher energy efficiency. Fig. 15(a), Fig.

Table 5. Comparison with Prior Digital IMC Works

| Reference                                     | This Work     | C.-F. Lee et. al. 2022 | Y.-D. Chih et al. 2021 | H.Fujiwara et al. 2022 | J. Oh et al 2023 | C.-T. Lin et al., 2023 | H. Mori et al. 2023 |

|-----------------------------------------------|---------------|------------------------|------------------------|------------------------|------------------|------------------------|---------------------|

| <b>Technology</b>                             | 28nm          | 12nm                   | 22nm                   | 5nm                    | 28nm             | 28nm                   | 4nm                 |

| <b>Bit cell Density</b>                       | 6T+4T (4xAND) | -                      | 6T+4T (1xAND)          | 12T+1T                 | 6T+2T (XNOR)     | 6T+0.5T                | 8Tx2bit+ OAI        |

| <b>Array Size</b>                             | 8Kb/Macro     | 8Kb                    | 64Kb                   | 64Kb                   | 16Kb             | 16Kb                   | 54Kb                |

| <b>Macro area (mm<sup>2</sup>)</b>            | 0.32/Macro    | 0.0323                 | 0.202                  | 0.0133                 | 0.033, 0.049     | 0.0159                 | 0.0172              |

| <b>Supply(V)</b>                              | 0.54-1.2      | 0.72                   | 0.72                   | 0.5-0.9                | 0.45-1.1         | 0.6-1.1                | 0.32-1.1            |

| <b>Input Precision</b>                        | 1b-8b         | 4b-8b                  | 1b-8b                  | 4b                     | 1b-4b            | 1-8b                   | 8b/12b/16b          |

| <b>Weight Precision</b>                       | 1b/4b/8b      | 4b/8b                  | 4b/8b/12b/16b          | 4b                     | 1b               | 8b                     | 8b/12b              |