# Zero-Power Feed-Forward Spur Cancelation for Supply-Regulated CMOS Ring PLLs

Pawan Agarwal<sup>®</sup>, *Student Member, IEEE*, Jong-Hoon Kim, Partha Pratim Pande<sup>®</sup>, and Deukhyoun Heo<sup>®</sup>, *Senior Member, IEEE*

Abstract—A new reference-spur cancelation technique is presented for supply-regulated ring-oscillator-based integer-N phaselocked loops (PLLs). A passive RC filter is used to implement a feed-forward (FF) spur-coupling path to perform spur cancelation at the PLL control signal. The proposed technique achieves a simulated spur cancelation of about 22 dB at the first spur harmonic. The simulated postcancelation spur value is -79 dBc for an oscillator gain of 0.1 GHz/V and -46 dBc for an oscillator gain of 6 GHz/V. Spur cancelation is also robust against large process, voltage, and temperature variations in the gain and bandwidth of the FF path. A 1-GHz integer-N PLL prototype in a 65-nm CMOS process has a measured cancelation of 19.5 and 13 dB at the first and the second spur harmonic, respectively, with 320  $\mu$ W of total power consumption. The PLL prototype has an oscillator gain of 1.5 GHz/V, which results in a postcancelation spur of -53 dBc. The proposed zeropower technique is suitable for low-power PLLs as it achieves a large spur cancelation without requiring any additional power consumption or calibration.

*Index Terms*—Band-reject filter, low power, low-dropout regulator (LDO), phase-locked loop (PLL), reference-spur cancelation.

#### I. INTRODUCTION

ORE than 20 billion low-cost consumer devices are envisioned to have low data-rate wireless connectivity by 2020 [1] for monitoring, diagnostics, and corrections [2], i.e., a global expansion of the Internet of Things. The subgigahertz bands in the industrial, scientific, and medical category (e.g., 915 MHz in USA and 920 MHz in Japan) are an attractive choice for these low-rate applications using lowpower communication standards, such as IEEE 802.15.4 [3].

Manuscript received May 8, 2017; revised August 13, 2017 and November 11, 2017; accepted December 10, 2017. Date of publication January 17, 2018; date of current version March 20, 2018. This work was supported in part by the U.S. National Science Foundation under Grant CNS-1705026 and Grant CNS-1564014, in part by the NSF Center for Design of Analog-Digital Integrated Circuits, in part by the Korea Food Research Institute through the Technology Development Program, and in part by the Natural Sciences and Engineering Research Council of Canada. (*Corresponding author: Deukhyoun Heo.*)

P. Agarwal was with the School of Electrical Engineering and Computer Science, Washington State University, Pullman, WA 99163 USA. He is now with Maxlinear, Inc., Carlsbad, CA 92008 USA.

J.-H. Kim is with the Research Group of Smart Distribution System, Korean Food Research Institution, Sungnam 463-764, South Korea.

P. P. Pande and D. Heo are with the School of Electrical Engineering and Computer Science, Washington State University, Pullman, WA 99163 USA (e-mail: dheo@eecs.wsu.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TVLSI.2017.2788882

Phase-locked loops (PLLs) are used to synthesize the local oscillator (LO) signal in synchronized wireless transceivers for the up/down conversion of the modulated data. The spectral purity of a PLL output is quantified as the relative strength of the phase noise (PN) and the spurious tones (spurs) compared to the LO signal. The reference spurs degrade signal-to-noise ratio in wireless systems by down-converting interference over the desired signal band through reciprocal mixing. The reference spurs also increase PLL's output jitter (i.e., integrated noise).

Normally, the PLL bandwidth (BW) and the frequency tuning range (i.e., oscillator gain) are chosen according to the system requirements. For given PLL design parameters, the PLL PN can be reduced by increasing power consumption. For example, with a fixed PLL BW and oscillator gain, increasing oscillator power consumption reduces PLL's out-of-band PN, while increasing the charge-pump (CP) current may reduce the PLL's in-band PN [4]. However, the reference spurs are a strong function of the PLL BW and oscillator gain. Hence, the reference spurs may not reduce with a simple scaling of PLL power consumption. This has encouraged numerous methods for reducing the spurs [5]–[15].

We propose a feed-forward (FF) spur cancelation technique to minimize the reference spurs in supply-regulated ring PLLs. A high-frequency spur-coupling path is introduced within the PLL using a passive *RC* filter, which provides the replica spur signal for spur cancelation. The reference spurs are canceled just before they induce frequency modulation in the ring oscillator (RO). Consequently, the effect of several spur-causing PLL nonidealities is suppressed simultaneously. A large and robust reference spur cancelation is achieved over a wide range of spur values and various PLL design parameters. The proposed technique does not require any power consumption or complex calibration which makes it suitable for low-power PLL designs.

This paper is organized as follows. A brief introduction on PLL architecture, reference spurs in integer-N PLLs, and prior art is given in Section II. The proposed technique, its performance, and scalability are presented in Section III. The impact of the spur-coupling path on PLL stability and PN is analyzed in Section IV. The PLL design details are provided in Section V. Measurement results are shown in Section VI and the conclusions are summarized in Section VII.

1063-8210 © 2018 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

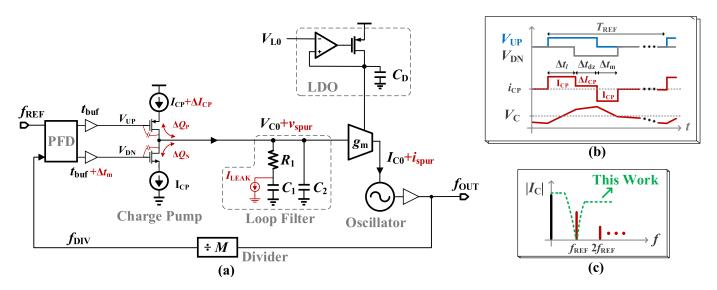

Fig. 1. (a) Integer-N PLL block diagram (key nonidealities that cause reference spurs are highlighted). (b) Time-domain waveforms at the PFD, charge-pump, and the loop-filter outputs. (c) Oscillator's frequency control current  $(I_C)$  in the frequency domain.

#### **II. REFERENCE SPURS IN INTEGER-N PLLS**

# A. Supply-Regulated Ring PLL Architecture

A block diagram of a conventional integer-N PLL is shown in Fig. 1(a). With the very large-scale integration of digital and analog circuits on a common silicon substrate, the resulting large supply noise degrades the PLL PN [16]. The frequency modulation of supply noise by the RO is most detrimental to PLL noise performance, as ROs have a large oscillator gain due to their highly nonlinear frequency tuning characteristics. Furthermore, the control-voltage ( $V_C$ ) range in a PLL operating from 1-V supply is usually limited from 0.3 to 0.7 V, to ensure that CP current sources operate in a deep saturation region. A smaller  $V_C$  range requires a higher oscillator gain to maintain the same frequency tuning range.

An RO's supply-noise immunity is improved by using a dedicated low-dropout regulator (LDO) [17]. The LDO can be used either within the PLL's negative-feedback loop by using a supply-voltage-tuned RO [18] or outside the loop by using a gate-voltage-tuned RO [19]. The LO buffers are used to provide a rail-to-rail voltage swing for the feedback divider, and to isolate the RO from variable output loading conditions. To maintain a constant swing at the PLL output, a supply-voltage-tuned RO requires an increasingly larger buffer gain with a decreasing supply voltage. Hence, the gate-voltage-tuned RO is used for lower power implementation, as shown in Fig. 1(a).

#### B. Reference Spurs: Cause and Strength

PLL operation in the lock state is described as follows. The phase-frequency detector (PFD) samples the input phase difference ( $\Delta \Phi_{IN}$ ) between the reference ( $f_{REF}$ ) and the feedback ( $f_{DIV}$ ) signals with a  $T_{REF}$  period. The CP then converts  $\Delta \Phi_{IN}$  into an equivalent charge injected in or withdrawn from the loop filter (LF). The key PLL nonidealities causing a periodic high-frequency spurious signal ( $v_{spur}$ ) at the control voltage  $V_C$  are highlighted in Fig. 1(a), and briefly summarized as follows.

- 1) The timing mismatch  $(\Delta t_m)$  between the  $V_{\rm UP}$  and the  $V_{\rm DN}$  signal paths due to mismatches in the capacitive loading and during the single ended to differential conversion in the PFD.

- 2) The periodic charge sharing/injection into the LF by the CP switches during the ON/OFF transitions.

- The signal feed through, i.e., capacitive coupling of the PFD's digital output signal to the LF through the gate-drain capacitance of the CP switches.

- 4) The minimum required pulsewidth  $(\Delta t_{dz})$  for  $V_{\text{UP}}$  and  $V_{\text{DN}}$  signals for a complete steering of the CP currents to avoid the switching dead zone. The CP's UP and DN current mismatch  $(\Delta I_{\text{CP}})$  is injected into the LF for  $\Delta t_{dz}$  duration.

- 5) The LF capacitor ( $C_1$ ) leakage current ( $I_{\text{LEAK}}$ ) decreases  $V_C$ , which is compensated by injecting  $I_{\text{CP}}$  into the LF for an additional  $\Delta t_l$  duration. For example, an  $I_{\text{LEAK}}$  of 0.5  $\mu$ A discharges  $C_1$  of 150 pF by 0.35 mV in (a  $T_{\text{REF}}$  of) 100 ns.

The time-domain signal waveforms for the PFD, the CP, and the LF are depicted in Fig. 1(b), ignoring charge injection and signal feed through. The periodic disturbances at  $V_C$  are filtered by the loop. The resulting control current ( $I_C$ ) at the output of the transconductance ( $g_m$ ) is shown in Fig. 1(c) in the frequency domain. The spur components in  $I_C$  are frequency modulated to PLL output by the oscillator as reference spurs.

Using the narrowband frequency-modulation approximation, the output spur strength  $(A_{spur})$  of the first reference harmonic at  $f_{REF}$  relative to the PLL output  $(A_{out})$  is given as

$$\frac{A_{\text{spur}}}{A_{\text{out}}}\Big|_{@f_{\text{REF}}} = \frac{g_m K_C}{2f_{\text{REF}}} v_{\text{spur}}\Big|_{@f_{\text{REF}}}$$

$$\approx \frac{g_m K_C}{2f_{\text{REF}}} \frac{f_2}{f_{\text{REF}}} R_1 i_{\text{CP}}\Big|_{@f_{\text{REF}}} \tag{1}$$

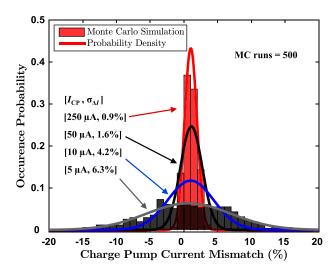

Fig. 2. Monte Carlo simulation results for the CP current mismatch for 500 runs. The histogram is shown for an  $I_{CP}$  of 5 and 250  $\mu$ A.

where  $i_{CP}$  is the current injected by the CP into the LF. The  $K_C$  is the oscillator gain (Hz/A), which results in a net oscillator gain of  $g_m K_C$  (Hz/V). The zero and pole by the second-order LF are  $\omega_1$  (=  $1/C_1R_1$ ) and  $\omega_2$  (=  $1/C_2R_1$ ), respectively. Equation (1) shows that for a given PLL BW and  $f_2$ , the spur value scales in proportion to the oscillator gain. For example, approximating  $v_{spur}$  as a saw-tooth waveform of 0.5-mV amplitude, with  $f_{REF}$  of 10 MHz, a  $g_m K_C$ of 1.5, and 0.1 GHz/V results in a spur of -35 and -58.5 dBc, respectively.

The PLL power consumption can be lowered by reducing the power consumption of the oscillator, CP, and its bias circuit. The oscillator gain may not necessarily change with its power consumption. The PLL's open-loop gain transfer function (TF),  $G_{OL}(s)$ , is

$$G_{\rm OL}(s) = \frac{I_{\rm CP}}{2\pi} \frac{\left(1 + \frac{s}{\omega_1}\right)}{sC_1\left(1 + \frac{s}{\omega_2}\right)} \frac{g_m K_C}{s} \frac{1}{M}$$

(2)

where the feedback division ratio is M, and  $I_{CP}/2\pi$  (A/rad) is the combined gain of the PFD and the CP. A lower  $I_{CP}$ requires a proportionally smaller LF capacitor  $C_1$ .<sup>1</sup> A smaller  $C_1$  requires a proportionally larger LF resistor  $R_1$  to maintain  $\omega_1$ , i.e., the PLL BW and PM.

The histogram for the mismatch between the CP's UP and DN currents is shown in Fig. 2. For simplicity, the MOSFET gate bias and gate length are kept fixed while the device width is scaled to scale the CP current. The standard deviation  $(\sigma_{\Delta I})$  of the percentage current mismatch increases with a decrease in the CP current as the MOSFET device area is reduced [21]. Overall, reducing the CP current increases the ripple  $i_{CP}R_1$  on the control voltage due to a proportionally larger  $R_1$  and a higher current mismatch. For example, an  $I_{CP}$  of 10  $\mu$ A with  $3\sigma_{\Delta I}$  mismatch between UP and DN currents results in a calculated spur value of -32.3 dBc (1) [22], using  $R_1$  of 14 k $\Omega$ ,  $g_m K_c$  of 1.5 GHz/V,  $\Delta t_{dz}$  of 400 ps, and  $f_2$  of 22.7 MHz.

<sup>1</sup>Note that the CP bias-circuit power consumption also scales with  $I_{CP}$  for a fixed percentage contribution by the bias-circuit noise to the total CP noise.

Similarly, designing a lower power PFD requires smaller device sizes. The smaller PFD device sizes may result in a larger mismatch between the UP and DN signal paths, which increases the timing mismatch  $\Delta t_m$ . A larger  $\Delta t_m$  results in higher reference spur. Therefore, low-power ring PLLs with large oscillator gain are inherently prone to large spurs.

#### C. Prior Art of Spur Reduction

The reference spur can be suppressed by simply using a smaller PLL BW, which results in a higher noise contribution from the RO and a longer settling time. Subblock level spurcause mitigation techniques, such as the PFD calibration [5], minimization of the  $\Delta I_{CP}$  [6], [15], the charge injection [20], and the  $I_{LEAK}$  [8], [9], have been proposed to reduce spurs.

A holistic approach can minimize the cumulative effect of multiple PLL nonidealities simultaneously. The PLL corrects the input phase difference at each rising/falling reference edges. The spur periodicity is broken by randomizing the correction time instant using pulse position modulation [12] or random clock generator [21], which spreads the spur as broadband noise. If the period at which the loop corrects the error is reduced from  $T_{\text{REF}}$ , the (now) higher frequency spurs experience higher filtering by the loop. The period is decreased by eight times using edge interpolators in [7] which suppresses the fundamental spur by 16 dB, but requires 5.8 mW for only the edge interpolators.

As shown in Fig. 1(c), use of a band-reject filter at the oscillator control signal reduces the spurs. A power-hungry digital filter is realized in [11] by adding a digital correction signal (ideally equal to  $-v_{spur}$ ) to  $V_C$ , which achieves on average 13.3 dB of spur suppression. A direct down-conversion receiver is used for an analog cancelation in [10], which achieves 12.5 dB of noise and spur reduction while consuming an additional 4.5 mW. In [14], an active-*L*-based *LC*-filter is used at the control node to shunt the spurs to the ground, which reduces the spur by 18 dB after calibration and consumes 250  $\mu$ W. In comparison, the proposed method employs a passive *RC* filter to achieve 19.5 dB of measured spur cancelation without any additional power consumption or calibration.

#### III. FEED-FORWARD SPUR CANCELATION TECHNIQUE

# A. Proposed Concept

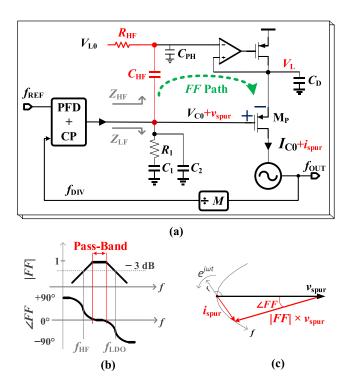

The PLL block diagram with the proposed FF uses a passive high-pass filter  $H_{\rm HF}(s)$  to couple the high-spur-coupling path is shown in Fig. 3(a). The proposed design frequency spur signals to the LDO input. The spur signal then travels to the RO's supply node ( $V_L$ ) with an additional low-pass filtering by the LDO closed-loop TF  $H_{\rm LDO}(s)$ . Consequently, the FF path TF FF(s) has a bandpass frequency response. The FF(s) is depicted in the bode-plot diagram of Fig. 3(b), with  $f_{\rm LDO}$ as the closed-loop 3-dB BW of the LDO.

The MOSFET drain current in saturation region is a function of the difference of its gate and source voltages  $(V_G - V_S)$ . Hence, the  $M_P$ 's  $V_{GS}$  is the effective control voltage for the RO. The LDO output voltage  $V_L$  is given as

$$V_L = V_{L0} + FF(s)v_{\rm spur} \tag{3}$$

Fig. 3. (a) Proposed PLL architecture with the FF path. (b) Bode plot of the FF TF, FF(s). (c) Phasor diagram representation of the FF reference-spur cancelation by the  $M_P$ .

where  $V_{L0}$  is LDO's input reference voltage. The  $M_P$ 's drain current (i.e., oscillator control current)  $I_C$  is given as

$$I_{C} = (V_{L0} - V_{C0}) - (1 - FF(s))g_{m}v_{spur}$$

=  $I_{C0} - R(s)g_{m}v_{spur}.$  (4)

The high-frequency spur components  $(i_{spur})$  of  $I_C$  that fall within the FF(s) passband are filtered by an equivalent bandreject filter R(s) due to the  $V_{GS}$  cancelation by the  $M_P$ . The spur cancelation phasor diagram is shown in Fig. 3(c). The highest spur cancelation is achieved at the R(s) center frequency  $f_R$ , where ideally the FF(s) magnitude (|FF|) is 1 and phase shift ( $\angle$ FF) is 0°. With a wideband FF path and finite gain roll-off of the FF(s), the higher spur harmonics are also feed-forwarded and canceled by the  $M_P$ .

#### B. Feed-Forward Design and Implementation

The FF path TF FF(s) is given as

$$FF(s) = H_{HF}(s)H_{LDO}(s)$$

(5)

$$H_{\rm HF}(s) = \frac{s}{\omega_{\rm HF}} \frac{\beta}{\left(1 + \frac{s}{\omega_{\rm HF}}\right)} \tag{6}$$

$$H_{\rm LDO}(s) = \frac{H_L(s)}{1 + H_L(s)} \tag{7}$$

where  $\beta = C_{\rm HF}/(C_{\rm HF} + C_{\rm PHF})$ ,  $\omega_{\rm HF} = 1/(C_{\rm HF}R_{\rm HF})$ , and  $H_L(s)$  is the LDO open-loop TF. The *FF* path impedance  $Z_{\rm HF}$  introduces a pole–zero pair in the effective loop-filter impedance  $Z_{\rm ELF}$  (=  $Z_{\rm HF}||Z_{\rm LF}$ ), which affects the PLL phase margin (PM). Here,  $Z_{\rm LF}$  is the second-order LF impedance as shown in Fig. 3(a). The BW of  $H_{\rm HF}(s)$  should be much

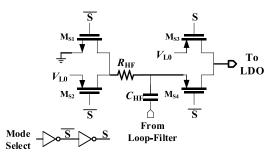

Fig. 4. Schematic of the switch network used for controlling the FF path between ON and OFF modes, only for comparing PLL performance.

higher than the PLL BW to avoid a considerable degradation of the PLL PM. The optimum  $f_{\rm HF}$  is calculated by solving for  $\angle FF(j\omega_R) = 0^\circ$  (i.e., maximum spur cancelation at  $f_R$ ), which results in

$$f_R^2 = f_{\rm HF} f_{\rm LDO}.$$

(8)

For an  $f_{\text{LDO}}$  of 70 MHz in this paper,  $f_{\text{HF}}$  is chosen as 1.5 MHz for an  $f_R$  of 10 MHz (=  $f_{\text{REF}}$ ).

A switch (SW) network is used to switch the FF path between the ON mode and the OFF mode, only for comparative measurement capability. The switch network schematic is shown in Fig. 4. The resistance  $R_{\rm HF}$  is grounded in the OFF mode, for an equal loop-filter impedance in both ON and OFF modes. The channel resistance of  $M_{S1-2}$  is included in  $R_{\rm HF}$ , and the parasitic capacitance due to  $M_{S3-4}$  is included in  $C_{\rm PHF}$ as shown in Fig. 3(a). Hereafter, the PLL shown in Fig. 3(a) is referred to as the conventional PLL (Conv PLL) with the FF path OFF and as the FF PLL with the FF path ON.

## C. Spur Cancelation Performance and Scalability

The PLL shown in Fig. 3(a) is designed using a 65-nm CMOS process with an  $f_{\text{REF}}$  of 10 MHz. The PLL is simulated using transistor-level circuits for a range of  $g_m K_C$  values to ascertain the performance of proposed spur cancelation technique. The RO is implemented using VerilogA only for these simulations. PLL design details are provided in Section V. The  $I_{\text{CP}}$  in (2) is scaled in inverse proportion to  $g_m K_C$  to maintain PLL characteristics during comparisons.

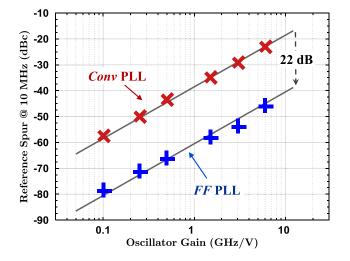

The simulated first reference-spur harmonic strength (in dBc) is shown in Fig. 5. An oscillator gain of 1.5 and 0.1 GHz/V results in a reference spur of -35 and -57.5 dBc, respectively, in the Conv PLL. The spur strength scales with the oscillator gain for a fixed PLL BW, as shown in (1). The FF PLL achieves a spur of -79 dBc for an oscillator gain of 0.1 GHz/V. The fundamental spur harmonic is canceled by an average of 22 dB using the proposed technique across the precancelation spur values of -23 to -57.5 dBc.

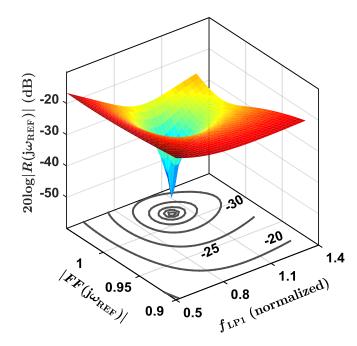

The FF(s) design parameters, such as gain and frequency response, may vary with process, voltage, and temperature (PVT) variations and thus affect the spur cancelation performance. The proposed band-reject filter's magnitude at  $f_{\text{REF}}$ ( $|R(j\omega_{\text{REF}})|$ ) is shown in Fig. 6 against PVT variations in the FF path gain ( $|\text{FF}(j\omega_{\text{REF}})|$ ) and LDO's dominant

Fig. 5. Spur strength in a PLL using transistor-level circuit simulations. Only the ring oscillator is implemented using VerilogA. The  $f_{OUT}$  is 1 GHz, and  $f_{REF}$  is 10 MHz. The proposed method achieves a spur cancelation of 22 dB.

Fig. 6. Calculated R(s) magnitude at  $f_{\text{REF}}$  against PVT-induced variations in the gain of FF(s). The  $f_{\text{OUT}}$  is 1 GHz,  $f_{\text{REF}}$  is 10 MHz, and  $g_m K_C$  is 1.5 GHz/V.

open-loop pole  $f_{\text{LP1}}$ .<sup>2</sup> In practice,  $\angle \text{FF}(j\omega_{\text{REF}})$  is not equal to 0° due to higher order parasitic poles and zeros. Consequently, the theoretical maximum spur cancelation is 55 dB at an  $|\text{FF}(j\omega_{\text{REF}})|$  of 1.015. Moreover,  $|\text{FF}(j\omega_{\text{REF}})|$  is less than 1 due to a finite LDO open-loop gain, and passive implementation of the  $H_{\text{HF}}(s)$  which causes a  $\beta$  of less than 1, as shown in (6). The simulated  $|\text{FF}(j\omega_{\text{REF}})|$  is 0.95 in this paper, which results in a spur cancelation of 24 dB for an optimum  $f_{\text{LP1}}$ . As shown in Fig. 6, the proposed technique achieves a robust spur cancelation of more than 20 dB against 16% variation in  $|\text{FF}(j\omega_{\text{REF}})|$  and 30% variation in  $f_{\text{LP1}}$ .

<sup>2</sup>The effect of  $f_{\rm HF}$  on R(s) is similar to that of the  $f_{\rm LP1}$  (i.e.,  $f_{\rm LDO}$ ). However, due to passive implementation,  $f_{\rm HF}$  is much less sensitive to variations compared to the LDO frequency response.

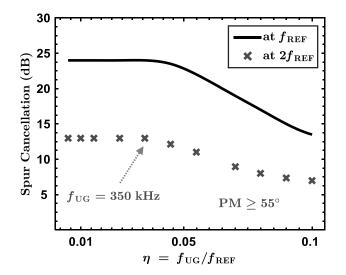

Fig. 7. Calculated spur cancelation against PLL BW with a minimum FF PLL PM of 55°. The  $f_{OUT}$  is 1 GHz,  $f_{REF}$  is 10 MHz, and  $g_m K_C$  is 1.5 GHz/V.

The spur cancelation is also simulated against PLL BWs to investigate the applicability of the proposed method to the PLLs designed for different applications.<sup>3</sup> A minimum FF PLL PM of 55° is maintained during these simulations. The  $f_{\rm HF}$  is kept as 1.5 MHz for  $f_{\rm UG}/f_{\rm REF}$  ( $\eta$ )  $\leq$  0.05, since the resulting PLL PM is greater than 55°. The  $f_{\rm HF}$  is increased for  $\eta > 0.05$  values to maintain the PM. As shown in Fig. 7, a spur cancelation of 24 and 13 dB is achieved at  $f_{\rm REF}$  and  $2f_{\rm REF}$ , respectively, for  $\eta \leq 0.05$ . The  $f_R$  increases with  $f_{\rm HF}$ , as shown in (8), which reduces spur cancelation for  $\eta > 0.05$  values. A minimum cancelation of 13 dB is achieved at  $f_{\rm REF}$  for a maximum  $\eta$  of 0.1. An optimized PLL design can increase spur cancelation for large values of  $\eta$ .

#### IV. PLL ANALYSIS AND DESIGN

#### A. Loop Stability

FF PLL open-loop gain TF  $G_{OLFF}(s)$  and the  $Z_{ELF}$  are given as

$$G_{\text{OLFF}}(s) = \frac{I_{\text{CP}}}{2\pi} Z_{\text{ELF}} R(s) \frac{g_m K_C}{s} \frac{1}{M}$$

(9)

$$Z_{\text{ELF}} = Z_{LF} ||Z_{\text{HF}}|$$

$$= \frac{\left(1 + \frac{s}{\omega_1}\right)}{s(C_1 + C_{\rm HF})\left(1 + \frac{s}{\omega_2}\right)} \frac{\left(1 + \frac{s}{\omega_{\rm HF}}\right)}{\left(1 + \frac{s}{\omega_T}\right)} \quad (10)$$

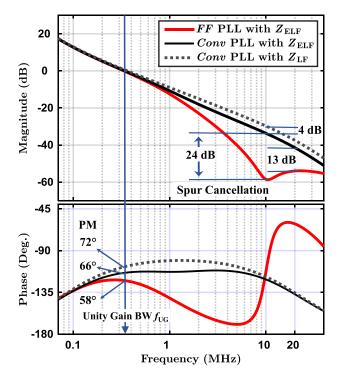

where  $\omega_T = 1/[(C_{\rm HF}||C_1)(R_{\rm HF} + R_1)]$ . The calculated pole and zero values are:  $f_1 = 76$  kHz,  $f_2 = 22$  MHz,  $f_{\rm HF} =$ 1.5 MHz, and  $f_T = 0.96$  MHz. The bode plots of the PLL open-loop gain are shown in Fig. 8 for the FF PLL, the Conv PLL with  $Z_{\rm ELF}$  as the loop-filter impedance (i.e., FF path in OFF mode), and the Conv PLL with  $Z_{\rm LF}$  as the loop-filter impedance [as shown in Fig. 1(a)]. With FF path in ON mode, the fundamental and the second spur harmonics are canceled by 24 and 13 dB, respectively, compared to when the FF

<sup>3</sup>For PLLs using a variable reference frequency, the  $H_{\rm HF}(s)$  can be reconfigured (for example, by implementing  $C_{\rm HF}$  using a capacitor bank) to realign the R(s) center frequency  $f_R$  with that of the reference frequency (8). Then, spur cancelation is determined by the ratio  $\eta$ , as shown in Fig. 7.

Fig. 8. Bode plots of the PLL open-loop gain TF for the FF PLL, the Conv PLL with  $Z_{ELF}$ , and the Conv PLL with  $Z_{LF}$ .

path is in OFF mode.<sup>4</sup> The PLL unity-gain frequency ( $f_{UG}$ ) is about 350 kHz for all three cases. The Conv PLL PM is 72° with  $Z_{LF}$ , which reduces to 66° with  $Z_{ELF}$ . With an equal LF impedance  $Z_{ELF}$ , the PLL PM reduces by 8° due to R(s) when FF path is ON compared to when FF path is OFF.<sup>5</sup>

# B. Design Details

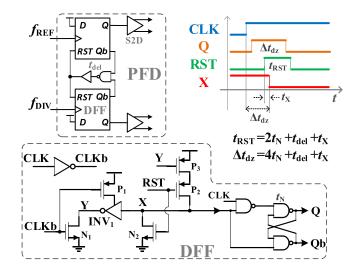

A D flip-flop (DFF)-based tri-state PFD is used. The schematics of the PFD and the DFF with reset are shown in Fig. 9. The operation of the DFF is as follows. With clock (CLK) and reset (RST) signal as 0, the X and Y nodes are precharged to 1 and 0, respectively. Transistor  $P_1$  disables inverter 1 (INV<sub>1</sub>). With CLK = 1, the arrival of PFD's RST signal enables the  $N_2$  to discharge the node X to 0, which charges the node Y to 1 through the INV<sub>1</sub>. Setting Y = 1 SWs OFF P<sub>3</sub>, thus holding X at 0 utill the CLK falling edge precharges Y to 0 through  $N_1$ . Assuming a zero phase difference at the PFD input, the timing diagram for the DFF is shown in Fig. 9.

A cascode current-mirror-based CP is used with an  $I_{CP}$  of 10  $\mu$ A. A current-mirror ratio of 4:1 is used in the CP to suppress the bias noise contribution by 16 times. The bias circuit is shared by the CP and the LDO. The loop-filter values

Fig. 9. PFD schematic and the timing diagram of the edge-triggered DFF with reset pulse generator.

Fig. 10. LDO schematic using Miller compensation for stability.

Fig. 11. LDO TFs using transistor-level circuit simulations.

are  $C_1 = 150$  pF,  $R_1 = 14$  k $\Omega$ ,  $C_2 = 0.5$  pF,  $R_{\rm HF} = 24$  k $\Omega$ , and  $C_{\rm HF} = 4.5$  pF. The RO is composed of three-stage currentstarved single-ended inverters. The  $M_P$ 's bulk and source

<sup>&</sup>lt;sup>4</sup>Reference spurs can also be reduced by using a third-order LF [15]. The additional LF pole  $f_P$  increases spur filtering by the loop at the cost of a lower PLL PM. For example, an additional pole  $f_P$  of 1.4 MHz reduces the PLL PM by  $\tan^{-1}(f_{\text{UG}}/f_P) = 14^{\circ}$  and the spur at  $f_{\text{REF}}$  by  $20 \times \log_{10}(f_{\text{REF}}/f_P) = 17$  dB compared to the *Conv* PLL with  $Z_{\text{LF}}$ . In comparison, the proposed FF PLL reduces PM by 14° and spur by 28 dB compared to the Conv PLL with  $Z_{\text{LF}}$ , as shown in Fig. 8.

<sup>&</sup>lt;sup>5</sup>A unity-gain amplifier with BW greater than the LDO BW can restore PM by isolating impedance  $Z_{\rm HF}$  from the LF.

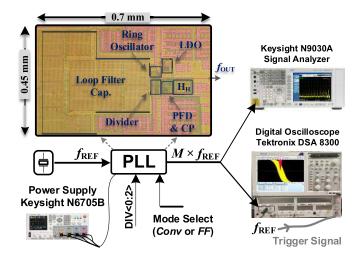

Fig. 12. PLL chip micrograph and measurement setup for the time- and frequency-domain characterization.

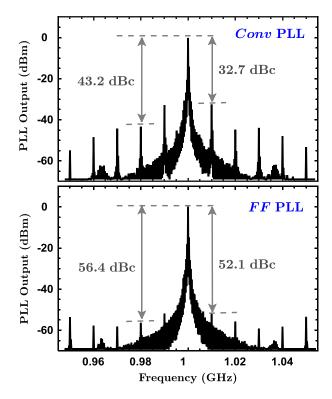

Fig. 13. Measured PLL output spectrum at 1-GHz output frequency in FF and Conv modes. RBW = 10 kHz and VBW = 1 kHz.

nodes are shorted to nullify its bulk transconductance. The RO has a tuning range of 0.6–1.7 GHz and an oscillator gain of 1.5 GHz/V.

PLL output is divided by two before feeding to the prescaler in the feedback divider. Feedback divider ranges from 44 to 51. PLL output frequency tuning range is 880 MHz–1.02 GHz, which is limited by the divider in this demonstration. To minimize spur leakage through the substrate, PLL blocks are isolated by placing each block in an independent deep n-well that is surrounded by a single layer of deep-trench wall [23].

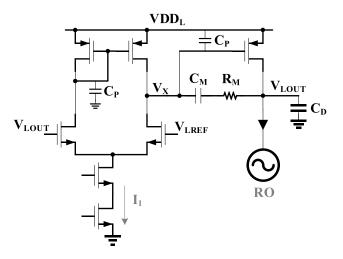

The LDO schematic is shown in Fig. 10. The Miller compensation technique with zero placement is used to stabilize

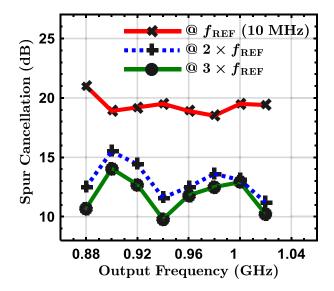

Fig. 14. Measured spur cancelation for various reference harmonics across the PLL frequency tuning range.

| TABLE I                    |  |  |  |  |  |  |  |

|----------------------------|--|--|--|--|--|--|--|

| FF PLL PERFORMANCE SUMMARY |  |  |  |  |  |  |  |

| Technology                            | 65 nm CMOS          |

|---------------------------------------|---------------------|

| Supply voltage                        | 1 V and 1.5 V       |

| Output frequency                      | 1 GHz               |

| Reference frequency                   | 10 MHz              |

| Loop bandwidth                        | 0.35 MHz            |

| Oscillator gain                       | 1.5 GHz/V           |

| Reference spur at $f_{\text{REF}}$    | -52.1 dBc           |

| Spur cancellation at $f_{\text{REF}}$ | 19.5 dB             |

| Total power consumption               | 320 μW              |

| Phase noise at 100 KHz                | -62 dBc/Hz          |

| Die area                              | $0.32 \text{ mm}^2$ |

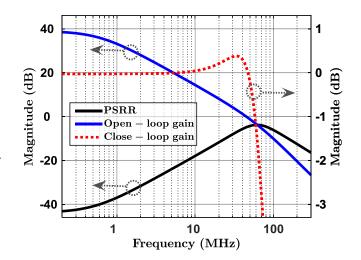

the LDO by using capacitor  $C_M$  and resistor  $R_M$ , as shown in Fig. 10. The bode-magnitude plot for the LDO's powersupply rejection ratio (PSRR), open-loop gain, and the closedloop gain are shown in Fig. 11. A 1.8-V-thick gate-oxide pMOS device regulates a 1.5- to 1-V supply voltage for the RO. The design parameters for the LDO are:  $C_M = 0.2$  pF,  $R_M = 3 \ k\Omega$ ,  $C_D = 57$  pF, and  $I_1 = 25 \ \mu$ A. The simulated LDO open-loop poles and zeros are at {0.6, 70, 190} and 190 MHz, respectively. The PSRR is more than 35 dB below 1 MHz. The  $H_L(s)$  has a peaking of <0.8 dB and phase margin of > 50° across process and temperature variations.

#### V. EXPERIMENTAL RESULTS

An integer-N PLL prototype is fabricated in a 65-nm bulk CMOS process. The PLL chip micrograph and measurement setup are shown in Fig. 12. The FF path adds an area overhead of less than 2% of the total area. The PLL operates from 1- to 1.5-V supplies and consumes a total of 320  $\mu$ W, excluding output buffers.

The measured PLL output spectrum at 1 GHz is compared in Fig. 13 for both PLL modes. A spur cancelation of 19.4 and

|     | TABLE II                                                                                                                |

|-----|-------------------------------------------------------------------------------------------------------------------------|

| Сом | MPARISON OF PROPOSED ZERO-POWER FF SPUR CANCELATION WITH PLLS USING SPUR SUPPRESSION AND OPERATING AT SIMILAR FREQUENCY |

|                                              | This<br>Work | [21]<br>TVLSI'13 | [14]<br>JSSC'16 | [7]<br>TVLSI'12 | [15]<br>RFIC'15 | [13]<br>JSSC'08 |

|----------------------------------------------|--------------|------------------|-----------------|-----------------|-----------------|-----------------|

| Output frequency [GHz]                       | 1            | 2.6              | 2.4             | 1               | 2.4             | 2.4             |

| Reference frequency $f_{\text{REF}}$ [MHz]   | 10           | 5                | 22.6            | 13              | 1               | 12              |

| $f_{ m UG}/f_{ m REF}$                       | 1/29         | 1/100            | 1/2.3           | 1/44            | 1/25            | 1/12            |

| Oscillator gain [GHz/V]                      | 1.5          | 0.33             | 1.5             | 0.05            | 0.09            | 0.06            |

| 1 <sup>st</sup> Spur harmonic [dBc]          | -53          | -72              | -65             | -57             | -50             | -70             |

| Spur suppression <sup>*</sup> [dB]           | 19.5         | 19               | 18              | 16              | 15              | 12              |

| Power overhead for<br>Spur cancellation? (%) | No<br>(0%)   | Yes<br>(N/A)     | Yes<br>(6.3%)   | Yes<br>(20%)    | No<br>(0%)      | Yes<br>(N/A)    |

<sup>†</sup>Type-I PLL. 1<sup>st</sup> spur harmonic post-cancellation or suppression.

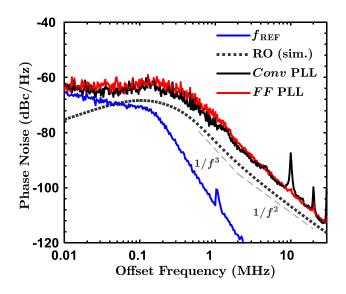

Fig. 15. Measured PLL PN at 1 GHz in FF and Conv modes. Contribution of the reference signal (measured) and the RO (simulated) to PLL's PN is also shown.

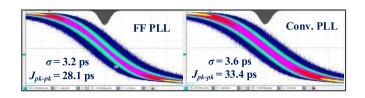

Fig. 16. Measured jitter histogram of PLL at 880-MHz output in FF and Conv modes using 100-K waveform samples.

13 dB is measured at the first and the second spur harmonics, respectively. The measured spur cancelation across the PLL frequency tuning range for up to the third spur harmonic is shown in Fig. 14. An average spur rejection of 19.5, 13, and 11.8 dB is achieved at the first, second, and third spur harmonics, respectively. Spur cancelation increases at higher harmonics and decreases at the first harmonic as  $f_R$  is shifted to higher frequency.

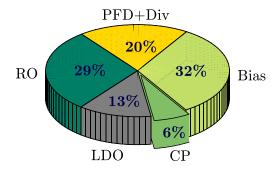

Fig. 17. Power consumption breakdown of the PLL at 1 GHz.

PLL PN for a 1-GHz output frequency is shown in Fig. 15 for both modes of the FF path. The (measured) XTAL oscillator and the (simulated) RO PN contribution to the PLL's PN are also shown in Fig. 15. The PLL in-band PN is -63 and -62.1 dBc/Hz at a 100-kHz offset for the Conv and the FF modes, respectively. The presence of a pole-zero pair in the effective loop-filter impedance  $Z_{ELF}$  due to the FF path, as shown in (10), causes peaking in the PLL's noise TF. This noise transfer peaking increases the PN by about 1 dB near the  $f_{UG}$ . PLL jitter histograms are shown in Fig. 16. The spur cancelation reduces the integrated noise, which reduces peakto-peak jitter ( $J_{pk-pk}$ ) and the jitter variance ( $\sigma_t$ ) by more than 14% and 10%, respectively, across the PLL output frequency tuning range.

PLL power consumption breakdown at 1-GHz output frequency is shown in Fig. 17. PLL performance is summarized in Table I. The proposed technique is compared with the state-of-the-art spur suppression methods in Table II. The proposed method suppresses the first spur harmonic by 19.5 dB without consuming any power. Despite a large oscillator gain of 1.5 GHz/V, the PLL prototype has a postcancelation spur of -53 dBc. In comparison, [21] suppresses the first spur harmonic by an average of 19 dB using power hungry and complex active circuits. The spurs in [15] are dominated by the charge sharing between the CP switches and the LF, which is suppressed by 15 dB at the first spur harmonic using fixed voltage CP biasing. However, this method has limited benefits as it cannot reduce the spur if it is dominated by other PLL nonidealities, as discussed in Section II-B. In summary, the proposed low-complexity technique achieves among the highest spur suppression without requiring any calibration and zero-power consumption.

# VI. CONCLUSION

This paper presents a novel FF spur cancelation technique for supply-regulated ring PLLs. Up to the third spur harmonics are canceled significantly by introducing a passive high-pass filter-based FF spur-coupling path. The proposed method achieves simulated postcancelation spur values of -46 to -79 dBc (depending on the oscillator gain), and is applicable to a wide range of PLL designs with any loop BW. Spur cancelation performance is robust against large PVT variations, which avoids the need of calibration schemes. An integer-N PLL prototype in 65-nm CMOS process achieves a spur cancelation of 19.5, 13, and 11.8 dB at the first, second, and third spur harmonics, respectively. The proposed technique has low complexity and zero power consumption, which makes it suitable for the design of low-power PLLs for low-cost applications.

#### REFERENCES

- Gartner. Gartner Says 6.4 Billion Connected 'Things' Will Be in Use in 2016, Up 30 Percent From 2015. Accessed: Jul. 1, 2017. [Online]. Available: http://www.gartner.com/newsroom/id/3165317

- [2] J. A. Stankovic, "Research directions for the Internet of Things," *IEEE Internet Things J.*, vol. 1, no. 1, pp. 3–9, Feb. 2014.

[3] *IEEE 802.15.4.* Accessed: Jul. 1, 2017. [Online]. Available:

- [3] IEEE 802.15.4. Accessed: Jul. 1, 2017. [Online]. Available: http://standards.ieee.org/

- [4] M. Mansuri and C.-K. Ken, "Jitter optimization based on phase-locked loop design parameters," *IEEE J. Solid-State Circuits*, vol. 37, no. 11, pp. 1375–1382, Nov. 2002.

- [5] C. T. Charles and D. J. Allstot, "A calibrated phase/frequency detector for reference spur reduction in charge-pump PLLs," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 53, no. 9, pp. 822–826, Sep. 2006.

- [6] C.-F. Liang, S.-H. Chen, and S.-I. Liu, "A digital calibration technique for charge pumps in phase-locked systems," *IEEE J. Solid-State Circuits*, vol. 43, no. 2, pp. 390–398, Feb. 2008.

- [7] J. Choi, W. Kim, and K. Lim, "A spur suppression technique using an edge-interpolator for a charge-pump PLL," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 20, no. 5, pp. 969–973, May 2012.

- [8] I.-T. Lee, Y.-T. Tsai, and S.-I. Liu, "A leakage-current-recycling phaselocked loop in 65 nm CMOS technology," *IEEE J. Solid-State Circuits*, vol. 47, no. 11, pp. 2693–2700, Nov. 2012.

- [9] P. Agarwal, S. P. Sah, and H. Deukhyoun, "A low leakage pull-down network for PLL with 6.7 dB improvement in reference spur," presented at the IEEE Asia–Pacific Microw. Conf. (APMC), 2013.

- [10] S. Min, T. Copani, S. Kiaei, and B. Bakkaloglu, "A 90-nm CMOS 5-GHz ring-oscillator PLL with delay-discriminator-based active phasenoise cancellation," *IEEE J. Solid-State Circuits*, vol. 48, no. 5, pp. 1151–1160, May 2013.

- [11] F. Bohn, K. Dasgupta, and A. Hajimiri, "Closed-loop spurious tone reduction for self-healing frequency synthesizers," presented at the IEEE Radio Freq. Integr. Circuits Symp. (RFIC), 2011.

- [12] C. Thambidurai and N. Krishnapura, "On pulse position modulation and its application to PLLs for spur reduction," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 7, pp. 1483–1496, Jul. 2011.

- [13] K. J. Wang, A. Swaminathan, and I. Galton, "Spurious tone suppression techniques applied to a wide-bandwidth 2.4 GHz fractional-N PLL," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 2787–2797, Dec. 2008.

- [14] L. Kong and B. Razavi, "A 2.4 GHz 4 mW inductorless RF synthesizer," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2015, pp. 1–3.

- [15] A. Paidimarri, N. Ickes, and A. P. Chandrakasan, "A 0.68V 0.68 mW 2.4 GHz PLL for ultra-low power RF systems," presented at the IEEE Radio Freq. Integr. Circuits Symp. (RFIC), 2015.

- [16] G. Shu *et al.*, "A reference-less clock and data recovery circuit using phase-rotating phase-locked loop," *IEEE J. Solid-State Circuits*, vol. 49, no. 4, pp. 1036–1047, Apr. 2014.

- [17] V. Gupta, G. A. Rincon-Mora, and P. Raha, "Analysis and design of monolithic, high PSR, linear regulators for SoC applications," presented at the IEEE Int. SOC Conf., 2004.

- [18] A. Arakali, S. Gondi, and P. K. Hanumolu, "Low-power supplyregulation techniques for ring oscillators in phase-locked loops using a split-tuned architecture," *IEEE J. Solid-State Circuits*, vol. 44, no. 8, pp. 2169–2181, Aug. 2009.

- [19] K.-C. Choi, S.-G. Kim, S.-W. Lee, B.-C. Lee, and W.-Y. Choi, "A 990-μW 1.6-GHz PLL based on a novel supply-regulated activeloop-filter VCO," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 60, no. 6, pp. 311–315, Jun. 2013.

- [20] C. T. Charles and D. J. Allstot, "A buffered charge pump with zero charge sharing," presented at the IEEE Int. Symp. Circuits Syst., 2008.

- [21] T.-W. Liao, J.-R. Su, and C.-C. Hung, "Spur-reduction frequency synthesizer exploiting randomly selected PFD," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 21, no. 3, pp. 589–592, Mar. 2013.

- [22] X. Gao, E. A. M. Klumperink, G. Socci, M. Bohsali, and B. Nauta, "Spur reduction techniques for phase-locked loops exploiting a subsampling phase detector," *IEEE J. Solid-State Circuits*, vol. 45, no. 9, pp. 1809–1821, Sep. 2010.

- [23] T. Hashimoto, H. Satoh, H. Fujiwara, and M. Arai, "A study on suppressing crosstalk through a thick SOI substrate and deep trench isolation," *IEEE J. Electron Devices Soc.*, vol. 1, no. 7, pp. 155–161, Jul. 2013.

**Pawan Agarwal** (S'11) received the B.Tech. and M.Tech. degrees in electrical engineering from IIT Madras, Chennai, India, in 2009, and the Ph.D. degree from the Washington State University, Pullman, WA, USA, in 2017.

He was with Applied Micro, Pune, India, from 2009 to 2011, where he designed frequency synthesizers and regulators. He joined Applied Micro, Sunnyvale, CA, USA, as an intern in 2012, where he was involved in wire-line systems for 100-G bit Ethernet applications. In 2014, he joined

Maxlinear Inc., Irvine, CA, USA, as a Research Intern, where he focused on wireless systems for millimeter-wave backhaul applications. He is currently with Maxlinear Inc., Carlsbad, CA, USA. His current research interests include low-power reconfigurable millimeter-wave phased-array systems.

Dr. Agarwal was a recipient of the IEEE Microwave Theory and Techniques Society (MTT-S) Graduate Fellowship Award, the MTT-S International Microwave Symposium Student Paper Competition Award, and the Washington State University Voiland College of Engineering and Architecture Outstanding Teaching Assistant Award.

**Jong-Hoon Kim** received the Ph.D. degree in bio-mechatronics engineering from Sungkyunkwan University, Seoul, South Korea, in 1997.

In 2004, he became an Adjunct Professor at the Bio-Mechatronics Engineering Department, Sungkyunkwan University. He was a Visiting Scholar at the Washington State University, Pullman, WA, USA, from 2008 to 2009. He has been a Principle Researcher with the Korea Food Research Institute, Sungnam, South Korea, since 1991, where he is currently with the Research Group of Smart

Distribution System. His current interests include the convergence of information and communication technology and food technology, and also nondestructive sensing technology and system optimization.

Partha Pratim Pande received the M.S. degree in computer science from the National University of Singapore, Singapore and the Ph.D. degree in electrical and computer engineering from the University of British Columbia, Vancouver, BC, Canada.

He is currently a Professor and the Boeing Centennial Chair of Computer Engineering at the School of Electrical Engineering and Computer Science, Washington State University, Pullman, WA, USA. His current research interests include novel interconnect architectures for multicore chips, on-chip wireless communication networks, and hardware accelerators for biocomputing.

Dr. Pande was a recipient of the NSF CAREER Award in 2009. He received the Anjan Bose Outstanding Researcher Award from the College of Engineering, Washington State University, in 2013. He is the Editor-in-Chief (EIC) of the IEEE TRANSACTIONS ON MULTI-SCALE COMPUTING SYSTEMS and the Associate Editor-in-Chief of IEEE Design and Test. He also serves on the editorial boards of the ACM Journal of Emerging Technologies in Computing Systems, and the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS. He serves in the program committees of many reputed international conferences.

Deukhyoun Heo (S'97-M'00-SM'13) received the B.S.E.E. degree in electrical engineering from Kyoungpuk National University, Daegu, South Korea, in 1989, the M.S.E.E. degree in electrical engineering from the Pohang University of Science and Technology, Pohang, South Korea, in 1997, and the Ph.D. degree in electrical and computer engineering from Georgia Institute of Technology, Atlanta, GA, USA, in 2000.

In 2000, he joined the National Semiconductor Corporation as a Senior Design Engineer, where he

was involved in the development of silicon RFICs for cellular applications. In 2003, he joined the Faculty of Electrical Engineering and Computer Science Department, Washington State University, Pullman, WA, USA, where he is currently the Frank Brands Analog Distinguished Professor of electrical engineering. He has authored or coauthored approximately 160 publications, including peer-reviewed journal papers and international conference papers. His current research interests include RF/microwave/opto transceiver design based on CMOS, SiGe BiCMOS, and GaAs technologies for wireless and wire-line data communications, batteryless wireless sensors and intelligent power management system for sustainable energy sources, adaptive beam formers for phased-array communications, low-power high data-rate wireless links for biomedical applications, and multilayer module development for system-in-package solution.

Dr. Heo was a recipient of the 2000 Best Student Paper Award presented at the IEEE Microwave Theory and Techniques Society (IEEE MTT-S) International Microwave Symposium (IMS) and the 2009 National Science Foundation CAREER Award. He has been the Technical Program Committee Member of the IEEE MTT-S IMS and the International Symposium of Circuit and Systems. He has served as an Associate Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS —PART II: EXPRESS BRIEFS from 2007 to 2009 and the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES.