# **PROCEEDINGS OF SPIE**

SPIEDigitalLibrary.org/conference-proceedings-of-spie

Impact of processing and growth conditions on the site-catalyzed patterned growth of GaAs nanowires by molecular beam epitaxy

Manish Sharma Pavan Kasanaboina Shanthi Iyer

Impact of Processing and Growth Conditions on the Site-Catalyzed

Patterned Growth of GaAs Nanowires by Molecular Beam Epitaxy

Manish Sharma<sup>1</sup>, Pavan Kasanaboina<sup>2</sup> and Shanthi Iver<sup>+1,2</sup>

<sup>1</sup>Nanoengineering, Joint School of Nanoscience and Nanoengineering, North Carolina A&T State

University, Greensboro, North Carolina 27401, USA.

<sup>2</sup>Department of Electrical and Computer Engineering, North Carolina A&T State University,

Greensboro, North Carolina 27411, USA.

+ corresponding author: iver@ncat.edu

**Abstract**

We report on the site-selective growth of >90% vertical GaAs nanowires (NWs) on Si (111) using self-assisted

molecular beam epitaxy. The influences of growth parameters (pre-growth Ga opening time, V/III flux ratio) and

processing conditions (reactive ion etching (RIE) and HF etching time) are investigated for different pitch lengths (200-

1000 nm) to achieve vertical NWs. The processing variables determine the removal of the native oxide layer and the

contact angle of Ga-droplet inside the patterned hole that are critical to the vertical orientation of the NWs. Pre-growth

Ga-opening time is found to be a crucial factor determining the size of the droplet in the patterned hole, while the V/III

beam equivalent pressure (BEP) ratio influenced the occupancy of the holes due to the axial growth of NWs being

group-V limited.

Introduction

Semiconductors nanowires (NWs) have drawn considerable attention for use in future optoelectronic devices due to its

unique optical properties arising from its one-dimensional architecture. The higher tolerance of lattice-mismatch-induced

stress-strain can be advantageously used to integrate the optoelectronic devices with silicon-based technologies. The

reliable performance of NW-based heterostructure devices requires an uniform array of NWs of desired density of high

quality and consistent composition. [1-3] NW-based devices exhibit an enhanced light entrapment due to multiple

scattering of light on the surface of NWs, which is a function of pitch length and diameter of the NWs. [4-7]

Nanoengineering: Fabrication, Properties, Optics, and Devices XIV, edited by Eva M. Campo, Elizabeth A. Dobisz, Louay A. Eldada, Proc. of SPIE Vol. 10354, 103540F  $\cdot$  © 2017 SPIE  $\cdot$  CCC code: 0277-786X/17/\$18  $\cdot$  doi: 10.1117/12.2274669

Numerous techniques have been used to generate a pattern on the Si surface, e.g., nanosphere lithography [8, 9], laser-interface lithography [10], electron beam lithography (EBL) [11-14] and nanoimprint lithography (NIL) [15-19]. Among these, EBL and NIL are capable of patterning on the mask with high throughput. EBL is extensively used over NIL for patterned III-V NWs on both III-V and Si substrates. Extensive work has been reported by Tomioka et al. [11, 12, 20] on site-selective growth of III-V NWs by MOVPE using EBL. Plissard et al. [14] investigated the effect of growth parameters such as Ga pre-deposition, V/III ratio, growth temperature, oxide layer thickness, and pitch on the structure and yield of Ga-assisted GaAs NWs. Averchi et al. [21] studied the role of surface properties on the opening of the holes at the nanoscale, which determines the contact angle and position of the Ga droplet to achieve a high yield of vertical GaAs NWs on the Si substrate. Gibson et al. [1] have provided an account of various fluxes (direct impingement flux, secondary flux re-emitted from the oxide surface) contributing toward the axial and radial growth of GaAs-patterned NW arrays. Manish et al. [3] have modified Gibson et al. [1] growth model by considering an additional contribution of growth species desorbed from the NWs' side facets to explain the pitch-induced variation of axial and radial growth rates of GaAs, GaAs/GaAsSb core-shell, and GaAsSb axial NWs for high V/III flux ratios.

There have been numerous reports elucidating the role of the various parameters influencing the occupancy of the patterned holes, but achieving occupancy close to 100% has always been a challenge. In particular, in the molecular beam epitaxy (MBE) growth of NWs, several growth parameters need to be optimized in addition to the processing parameters, and further, their interdependency creates complexity [8, 14, 22]. Hence, in this report, a comprehensive study has been conducted to analyze the effects of processing conditions (reactive ion etching time, HF etching time), which influence the transfer of pattern on to the substrate by removal of an oxide layer from the patterned hole and the growth parameters (pre-growth Ga opening time, V/III beam equivalent pressure [BEP] ratio) to yield >90% vertical NWs.

#### **Experimental details**

The NWs were grown via a vapor-liquid-solid (VLS) mechanism in an EPI 930 solid-source MBE system with valved As source. Ga-assisted NW growth was initiated by impinging Ga flux on the substrate prior to the opening of the  $As_4$  flux with a beam equivalent pressure of  $4.8 \times 10^{-6}$  Torr. The surface morphology of NWs was characterized using a Carl Zeiss Auriga-BU FIB field emission scanning electron microscope (FESEM).

To fabricate nanoscale patterned holes on oxide layer, a PMMA 950K photo resist layer was first spun on the SiO<sub>2</sub> (15 nm)/Si (111) substrate at 3000 rpm for 40 s having a thickness of ~120 nm followed by a hot plate bake at 180°C for 120 s. The sample was then loaded into Elionix ELS- 7500 EX EBL system to write the desired features on the PMMA resist layer using a pre-designed computer aided design (CAD) file loaded into the EBL system. A high voltage of 50 KeV and 50 pA beam current were used during electron beam exposure. After this, the sample was developed using 1:3 methyl isobutyl ketone (MIBK): isopropyl alcohol (IPA) solution and rinsed by pure IPA, followed by a deionized (DI) water. A Trion technology Phantom II RIE was subsequently used to remove an oxide layer through the patterned features. The RIE process involved etching of SiO<sub>2</sub> using CF<sub>4</sub> and O<sub>2</sub> through patterned holes in the PMMA. Once the pattern was transferred to the substrate, O<sub>2</sub> plasma etching was performed to completely strip off the hardened PMMA, and the remnant PMMA resist was subsequently removed by acetone treatment. The patterned Si was cleaned by using Piranha solution and treated with HF solution to remove native oxide from the patterned hole after that sample was loaded for the growth of NW.

### **Results and Discussion**

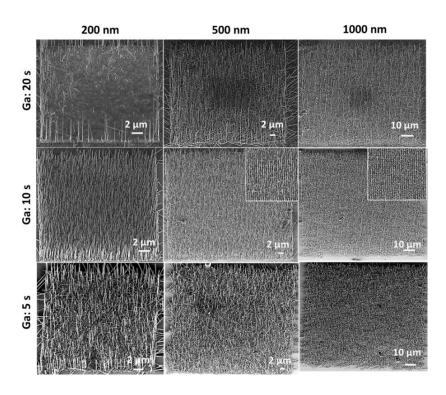

The effects of various parameters—namely, pre-growth Ga opening, V/III BEP ratio, RIE etching, and HF etching time—on the growth of vertical NWs have been investigated in detail for different pitch lengths (200 - 1000 nm). We found that the pre-growth Ga-opening duration (increase/decrease) has a direct effect on the size of the Ga droplet (increase/decrease) on the patterned hole, which in principle needs to be optimized for each pitch length. For instance, at a lower pitch length, if the Ga droplet size is larger than the hole size, the adjacent Ga droplets may combine to form a parasitic layer. This is shown in Fig. 1 for the pitch length of 200 nm and Ga shutter opening duration of 20 s. For the same Ga shutter opening duration of 20 s at higher pitch lengths, no significant parasitic layer is observed, which is attributed to the distance between Ga droplets being large. The Ga-opening duration of 10 s was found to result in vertical NW growths of high density for almost all pitch lengths, as shown in Fig.1. The reduction of Ga shutter opening duration to 5 s led to a reduction in the NW density along with bent NWs. We speculated that this was due to the Ga droplet size being smaller than the hole, leading to a change in the contact angle; as a result, the amount of Ga deposited may not have been sufficient for nucleation and growth. Therefore, a Ga shutter opening duration of 10 s was determined to be the optimum duration resulting in the occupancy of >90% of the hole for all pitch lengths.

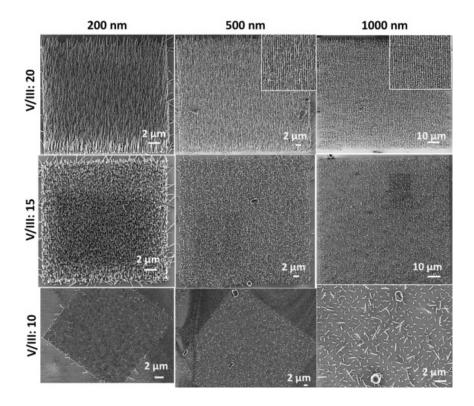

Now, with the initial Ga shutter opening duration opitmised at 10 s, the effect of V/III BEP ratio variation for different pitch lengths was investigated as illustrated in Figure 2. Notably, the V/III BEP ratio variation was carried out with varying group-V flux for a constant Ga flux. As shown in Fig. 2, a V/III BEP ratio of 20 led to better occupancy of holes, as with decreasing V/III BEP ratio, the occupancy (NW density) is reduced, which could be attributed to unavailability of As atoms towards the nucleation and subsequent supersaturation as axial growth are group-V limited.

Figure 1: SEM images of the effect of variation of NW density with initial Ga shutter opening duration for different pitch lengths.

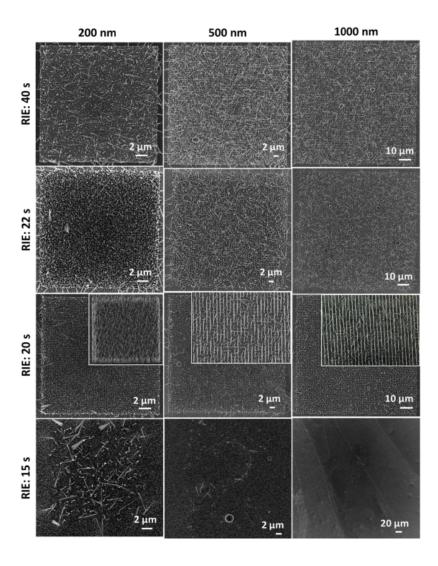

Despite optimization of the critical growth parameters, all vertical and 100% occupancy were still not achieved. This provided a hint that the oxide thickness required optimization. For all the above growths, the substrates were prepared with RIE duration of 30 s, which might have either over- or under-etched the 15 nm SiO<sub>2</sub> layer through holes. Hence, the growths of the NWs under optimized conditions were investigated as a function of RIE duration (the results are displayed in Fig. 3). For the RIE duration of 15 s, 20 s, and 40 s, the NW growths transitioned from no growth to ~85-90% occupancy of holes with vertical NWs to bent NWs.

These observations can be qualitatively explained regarding the removal of an oxide layer in the pores with increasing RIE duration. For the lowest RIE duration of 15 s, the oxide layer is not sufficiently etched, preventing any NW growth.

On the other extreme of 40 s RIE, over-etching of the oxide layer is causing the underlying Si substrate to be etching, leading to non-vertical NWs. Thus 20 s RIE appeared to be close to optimized etching duration. Since a small change in the RIE duration makes a significant variation in the occupancy and vertical NWs, further fine-tuning of the RIE duration was attempted close to the 20 s. However, RIE durations of 19 s, 21 s, and 22 s led to the growth of more non-vertical NWs, suggesting the inability to optimize the oxide layer thickness by RIE alone due to the high etch rate of  $SiO_2$  by this process.

Figure 2: SEM images of the effect of variation of NW density with V/III BEP ratio for different pitch lengths.

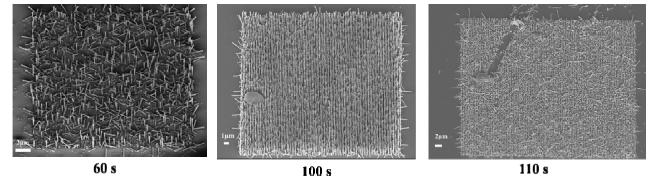

Hence, HF etching duration was investigated to achieve a better control on the oxide removal. Figure 4 displays the variation of the NW density as a function of three HF etching durations of 60 s, 100 s, and 110 s. A strong influence of the initial etching is observed with an inoccupancy of the holes at 60 s, to >90% occupancy of holes at 100 s, to bent NWs at 110 s etching. These indicate the presence of residual oxide from complete removal to over-etching of the Si surface, respectively, with the variation of HF etching duration. The last one apparently leads to a fine-tuning for removal of the oxide layer from patterned holes, likely resulting in a change in the contact angle Ga-droplet makes with

the substrate, resulting in vertical NWs. Thus, 100 s was found to be the optimum HF etching duration for achieving maximum occupancy of holes and growth of vertical NWs.

Figure 3: SEM images of the effect of RIE duration variation on the NW growth for three different pitch lengths.

Figure 4: SEM image of variation of HF etching time on the growth of GaAs NWs.

### Conclusion

The process and growth parameters were investigated for the self-catalyzed growth of >90% vertical GaAs nanowires on patterned Si substrate. It was found that the RIE (course tune) and HF etching duration (fine tune) had a strong effect on selective etching of SiO<sub>2</sub> layer that likely aided in the formation of a contact angle of 90°, which is a necessary condition for the growth of vertical NWs. Pre-deposition Ga-opening duration along with pitch length influences the formation of an appropriate size of the Ga droplet and/or formation of the passive layer due to agglomeration, while the V/III BEP ratio impacted the supersaturation of Ga droplets. Optimized conditions for the growth of >90% vertical GaAs NWs were thus found to be an RIE duration of 20 s, an HF etching duration of 100 s, a pre-deposition Ga-opening duration of 10 s, and a V/III BEP ratio of 20.

#### Acknowledgments

This work is financially supported by Army Research Office (Grant No. W911NF-15-1-0160) and National Science Foundation (Award No. 1649517). Part of this work was performed at the Joint School of Nanoscience and Nanoengineering, a member of the Southeastern Nanotechnology Infrastructure Corridor (SENIC) and National Nanotechnology Coordinated Infrastructure (NNCI), which is supported by the National Science Foundation (ECCS-1542174).

## References

- [1] Gibson, S. J. and LaPierre, R. R. "Model of patterned self-assisted nanowire growth," Nanotechnology 25, 415304 (2014).

- [2] LaPierre, R. R., Chia, A. C. E., Gibson, S. J., Haapamaki, C. M., Boulanger, J., Yee, R., Kuyanov, P., Zhang, J. Tajik, N., Jewell, N., and Rahman, K. M. A. "III-V nanowire photovoltaics: Review of design for high efficiency," Phys. Stat. Soli. (RRL) 7, 815-830 (2013).

- [3] Sharma, M., Karim, M. R., Kasanaboina, P., Li, J. and Iyer, S. "Pitch-Induced Bandgap Tuning in Self-Catalyzed Growth of Patterned GaAsSb Axial and GaAs/GaAsSb Core—Shell Nanowires Using Molecular Beam Epitaxy," Cryst. Growth & Des. 17, 730-737 (2017).

- [4] Garnett, E. and Yang, P. "Light trapping in silicon nanowire solar cells," Nano Lett. 10, 1082-7 (2010).

- [5] Gutsche, C., Lysov, A., Braam, D., Regolin, I., Keller, G., Li, Z. An., Geller, M., Spasova, M., Prost, W. and Tegude, F. J. "n-GaAs/InGaP/p-GaAs Core-Multishell Nanowire Diodes for Efficient Light-to-Current conversion," Adv. Funct. Mater. 22, 929-936 (2012).

- [6] Heiss, M., Averchi, E. R., Mallorqui, A. D., Tutuncuoglu, G., Matteini, F., Ruffer, D., Conesa-Boj, S., Demichel, O., Alarcon-Lladó, E and Morral, A Fontcuberta i. "III-V nanowire arrays: growth and light interaction," Nanotechnology 25, 014015 (2014).

- [7] Leung, S. F., Zhang, Q., Xiu, F., Yu, D., Ho, J. C., Li, D., and Fan, Z. "Light Management with Nanostructures for Optoelectronic Devices," J. Phys. Chem. Lett. 5, 1479-95 (2014).

- [8] Fuhrmann, B., Leipner, H. S., and Hoche, H.R. "Ordered arrays of Si Nanowires Produced by Nanosphere Lithography and Molecular Beam Epitaxy," Nano Lett. 5, 2524-27 (2005).

- [9] Madaria, A. R., Yao, M., Chi, C., Huang, N., Lin, C., Li, R., Povinellli, M.L., Dapkus, P.D., and Zhou, C. "Toward Optimized Light Utilization in Nanowire Arrays Using Scalable Nanosphere Lithography and Selected Area Growth," Nano Lett. 12, 2839-45 (2012).

- [10] Kim, D. S., Ji, R., Fan, H. J., Bertram, F., Scholz, R., Dadgar, A., Nielsch, K., Krost, A., Christen, U. G. and Zacharias, M. "Laser-interference lithography tailored for highly symmetrically arranged ZnO nanowire arrays," Small 3, 76-80 (2007).

- [11] Tomioka, K., Kobayashi, Y., Motohisa, J., Hara, S. and Fukui, T., "Selective-area growth of vertically aligned GaAs and GaAs/AlGaAs core-shell nanowires on Si (111) substrate," Nanotechnology 20, 145302 (2009).

- [12] Tomioka, K., Motohisa, J., Hara, S., and Fukui, T. "Control of InAs Nanowire Growth Directions on Si," Nano Lett. 8, 3475-80 (2008).

- [13] Plissard, S., Dick, K. A., Larrieu, G., Godey, S., Addad, A., Wallart, X., and Caroff, P., "Gold-free growth of GaAs nanowires on silicon: arrays and polytypism," Nanotechnology 21, 385602 (2010).

- [14] Plissard, S., Larrieu, G., X. Wallart, and P. Caroff, "High yield of self-catalyzed GaAs nanowire arrays grown on silicon via gallium droplet positioning," Nanotechnology 22, 275602 (2011).

- [15] Haas, F., Sladek, K., Winden, A., von der Ahe, M., Weirich, T. E., Rieger, T., Luth H, Grutzmacher, D., Schapers. T., Hardtdegen, H. "Nanoimprint and selective-area MOVPE for growth of GaAs/InAs core/shell nanowires," Nanotechnology 24, 085603 (2013).

- [16] Hertenberger, S., Funk, S., Vizbaras, K., Yadav, A., Rudolph, D., Becker, J., Bolte, S., Doblinger, M., Bichler, M., Scarpa, G., Lugli, P., Zardo, I., Finley, J. J., Amann, M.C., Abstreiter, G. and Koblmuller, G. "High compositional homogeneity in In-rich InGaAs nanowire arrays on nanoimprinted SiO2/Si (111)," Appl. Phys. Lett. 101, 043116 (2012).

- [17] Kim, H., Lee, J.H., Chae, E. J., Choi, J.W., and Oh, B.K. "Detection of Dopamine Using a Silicon Nanowire Patterned by Nanoimprint Lithography," J. Nanosci. Nanotechnol. 11, 7516-7519 (2011).

- [18] Martensson, T., Carlberg, P., Borgstrom, M., Montelius, L., Seifert, W., and Samuelson, L, "NW arrays defined by nanoimprint lithography," Nano lett. 4, 699-702 (2004).

- [19] Munshi, A. M., Dheeraj, D. L., Fauske, V. T., Kim, D. C., Huh, J., Reinertsen, J. F., Ahtapodov, L., Lee, K. D., Heidari, B., van Halvoort, A.T.J., Fimland, B.O., and Weman, H. "Position-controlled uniform GaAs nanowires on silicon using nanoimprint lithography," Nano Lett. 14, 960-6 (2014).

- [20] Tomioka, K., Ikejiri, K., Tanaka, T., Motohisa, J., Hara, S., Hiruma, K., and Fukui, T., "Selective-area growth of III-V nanowires and their applications," J. Mater. Res. 26, 2127-2141 (2011).

- [21] Averchi, E. R., Plestina, J. V., Tutuncuoglu, G., Matteini, F., Mallorqui, A. D., Mata, M. D L, Ruffer, D., Potts, H.A., Arbiol, J., Conesa-Boj, S. and Morral, A.F.i. "High Yield of GaAs Nanowire Arrays on Si Mediated by the Pinning and Contact Angle of Ga," Nano Lett. 15, 2869-74 (2015).

- [22] Gibson, S., and LaPierre, R. "Study of radial growth in patterned self-catalyzed GaAs nanowire arrays by gas source molecular beam epitaxy," Phys. Stat. Soli. (RRL) 7, 845-849 (2013).