# Doping-Free Complementary Logic Gates Enabled by Two-Dimensional Polarity-Controllable Transistors

Giovanni V. Resta,<sup>\*,†,ID</sup> Yashwanth Balaji,<sup>‡,§</sup> Dennis Lin,<sup>‡</sup> Iuliana P. Radu,<sup>\*,‡</sup> Francky Catthoor,<sup>‡,§</sup> Pierre-Emmanuel Gaillardon,<sup>\*,||</sup> and Giovanni De Micheli<sup>\*</sup>

<sup>†</sup>Integrated System Laboratory (LSI), School of Engineering, École Polytechnique Fédérale de Lausanne (EPFL), CH-1015 Lausanne, Switzerland

<sup>‡</sup>IMEC, Kapeldreef 75, B-3001 Leuven, Belgium

<sup>§</sup>KU Leuven, Celestijnenlaan 200D, B-3001 Leuven, Belgium

<sup>||</sup>Laboratory of NanoIntegrated Systems (LNIS), Department of Electrical and Computer Engineering, University of Utah, Salt Lake City, Utah 84112, United States

## Supporting Information

**ABSTRACT:** Atomically thin two-dimensional (2D) materials belonging to transition metal dichalcogenides, due to their physical and electrical properties, are an exceptional vector for the exploration of next-generation semiconductor devices. Among them, due to the possibility of ambipolar conduction, tungsten diselenide ( $\text{WSe}_2$ ) provides a platform for the efficient implementation of polarity-controllable transistors. These transistors use an additional gate, named polarity gate, that, due to the electrostatic doping of the Schottky junctions, provides a device-level dynamic control of their polarity, that is, n- or p-type. Here, we experimentally demonstrate a complete doping-free standard cell library realized on  $\text{WSe}_2$  without the use of either chemical or physical doping. We show a functionally complete family of complementary logic gates (INV, NAND, NOR, 2-input XOR, 3-input XOR, and MAJ) and, due to the reconfigurable capabilities of the single devices, achieve the realization of highly expressive logic gates, such as exclusive-OR (XOR) and majority (MAJ), with fewer transistors than possible in conventional complementary metal-oxide-semiconductor logic. Our work shows a path to enable doping-free low-power electronics on 2D semiconductors, going beyond the concept of unipolar physically doped devices, while suggesting a road to achieve higher computational densities in two-dimensional electronics.

**KEYWORDS:** two-dimensional semiconductor,  $\text{WSe}_2$ , electrostatic doping, polarity control, reconfigurable, logic gates, standard cell library

Dimensional scaling has been the main drive of the silicon industry in recent decades. The growth of information technology has been sustained by the miniaturization of complementary metal-oxide-semiconductor (CMOS) field-effect transistors (FETs),<sup>1</sup> with the number of devices per unit area constantly increasing, as exemplified by Moore's law.<sup>2</sup> Modern digital integrated circuits (ICs) contain billions of transistors and logic gates, fabricated with CMOS technology. In CMOS, silicon is physically doped during the fabrication process with ion implantation to create unipolar devices with Ohmic contacts. The doping process irreversibly sets the polarity of the transistors (n- or p-type) according to the dopant atoms used (arsenic (As) for electron and phosphorus (P) for hole doping). With the physical gate

length of modern devices approaching 10 nm, ion implantation has become increasingly more complicated to control.<sup>3,4</sup> Fluctuations in number of dopant atoms present in the transistor channel are responsible for an increased variability of the threshold voltage of the devices.<sup>4</sup> In addition, ion implantation requires high-temperature annealing to repair damages in the silicon and achieve proper dopant activation.<sup>5,6</sup> This high-temperature process is not compatible with the process for monolithic 3D-CMOS, which requires a low

Received: April 12, 2018

Accepted: June 26, 2018

thermal budget. A device concept that would not rely on any physical doping and use undoped materials would be of great interest in this regard. Undoped materials are, for the most part, able to conduct both charge carriers (*i.e.*, electrons and holes), a property which is called ambipolarity, and usually create Schottky barriers (SB) at the contact interface with a metal. However, a purely ambipolar device would be difficult to switch off with a standard gate configuration, as we cannot selectively suppress the injection of one type of charge carrier.<sup>7,8</sup> The key to unlock the possibility of controlling the polarity of the transistor is the separate gating of different channel regions, due to a double-independent-gate structure.<sup>8</sup> By adding a second gate, which we refer to as polarity gate (or program gate, PG), we are able to induce electrostatic doping at the contact interfaces and block the injection either of electrons or holes. It is then possible to dynamically reconfigure the device polarity at run time, by reversing the bias applied to the polarity gate. A conventional gate, named control gate, acting in the central region of the channel modulates a potential barrier in the semiconducting material controlling the ON/OFF state of the device. The possibility to dynamically change the polarity at run time enhances the switching property of the transistors, enabling a doping-free, highly flexible design for logic circuits.<sup>9</sup> Polarity-controllable devices have been demonstrated using a variety of semiconducting materials;<sup>8,10–20</sup> however, the fabrication of complex logic gates, exploiting the polarity control of the transistors, has only been shown on silicon.<sup>11,20</sup> Here, we report a library of logic gates realized with two-dimensional polarity-controllable transistors.

Two-dimensional semiconductors of the transition metal dichalcogenide (TMDC) family<sup>21</sup> have recently attracted the attention of the scientific community in view of their structural and electronic properties.<sup>22–24</sup> With sub-nanometer single layers, providing optimal electrostatic control,<sup>25–27</sup> a significant energy band gap, and the promise of dangling-bond-free interfaces,<sup>22–24</sup> avoiding surface scattering, 2D-TMDC semiconducting materials, such as molybdenum disulfide (MoS<sub>2</sub>) and WSe<sub>2</sub>, have been extensively studied.<sup>28–33</sup> Rigorous quantum transport simulations have also been carried out to assess the performances of 2D semiconductor devices at ultrascaled gate lengths, in the case of both unipolar physically doped devices<sup>43,44</sup> and doping-free polarity-controllable transistors.<sup>45</sup> Continuous progress in the growth of 2D materials<sup>34–36</sup> in testing and understanding of their properties<sup>37–39</sup> and in the demonstration of device concepts<sup>40–42</sup> keeps the spotlight on this family of materials. Complex logic circuits have been demonstrated with 2D semiconductors<sup>29,46</sup> using a pseudo-n-MOS logic, with n-type MoS<sub>2</sub> transistor, which does not have the power consumption benefits of CMOS. However, physical doping of 2D materials is still an open challenge, and the realization of CMOS logic gates on 2D semiconductors has only been achieved with the use of chemical doping and different metal contacts<sup>31,32</sup> or using two different materials for n- and p-type devices.<sup>33</sup> Both methods greatly complicate the fabrication process and, in the case of chemical doping, make it nonscalable and noncompatible with conventional CMOS fabrication. When no physical or chemical doping is introduced, contact to a 2D semiconductor usually results in the creation of a Schottky barrier. Thus, the use of electrostatic doping of the contact regions to reversibly select the polarity of the transistor adapts perfectly to these emerging class of materials and provides a path for the

realization of CMOS logic with the use of a single two-dimensional ambipolar semiconductor. The most known TMDC material, MoS<sub>2</sub>, has proven to be a viable solution for the realization of n-MOS transistors,<sup>28,29</sup> and ultrascaled devices have been recently demonstrated.<sup>25–28</sup> Despite recent work that has shown the possibility of achieving ambipolar behavior in MoS<sub>2</sub>,<sup>47</sup> due to hexagonal boron nitride (h-BN) tunneling contacts, the partial Fermi level pinning at the contact interface<sup>48</sup> remains challenging to overcome without greatly complicating the fabrication process. Moreover, the higher band gap reported for MoS<sub>2</sub>, with respect to that of WSe<sub>2</sub> and other 2D materials such as zirconium selenide (ZrSe<sub>2</sub>) and hafnium selenide (HfSe<sub>2</sub>),<sup>37</sup> makes it less appealing for polarity-controllable applications, as it would produce higher Schottky barriers, thus limiting carrier injection at the contacts.<sup>45</sup> WSe<sub>2</sub> has shown high carrier mobility<sup>49</sup> and ambipolar behavior,<sup>7,8</sup> and CMOS-like devices have been reported experimentally with chemical doping of the material.<sup>31,32</sup> Recently, polarity-controllable transistors have been shown on 2D tungsten diselenide (WSe<sub>2</sub>), achieving ON/OFF ratios higher than 10<sup>6</sup> for both n- and p-type behavior in a single device,<sup>8</sup> making it arguably the best candidate for further exploration of the potential of reconfigurable devices. However, to the best of our knowledge, a complete basis for an effective standard cell library of two-dimensional logic gates, fabricated with polarity-controllable devices, has not been demonstrated yet.

In this paper, we use two-dimensional semiconducting material to fabricate highly expressive doping-free logic gates using polarity-controllable devices. We exploit the presence of Schottky barrier contacts in WSe<sub>2</sub>, and due to electrostatic doping, we achieve dynamic control of the polarity of the transistor, removing the need for any physical or chemical doping during the fabrication process. We fabricate and characterize a variety of polarity-controllable logic gates such as inverters (INV), negative-AND (NAND), and negative-OR (NOR) that are the building primitives used in the logic synthesis frameworks for conventional CMOS logic. Moreover, we experimentally show 2-input XOR (XOR-2), 3-input XOR (XOR-3), and Majority (MAJ) gates that, due to the polarity-controllable devices, can be realized with fewer transistors than what is achievable in conventional CMOS. We demonstrate a complete standard cell library with the possibility of fabricating compact, highly expressive logic gates that can be exploited to gain advantages at circuit level, using XOR and MAJ functions as logic primitives.<sup>50–53</sup>

## RESULTS AND DISCUSSION

**Fabrication of Logic Gates and Design Regularity.** For our experiments, we use WSe<sub>2</sub> flakes prepared by mechanical exfoliation from commercially available bulk crystals. The flakes are exfoliated on a Si/SiO<sub>2</sub> substrate and then transferred (see [Materials and Methods](#) and [Supporting Information S1](#)) on a target substrate with prepatterned back-gates (2 nm Ti/10 nm Pt) isolated with ZrO<sub>2</sub> deposited by atomic layer deposition (details on the fabrication process are presented in [Materials and Methods](#) and [Supporting Information S2](#)). The addition of the polarity gate enables us to use a single semiconducting material for the realization of both n- and p-type transistors, without the addition of physical or chemical doping. This is a great advantage because the latter greatly complicates the fabrication process, often making it nonscalable and non-CMOS compatible. [Figure 1a](#) shows a

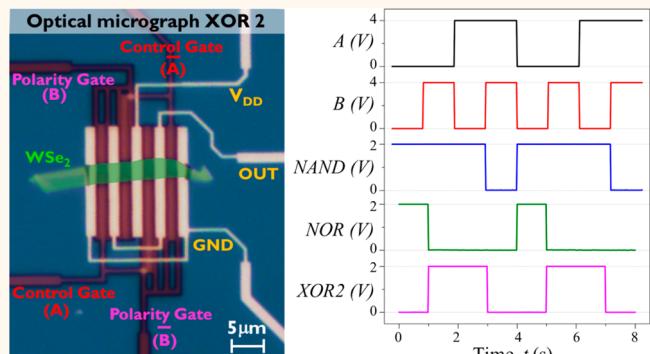

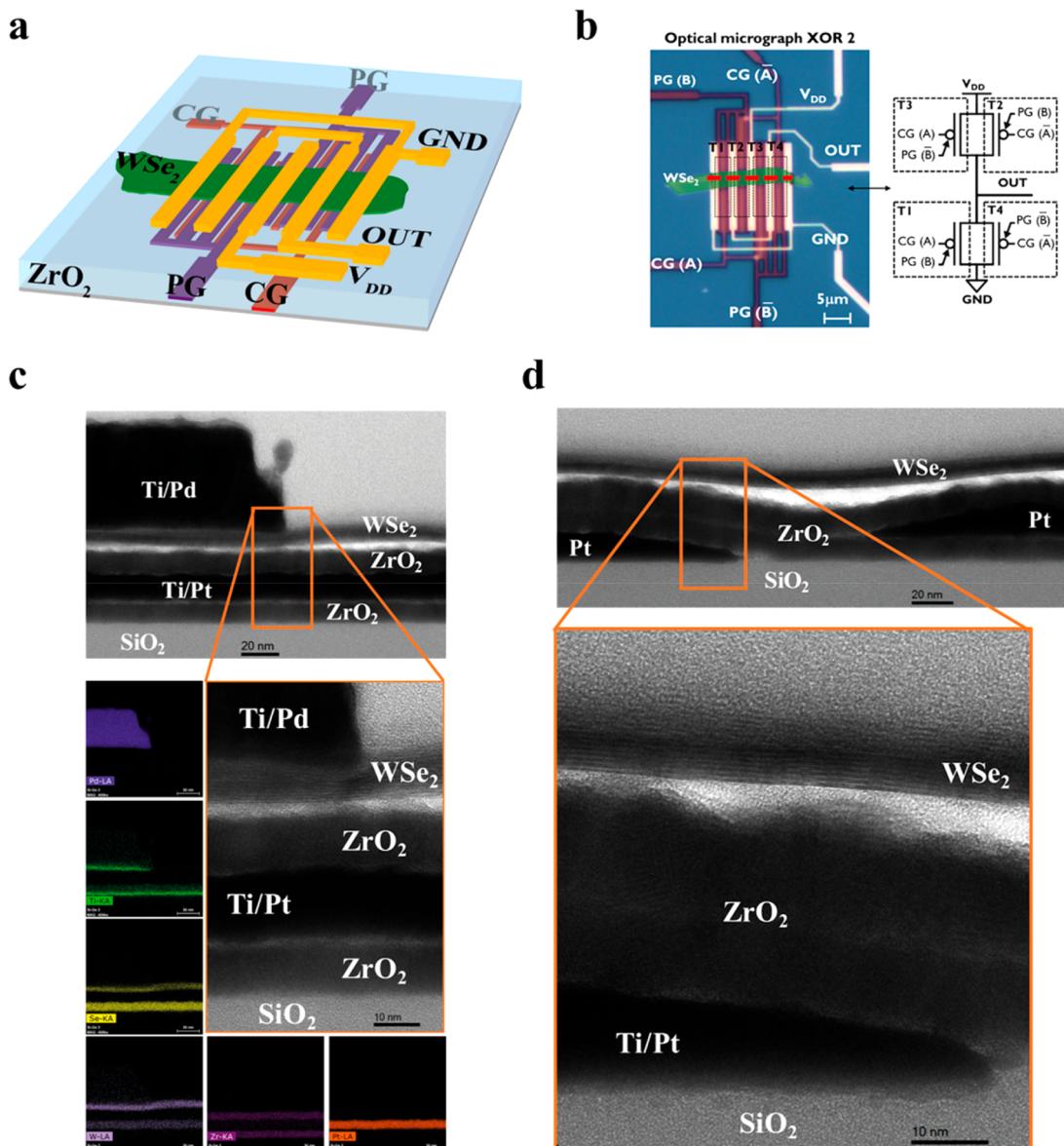

**Figure 1.** 2D-WSe<sub>2</sub> polarity-controllable two-input XOR and cross-sectional TEM with EDX mapping. (a) Cartoon of the WSe<sub>2</sub> 2-input XOR logic gate with platinum buried gates (CG and PG) and titanium/palladium contacts. (b) Optical micrograph of the fabricated 2-input XOR gate, with corresponding circuit schematic highlighting the position of the four transistors and the logic inputs acting on them. The red dashed line indicates the position where the TEM cross sections are taken. (c,d) Cross-sectional TEM image of the contact region with EDX mapping (c) and of the central region of the device, showing the separation between CG and PG (d). Note that the EDX mapping for selenium (Se) and tungsten (W) also shows a false signal due to the overlap between the Se, W, and Pt peaks used during the measurements. Se and W are present only in the top 2D layer. The white region between the ZrO<sub>2</sub> and the WSe<sub>2</sub> is empty space, as confirmed by the lack of C atoms in the region (see Figure S4). It is probably caused by partial delamination of the 2D flake, occurring during the focused ion beam sample preparation.

cartoon schematic of a 4-transistor XOR-2, with an optical micrograph of the device and the corresponding circuit schematic presented in Figure 1b. Each transistor has now two independent gates that can be biased with different logic inputs (e.g., CG (A) is a control gate biased with logic input A and PG (B) is a polarity gate biased with logic value B). The design of the polarity and control gate (PG and CG, respectively) was chosen in order to allow the use of a single WSe<sub>2</sub> flake for the fabrication of each logic gate. Moreover, the PG and CG structures are identical for all the fabricated logic gates (except for the inverter design), creating a universal gating structure that enables a highly regular and flexible design of the logic gates. In fact, different logic gates can be obtained

from the same gating structure by wiring differently the source and drain contacts of the transistors (see Figure S2.2). The fabricated logic gates (NAND, NOR, XOR-2, XOR-3, and MAJ) have four polarity-controllable transistors (except for the INV, which has 2) that share the same semiconducting WSe<sub>2</sub> flake but behave with opposite polarities according to the bias applied to the respective PG. The TEM cross section taken at the contact interface (see Figure 1c) shows the PG buried structure isolated by ZrO<sub>2</sub>, with the 2D-WSe<sub>2</sub> flake on top and the Pd contact. Energy-dispersive X-ray (EDX) spectroscopy confirms the elemental composition of the device. Figure 1d focuses in the central region of the channel and shows the separation (~60 nm) and ZrO<sub>2</sub> isolation between the CG and

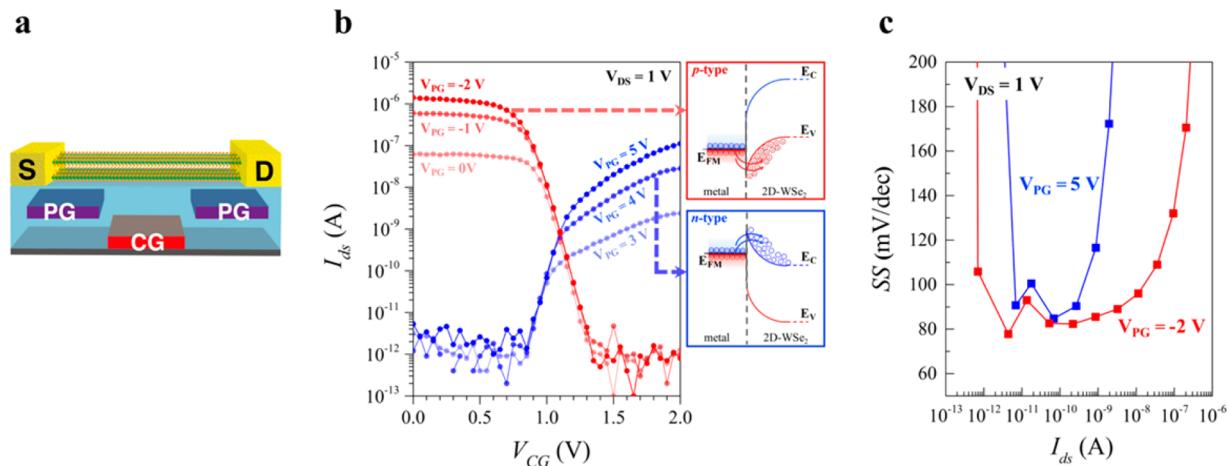

**Figure 2. Polarity-controllable device characteristics** (a) Cartoon of the cross section for a single device, showing the position of the PG and CG with respect to the 2D semiconducting channel. (b) Transfer characteristics showing ambipolar conduction and demonstrating the polarity-controllable behavior. The p-type (n-type) operation is achieved for  $V_{PG} < 0$  V ( $> 3$  V). The insets show the effect of the PG on the Schottky barrier, leading to the injection of only one type of charge carriers. (c) Subthreshold slopes extracted from the transfer characteristics presented in (b) for  $V_{PG} = 5$  V and  $V_{PG} = -2$  V.

the PG structures. The atomic layers of the 2D-WSe<sub>2</sub> are clearly visible in the zoomed-in views of Figure 1c,d, and the thickness of the transferred flake can be estimated to be around 6 nm.

**Characterization of a Single Device.** As mentioned above, the regular and flexible design for the logic gates is made possible by the switching properties of the single polarity-controllable devices that are also enabling the compact fabrication of the XOR-2 gate, which is presented in Figure 1a,b. We will now decompose the behavior of our logic gate and study in detail the switching properties of the single polarity-controllable devices fabricated with the process presented above. Figure 2a shows a 3D schematic cross section of a single device, highlighting the multilayer 2D semiconducting channel and the overlap between the PG and the source and drain contacts, which is necessary to ensure optimal modulation of the Schottky barrier. The CG gate controls the ON/OFF state of the device.

Ambipolar conduction and polarity control behavior are observed, as shown in Figure 2b. When the PG is biased at 0 V or below, holes are favorably injected in the channel and the device behaves as a p-type transistor. Conversely, the transistor is programmed to function as a n-type device when the PG is biased at 3 V and above. In both cases, the CG is able to turn the transistor ON and OFF when swept between 0 and 2 V. It appears that a higher voltage range is needed to flip the transistor polarity, using PG, with respect to the voltage needed to control the potential barrier in the channel, using the CG. We believe this difference stems from the different mechanism that the two gates are exploiting, that is, electrostatic doping of the Schottky junction and modulation of a potential barrier in the channel, with a different band movement factor probably occurring for the two gates. We achieve high ON/OFF ratios of  $10^5$  and  $10^6$  for n- and p-type conduction, respectively, on the same device. The asymmetry between the n- and p-type transfer characteristics, with the p-current around  $10\times$  higher than the n-current, stems from the nonperfect midgap contact alignment, creating asymmetric Schottky barriers for electrons and holes, which was achieved with Ti/Pd contacts. Current flow in a Schottky barrier FET (SB-FET) is the result of two separate conduction mechanism

across the barrier: (i) thermionic emission of carriers over the top of the barrier and (ii) tunneling of charge carriers through the Schottky barrier.<sup>54</sup> Here, the PG acts both at the contact interface between the metal and the semiconductor and also on the region underneath the contact (as can be seen in Figure 1a), which is essential to have an efficient charge injection. It has been recently shown how the gate-induced modulation underneath the contacts (contact gating), provides additional tunneling paths that allow a better carrier injection in the 2D semiconductor.<sup>55</sup> Biasing the PG leads to accumulation of mobile charges underneath and at the contact interface, providing electrostatic doping of the 2D-WSe<sub>2</sub> and considerably thinning the SB. Tunneling of charge carriers through the thinned barrier thus becomes much more favorable. The control of the PG on the barriers is evident as changing the PG bias from 0 to 3 V results in a complete switch of the transistor polarity. However, because the transmission of charge carriers through the barrier depends exponentially on the barrier height (for both thermionic emission and tunneling),<sup>54</sup> it is essential to ensure a midgap contact to have symmetric barrier heights for electrons and holes. Future work will focus in improving the symmetry between the n and p branch, which is a desired feature for circuit operation,<sup>20</sup> exploring different metals or introducing graphene to finely tune the Fermi level alignment at the contacts. Moreover, in our previous studies,<sup>8</sup> we found the Ti/Pd contact to WSe<sub>2</sub> to provide an enhanced electron conduction, with the n-current roughly  $10\times$  higher than that of the p-current. We attribute this difference to the change in the dielectric environment (Al<sub>2</sub>O<sub>3</sub> in our previous work, and ZrO<sub>2</sub> in this work) that could lead to a different doping of the semiconducting 2D-WSe<sub>2</sub>. Further experiments would be needed to assess the influence of the dielectric environment on the conduction properties of 2D materials but are outside of the scope of this work. The extrinsic mobility, extracted from the transfer characteristics (see Supporting Information S3), is 1.5 and  $0.1\text{ cm}^2\text{ V}^{-1}\text{ s}^{-1}$  for hole and electron conduction, respectively. These values are smaller than those reported in the literature for WSe<sub>2</sub>,<sup>31,32</sup> and are determined by the presence of large Schottky barriers at the contacts, the lack of a top high- $\kappa$  passivation, and the presence of interface charges at the ZrO<sub>2</sub>/WSe<sub>2</sub> interface that could increase charge scattering

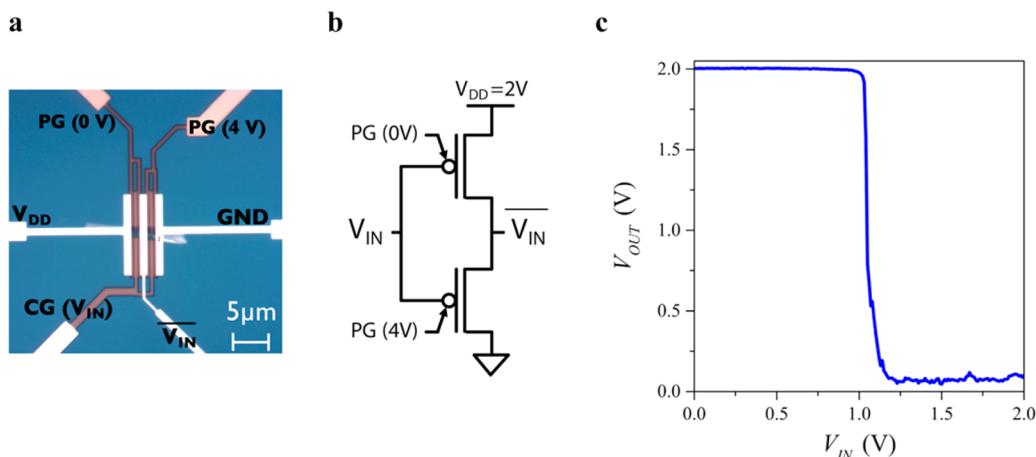

**Figure 3.** Inverter behavior. (a) Optical micrograph of the fabricated inverter with the terminal names reported. (b) Corresponding circuit schematic, showing the voltage bias on the program gates. (c) Measured inverter behavior for  $V_{DD} = 2$  V, showing a sharp transition between the “1” and “0” state around  $V_{DD}/2$ .

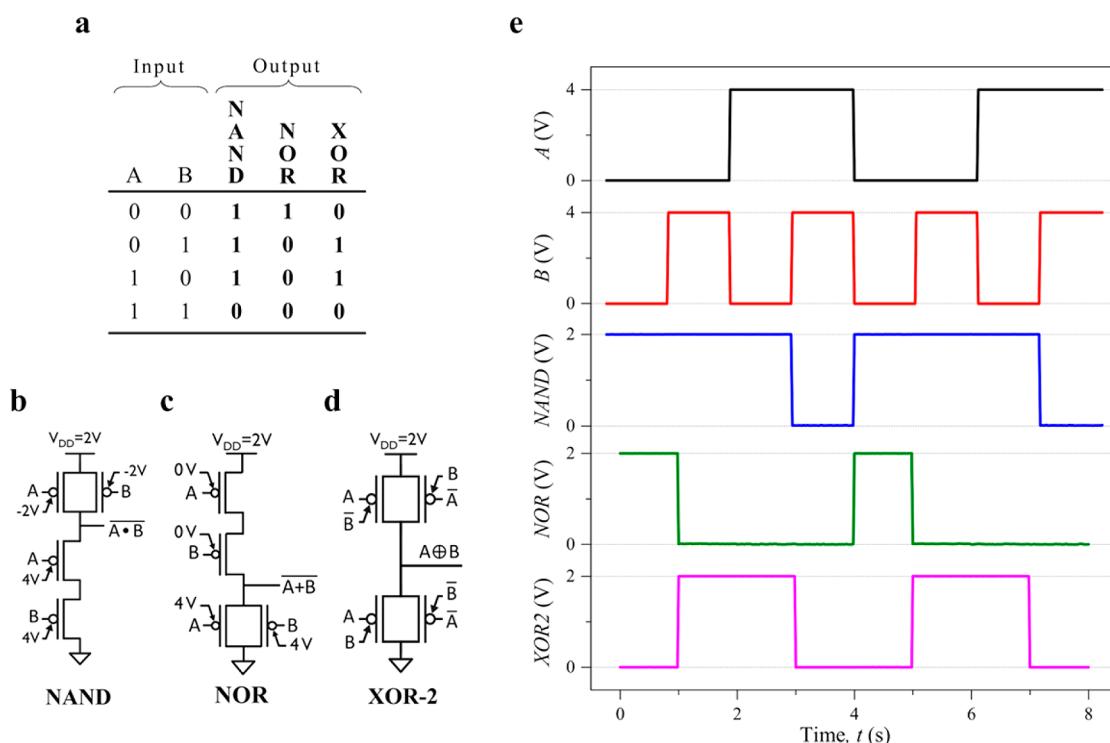

**Figure 4.** Two-input logic gates. (a) Truth table of the NAND, NOR, and XOR-2 logic functions. (b–d) Circuit schematic of the logic gates describing where the logic inputs are applied and showing the fixed bias of the PG in the case of NAND and NOR gates. (e) Experimental waveforms demonstrating the operation of the NAND, NOR, and XOR-2 gates fabricated with polarity-controllable WSe<sub>2</sub> transistors.

phenomena in the channel. Due to the scaled high- $\kappa$  oxide and the use of platinum gates, p-type operation is achieved when biasing the PG and the CG at ground (GND), which is an essential step to ensure the cascability of the devices. Moreover, the use of scaled high- $\kappa$  ZrO<sub>2</sub> creates a high gate capacitance that translates into improved electrostatic control over the channel. We measured subthreshold slopes (SS) below 100 mV/dec over 2 and 4 decades of current for n- and p-type conduction, respectively (see Figure 2c). The minimum SS achieved for both electrons and holes of  $\sim 85$  mV/dec roughly translates into an interface trap density ( $D_{it}$ ) on the order of  $2.5 \times 10^{12}$ , which is in good agreement with previous literature on 2D materials<sup>37</sup> (see Supporting Information S3).

**Demonstration of Logic Gates.** When using polarity-controllable transistors to fabricate INV, NAND, and NOR functions, the program gates are biased at a fixed value, setting the polarity of the transistor, and the gates are arranged in a CMOS-like fashion (see Figure S2.3) with logic inputs only applied on the CG. For the case of an INV (see Figure 3a,b), proper operation of the logic gate is achieved biasing the PG at 0 and 4 V for the p- and n-type transistor, respectively, while having  $V_{DD} = 2$  V. The inverter behavior is verified (see Figure 3c), achieving high inverter gains ( $d(V_{OUT})/d(V_{IN}) > 30$ ), as exemplified by the desirable sharp transition between the high and low state at around  $V_{DD}/2$ . The imbalance in the transition is caused by the different drive current in the n- and p-type

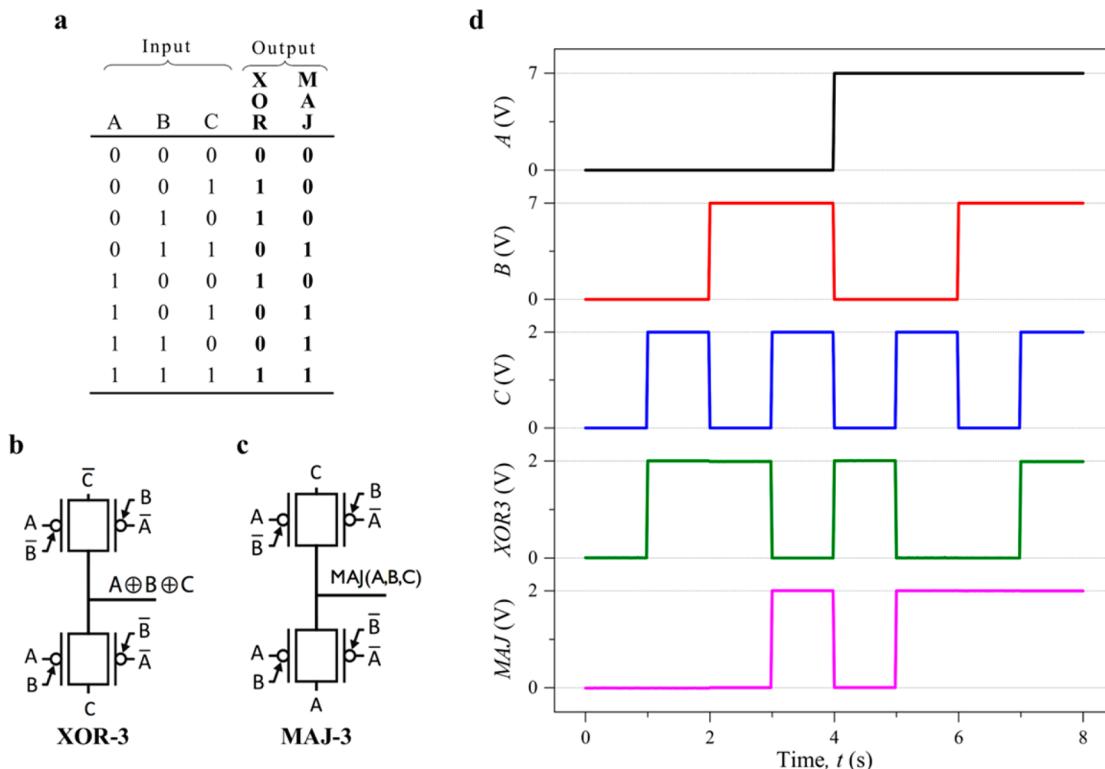

**Figure 5.** Three-input logic gates. (a) Truth table of the XOR-3 and MAJ-3 logic functions. (b–d) Circuit schematic of the logic gates describing where the logic inputs are applied. (e) Experimental waveforms demonstrating the operation of the XOR-3 and MAJ-3 gates fabricated with polarity-controllable WSe<sub>2</sub> transistors. For the MAJ-3 gate, the logic input A applied at the GND terminal is kept between 0 and 2 V, and the input on the gates is kept between 0 and 7 V.

operation mode, as mentioned in the previous section, and can be addressed by finely tuning the contacts.

Using the universal gating structure presented in Figure 1, we are able to fabricate NAND and NOR gates with a conventional CMOS-like design (see Figure 4 and Figure S2.3). The PG of the transistors are biased at a fixed voltage, whereas the logic inputs, A and B, are only applied to the CG of the transistors. We verified the functioning of the NAND and NOR gates for  $V_{DD} = 2$  V, while keeping the bias of the logic inputs between 0 and 4 V. Although for the NOR gate the PG is biased with the same voltage levels of the logic inputs, in the case of the NAND gate, in order to achieve the proper logic behavior, we apply a negative bias of  $-2$  V to the PG of the p-type device. This is most likely caused by some residues on the channel or under the contacts that are preventing the transistor from efficiently conducting holes at  $V_{PG} = 0$  V. Moreover, flake-to-flake variations, both in terms of thickness and defect density, can also contribute to the variation in the bias that needs to be applied to the polarity gates.

At this stage, we have demonstrated how polarity-controllable 2D-WSe<sub>2</sub> transistors can be used to replicate CMOS-like logic gates. However, the real advantage in the use of polarity-controllable transistors with respect to CMOS comes only when exploiting the PG as a logic input, unlocking the enhanced switching properties of the devices. Having a logic input connected to the PG implies that the polarity of the device is no longer fixed and will change at run time according to the logic value of the signal (e.g., p-type for logic “0” and n-type for logic “1”). With this configuration, only possible due to the enhanced expressive switching function of the single

devices (see Figure 2), we can achieve highly compact implementation of XOR and MAJ functions with fewer transistors than what is achievable in conventional CMOS. Disregarding the inverters needed to generate the complemented inputs ( $\bar{A}$  and  $\bar{B}$ ), the XOR-2 is realized with only four polarity-controllable devices, whereas a conventional CMOS design would require eight transistors. We show the operation of the XOR-2 gate, as shown in Figure 4d,e, with all the logic inputs acting between 0 and 4 V, thus assuring the full cascadability of the gate. As shown in the circuit schematic of the XOR-2 gate (see Figure 4d), logic input B is now acting on PG and not on CG as was the case for the NAND and NOR gates. It is important to notice that in contrast to the transfer characteristics presented in Figure 2b, where the CG was only swept between 0 and 2 V, we are now operating both the CG and PG between 0 and 4 V. There is no drawback in further sweeping the CG up to 4 V as the current levels would just remain constant in either p-type OFF state or n-type ON state. By replacing the  $V_{DD}$  and GND terminals with additional inputs, we are also able to demonstrate the logic operation for a highly compact four transistors XOR-3 and MAJ, as shown in Figure 5. These gates were realized on a thicker high- $\kappa$  oxide (20 nm instead of 10 nm), thus requiring a higher voltage range for the logic inputs applied on the gates (between 0 and 7 V). For the proper operation of the logic gates, the signals replacing the  $V_{DD}$  and GND terminals ( $C$ ,  $\bar{C}$ , and  $A$ ,  $C$  for the XOR-3 and MAJ-3, respectively) are instead kept between 0 and 2 V. This limitation can be overcome by further scaling the gate oxide, allowing all logic inputs to have the same voltage range. XOR-3 and MAJ-3 are fundamental logic primitives that are present in virtually any arithmetic operator (consider that a

1-bit adder can be realized by a MAJ-3 gate to generate the carry out and a XOR-3 gate to generate the sum) but are not efficiently realizable in CMOS logic. The possibility of having an efficient realization of these functions enables their use as powerful logic primitives during the logic synthesis flow, providing considerable advantages at circuit level.<sup>50–53</sup>

## CONCLUSIONS

Here, we have investigated the potential advantages in the use of polarity-controllable two-dimensional transistors for next-generation electronic devices, highlighting a path toward the achievement of higher computational densities in two-dimensional electronics. We have shown a complete basis for an effective standard cell library of logic gates (INV, NAND, NOR, XOR-2, XOR-3, and MAJ-3), fabricated with WSe<sub>2</sub> polarity-controllable transistors. These devices, due to the addition of the polarity gate, allowed us to exploit the electrostatic doping of the source and drain Schottky junctions to dynamically set the polarity of the transistors at run time, removing the need for any physical or chemical doping. We tested individual transistors and demonstrated polarity-controllable behavior, achieving ON/OFF ratios  $>10^5$  for both polarities on the same device with subthreshold swings as low as 80 mV/dec. The enhanced switching properties of the single devices allowed us to experimentally demonstrate highly compact and expressive XOR and MAJ gates, with fewer transistors than possible in a conventional CMOS logic.

## MATERIALS AND METHODS

**PMMA Dry Transfer Process.** For the dry-transfer process, we use thick ( $\sim 10 \mu\text{m}$ ) spin-coated poly(methyl methacrylate) (PMMA) as transferring agent. After the flake is selected for transfer, PMMA is spin-coated on the sample and annealed at 165 °C on a hot plate. We then dice the PMMA around the flake using a microengraver, and upon release of the WSe<sub>2</sub>/PMMA stack, we pick it up using a microneedle. The WSe<sub>2</sub>/PMMA stack is then transferred to the target substrate and aligned with respect to the buried program gate by a manual pick-and-drop process. Adhesion of the WSe<sub>2</sub>/PMMA stack is assured by 2 min hot plate annealing at 190 °C. Finally, PMMA is dissolved using dichloromethane, and the sample is cleaned with a hot acetone bath ( $\sim 12$  h) to ensure the absence of PMMA residues. In Figure S1, (i) WSe<sub>2</sub> has been exfoliated on the 20 nm SiO<sub>2</sub>/Si substrate, (ii) and (iii) show schematically the PMMA adhesion to the flake and the PMMA release process. In (iv), the transferred flake is aligned with respect to the PG buried structures on the target substrate. The PMMA is finally dissolved after another annealing step, and (v) shows the transferred flake.

**Device Fabrication.** The WSe<sub>2</sub> flakes are exfoliated from commercially available synthetic crystal, provided by HQ-graphene, using a standard low-tack dicing tape. The flake characterization is performed with a dimension edge AFM from Bruker in tapping mode and with Raman analysis (see Figure S2.1). The fabrication process is depicted in Figure S2.2. We use a double-layer resist consisting of LOR1A and PMMA resist (solution with 3% chlorobenzene) for the patterning of the CG buried gate (i). The LOR1A is spinned for 45 s at 4500 rpm and subsequently baked on a hot plate for 5 min at 190 °C. The PMMA layer is then spinned for 45 s at 4500 and then baked on a hot plate for 5 min at 120 °C. After exposure, the PMMA resist is developed in a 1:1 solution (at 20 °C) of methyl isobutyl ketone and isopropyl alcohol for 42 s. The LOR1A is developed with a 3 s dip in OPD5262 followed by rinsing in deionized water. After the gate metal deposition (2 nm Ti/10 nm Pt), done with a commercial electron gun evaporator tool, lift-off is carried out in hot acetone (50 °C) for around 2 h. The remaining LOR1A resist is then removed in OPD5262. High- $\kappa$  ZrO<sub>2</sub> (10 nm) is deposited with atomic layer deposition at 250 °C using an AMAT Centura III–V module with

TEMAZ/H<sub>2</sub>O precursor (ii), and then the PG structures are defined with the same process described for CG (ii). The PG structures are isolated from the flake with high- $\kappa$  ZrO<sub>2</sub> (10 nm), and the flake is then transferred on top of the buried structures (iii). We use a single-layer PMMA recipe for the patterning of the metal contacts, in order to avoid exposure of the 2D material to OPD5262 (LOR1A developer) and water. The source and drain contacts (2 nm Ti/50 nm Pd) are then evaporated with a commercial electron gun evaporator tool. The Ti is directly in contact with the WSe<sub>2</sub> and acts as an adhesion layer between the 2D flake and the Pd.

An annealing step is then performed at 200 °C for 12 h in a Nabertherm open-tube furnace in vacuum with a constant argon (Ar) flow of 0.5 L/h. The same design of the wiring can be used for the realization of NAND and NOR gates (iv), whereas a different wiring is needed to realize XOR-2, XOR-3, and MAJ gates. Figure S2.3 shows optical micrographs and circuit schematics for all the fabricated logic gates.

**Device Characterization.** All electrical measurements were performed at room temperature in N<sub>2</sub> environment using a Keithley 4200 semiconductor characterization system with a preamplifier probe station. The current measurements were performed with autorange setting allowing for highest accuracy (1% of reading  $\pm 10$  fA) on off-current measurements.

## ASSOCIATED CONTENT

### Supporting Information

The Supporting Information is available free of charge on the ACS Publications website at DOI: [10.1021/acsnano.8b02739](https://doi.org/10.1021/acsnano.8b02739).

Detailed flake transfer procedure schematic, complete fabrication process schematic, optical image and circuit of fabricated logic gates, method for the extraction of interface trap density and detailed EDX map of the device ([PDF](#))

## AUTHOR INFORMATION

### Corresponding Authors

\*E-mail: [giovanni.resta@epfl.ch](mailto:giovanni.resta@epfl.ch).

\*E-mail: [iuliana.radu@imec.be](mailto:iuliana.radu@imec.be).

\*E-mail: [pierre-emmanuel.gaillardon@utah.edu](mailto:pierre-emmanuel.gaillardon@utah.edu).

### ORCID

Giovanni V. Resta: [0000-0003-3996-423X](https://orcid.org/0000-0003-3996-423X)

### Author Contributions

G.V.R. fabricated the experimental devices, performed the measurements, and analyzed the data presented in the paper. Y.B. helped develop the flake transfer procedure. Y.B., D.L., I.P.R., F.C., P.-E.G., and G.D.M. helped interpret the experimental results. G.V.R. wrote the manuscript with contribution from all authors.

### Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

We acknowledge support from the NSF (Grant No. 1644592) and by IMEC core partners' CMOS program. We wish to acknowledge Kim Baumanns and Nicolo Pinna for their technical support in the fabrication of the devices. We thank Abhinav Gaur and Alessandra Leonhardt for the always useful and stimulating discussions.

## REFERENCES

- (1) Dennard, R. H.; Gaensslen, F. H.; Rideout, V. L.; Bassous, E.; LeBlanc, A. R. Design of Ion-Implanted MOSFET's with Very Small Physical Dimensions. *IEEE J. Solid-State Circuits* **1974**, *9*, 256–268.

(2) Moore, G. E. Cramming More Components onto Integrated Circuits. *Electronics* **1965**, *38*, 1–14.

(3) Borkar, S. Designing Reliable Systems from Unreliable Components: The Challenges of Transistor Variability and Degradation. *Micro, IEEE* **2005**, *25*, 10–16.

(4) Li, Y.; Hwang, C. H.; Li, T. Y. Random-Dopant-Induced Variability in Nano-CMOS Devices and Digital Circuits. *IEEE Trans. Electron Devices* **2009**, *56*, 1588–1597.

(5) Shen, M. Y.; Basavalingappa, A.; Hayakawa, T.; Matsugi, H.; Borst, C.; Chang, S. Effect of Ion Flux in Source-Drain Extension Ion Implantation for 10-nm Node FinFet and beyond on 300/450mm Platforms. *IEEE Ion Implantation Technology, IIT* **2016**, *1*.

(6) Qiu, Y.; Cristiano, F.; Huet, K.; Mazzamuto, F.; Fisicaro, G.; La Magna, A.; Quilic, M.; Cherkashin, N.; Wang, H.; Duguay, S.; Blavette, D. Extended Defects Formation in Nanosecond Laser-Annealed Ion Implanted Silicon. *Nano Lett.* **2014**, *14*, 1769–1775.

(7) Das, S.; Appenzeller, J. WSe<sub>2</sub> Field Effect Transistors with Enhanced Ambipolar Characteristics. *Appl. Phys. Lett.* **2013**, *103*, 103501.

(8) Resta, G. V.; Sutar, S.; Balaji, Y.; Lin, D.; Raghavan, P.; Radu, I. P.; Catthoor, F.; Thean, A.; Gaillardon, P.-E.; De Micheli, G. Polarity Control in WSe<sub>2</sub> Double-Gate Transistors. *Sci. Rep.* **2016**, *6*, 29448.

(9) Gaillardon, P.-E.; Amaru, L.; Zhang, J.; De Micheli, G. *Advanced System on a Chip Design Based on Controllable-Polarity FETs*; IEEE, 2014.

(10) De Marchi, M.; Sacchetto, D.; Frache, S.; Zhang, J.; Gaillardon, P.-E.; Leblebici, Y.; De Micheli, G. Polarity Control in Double-Gate, Gate-all-Around Vertically Stacked Silicon Nanowire FETs. *IEEE Electron Devices Meeting (IEDM)* **2012**, 8.4.1.

(11) De Marchi, M.; Zhang, J.; Frache, S.; Sacchetto, D.; Gaillardon, P.-E.; Leblebici, Y.; De Micheli, G. Configurable Logic Gates Using Polarity-Controlled Silicon Nanowire Gate-all-Around FETs. *IEEE Electron Device Lett.* **2014**, *35*, 880–882.

(12) Trommer, J.; Heinzig, A.; Mühle, U.; Löffler, M.; Winzer, A.; Jordan, P. M.; Beister, J.; Baldauf, T.; Geidel, M.; Adolphi, B.; et al. Enabling Energy Efficiency and Polarity Control in Germanium Nanowire Transistors by Individually Gated Nanojunctions. *ACS Nano* **2017**, *11*, 1704–1711.

(13) Lin, Y. F.; Xu, Y.; Wang, S. T.; Li, S. L.; Yamamoto, M.; Aparecido-Ferreira, A.; Li, W.; Sun, H.; Nakaharai, S.; Jian, W. B.; et al. Ambipolar MoTe<sub>2</sub> Transistors and their Applications in Logic Circuits. *Adv. Mater.* **2014**, *26*, 3263–3269.

(14) Nakaharai, S.; Yamamoto, M.; Ueno, K.; Lin, Y. F.; Li, S. L.; Tsukagoshi, K. Electrostatically Reversible Polarity of Ambipolar  $\alpha$ -MoTe<sub>2</sub> Transistors. *ACS Nano* **2015**, *9*, 5976–5983.

(15) Robbins, M. C.; Koester, S. J. Black Phosphorus *p*-and *n*-MOSFETs with Electrostatically Doped Contacts. *IEEE Electron Device Lett.* **2017**, *38*, 285–288.

(16) Larentis, S.; Fallahazad, B.; Movva, H. C.; Kim, K.; Rai, A.; Taniguchi, T.; Watanabe, K.; Banerjee, S. K.; Tutuc, E. Reconfigurable Complementary Monolayer MoTe<sub>2</sub> Field-Effect Transistors for Integrated Circuits. *ACS Nano* **2017**, *11*, 4832–4839.

(17) Lin, Y. M.; Appenzeller, J.; Knoch, J.; Avouris, P. High-Performance Carbon Nanotube Field-Effect Transistor with Tunable Polarities. *IEEE Trans. Nanotechnol.* **2005**, *4*, 481–489.

(18) Nakaharai, S.; Iijima, T.; Ogawa, S.; Suzuki, S.; Tsukagoshi, K.; Sato, S.; Yokoyama, N. Electrostatically-Reversible Polarity of Dual-Gated Graphene Transistors with He Ion Irradiated Channel: Toward Reconfigurable CMOS Applications. In *Electron Devices Meeting (IEDM)*; IEEE International, 2012; pp 2–4.

(19) Heinzig, A.; Slesazeck, S.; Kreupl, F.; Mikolajick, T.; Weber, W. M. Reconfigurable Silicon Nanowire Transistors. *Nano Lett.* **2012**, *12*, 119–124.

(20) Heinzig, A.; Mikolajick, T.; Trommer, J.; Grimm, D.; Weber, W. M. Dually Active Silicon Nanowire Transistors and Circuits with Equal Electron and Hole Transport. *Nano Lett.* **2013**, *13*, 4176–4181.

(21) Wilson, J. A.; Yoffe, A. D. The Transition Metal Dichalcogenides: Discussion and Interpretation of the Observed Optical, Electrical and Structural Properties. *Adv. in. Adv. Phys.* **1969**, *18*, 193–335.

(22) Fiori, G.; Bonaccorso, F.; Iannaccone, G.; Palacios, T.; Neumaier, D.; Seabaugh, A.; Banerjee, S. K.; Colombo, L. Electronics Based on Two-Dimensional Materials. *Nat. Nanotechnol.* **2014**, *9*, 768–779.

(23) Jariwala, D.; Sangwan, V. K.; Lauhon, L. J.; Marks, T. J.; Hersam, M. C. Emerging Device Applications for Semiconducting Two-Dimensional Transition Metal Dichalcogenides. *ACS Nano* **2014**, *8*, 1102–1120.

(24) Wang, Q. H.; Kalantar-Zadeh, K.; Kis, A.; Coleman, J. N.; Strano, M. S. Electronics and Optoelectronics of Two-Dimensional Transition Metal Dichalcogenides. *Nat. Nanotechnol.* **2012**, *7*, 699–712.

(25) Desai, S. B.; Madhvapathy, S. R.; Sachid, A. B.; Llinas, J. P.; Wang, Q.; Ahn, G. H.; Pitner, G.; Kim, M. J.; Bokor, J.; Hu, C.; Wong, H. S. P.; et al. MoS<sub>2</sub> Transistors with 1-Nanometer Gate Lengths. *Science* **2016**, *354*, 99–102.

(26) Nourbakhsh, A.; Zubair, A.; Sajjad, R. N.; Tavakkoli KG, A.; Chen, W.; Fang, S.; Ling, X.; Kong, J.; Dresselhaus, M. S.; Kaxiras, E.; et al. MoS<sub>2</sub> Field-Effect Transistor with Sub-10 nm Channel Length. *Nano Lett.* **2016**, *16*, 7798–7806.

(27) Li, K. S.; Wu, B. W.; Li, L. J.; Li, M. Y.; Cheng, C. C. K.; Hsu, C. L.; Lin, C. H.; Chen, Y. J.; Chen, C. C.; Wu, C. T.; Chen, M. C. MoS<sub>2</sub> U-shape MOSFET with 10 nm Channel Length and Poly-Si Source/Drain Serving as Seed for Full Wafer CVD MoS<sub>2</sub> availability. *IEEE Symposium on VLSI Technology* **2016**, *1*.

(28) Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-Layer MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* **2011**, *6*, 147–150.

(29) Wang, H.; Yu, L.; Lee, Y. H.; Shi, Y.; Hsu, A.; Chin, M. L.; Li, L. J.; Dubey, M.; Kong, J.; Palacios, T. Integrated Circuits based on Bilayer MoS<sub>2</sub> Transistors. *Nano Lett.* **2012**, *12*, 4674–4680.

(30) Cui, X.; Lee, G. H.; Kim, Y. D.; Arefe, G.; Huang, P. Y.; Lee, C. H.; Chenet, D. A.; Zhang, X.; Wang, L.; Ye, F.; et al. Multi-Terminal Transport Measurements of MoS<sub>2</sub> Using a Van der Waals Heterostructure Device Platform. *Nat. Nanotechnol.* **2015**, *10*, 534–540.

(31) Yu, L.; Zubair, A.; Santos, E. J.; Zhang, X.; Lin, Y.; Zhang, Y.; Palacios, T. High-Performance WSe<sub>2</sub> Complementary Metal Oxide Semiconductor Technology and Integrated Circuits. *Nano Lett.* **2015**, *15*, 4928–4934.

(32) Tosun, M.; Chuang, S.; Fang, H.; Sachid, A. B.; Hettick, M.; Lin, Y.; Zeng, Y.; Javey, A. High-Gain Inverters based on WSe<sub>2</sub> Complementary Field-Effect Transistors. *ACS Nano* **2014**, *8*, 4948–4953.

(33) Sachid, A. B.; Tosun, M.; Desai, S. B.; Hsu, C. Y.; Lien, D. H.; Madhvapathy, S. R.; Chen, Y. Z.; Hettick, M.; Kang, J. S.; Zeng, Y.; He, Jr.-H.; Chang, E. Y.; Chueh, Y. L.; Javey, A.; Hu, C. Monolithic 3D CMOS Using Layered Semiconductors. *Adv. Mater.* **2016**, *28*, 2547–2554.

(34) Kang, K.; Xie, S.; Huang, L.; Han, Y.; Huang, P. Y.; Mak, K. F.; Kim, C. J.; Muller, D.; Park, J. High-Mobility Three-Atom-Thick Semiconducting Films with Wafer-Scale Homogeneity. *Nature* **2015**, *520*, 656–660.

(35) Duan, X.; Wang, C.; Shaw, J. C.; Cheng, R.; Chen, Y.; Li, H.; Wu, X.; Tang, Y.; Zhang, Q.; Pan, A.; et al. Lateral Epitaxial Growth of Two-Dimensional Layered Semiconductor Heterojunctions. *Nat. Nanotechnol.* **2014**, *9*, 1024–1030.

(36) Chiappe, D.; Asselberghs, I.; Sutar, S.; Iacovo, S.; Afanas'ev, V.; Stesmans, A.; Balaji, Y.; Peters, L.; Heyne, M.; Mannarino, M.; Vandervorst, W.; Sayan, S.; Huyghebaert, C.; Caymax, M.; Heyns, M.; De Gendt, S.; Radu, I. P.; Thean, A. Controlled Sulfurization Process for the Synthesis of Large Area MoS<sub>2</sub> Films and MoS<sub>2</sub>/WS<sub>2</sub> Heterostructures. *Adv. Mater. Interfaces* **2016**, *3*, 1500635.

(37) Mleczko, M. J.; Zhang, C.; Lee, H. R.; Kuo, H. H.; Magyari-Köpe, B.; Moore, R. G.; Shen, Z. X.; Fisher, I. R.; Nishi, Y.; Pop, E. HfSe<sub>2</sub> and ZrSe<sub>2</sub>: Two-Dimensional Semiconductors with Native High- $\kappa$  Oxides. *Science Adv.* **2017**, *3*, e1700481.

(38) Leonhardt, A.; Chiappe, D.; Asselberghs, I.; Huyghebaert, C.; Radu, I. P.; De Gendt, S. Improving MOCVD MoS<sub>2</sub> Electrical Performance: Impact of Minimized Water and Air Exposure Conditions. *IEEE Electron Device Lett.* **2017**, *38*, 1606–1609.

(39) Gaur, A.; Balaji, Y.; Lin, D.; Adelmann, C.; Van Houdt, J.; Heyns, M.; Mocuta, D.; Radu, I. P. Demonstration of  $2e12 \text{ cm}^{-2}\text{eV}^{-1}$  2D-Oxide Interface Trap Density on Back-Gated MoS<sub>2</sub> Flake Devices with 2.5nm EOT. *Microelectron. Eng.* **2017**, *178*, 145–149.

(40) Sarkar, D.; Xie, X.; Liu, W.; Cao, W.; Kang, J.; Gong, Y.; Kraemer, S.; Ajayan, P. M.; Banerjee, K. A Subthermionic Tunnel Field-Effect Transistor with an Atomically Thin Channel. *Nature* **2015**, *526*, 91–95.

(41) Nourbakhsh, A.; Zubair, A.; Dresselhaus, M. S.; Palacios, T. Transport Properties of a MoS<sub>2</sub>/WSe<sub>2</sub> Heterojunction Transistor and its Potential for Application. *Nano Lett.* **2016**, *16*, 1359–1366.

(42) Balaji, Y.; Smets, Q.; De La Rosa, C. J. L.; Lu, A. K. A.; Chiappe, D.; Agarwal, T.; Lin, D.; Huyghebaert, C.; Radu, I.-P.; Mocuta, D.; Groeseneken, G. Tunneling Transistors based on MoS<sub>2</sub>/MoTe<sub>2</sub> Van der Waals Heterostructures. *IEEE J. Electron Devices Soc.* **2018**, *1*.

(43) Cao, W.; Kang, J.; Sarkar, D.; Liu, W.; Banerjee, K. 2D Semiconductor FETs—Projections and Design for sub-10 nm VLSI. *IEEE Trans. Electron Devices* **2015**, *62*, 3459–3469.

(44) Szabó, Á.; Rhyner, R.; Luisier, M. Ab Initio Simulation of Single-and Few-Layer MoS<sub>2</sub> Transistors: Effect of Electron-Phonon Scattering. *Phys. Rev. B: Condens. Matter Mater. Phys.* **2015**, *92*, 035435.

(45) Resta, G. V.; Agarwal, T.; Lin, D.; Radu, I. P.; Catthoor, F.; Gaillardon, P.-E.; De Micheli, G. Scaling Trends and Performance Evaluation of 2-dimensional Polarity-Controllable FETs. *Sci. Rep.* **2017**, *7*, 45556.

(46) Wachter, S.; Polyushkin, D. K.; Bethge, O.; Mueller, T. A Microprocessor based on a Two-Dimensional Semiconductor. *Nat. Commun.* **2017**, *8*, 14948.

(47) Li, X. X.; Fan, Z. Q.; Liu, P. Z.; Chen, M. L.; Liu, X.; Jia, C. K.; Sun, D. M.; Jiang, X. W.; Han, Z.; Bouchiat, V. Gate-Controlled Reversible Rectifying Behaviour in Tunnel Contacted Atomically-Thin MoS<sub>2</sub> Transistor. *Nat. Commun.* **2017**, *8*, 970.

(48) Gong, C.; Colombo, L.; Wallace, R. M.; Cho, K. The Unusual Mechanism of Partial Fermi Level Pinning at Metal–MoS<sub>2</sub> Interfaces. *Nano Lett.* **2014**, *14*, 1714–1720.

(49) Chuang, H. J.; Tan, X.; Ghimire, N. J.; Perera, M. M.; Chamlagain, B.; Cheng, M. M. C.; Yan, J.; Mandrus, D.; Tománek, D.; Zhou, Z. High Mobility WSe<sub>2</sub> p-and n-Type Field-Effect Transistors Contacted by Highly Doped Graphene for Low-Resistance Contacts. *Nano Lett.* **2014**, *14*, 3594–3601.

(50) Amarú, L.; Gaillardon, P.-E.; De Micheli, G. Biconditional BDD: a Novel Canonical BDD for Logic Synthesis Targeting XOR-Rich Circuits. *IEEE Design, Automation & Test in Europe Conference* **2013**, *1014*.

(51) Amarú, L.; Gaillardon, P.-E.; De Micheli, G. Majority-Inverter Graph: A Novel Data-Structure and Algorithms for Efficient Logic Optimization. In *Proceedings of the 51st Annual Design Automation Conference ACM*, 2014; pp 1–6.

(52) Haaswijk, W.; Soeken, M.; Amarú, L.; Gaillardon, P.-E.; De Micheli, G. A Novel Basis for Logic Rewriting. *22nd IEEE Asia and South Pacific Design Automation Conference (ASP-DAC)*, 2017.

(53) Raitza, M.; Kumar, A.; Völp, M.; Walter, D.; Trommer, J.; Mikolajick, T.; Weber, W. M. Exploiting Transistor-Level Reconfiguration to Optimize Combinational Circuits. In *Proceedings of the Conference on Design, Automation & Test in Europe (DATE)*, 2017; pp 338–343.

(54) Sze, S. M.; Ng, K. K. *Physics of Semiconductor Devices*; John Wiley & Sons, 2006.

(55) Prakash, A.; Ilatikhameneh, H.; Wu, P.; Appenzeller, J. Understanding Contact Gating in Schottky Barrier Transistors from 2D Channels. *Sci. Rep.* **2017**, *7*, 12816.

## NOTE ADDED AFTER ASAP PUBLICATION

After this paper was published ASAP June 29, 2018, a correction was made to Figure S2.2 in the Supporting Information. The corrected version was reposted July 5, 2018.