# Self-Limited and Forming-Free CBRAM Device With Double $\text{Al}_2\text{O}_3$ ALD Layers

Jong Hoon Shin<sup>✉</sup>, Qiwen Wang, and Wei D. Lu<sup>✉</sup>, *Fellow, IEEE*

**Abstract**—Self-limited and forming-free Cu-based CBRAM devices with a double  $\text{Al}_2\text{O}_3$  atomic layer deposition layer (D-ALD) structure were developed. The proposed structure offers desirable properties such as forming free ( $V_{\text{forming}} = V_{\text{SET}}$ ), self-limited resistive switching with very low programming current ( $\sim 10 \text{ nA}$ ), high ON/OFF ratio ( $> 100$ ), and nonlinear  $I-V$  ( $N_{\text{L,read}} \text{ and } N_{\text{L,SET}} \sim 10$ ) at low resistance state. The outstanding performance of D-ALD devices was due to the HT-ALD layer that operates as both a diffusion barrier preventing over injection of Cu ions and a tunneling barrier enabling self-limited programming.

**Index Terms**—CBRAM, RRAM, low-current, nonlinearity, forming-free, self-limited, uniformity.

## I. INTRODUCTION

CONDUCTIVE-BRIDGE random access memory (CBRAM) has been considered as a promising candidate for next generation non-volatile memory, as well as in-memory computing applications due to its properties such as fast speed, low power consumption, high on/off ratio, and high density ( $4\text{F}^2$ ) [1]–[3]. On the other hand, extensive device optimizations still need to be performed to support large-scale implementations [4]–[7]. First, forming-free cells are desired for crossbar operations since high forming voltages could damage cells already formed in the array [8], [9]. In addition, self-limited programming is necessary to ensure cell reliability, since external current compliance (CC) will not be effective in passive crossbar arrays [10], [11]. Low programming current helps mitigate the series resistance issue and reduces the operation power [12], while nonlinear  $I-V$  characteristics in low resistance state (LRS) helps mitigate sneak currents [13], [14].

In this study, a Cu-based CBRAM device with a double  $\text{Al}_2\text{O}_3$  atomic layer deposition (D-ALD) layer structure, consisting of a low-temperature (LT)  $\text{Al}_2\text{O}_3$  ALD switching layer and a high-temperature (HT)  $\text{Al}_2\text{O}_3$  ALD barrier layer, was developed. The proposed D-ALD devices achieved ultra-low self-limited programming current ( $< 100 \text{ nA}$ ), forming-free switching ( $V_{\text{forming}} = V_{\text{SET}}$ ), large on/off ratio ( $\sim 100$ ), reliable switching cycle ( $> 1000$  cycles),  $I-V$  nonlinearity ( $N_{\text{L,read}} \text{ and } N_{\text{L,SET}} \sim 10$ ), and good cycle-to-cycle (C-to-C) and device-to-device (D-to-D) uniformity, using CMOS compatible processes.

Manuscript received August 20, 2018; accepted August 30, 2018. Date of publication September 3, 2018; date of current version September 25, 2018. This work was supported by the National Science Foundation under Grant ECCS-1708700. The review of this letter was arranged by Editor B. Govoreanu. (*Corresponding author: Wei D. Lu*)

The authors are with the Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI 48109 USA (e-mail: [wlu@eecs.umich.edu](mailto:wlu@eecs.umich.edu)).

Color versions of one or more of the figures in this letter are available online at <http://ieeexplore.ieee.org>.

Digital Object Identifier 10.1109/LED.2018.2868459

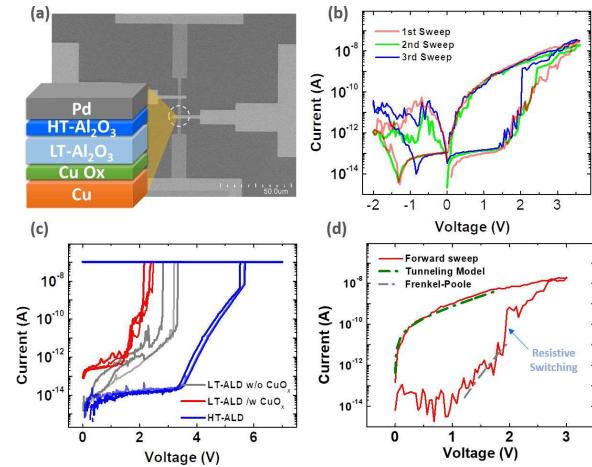

**Fig. 1.** (a) SEM image of Cu/CuO<sub>x</sub>/LT-ALD/HT-ALD/Pd crossbar devices. Inset: the schematic structure of D-ALD devices. (b) Successive  $I-V$  sweeps including the forming process of as-fabricated device (red). (c)  $I-V$  curves of LT-ALD devices without CuO<sub>x</sub> ( $V_{\text{forming}} \sim 3\text{V}$ ), LT-ALD devices with CuO<sub>x</sub> ( $V_{\text{forming}} \sim 2\text{V}$ ), and HT-ALD devices ( $V_{\text{forming}} \sim 5.5\text{V}$ ). Results from three devices are shown for each structure. (d) Fitting of the D-ALD device  $I-V$ . The fitting was limited to below 2.0V where resistive switching occurred.

## II. EXPERIMENTS

The Cu/CuO<sub>x</sub>/LT-ALD/HT-ALD/Pd cells were fabricated in a  $2\mu\text{m} \times 2\mu\text{m}$  two-terminal crossbar structure as shown in Fig. 1(a). The bottom electrode (BE) was defined on top of a SiO<sub>2</sub>/Si substrate by photolithography, followed by e-beam evaporation of 5nm/50nm of NiCr/Cu. The Cu BE was then subjected to O<sub>2</sub> plasma treatment for 2 minutes at 150°C to form a copper oxide layer. 40 cycles ( $\sim 45\text{\AA}$ ) of Al<sub>2</sub>O<sub>3</sub> LT-ALD switching layer was then deposited in an Oxford ALD tool at 110°C using H<sub>2</sub>O recipe, using Al(CH<sub>3</sub>)<sub>3</sub> and H<sub>2</sub>O as metal precursor and oxidizing agent, respectively. The ALD tool was then heated up to 250°C, and 6 cycles ( $\sim 7\text{\AA}$ ) of Al<sub>2</sub>O<sub>3</sub> HT-ALD layer was deposited with plasma recipe using O<sub>2</sub> plasma as oxidizing agent. The Pd top electrode (TE) was formed by e-beam evaporation. The devices were measured by a Keithley 4200 semiconductor parameter analyzer. All switching characteristics were obtained without external CC.

## III. RESULTS AND DISCUSSIONS

In Fig. 1(a), D-ALD device with Cu/CuO<sub>x</sub>/LT-ALD/HT-ALD/Pd structure is illustrated. The CuO<sub>x</sub> layer was found to improve nucleation during growth of the LT-ALD switching layer. Additionally, the Cu ions in the CuO<sub>x</sub> layer facilitates the redox processes involved in conducting filament (CF) formation and thus reduces  $V_{\text{forming}}$  [15], [16]. The thin HT-ALD layer is used as a barrier layer to limit CF growth and reduce the programming current. X-ray reflectance measurements (XRR) show the HT-ALD film has higher

density ( $3.7\text{g}/\text{cm}^3$ ) than the LT-ALD film ( $3.3\text{g}/\text{cm}^3$ ). Resistive switching in HT-ALD was found to be more difficult than in LT-ALD, possibly because of the denser film makes it harder for the inclusion of water molecules to mediate Cu redox processes [17]. As a result, the HT-ALD film can act as a good Cu diffusion barrier layer.

**Fig. 1(b)** shows three consecutive resistive switching curves without CC, starting from the as-fabricated state, with voltage applied on the Cu BE and the TE grounded. Note the non-zero crossing during the negative sweep was caused by a small ( $\sim 0.15\text{pA}$ ) offset current, likely due to discharging from parasitic capacitances as the voltage is decreased. Smooth I-V curves and zero-crossing can be obtained by removing this small current offset. The first I-V sweep from the as-fabricated device leads to a switching to LRS at  $\sim 2\text{V}$ . This  $V_{\text{forming}}$  is the same as the switching voltage in subsequent sweeps, showing forming-free characteristics. The self-limited programming process can be observed from the reliable switching curves - the switching does not lead to uncontrollable ramp up of the current, even without any external CC or added series-resistance to limit the applied voltage. Compared with previous studies on  $\text{Al}_2\text{O}_3$ -based CBRAM that require high  $V_{\text{forming}} \sim 2.3 \times V_{\text{SET}}$  and external CC [6], the forming-free and self-limited programming of D-ALD devices allow more reliable device operation and transistor-free 1S1R crossbar implementations, where low-forming voltage is necessary and external current compliance will be difficult to apply. The I-V curves obtained from the resistive switching cycles are similar to each other, with consistent LRS and high-resistance state (HRS) values, showing good C-to-C uniformity without elaborate control circuitry. I-V nonlinearity  $NL_{\text{read}}$  and  $NL_{\text{SET}}$  of  $\sim 10$  (defined as  $NL_{\text{read}} = I(V_{\text{read}})/I(1/2V_{\text{read}})$  at  $V_{\text{read}} = 1.0\text{V}$  and  $NL_{\text{SET}} = I(V_{\text{SET}})/I(1/2V_{\text{SET}})$  at  $V_{\text{SET}} = 3.0\text{V}$ ) are also observed in the I-V curve in LRS. Due to the very low read current ( $0.1\text{nA}$ ) and the high on-state device resistance ( $> 1\text{G}\Omega$ ), the ground scheme can be successfully applied to arrays during read, while the nonlinearity  $NL_{\text{SET}}$  becomes attractive during write to help reduce the power consumption using the  $V/2$  write scheme during array operation [13], [14].

The desirable performance can be attributed to the role of the layers,  $\text{CuO}_x$ , LT-ALD, and HT-ALD in the device. **Fig. 1(c)** shows forward I-V sweeps obtained from three as-fabricated control devices with different structures until their breakdown.  $\text{Cu}(\text{TE})/\text{LT-ALD}(50\text{ cycles})/\text{Pd}(\text{BE})$  devices without  $\text{CuO}_x$  was used to investigate the role of the  $\text{CuO}_x$  layer. It showed not only higher  $V_{\text{forming}} \sim 3\text{V}$ , but also large D-to-D variations (gray curves) and low yield (5 out of 10 devices were initially shorted). This result can be attributed to poor nucleation of the LT-ALD layer on top of the copper BE that leads to high density of defects such as pin-holes and rough surface [18]. To address this issue, we note copper oxide has been used to improve nucleation of the  $\text{Al}_2\text{O}_3$  layer during ALD growth since hydroxyl (OH) groups can be chemisorbed onto the  $\text{CuO}$  sites and react with the organometallic precursors during ALD [19]–[21]. Hence,  $\text{Cu}(\text{BE})/\text{CuO}_x/\text{LT-ALD}(50\text{ cycles})/\text{Pd}(\text{TE})$  devices with the LT-ALD layer grown on top of  $\text{CuO}_x$  were fabricated. The formation of  $\text{CuO}_x$  was conducted by 2 minutes of exposure to  $\text{O}_2$  plasma. The LT-ALD devices grown on  $\text{CuO}_x$  layer show a low  $V_{\text{forming}}$  close to  $2.0\text{V}$  (red curves) with enhanced uniformity and high yield (all the pristine devices are initially

insulating). Moreover, copper ions ( $\text{Cu}^{2+}$ ) can be more easily supplied from  $\text{CuO}_x$  and diffuse into the  $\text{Al}_2\text{O}_3$  layer compared to the Cu metal case, due to the lower Cu-O bond energy in  $\text{CuO}$  ( $\sim 1.5\text{eV}$ ) compared with that of Cu-Cu metallic bond ( $\sim 2.0\text{eV}$ ) [16], [21]–[23]. Therefore, devices with  $\text{CuO}_x$  as the ion source layer exhibit reduced  $V_{\text{forming}}$ . The low forming voltage of LT-ALD can also be attributed by the effects of  $\text{H}_2\text{O}$  molecules in the LT- $\text{Al}_2\text{O}_3$  film, which has been shown to be more hydrophilic than  $\text{SiO}_2$  [24]. The  $\text{H}_2\text{O}$  molecules absorbed in the LT-ALD layer can facilitate the Cu redox processes, as has been observed in  $\text{SiO}_2$ -based devices [15].

The HT-ALD control devices were fabricated in the same structure as the LT-ALD device, i.e.  $\text{Cu}(\text{BE})/\text{CuO}_x/\text{HT-ALD}(50\text{cycles})/\text{Pd}(\text{TE})$ , by simply replacing the ALD growth condition from  $110^\circ\text{C}$  with  $\text{H}_2\text{O}$  in the LT-ALD device to  $250^\circ\text{C}$  with  $\text{O}_2$  plasma in the HT-ALD device. Since the same number of ALD cycles (50 cycles) for both the HT-ALD device and the LT-ALD device were used, resulting in similar thickness of  $\sim 55\text{ \AA}$ , the difference of I-V the characteristics between LT-ALD devices and HT-ALD devices are mainly due to the ALD film quality. The I-V curves of HT-ALD devices (blue lines) in **Fig. 1(c)** showed very low leakage current ( $\sim 10^{-14}\text{A}$ ) and eventually broke down at a high voltage,  $\sim 5.5\text{V}$ . These results verify that the HT-ALD layer can offer very low leakage current and support high electric field. The closely packed  $\text{Al}_2\text{O}_3$  in HT-ALD films makes it harder to hold water molecules, which have been shown to reduce the activation energy of copper ion migration [17]. These results suggest that HT-ALD can be used as an effective ion diffusion barrier to control the growth of the CF. The excellent insulating quality of the HT-ALD layer is also useful to limit the current and achieve self-compliance during the switching process, as have been verified in the D-ALD devices shown in **Fig. 1(b)**.

The conduction mechanism can be further explained by fitting the I-V curves, as shown in **Fig. 1(d)**. The I-V curve in HRS was fitted to Frenkel-Poole model in the  $1.2\sim 2.0\text{V}$  range (where the current is clearly above the measurement resolution limit), which implies trap-related leakage mechanism in HRS, as shown in **Fig. 1(d)** [25]. The LRS regime can be fitted with direct tunneling, implying the existence of a barrier between the CF and the inert electrode [26]. From the fitting, the tunneling gap and diameter of the CF is estimated to be  $10\text{\AA}$  and  $16\text{\AA}$ , respectively. The tunneling gap of  $10\text{\AA}$  is close to the thickness of the HT-ALD barrier,  $\sim 7\text{\AA}$ .

This analysis supports the hypothesis that the vertical growth of the Cu CF is stopped by the HT-ALD layer, and conduction in the LRS is dominated by tunneling through the barrier layer.

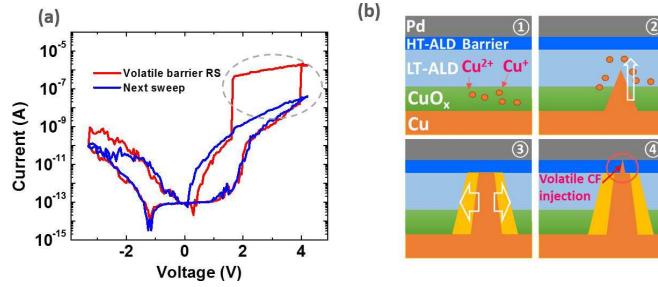

Additional evidence of reliability of the HT-ALD barrier can be observed in **Fig. 2(a)**. Here the applied voltage was continuously applied beyond the typical programming voltage range of  $3\text{V}$ . At  $\sim 4\text{V}$ , Cu ion injection into the HT-ALD barrier layer occurs, leading to abruptly increased current. However, the device recovers the lower LRS current level at  $\sim 1.6\text{V}$  during reverse sweep without suffering from permanent damage, suggesting the partial filament in the HT-ALD layer is not stable and the HT-ALD film can restore its barrier property even if the device is accidentally exposed to high voltage. The instability of the Cu filament in the HT-ALD layer can be understood from the enhanced mechanical stress due to

Fig. 2. (a) An I-V sweep with larger voltage range showing over-programming (red) and the subsequent restoration to the original resistive switching curve (blue) (b) Schematic illustration of the switching mechanism of D-ALD device.

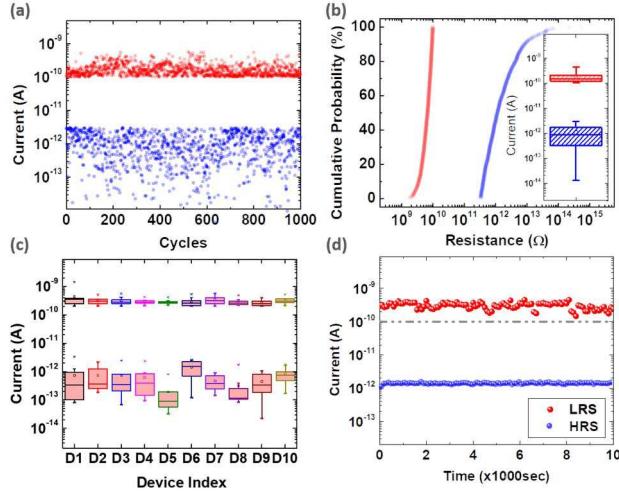

Fig. 3. (a) Pulse cycling test (3.0V/5ms for SET pulse, -2.5V/5ms for RST pulse, and 1.0V for read pulse) (b) Cumulative probability of resistance in LRS and HRS. Inset: box plot showing C-to-C variation. (c) Box plots of on/off current from 10 devices (d) retention test of LRS and HRS at T = 100°C.

the high Young's modulus in the HT-ALD layer [27]–[29]. Enhanced mechanical stress reduces the activation energy for Cu cluster dissolution and makes the CF volatile in the HT-ALD layer.

The resistive switching mechanism of the D-ALD device is illustrated in Fig. 2(b). (1) In the as-fabricated device, Cu ions can be supplied from the CuO<sub>x</sub> layer and migrate into the LT-ALD layer leading to resistive switching with forming-free behavior (2). The growth of the Cu CF in the LT-ALD layer increases the current level from  $\sim 10^{-12}$  A to  $\sim 10^{-9}$  A. The vertical growth is stopped by the HT-ALD layer. (3) Afterwards, lateral CF growth results in gradual increase in device current when the voltage is continuously applied. (4) If the device is accidentally subjected to high voltage, Cu ions may be injected into the HT-ALD layer. However, the injected Cu will not be stable and the HT-ALD layer can recover its barrier property.

Fig. 3(a) shows the cycling test results. The D-ALD device achieved 1000 cycles of resistive switching without any observable degradation of on/off ratio ( $\sim 100$ ). The C-to-C cumulative distribution in Fig. 3(b) shows uniform on-current in the 100–300 pA range (at 1V), without any help of CC. D-to-D uniformity was examined in Fig. 3(c). Box plots measured from 10 different devices show similar distribution in current levels in both LRS and HRS for all devices. The improved uniformity of the devices can be attributed

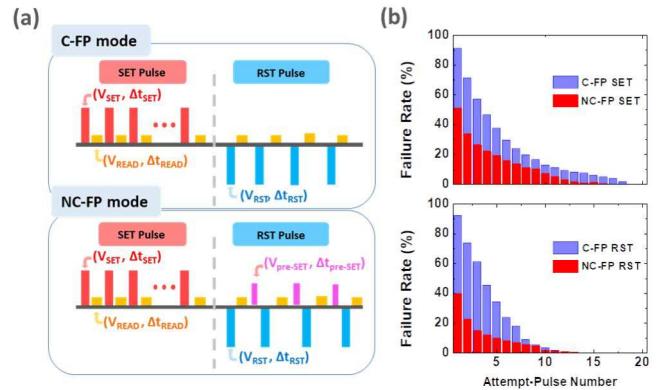

Fig. 4. (a) Schematic pulse sequence consisting of SET pulse train and RST pulse train with verification scheme, for the cumulative fixed pulse mode (C-FP) and the non-cumulative fixed pulse mode (NC-FP). (b) Switching probability of SET (upper) and RESET (lower) for attempts using C-FP (purple) and NC-FP (red). The conditions of SET, RST, pre-SET pulses are fixed at 3.0V/5ms, -2.5V/5ms, and 2.0V/5ms, respectively.

to the uniformity of the deposited ALD layers, including both the LT-ALD switching layer and the HT-ALD barrier layer. In addition, retention over  $10^4$  seconds was obtained at 100°C (Fig.3(d)).

Finally, we examined the effects of the pulse programming algorithms on device operation. The standard pulse programming method is the cumulative fixed pulse (C-FP) mode, a commonly-used write-verification method, consisting of 3.0V/5ms SET pulses followed by 1.0V read pulses for verification during SET, and -2.5V/5ms RESET (RST) pulses and subsequent read pulses during RESET (top panel of Fig.4(a)). To optimize device operation, the RESET sequence was changed following [30]. When the device was not erased after an RST pulse, a positive voltage pulse (pre-SET pulse) (2.0V/5ms) was applied prior to the subsequent RST pulse (bottom panel of Fig.4(a)). This programming method is called non-cumulative fixed pulse (NC-FP) mode [30]. Compared with C-FP mode, the application of the NC-FP mode lowered the switching failure rate, defined as the probability of resistive switching not being successful after a sequence of attempt SET or RST pulses, as shown in Fig.4(b) and improved the endurance from  $\sim 200$  to  $> 1000$ . It is believed that the pre-SET pulses help the Cu atoms escape from the metastable locations that may favor forward migration vs. backward migration. The reduction of the gap size due to the pre-SET pulse also increases the field during the subsequent RESET pulse and facilitates the subsequent removal of the Cu atoms. This approach additionally improves SET reliability, likely due to reduction of residual Cu ions in the LT-ALD layer and the reduced stress from the reduced number of RST attempts.

#### IV. CONCLUSIONS

Cu-based CBRAM devices with double Al<sub>2</sub>O<sub>3</sub> ALD layers have been developed. The D-ALD devices achieved self-limited current, forming free, high on/off ratio, good uniformity, nonlinear I-V at LRS, and robust pulse switching. The roles of CuO<sub>x</sub> and HT-ALD layers were investigated. The promising results from the D-ALD devices help advance of the CBRAM crossbar arrays for storage and novel computing applications.

## REFERENCES

- [1] R. Fackenthal, M. Kitagawa, W. Otsuka, K. Prall, D. Mills, K. Tsutsui, J. Javanifard, K. Tedrow, T. Tushima, Y. Shibahara, and G. Hush, "A 16 Gb ReRAM with 200MB/s write and 1 GB/s read in 27 nm technology," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2014, pp. 338–339, doi: [10.1109/ISSCC.2014.6757460](https://doi.org/10.1109/ISSCC.2014.6757460).

- [2] M. Zidan, Y. Jeong, J. H. Shin, C. Du, Z. Zhang, and W. Lu, "Field-programmable crossbar array (FPCA) for reconfigurable computing," *IEEE Trans. Multi-Scale Comput. Syst.*, in press, Jun. 2017, doi: [10.1109/TMCS.2017.2721160](https://doi.org/10.1109/TMCS.2017.2721160).

- [3] B. Chen, F. Cai, J. Zhou, W. Ma, P. Sheridan, and W. D. Lu, "Efficient in-memory computing architecture based on crossbar arrays," in *IEDM Tech. Dig.*, Dec. 2015, pp. 17.5.1–17.5.4, doi: [10.1109/IEDM.2015.7409720](https://doi.org/10.1109/IEDM.2015.7409720).

- [4] S. Gaba, F. Cai, J. Zhou, and W. Lu, "Ultralow sub-1-nA operating current resistive memory with intrinsic non-linear characteristics," *IEEE Electron Device Lett.*, vol. 35, no. 12, pp. 1239–1241, 2014, doi: [10.1109/LED.2014.2363618](https://doi.org/10.1109/LED.2014.2363618).

- [5] J. Zhou, F. Cai, Q. Wang, B. Chen, S. Gaba, and W. D. Lu, "Very low-programming-current RRAM with self-rectifying characteristics," *IEEE Electron Device Lett.*, vol. 37, no. 4, pp. 404–407, Apr. 2016, doi: [10.1109/LED.2016.2530942](https://doi.org/10.1109/LED.2016.2530942).

- [6] A. Belmonte, U. Celano, Z. Chen, J. Radhakrishnan, A. Redolfi, S. Clima, O. Richard, H. Bender, G. S. Karl, W. Vandervorst, and L. Goux, "Voltage-controlled reverse filament growth boosts resistive switching memory," *Nano Res.*, vol. 11, no. 8, pp. 4017–4025, 2018, doi: [10.1109/NANO.2015.7388967](https://doi.org/10.1109/NANO.2015.7388967).

- [7] I. Valov, "Interfacial interactions and their impact on redox-based resistive switching memories (ReRAMs)," *Semicond. Sci. Technol.*, vol. 32, p. 093006, Aug. 2017, doi: [10.1088/1361-6641/aa78cd](https://doi.org/10.1088/1361-6641/aa78cd).

- [8] D. S. Jeong, B. J. Choi, and C. S. Hwang, "Electroforming processes in metal oxide resistive switching cells," in *Resistive Switching: From Fundamentals of Nanoionic Redox Processes to Memristive Device Applications*. Weinheim, Germany: Wiley-VCH Verlag GmbH & Co. KGaA, 2016, pp. 289–316, doi: [10.1002/9783527680870.ch10](https://doi.org/10.1002/9783527680870.ch10).

- [9] A. Grossi, D. Walczyk, C. Zambelli, E. Miranda, P. Olivo, V. Stikanov, A. Feriani, J. Suñé, G. Schoof, R. Kraemer, B. Tillack, A. Fox, T. Schroeder, C. Wenger, and C. Walczyk, "Impact of intercell and intracell variability on forming and switching parameters in RRAM arrays," *IEEE Trans. Electron Devices*, vol. 62, no. 8, pp. 2502–2509, Aug. 2015, doi: [10.1109/TED.2015.2442412](https://doi.org/10.1109/TED.2015.2442412).

- [10] S. H. Jo, T. Kumar, C. Zitlaw, and H. Nazarian, "Self-limited RRAM with ON/OFF resistance ratio amplification," in *Proc. VLSI Technol. Symp.*, Jun. 2015, pp. T128–T129, doi: [10.1109/VLSIT.2015.7223715](https://doi.org/10.1109/VLSIT.2015.7223715).

- [11] D. Ielmini, "Modeling the universal set/reset characteristics of bipolar RRAM by field-and temperature-driven filament growth," *IEEE Trans. Electron Devices*, vol. 58, no. 12, pp. 4309–4317, Dec. 2011, doi: [10.1109/TED.2011.2167513](https://doi.org/10.1109/TED.2011.2167513).

- [12] S. Agarwal, O. D. Parekh, T.-T. Quach, C. D. James, J. B. Aimone, and M. Marinella, "The energy scaling advantages of RRAM crossbars," in *Proc. 4th Berkeley Symp. Energy Efficient Electron. Syst. (E3S)*, Oct. 2015, pp. 1–3, doi: [10.1109/E3S.2015.7336818](https://doi.org/10.1109/E3S.2015.7336818).

- [13] S. Kim, J. Zhou, and W. D. Lu, "Crossbar RRAM arrays: Selector device requirements during write operation," *IEEE Trans. Electron Devices*, vol. 61, no. 8, pp. 2820–2826, Aug. 2014, doi: [10.1109/TED.2014.2327514](https://doi.org/10.1109/TED.2014.2327514).

- [14] J. Zhou, K. H. Kim, and W. Lu, "Crossbar RRAM arrays: Selector device requirements during read operation," *IEEE Trans. Electron. Devices*, vol. 61, no. 5, pp. 1369–1376, 2014, doi: [10.1109/TED.2014.2310200](https://doi.org/10.1109/TED.2014.2310200).

- [15] T. Tsuruoka, K. Terabe, T. Hasegawa, I. Valov, R. Waser, and M. Aono, "Effects of moisture on the switching characteristics of oxide-based, gapless-type atomic switches," *Adv. Funct. Mater.*, vol. 22, no. 1, pp. 70–77, Jan. 2012, doi: [10.1002/adfm.201101846](https://doi.org/10.1002/adfm.201101846).

- [16] B. G. Willis and D. V. Lang, "Oxidation mechanism of ionic transport of copper in  $\text{SiO}_2$  dielectrics," *Thin Solid Films* vol. 67, pp. 284–293, Nov. 2004, doi: [10.1016/j.tsf.2004.04.028](https://doi.org/10.1016/j.tsf.2004.04.028).

- [17] T. Tsuruoka, I. Valov, S. Tappertzhofen, J. van den Hurk, T. Hasegawa, R. Waser, and M. Aono, "Redox reactions at  $\text{Cu}/\text{Ag}/\text{Ta}_2\text{O}_5$  interfaces and the effects of  $\text{Ta}_2\text{O}_5$  film density on the forming process in atomic switch structures," *Adv. Funct. Mater.*, vol. 25, no. 40, pp. 6374–6381, Oct. 2015, doi: [10.1002/adfm.201500853](https://doi.org/10.1002/adfm.201500853).

- [18] Y. Zhang, J. A. Bertrand, R. Yang, S. M. George, and Y. C. Lee, "Electroplating to visualize defects in  $\text{Al}_2\text{O}_3$  thin films grown using atomic layer deposition," *Thin Solid Films*, vol. 517, pp. 3269–3272, Apr. 2009, doi: [10.1016/j.tsf.2008.12.052](https://doi.org/10.1016/j.tsf.2008.12.052).

- [19] S. M. George, "Atomic layer deposition: An overview," *Chem. Rev.*, vol. 110, no. 1, pp. 111–131, 2010, doi: [10.1021/cr900056b](https://doi.org/10.1021/cr900056b).

- [20] Y. Xie and C. O. Huber, "Electrocatalysis and amperometric detection using an electrode made of copper oxide and carbon paste," *Anal. Chem.*, vol. 63, no. 17, pp. 1714–1719, 1991, doi: [10.1021/ac00017a012](https://doi.org/10.1021/ac00017a012).

- [21] H. B. Lv, M. Yin, P. Zhou, T. A. Tang, B. A. Chen, Y. Y. Lin, A. Bao, and M. H. Chi, "Improvement of endurance and switching stability of forming-free  $\text{Cu}_x\text{O}$  RRAM," in *Proc. 23rd IEEE NVSMW ICMTD*, Apr. 2008, pp. 52–53, doi: [10.1109/NVSMW.2008.21](https://doi.org/10.1109/NVSMW.2008.21).

- [22] H. Häkkinen, M. Moseler, and U. Landman, "Bonding in Cu, Ag, and Au clusters: Relativistic effects, trends, and surprises," *Phys. Rev. Lett.*, vol. 89, p. 033401, Jul. 2002, doi: [10.1103/PhysRevLett.89.033401](https://doi.org/10.1103/PhysRevLett.89.033401).

- [23] D.-Y. Cho, S. Tappertzhofen, R. Waserab, and I. Valov, "Bond nature of active metal ions in  $\text{SiO}_2$ -based electrochemical metallization memory cells," *Nanoscale*, vol. 5, no. 5, 1781–1784, 2013, doi: [10.1039/c3nr34148h](https://doi.org/10.1039/c3nr34148h).

- [24] M. Takeuchi, L. Bertinetti, G. Martra, S. Coluccia, and M. Anpo, "Evaluation of the adsorption states of  $\text{H}_2\text{O}$  on oxide surfaces by vibrational absorption: Near- and mid-infrared spectroscopy," *J. Near Infr. Spectrosc.*, vol. 17, no. 6, pp. 373–384, Aug. 2009, doi: [10.1255/jnirs.843](https://doi.org/10.1255/jnirs.843).

- [25] M. Specht, M. Städle, S. Jakschik, and U. Schröder, "Transport mechanisms in atomic-layer-deposited  $\text{Al}_2\text{O}_3$  dielectrics," *Appl. Phys. Lett.*, vol. 84, no. 16, pp. 3076–3078, Apr. 2004, doi: [10.1063/1.1703840](https://doi.org/10.1063/1.1703840).

- [26] R. Stratton, "Volt-current characteristics for tunneling through insulating films," *J. Phys. Chem. Solids*, vol. 23, no. 9, pp. 1177–1190, 1962, doi: [10.1016/0022-3697\(62\)90165-8](https://doi.org/10.1016/0022-3697(62)90165-8).

- [27] S. Ambrogio, S. Balatti, S. Choi, and D. Ielmini, "Impact of the mechanical stress on switching characteristics of electrochemical resistive memory," *Adv. Mater.*, vol. 26, no. 23, pp. 3885–3892, 2014, doi: [10.1002/adma.201306250](https://doi.org/10.1002/adma.201306250).

- [28] P. Auerkari, "Mechanical and physical properties of engineering alumina ceramics," *VTT Manuf. Technol. Res. Notes*, Tech. Res. Center Finland, Espoo, Finland, 2016, vol. 1792, pp. 14–15.

- [29] S. Menzel, P. Kaupmann, and R. Waser, "Understanding filamentary growth in electrochemical metallization memory cells using kinetic Monte Carlo simulations," *Nanoscale*, vol. 7, no. 29, pp. 12673–12681, Aug. 2015, doi: [10.1039/C5NR02258D](https://doi.org/10.1039/C5NR02258D).

- [30] A. Belmonte, A. Fantini, A. Redolfi, M. Houssa, M. Jurczak, and L. Goux, "Optimization of the write algorithm at low-current ( $10\mu\text{A}$ ) in  $\text{Cu}/\text{Al}_2\text{O}_3$ -based conductive-bridge RAM," in *Proc. 45th Eur. Solid State Device Res. Conf. (ESSDERC)*, Sep. 2015, pp. 114–117, doi: [10.1109/ESSDERC.2015.7324726](https://doi.org/10.1109/ESSDERC.2015.7324726).