# Integrated Circuits Comprising Patterned Functional Liquids

Bhagwati Prasad, Georg Pfanzelt, Evangelos Fillis-Tsirakis, Michael J. Zachman, Lena F. Kourkoutis, and Jochen Mannhart\*

**Solid-state heterostructures are the cornerstone of modern electronics. To enhance the functionality and performance of integrated circuits, the spectrum of materials used in the heterostructures is being expanded by an increasing number of compounds and elements of the periodic table. While the integration of liquids and solid–liquid interfaces into such systems would allow unique and advanced functional properties and would enable integrated nanoionic circuits, solid-state heterostructures that incorporate liquids have not been considered thus far. Here solid-state heterostructures with integrated liquids are proposed, realized, and characterized, thereby opening a vast, new phase space of materials and interfaces for integrated circuits. Devices containing tens of microscopic capacitors and field-effect transistors are fabricated by using integrated patterned NaCl aqueous solutions. This work paves the way to integrated electronic circuits that include highly integrated liquids, thus yielding a wide array of novel research and application opportunities based on microscopic solid/liquid systems.**

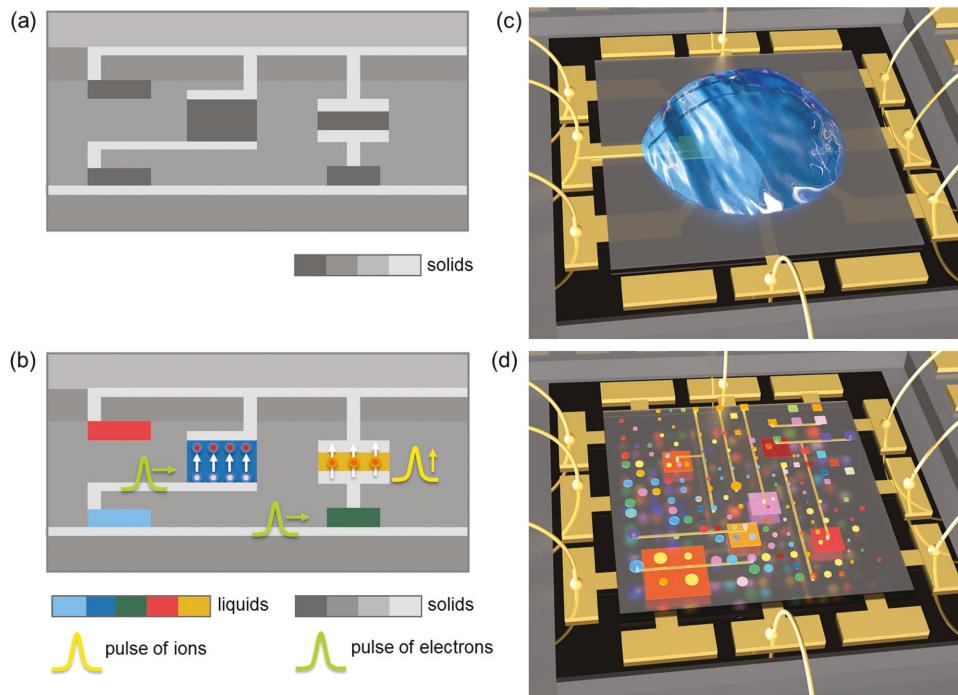

Intriguing phenomena in biology, chemistry, and physics occur when states of matter—solid, liquid, gas, and plasma—are combined. Thus, amazing possibilities would emerge if it were possible to incorporate liquids at microscopic length scales into integrated circuits (for an illustration, see **Figure 1**). Enabling integrated circuitry to include liquids would introduce a new phase of matter to the spectrum of materials currently available for solid-state devices, and thereby qualitatively extend their range of properties and functionalities. Integrated circuits that comprise microscopic liquid volumes will unlock numerous innovative applications of heterostructures in physics, chemistry, and biology.

Dr. B. Prasad, Dr. G. Pfanzelt, Dr. E. Fillis-Tsirakis, Prof. J. Mannhart

Max Planck Institute for Solid State Research

70569 Stuttgart, Germany

E-mail: j.mannhart@kfk.mpg.de

M. J. Zachman, Prof. L. F. Kourkoutis

School of Applied and Engineering Physics

Cornell University

Ithaca, NY 14853, USA

Prof. L. F. Kourkoutis

Kavli Institute for Nanoscale Science

Cornell University

Ithaca, NY 14853, USA

The ORCID identification number(s) for the author(s) of this article can be found under <https://doi.org/10.1002/adma.201802598>.

DOI: 10.1002/adma.201802598

Labs-on-a-chip already combine liquids and solids in microfluidic chips (for an overview, see, e.g., ref. [1]). In labs-on-a-chip, fluids are moved and analyzed, primarily by employing lithographically patterned polymer or silicon structures. Compared to labs-on-a-chip, solid-state heterostructures used in integrated circuits have very different tasks, such as computing, data storage, and control. They therefore draw on different architectures than labs-on-a-chip, are built with different technologies, and, as their name says, are created from solids.

To take advantage of the large polarization achievable at liquid–solid interfaces, solid-state field-effect transistors (FETs) are already being fabricated in which the gate dielectric consists of water gels<sup>[2]</sup> or solid-state electrolytes such as water-infiltrated nanoporous  $12\text{CaO} \times 7\text{Al}_2\text{O}_3$  glass.<sup>[3]</sup> Moreover, liquid-gated graphene FETs have been fabricated by coating the graphene to position millimeter-sized droplets of NaCl aqueous solutions as gate dielectrics on sample surfaces.<sup>[4]</sup> Numerous devices have furthermore been successfully manufactured in which gels were printed or photo-patterned (see, e.g., refs. [5,6]). In these devices and in the pioneering electrolyte-gated FETs,<sup>[7–18]</sup> liquids and solids were combined to enhance functional properties or to achieve new ones. Further progress resulting from combining liquids and solids in devices could be accelerated if it were possible to integrate liquids into solid-state heterostructures. The liquids would be protected from interacting with the atmospheric environment, and by using thin-film technologies small volumes of different liquids could be positioned at microscopically defined locations. The idea of genuine integration of liquids in solid heterostructures such as illustrated in Figure 1, has—to our knowledge—not yet been pursued. The basic question is how liquids can be patterned and overgrown with solid layers. Here we demonstrate successful integration of liquids into heterostructure devices and report on their properties and potential.

The path we have explored to solve both problems of patterning the liquids and overgrowing them is to first grow solid precursors of the liquids, and then to liquefy them after heterostructure growth. Solid–liquid transitions may, for example, be achieved for specific compounds by cracking chemical bonds with photon irradiation. In the work discussed here, we implemented a cryogenic process and deposited

**Figure 1.** Schematics of integrated heterostructures comprising functional liquids. a) Exemplary cross section of a solid-state heterostructure comprising several materials. b) Sketch of envisioned solid-state/liquid-state heterostructures. Analogous to (a), this cross section illustrates the freedom of design and advances achievable if microscopic volumes of liquids (colored) were integrated into heterostructures. In the liquid volumes, for example, ions may create electric double layers (center) or move across gaps (sketch at right). c) Illustration of a typical state-of-the-art sample setup used for ionic gating. A macroscopic drop of an electrolyte (blue) dropped onto the sample provides the gate liquid. d) Sketch illustrating the vision of a sample containing integrated, microscopic liquid volumes, as opposed to (c). Different liquids patterned into distinct shapes may be placed onto the sample at well-determined locations and then overgrown by subsequent layers.

frozen liquid which we subsequently melted and restructured (Figure S1, Supporting Information; Experimental Section). To explore the feasibility and potential of heterostructures with integrated liquids, we implemented integrated electric double-layer capacitors and integrated liquid-gated FETs as test vehicles. We selected the liquid for its compatibility with film growth processes, and to offer large polarizations and fast switching. These requirements are fulfilled by water (see, e.g., ref. [13]) and NaCl aqueous solutions, which can be grown by thermal evaporation, have polarizations of several  $\mu\text{F cm}^{-2}$  and switching delays below 100  $\mu\text{s}$  (Figure S2a, Supporting Information). Control experiments were performed by using macroscopic drops applied to large parts of the device surface (Supporting Information). This is the process used today to fabricate liquid-gated FETs, for example, to explore phase transitions in quantum matter (see, e.g., refs. [10,15–17,19–24]).

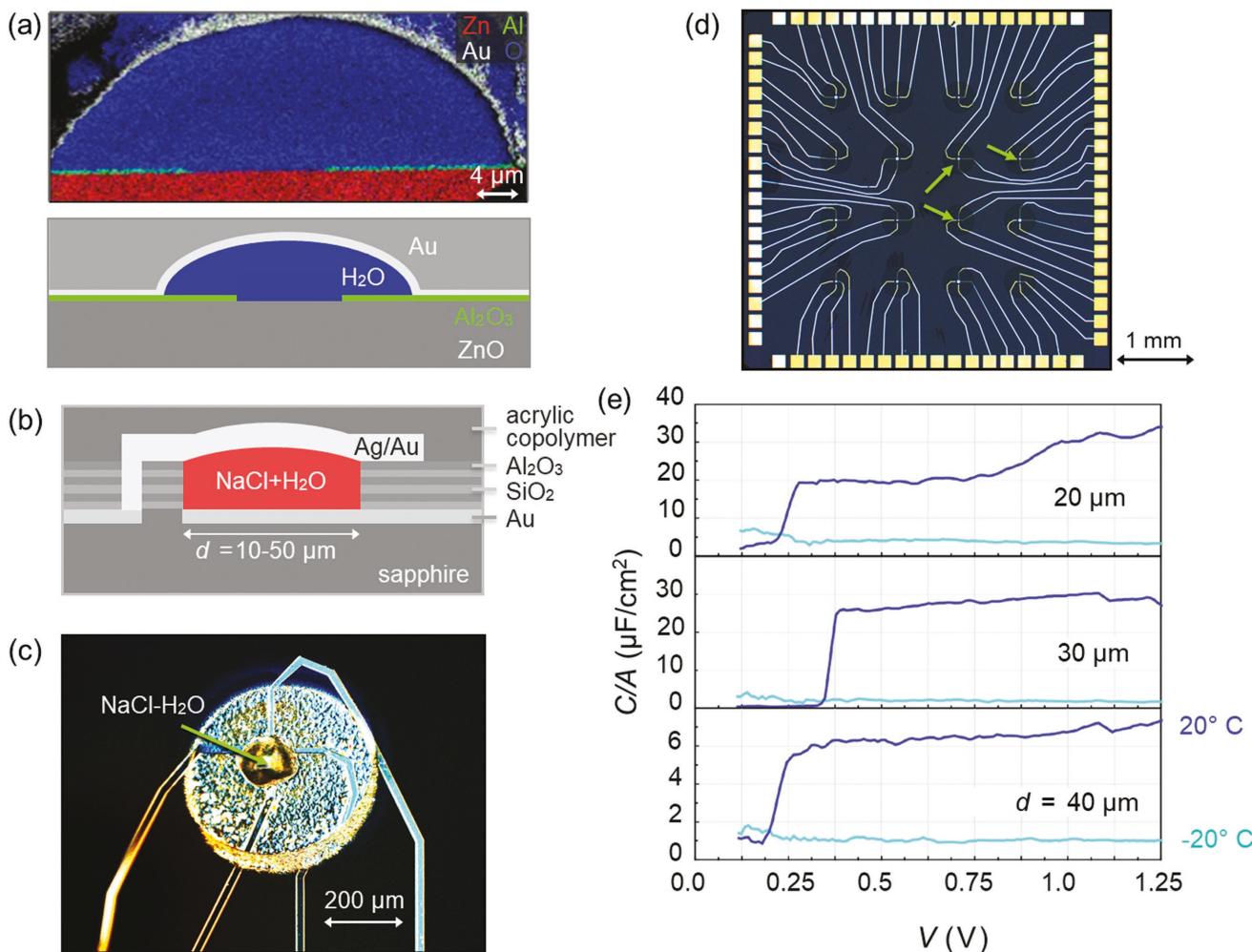

Integration of liquids into heterostructure using our cryogenic process required optimization of device architectures, materials, and growth conditions (see Experimental Section) to overcome the following three key challenges: i) encapsulating the liquid such as to withstand the liquid–solid volume change and the thermal expansion differences, ii) forming contacts at the liquid–solid interface over the microsized areas available, and iii) avoiding undesirable motion of the liquid during sample fabrication. Nanoscale characterization of the surfaces and interiors of test devices by cryo-scanning electron microscopy (cryo-SEM) and cryo-focused ion beam (cryo-FIB)

techniques, which preserve the frozen liquids, showed the aqueous solution to be intact and present in the desired areas throughout the interior of the investigated devices (Figure 2a).

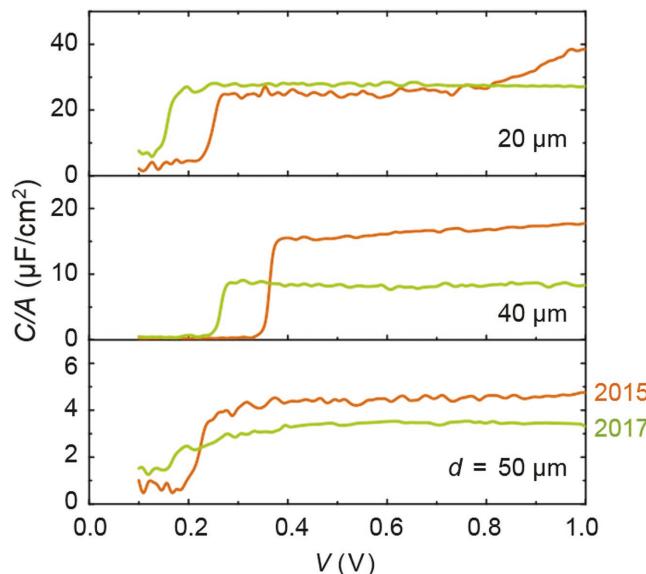

A typical capacitor chip contains devices of various sizes. If operated below the threshold voltage of water decomposition (1.23 V), the devices performed over hundreds of measurement cycles reproducibly for 2 weeks, including several cycles of freezing and warming. As known from bulk samples, the device characteristics showed slight drifts in consecutive measurement sweeps, consistent with the time needed for  $\text{Na}^+$  and  $\text{Cl}^-$  ions to relax in the bulk aqueous solution, the original behavior being recovered again when remeasuring the devices after a day or sloshing the device gently. After 2 years of unattended storage in air on a shelf, the capacitors showed nominally the characteristics of the devices after 2 weeks of experimenting (Figure 3). The room-temperature capacitances ( $5\text{--}40 \mu\text{F cm}^{-2}$ ) far exceeded those achieved with the bulk-drop technique ( $\approx 2\text{--}3 \mu\text{F cm}^{-2}$ ), but varied over a wider range. From their measured electric properties, we conclude that this variation is mainly caused by the electrolyte in some devices not being in contact with the full area of an electrode. Additional variations likely originate from differences of the NaCl concentrations in the device liquids. The high values of the capacitances agree with those of an electric double layer. In a control measurement, we cooled the devices below the freezing temperature. The capacitance collapsed by a factor of 20–25 to the value expected for the parasitic capacitance of the circuits, thus demonstrating that water had been successfully

**Figure 2.** Capacitors with integrated liquids. a) Cryo energy-dispersive X-ray (Cryo-EDX) map of a cross-sectional cut of a test sample after cryo-FIB milling, revealing an Al<sub>2</sub>O<sub>3</sub> isolation layer at the solid–liquid interface. The dark contrast at the top-right Au–liquid interface is due to the EDX detector location which gives rise to shadowing. The lower panel shows a sketch of the cross section. b) Sketch of a cross section (not to scale) of capacitors with integrated NaCl–H<sub>2</sub>O fabricated. c) Optical microscopy image of a capacitor with an integrated NaCl–H<sub>2</sub>O dielectric of  $\approx 20 \mu\text{m}$  diameter (green arrow). d) Photograph of a sample with 16 integrated capacitors after deposition of NaCl, before H<sub>2</sub>O deposition. The green arrows point to three of the capacitors (small bright dots). e) Areal capacitances of three capacitors with integrated NaCl–H<sub>2</sub>O and diameters of 20, 30, and 40  $\mu\text{m}$  measured as a function of applied voltage. Freezing the water causes the capacitances to collapse to the stray value.

integrated into electrolytic capacitor devices. Surprisingly, unlike the bulk-droplet devices, the  $C(V)$  characteristics of the integrated capacitors in various samples consistently displayed a step-like behavior (Figure 2e). At voltages of 0.2–0.4 V, the capacitance increases in a step from the parasitic capacitance to the double-layer capacitance (Figure 2e; Figure S3, Supporting Information). Such steps are followed by a continuous increase of the capacitance with increasing voltage. We attribute the steps to the presence of small vapor pockets in the devices, likely caused by the volume reduction of H<sub>2</sub>O during the melting step. The liquid–solid interface is formed only outside the pocket. The increasing voltage pulls the liquid to the solid as known from electrowetting,<sup>[25]</sup> thereby increasing the effective area of the liquid–solid interface, see, for example, Figure S4 (Supporting Information). Steps are also seen in the characteristics of several integrated FETs (Figure 4c), in the same voltage range as for the capacitors.

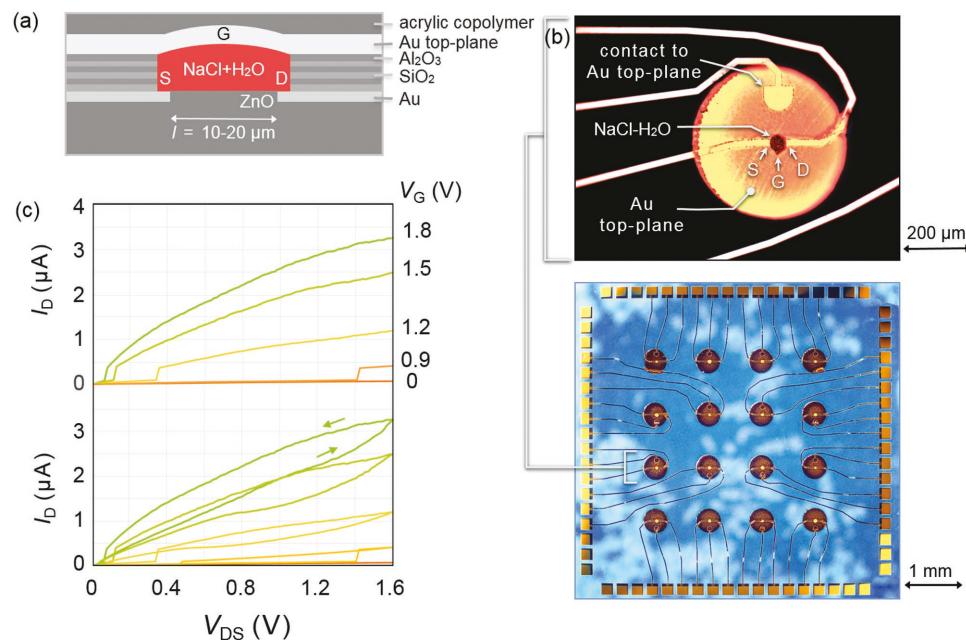

Using this process, we fabricated FETs with liquids integrated into the gate stacks (see Figure 4a). The samples were grown on ZnO, which served as channel material. ZnO FETs with bulk liquid-drop gates have already been explored<sup>[10]</sup> and found to have excellent characteristics. The chips contained 10–20 FETs (Figure 4b). This number was determined by boundary conditions of our setup, and should not suggest any limit to the possible integration level. The liquids had volumes of  $\approx 10 \times 10 \times 10 \mu\text{m}^3$  ( $w \times l \times h$ ), and the channel lengths of the FETs equaled 10  $\mu\text{m}$ . Figure 4c shows the room-temperature output characteristic  $I_D(V_{DS})$  of such an integrated FET. The characteristics are in good agreement with those of conventional ZnO FETs gated by bulk drops of H<sub>2</sub>O–NaCl. On–off ratios exceed 100 ( $\approx 20$  for the bulk devices), and gate currents are negligible ( $< 20 \text{ nA}$ ; Figure S5, Supporting Information). The devices tended to show a sizable hysteresis of the  $I_D(V_{DS})$  characteristics, as is common for electrolyte-gated FETs.

**Figure 3.** Areal capacitances of three capacitors with integrated  $\text{NaCl}-\text{H}_2\text{O}$  and diameters of  $20\text{--}50\text{ }\mu\text{m}$  measured at room temperature as a function of applied voltage before and after storing them for 2 years at room temperature, in air.

Interestingly, analogous to the switching behavior displayed by the  $C(V)$  characteristics of the capacitors, the FETs display a hysteretic switching of the drain currents, reminiscent of memristors.<sup>[26]</sup> This behavior of the drain currents is consistent with a similar behavior reported for water-gated  $\text{MoS}_2$  FETs<sup>[27,28]</sup> and is to be expected as the  $\text{H}_2\text{O}$  molecules in direct contact

with the drain-source channel act as charge scattering and trapping centers.

Compared to the standard layout of electrolyte-gated FETs that use open and large drops of electrolytes covering large sample areas, integrating the electrolytes by thin-film technologies opens the possibility to enhance the reproducibility of the fabrication process and keep the electrolytes clean and protected from the atmosphere. Geometrical factors and the environment of the liquid may be controlled with high precision so that several different electrolytes may be used in immediate spatial proximity. Reducing the liquid volumes may offer a route to increase the switching frequency of the devices.

We have investigated the potential and possibilities of merging integrated circuit technology with liquids by exploring, as examples, chips containing integrated capacitors and FETs. Patterned liquids integrated into solid-state heterostructures offer novel possibilities for science and applications. Challenges of incorporating liquids into solid-state heterostructures are given by enhanced complexity of the device fabrication, and—as we have found—new set of challenges on device stability, arising, for example, from the interdiffusion of ions, thermal expansion, and formation of vapor pockets. Any new technology needs to proceed through several phases while transitioning from explorations in research laboratories to real-life applications. We hope that with the next generation of devices enabling novel research applications, experience will be gained for first simple devices to be used in commercial applications, for example, in iontronics.

For the future, we foresee the implementation of a large variety of liquids patterned to even finer scales, possibly even into the nanoscopic regime, integrated into heterostructures of

**Figure 4.** Field-effect transistors with integrated liquids. a) Sketch showing a cross section (not to scale) of field-effect transistors with integrated  $\text{NaCl}-\text{H}_2\text{O}$  fabricated. b) Top: Optical microscopy images of a  $\text{ZnO}$ -field-effect transistors with integrated  $\text{NaCl}-\text{H}_2\text{O}$  dielectrics (arrow). These transistors have channel lengths  $l\approx 10\text{--}20\text{ }\mu\text{m}$ . Bottom: optical microscopy images of a chip containing 16 FETs in accordance with (a). The FET of line 3, row 1 is shown in the top panel. c) Typical switching characteristics of such FETs measured at room temperature. For clarity, the upper figure shows the characteristics for falling drain-source voltages only. During all measurements, the gate currents were smaller than 25 nA.

high complexity. By qualitatively extending the available spectrum of mechanical, electronic, and functional properties available, the incorporation of liquids into integrated circuits opens a hitherto unavailable phase space for circuit architecture. The capability of integrating liquids on the nanoscale into solid-state heterostructures will ultimately lead to mesoscopic fluids and mesoscopic liquid particles, which we expect to be of fundamental interest by enabling new applications of nanoionics.<sup>[29]</sup> By utilizing ion transport and the design possibilities for liquids in heterostructures, this novel device concept links integrated circuits, adaptive electronics, biology, solid-state chemistry, and neuromorphic computing. Integrated liquids pave the way to nanoscale chemical modifications of heterostructures, which utilize the liquids as sources and sinks of ions,<sup>[17,29,30]</sup> thus creating new possibilities for simultaneous electronic and ionic transport for processing energy and information.

## Experimental Section

**Sample Design and Growth Methods:** An essential step toward realizing FETs was to test the process of fabricating integrated capacitors as shown in Figure 2b–d and Figure S6 (Supporting Information). For the side walls confining the liquid, we found it important to grow  $\text{SiO}_2$  (20 nm)- $\text{Al}_2\text{O}_3$  (30 nm)  $\times$  3 superlattices instead of simple oxide monolayers because the superlattices provide enhanced mechanical strength in contact with the electrolyte. The top layer of an acrylic copolymer was deposited after growth to enhance the stability of the devices during thermal cycling and to provide additional protection of the devices' surfaces.

Fabrication steps of the integrated liquid capacitors and FETs

- Preparation of  $\text{ZnO}$  substrates by annealing in oxygen for 4 h at 500 °C. Fabrication of bottom contacts by thermal deposition of Ti (15 nm)/Pt (15 nm)/Au (15 nm) on  $\text{ZnO}$  (for transistors) or on  $\text{Al}_2\text{O}_3$  (for capacitors) substrates. Patterning of bottom contacts by optical lithography of photoresist and lift-off.

- Growth of [ $\text{SiO}_2$  (20 nm)/ $\text{Al}_2\text{O}_3$  (30 nm)]  $\times$  3 multilayers by thermal evaporation. Patterning by optical lithography of photoresist and lift-off.

- Deposition of  $\approx 35$  nm  $\text{NaCl}$  by thermal evaporation. Patterning by lifting-off photoresist with acetone.

- Deposition of  $\text{H}_2\text{O}$  by thermal evaporation through shadow mask, substrate temperature  $\sim 60^\circ\text{C}$ , thickness  $\approx 2\text{--}5$   $\mu\text{m}$ . Formation of the  $\text{NaCl}$  aqueous solution on the areas covered by  $\text{NaCl}$  by annealing for  $\approx 2$  min at room temperature and 1 bar of  $\text{N}_2$ .

- Ar-ion milling ( $\approx 1 \times 10^{-4}$  mbar, 5 min,  $-170^\circ\text{C}$ ) to clean water-free areas.

- Fabrication of  $\approx 100$  nm top contacts by thermal evaporation of Ag, Au, or Ag/Au through shadow mask. Sample temperature:  $-170^\circ\text{C}$ , growth rate  $\approx 5$   $\text{\AA s}^{-1}$ .

- Deposition of protection layer consisting of acrylic copolymer (2-butoxyethanol (5–10%), 2-methoxy-1-methylethylacetate (1–5%), acetone (30–60%), butane (5–10%), isobutane (1–5%), propane (10–30%)), and adhesion promoter on desired areas at room temperature.

**Capacitance Measurements:** All data shown in the main text of the manuscript have been gained from dc-measurements of the capacitance between the bottom contact (Au) and the top metallic layer (Ag/Au) that encapsulates the liquid (as described, see also Figure 2b). A Keithley 237 Source-Measure unit was used for the dc-measurements. The ac-measurements shown in Figure S2 (Supporting Information) were performed by using an LCR-meter (Agilent E4980A, 20 Hz–2 MHz) with excitation voltages in the order of 100 mV.

## Supporting Information

Supporting Information is available from the Wiley Online Library or from the author.

## Acknowledgements

B.P., G.P., and J.M. designed, and B.P. and G.P. built the setups for sample preparation and measurements. B.P., G.P., and E.F.-T. fabricated and characterized the devices; M.J.Z. and L.F.K performed the cryo-FIB/SEM and cryo-EDX measurement of the sample, and all authors analyzed data. J.M. developed the idea and guided the research. All the authors gratefully acknowledge discussions with H. D. Abruna, H. Boschker, D. Fischer, T. Harada, M. Jäger, R. Kjellander, H. Klauk, J. Maier, H. J. Mannhart, J. Popovic, and C. Schön. M.J.Z. and L.F.K. acknowledge support by the NSF (DMR-1654596) and the David and Lucile Packard Foundation. This work made use of the Cornell Center for Materials Research Shared Facilities which are supported through the NSFMRSEC program (DMR-1719875).

## Conflict of Interest

The authors declare no conflict of interest.

## Keywords

electrolyte gating, field-effect transistors, heterostructures, patterning liquids

Received: April 23, 2018

Revised: June 11, 2018

Published online: July 17, 2018

- [1] E. K. Sackmann, A. L. Fulton, D. J. Beebe, *Nature* **2014**, *507*, 181.

- [2] B. J. Kim, S. H. Um, W. C. Song, Y. H. Kim, M. S. Kang, J. H. Cho, *Nano Lett.* **2014**, *14*, 2610.

- [3] H. Ohta, T. Mizuno, S. Zheng, T. Kato, Y. Ikuhara, K. Abe, H. Kumomi, K. Nomura, H. Hosono, *Adv. Mater.* **2012**, *24*, 740.

- [4] N. C. S. Vieira, J. Borme, G. Machado Jr., F. Cerqueira, P. P. Freitas, V. Zucolotto, N. M. R. Peres, P. Alpuim, *J. Phys.: Condens. Matter* **2016**, *28*, 085302.

- [5] J. H. Cho, J. Lee, Y. Xia, B. Kim, Y. He, M. J. Renn, T. P. Lodge, C. D. Frisbie, *Nat. Mater.* **2008**, *7*, 900.

- [6] B. J. Kim, E. Hwang, M. S. Kang, J. H. Cho, *Adv. Mater.* **2015**, *27*, 5875.

- [7] S. R. Peck, L. S. Curtin, J. T. McDevitt, R. W. Murray, J. P. Collman, W. A. Little, T. Zetterer, H. M. Duan, C. Dong, A. M. Hermann, *J. Am. Chem. Soc.* **1992**, *114*, 6771.

- [8] H. Shimotani, G. Diguet, Y. Iwasa, *Appl. Phys. Lett.* **2005**, *86*, 022104.

- [9] M. J. Panzer, C. R. Newman, C. D. Frisbie, *Appl. Phys. Lett.* **2003**, *86*, 103503.

- [10] H. Shimotani, H. Asanuma, A. Tsukazaki, A. Ohtomo, M. Kawasaki, Y. Iwasa, *Appl. Phys. Lett.* **2007**, *91*, 082106.

- [11] R. Misra, M. McCarthy, A. F. Hebard, *Appl. Phys. Lett.* **2007**, *90*, 052905.

- [12] H. Yuan, H. Shimotani, A. Tsukazaki, A. Ohtomo, M. Kawasaki, Y. Iwasa, *Adv. Funct. Mater.* **2009**, *19*, 1046.

[13] L. Kergoat, L. Herlogsson, D. Braga, B. Piro, M.-C. Pham, X. Crispin, M. Berggren, G. Horowitz, *Adv. Mater.* **2010**, *22*, 2565.

[14] H. Yuan, H. Shimotani, A. Tsukazaki, A. Ohtomo, M. Kawasaki, Y. Iwasa, *J. Am. Chem. Soc.* **2010**, *132*, 6672.

[15] S. D. Ha, S. Ramanathan, *J. Appl. Phys.* **2011**, *110*, 071101.

[16] M. Nakano, K. Shibuya, D. Okuyama, T. Hatano, S. Ono, M. Kawasaki, Y. Iwasa, Y. Tokura, *Nature* **2012**, *487*, 459.

[17] J. Jeong, N. Aetukuri, T. Graf, T. D. Schladt, M. G. Samant, S. S. P. Parkin, *Science* **2013**, *339*, 1402.

[18] J. Shi, S. D. Ha, Y. Zhou, F. Schoofs, S. Ramanathan, *Nat. Commun.* **2013**, *4*, 2676.

[19] M. Weisheit, S. Fähler, A. Marty, Y. Souche, C. Poinsignon, D. Givord, *Science* **2007**, *315*, 349.

[20] S. Hormoz, S. Ramanathan, *Solid-State Electron.* **2010**, *54*, 654.

[21] A. S. Dhoot, S. C. Wimbush, T. Benseman, J. L. MacManus-Driscoll, J. R. Cooper, R. H. Friend, *Adv. Mater.* **2010**, *22*, 2529.

[22] H. Ji, J. Wei, D. Natelson, *Nano Lett.* **2012**, *12*, 2988.

[23] K. Ueno, H. Shimotani, H. Yuan, J. Ye, M. Kawasaki, Y. Iwasa, *J. Phys. Soc. Jpn.* **2014**, *83*, 032001.

[24] Y. Saito, T. Nojima, Y. Iwasa, *Nat. Rev. Mater.* **2017**, *2*, 16094.

[25] F. Mugele, J.-C. Baret, *J. Phys.: Condens. Matter* **2005**, *17*, R705.

[26] A. Sawa, *Mater. Today* **2008**, *11*, 28.

[27] Y. Shimazu, M. Tashiro, S. Sonobe, M. Takahashi, *Sci. Rep.* **2016**, *6*, 30084.

[28] J. Shu, G. Wu, Y. Guo, B. Liu, X. Wie, Q. Chen, *Nanoscale* **2016**, *8*, 3049.

[29] J. Maier, *Nat. Mater.* **2005**, *4*, 805.

[30] J. Shi, Y. Zhou, S. Ramanathan, *Nat. Commun.* **2014**, *5*, 4860.