# Well-Posed Verilog-A Compact Model for Phase Change Memory

Shruti R. Kulkarni\*, Deepak Vinayak Kadetotad†, Jae-sun Seo† and Bipin Rajendran\*

\*Department of Electrical and Computer Engineering

New Jersey Institute of Technology, Newark, NJ 07102

†School of Electrical, Computer and Energy Engineering,

Arizona State University, Tempe, AZ 85287, USA

Email: bipin@njit.edu

**Abstract**—In this work, we demonstrate a well-posed compact model for phase change memory (PCM) devices based on  $\text{Ge}_2\text{Sb}_2\text{Te}_5$  (GST) chalcogenide. This model supports all modes of simulation including transient, DC, and AC. The model is developed in Verilog-A and simulated using HSPICE. It is computationally simple and successfully captures the key high level behaviors of memory switching, including the resistance dependence on programming voltages, currents and pulse time-scales.

**Index Terms**—Phase change memory, chalcogenide, Verilog-A, well-posed model

## I. INTRODUCTION

Phase change memory (PCM) is a non-volatile memory technology that is emerging as a leading contender for storage class memories as well as in-memory computing applications based on crossbar array architectures with co-located memory and processing units [1]–[3]. Emerging memory devices such as PCM, STT-RAMs (Spin-Transfer Torque Random Access Memory) and RRAM (Resistive RAM) have also shown the capability to be programmed to store analog resistance levels, and are being explored for realizing area and power efficient accelerators for machine learning and embedded AI applications [4]–[8].

For designing neuromorphic and in-memory computing architectures using non-volatile memory (NVM) devices, efficient compact models are required, capturing their key operating characteristics. In this paper, we present a well-posed model for phase change memory (PCM) devices based on  $\text{Ge}_2\text{Sb}_2\text{Te}_5$  (GST) chalcogenide. Several models for the GST based PCM device have been proposed earlier, capturing various aspects of the device physics [9]–[19]. The hierarchical model in [9] incorporates the device geometry and device physics, though it is computationally quite expensive. Simpler models have also been developed using basic circuit elements such as controlled voltage/current sources, resistances and capacitances to model the device behavior [10], [11]. The model presented in [10] captures the binary switching of the device from crystalline to amorphous state, and vice versa. The state switching is based on the analysis of the quenching time once the device temperature exceeds the melting point. A further enhancement of this model showed the capability of demonstrating multiple resistance states within the device

as a function of programming current and quenching time [11]. A single equation was used to define the model's I-V response, describing both the off state (low field) and the on state (high field) behavior, with a set of blending functions used to combine the two regimes.

Our model, based on the one discussed in [11], is developed in Verilog-A. It is computationally simple as it uses basic circuit elements and successfully captures the high level dynamics of resistance switching, including its dependence on programming voltages, currents and pulse time-scales. Our results also show the capability of the model to emulate multi-bit storage characteristics of PCM, with pulse-width and pulse-quench based programming schemes. In addition, our model is well-posed and supports different modes of simulation including transient, DC and AC, as per the guidelines discussed in [20], [21], which so far has not been addressed in previous models.

The rest of the paper is organized as follows. In Section II, we first briefly describe the physics of PCM devices and their switching characteristics. The development of the compact model in Verilog-A is discussed in Section III, emphasizing the techniques used to make the model well-posed. In Section IV, we present simulation results based on the proposed model and compare the obtained characteristics with experimental device data.

## II. DEVICE PHYSICS AND OPERATION

Phase change memory (PCM) device consists of a chalcogenide alloy sandwiched between two metal electrodes. Depending on the amplitude and timescales of the programming pulses, the chalcogenide material can be heated and quenched to a high resistive amorphous phase (also called the RESET state) or re-crystallized to a low resistive poly-crystalline phase (also called the SET state) [1]–[3]. This transition between the crystalline and amorphous regions through Joule heating is reversible and allows the device to be used as a programmable resistor, and hence as a memory storage device. Typically observed contrast in conductance (ON/OFF ratio) of PCM devices is between 100 – 1000. Furthermore, by controlling the amplitude and falling rate of the programming pulse, it is also possible to gradually change the shape of the amorphous volume in the critical current path of the device,

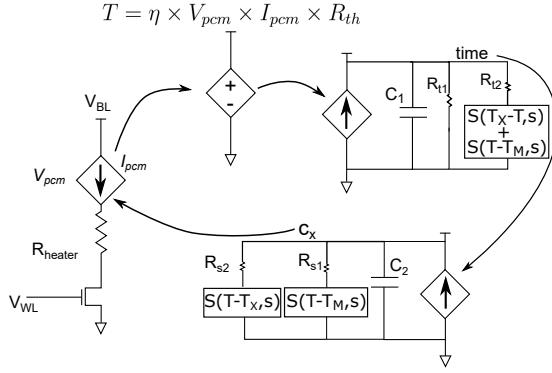

Fig. 1. Schematic of the continuous compact Verilog-A model for the PCM device. This model is inspired from [11], and also satisfies the guidelines for compact model development specified in [20].

enabling stable analog changes in conductance, and multi-bit storage [3], [22].

Different structures for the PCM devices have been demonstrated such as the mushroom, pore and bridge cell configurations [1]. The mushroom cell is more widely used, where the bottom electrode, which also acts as the heater, is much smaller in diameter ( $< 50$  nm) compared to the top electrode dimension [1]. More recently, confined PCM cells have been demonstrated, which enables strong control of Joule heating even in the presence of voids [23], [24].

### III. COMPACT MODEL

Building up on a previously published discontinuous model [11], we have developed a well-posed Verilog-A model of the device (Fig. 1), where the device resistance is calculated based on a lumped parameter  $c_x$  that represents the crystalline fraction within the device. The current through the device is given as:

$$I_{PCM} = I_\alpha(V_{PCM}, c_x) + F(I_{PCM}; I_{th}).[-I_\alpha(V1, c_x) + F(V_{PCM}; V_{hold}).I_{ON}(V_{PCM})] \quad (1)$$

where the OFF state current  $I_\alpha$  and programming region current  $I_{ON}$  is:

$$I_\alpha = \frac{\exp(n(c_x).V_{PCM}) - 1}{n(c_x).R(c_x). \exp\left(\frac{E_a(c_x)}{k_B} \left(\frac{1}{T} - \frac{1}{T_{ref}}\right)\right)} \quad (2)$$

$$I_{ON} = \frac{V_{PCM} - V_{hold}}{R_{ON}} \quad (3)$$

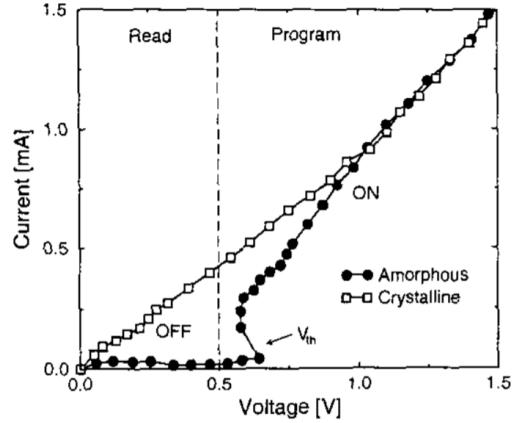

$I_{th}$  represents the threshold current below which switching does not take place and  $V_h$  is the hold voltage, which is the x-intercept of the linear region of the I-V curve (see Fig. 2).  $I_{ON}$  represents the current during the ON state or programming state of the device, when the conductance of the device increases. Note that the device resistance  $R_{ON}$ , when sufficiently large currents are passing through the device (such that some portion of the chalcogenide alloy is in the molten phase), is significantly lesser than the typical SET resistance of the device.

Fig. 2. Typical experimental I-V characteristics of PCM device (reproduced from [25]).

TABLE I

PARAMETERS USED IN THE WELL-POSED VERILOG-A PCM COMPACT MODEL.

| Symbol   | Value               | Symbol        | Value                             |

|----------|---------------------|---------------|-----------------------------------|

| $R_{th}$ | 65 MK/W             | $R_{s1}$      | $1 \mu\Omega$                     |

| $C_1$    | 1 nF                | $R_{s2}$      | $1 \Omega$                        |

| $R_{t1}$ | 1 G $\Omega$        | $R_{heater}$  | $410 \Omega$                      |

| $R_{t2}$ | $1 \mu\Omega$       | $E_a$ (in eV) | $0.27 - 0.25c_x$                  |

| $T_X$    | $200^\circ\text{C}$ | $\Gamma_a$    | $2.3 \text{ eV}$                  |

| $T_M$    | $600^\circ\text{C}$ | $A$           | $1.06 \times 10^{-23} \text{ ns}$ |

| $C_2$    | 20 nF               | $V_h$         | 0.5 V                             |

| $R_{ON}$ | 1000 $\Omega$       | $I_{th}$      | 40 $\mu\text{A}$                  |

Based on the device current and voltage, the temperature ( $T$ ) rise in the material is estimated using a lumped thermal resistance model, assuming a heating efficiency of  $\eta = 1\%$  [26]. We also assume that in scaled PCM devices, the thermal time constant is significantly smaller than typical SET and RESET pulse-widths.

The crystallization dynamics in the device is described using the Johnson-Mehl-Avrami-Kolmogorov (JMAK) expression [27], giving the instantaneous crystallization fraction  $c_x$  within the device, which is then used to approximate the device resistance using the following expressions:

$$c_x = 1 - \exp(-t/\tau(T)) \quad (4)$$

$$R = R_{SET} \times c_x + R_{RESET} \times (1 - c_x) \quad (5)$$

where  $\tau(T) = A \exp(\Gamma_a/k_B T)$  and the device resistance varies between the SET ( $R_{SET} = 10 \text{ k}\Omega$ ) and RESET resistance ( $R_{RESET} = 1 \text{ M}\Omega$ ). The functions  $F$  in equation 1 are the blending functions that combine the different regions of the model's I-V curve. We used a smooth step function  $S(x, s)$  to model temperature controlled switches in the auxiliary circuits (Fig. 1) [21]. They are given by the following expressions:

$$F(x; x_{th}) = \frac{1}{(1 + \exp(-(x - x_{th})/\alpha))} \quad (6)$$

$$S(x, s) = 0.5 \left( \frac{x}{\sqrt{x^2 + s}} + 1 \right) \quad (7)$$

where,  $s$  is the smoothening parameter controlling the transition rate of the step function  $S(x, s)$ . The different parameters used in our model are listed in Table I.

We follow the guidelines listed by the NEEDS (Nano-Engineered Electronic Device Simulation) initiative [20] to develop a mathematically well-posed model that converges for different modes of simulations such as transient, AC and DC. For this to be satisfied, the Verilog-A model should adhere to a set of coding guidelines. Some of the key requirements include describing the model as a set of Differential Algebraic Equations (DAE) and avoiding any abrupt bias dependent switching statements in the Verilog-A code. The I-V expression for the PCM (equation 1) as presented in [11] is an algebraic expression. By employing smoothed step functions (equation 7), we eliminate sharp temperature dependent switching in the auxiliary circuit (which computes the quench time and crystalline fraction) of the model. Hence, our continuous model is capable of operating in all the different modes of simulation.

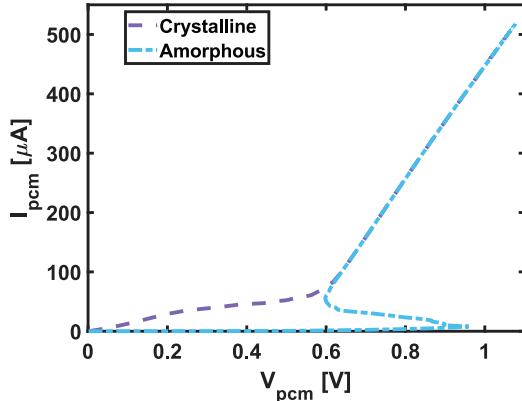

Fig. 3. I-V response of the well-posed PCM Verilog-A model. The behavior was captured by applying a voltage ramp at the Word Line ( $WL$ ), i.e., the gate of the access NMOS for the two states of initialization (SET and RESET).

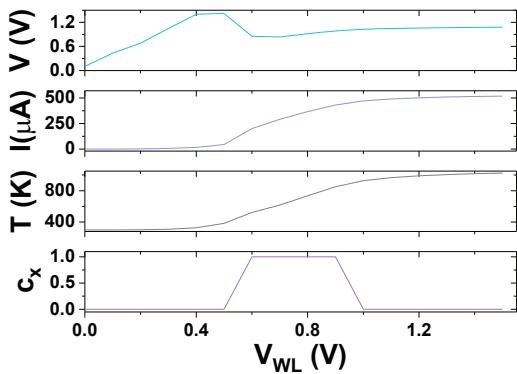

Fig. 4. DC behavior of the PCM device from HSPICE simulations. From top to bottom: the waveforms of the PCM voltage drop ( $V$ ), current ( $I$ ), temperature ( $T$ ) and the crystalline fraction ( $c_x$ ) as a function of  $V_{WL}$ .

#### IV. SIMULATION RESULTS

We simulated the switching behavior of the PCM device connected in series with an NMOS access transistor from a commercial 65 nm CMOS technology. Our simulations show that the model captures the essential features of typical I-V characteristics (Fig. 3) similar to what is seen in the experimental device data in Fig. 2. The simulations were conducted by applying a voltage ramp at the Word Line ( $WL$ ) for the two states of initialization (SET and RESET).

The model also works in the DC mode; Fig. 4 shows the steady state response of the internal parameters,  $T$  and  $c_x$  at different voltage values applied to the gate of the access transistor ( $V_{WL}$ ).

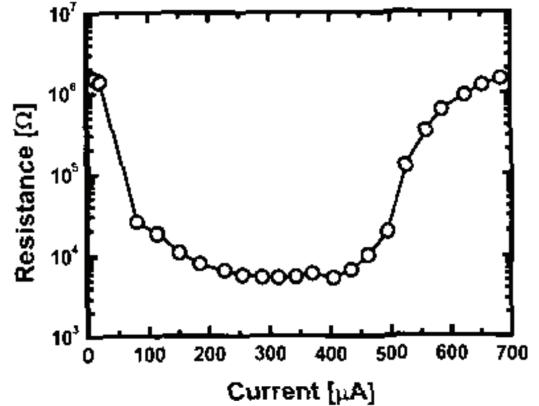

Fig. 5. Experimental resistance vs. programming current characteristics of a PCM device (reproduced from [28]).

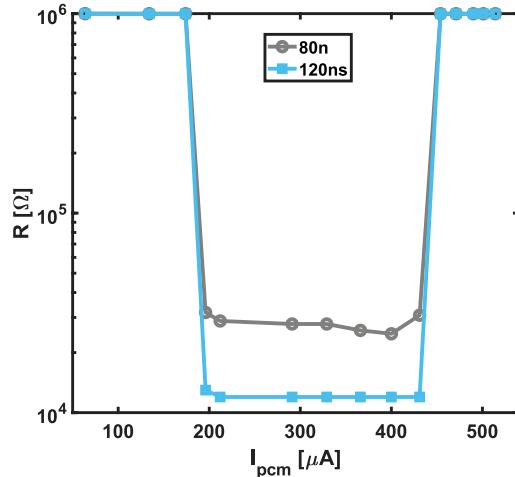

Fig. 6. The R-I curve obtained using the model for programming pulse widths of 80 ns and 120 ns.

Next, we compared the dependence of the device resistance as a function of the applied programming current. Typical experimental characteristics of a PCM device is shown in Fig. 5. Starting from a high resistance state, the device resistance can be reduced by applying low amplitude SET pulses; however,

once the applied pulse amplitude is sufficiently large to induce melting in the chalcogenide, the device is programmed to its RESET state. The proposed model's behavior shown in Fig. 6 closely matches this experimentally observed programming trend.

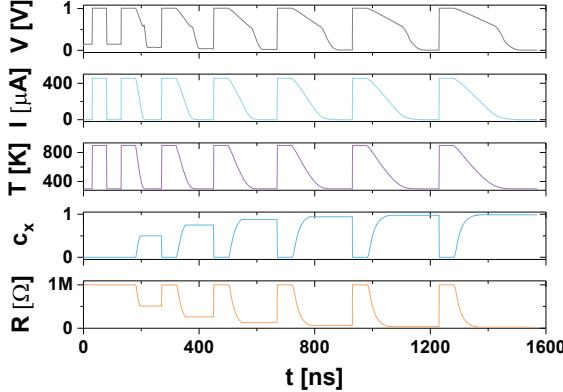

Fig. 7. Simulated device parameters as a function of the duration of the falling edge of the input pulse. Application of each pulse initially resets the pulse and then brings the final resistance to an intermediate value below  $R_{reset}$  depending on the duration of the falling edge. From top to bottom: the waveforms of the PCM voltage drop ( $V$ ), current ( $I$ ), device temperature ( $T$ ), crystalline fraction ( $c_x$ ) and the device resistance ( $R$ ).

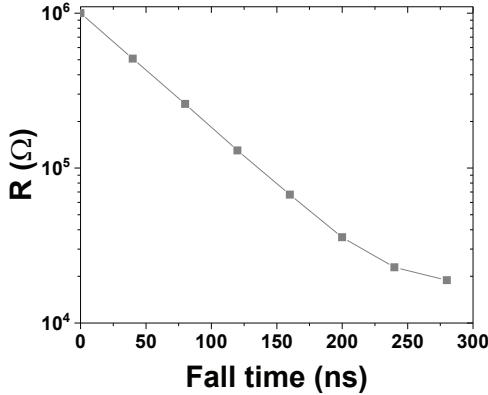

Fig. 8. PCM final resistance as a function of falling edge of input pulse, plotted from the resistance values as shown in Fig. 7.

We also studied the response of the device model to show multiple conductance levels between  $R_{SET}$  and  $R_{RESET}$  using two approaches. Dependence of the device resistance on quench time has been demonstrated in [29]. We also employed the same scheme in the simulations by applying pulses having variable fall times in the range of 50 ns to 300 ns. The last two panels in Fig. 7 show the gradual change in the crystalline fraction and the device resistance as the fall time of the programming pulse is increased. Fig. 8 shows the programmed resistance from the model as a function of the fall time.

Another method of programming the device to various intermediate conductance levels by applying partial SET pulses

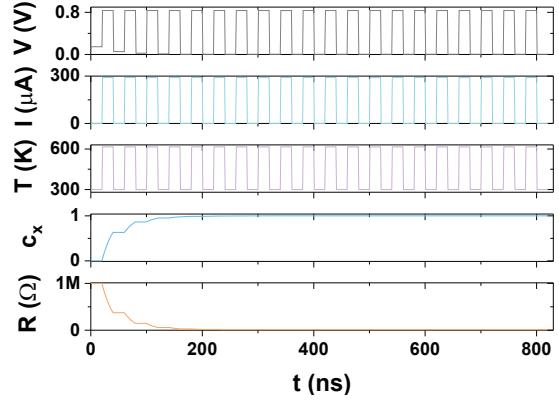

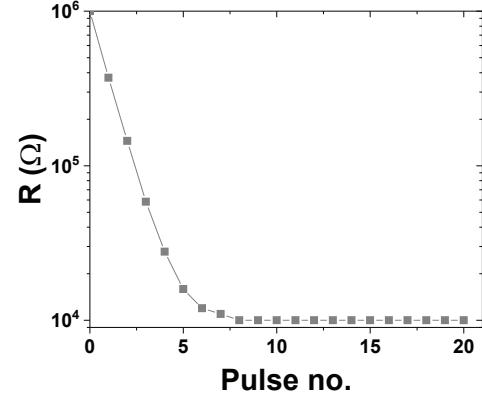

was demonstrated in [30]. We also simulated the similar behavior using the model, by applying a sequence of short duration pulses, as shown in the waveforms in Fig. 9. Each programming pulse has a constant amplitude ( $V_{WL} = 0.7$  V) and duration (20 ns). Fig. 10 shows the device resistance as a function of the number of programming pulses.

Fig. 9. Gradual conductance change by application of a series of low amplitude partial SET pulses. From top to bottom: the waveforms of the PCM voltage drop ( $V$ ), current ( $I$ ), device temperature ( $T$ ), crystalline fraction ( $c_x$ ) and the device resistance ( $R$ ).

Fig. 10. PCM resistance as a function of the number of partial SET pulses, plotted from the resistance values as shown in Fig. 9.

## V. CONCLUSION

We have developed a well-posed Verilog-A compact model that accurately captures the essential aspects of experimentally observed memory switching in phase change memory devices. The model also shows multiple resistance states depending on the programming schemes employed. Future work includes incorporating reliability aspects such as resistance drift and stuck-at fault simulation capability in the model, towards evaluating large memory arrays and neuromorphic circuits using PCM devices.

## ACKNOWLEDGEMENTS

This work was supported in part by the Semiconductor Research Corporation under grant number 2016-SD-2717, the CAMPUSENSE project grant from CISCO Systems Inc; and the National Science Foundation grant 1710009.

## REFERENCES

- [1] M. K. Qureshi, S. Gurumurthi, and B. Rajendran, "Phase change memory: From devices to systems," *Synthesis Lectures on Computer Architecture*, vol. 6, no. 4, pp. 1–134, 2011.

- [2] S. Raoux, F. Xiong, M. Wuttig, and E. Pop, "Phase change materials and phase change memory," *MRS Bulletin*, vol. 39, no. 8, p. 703710, 2014.

- [3] H. S. P. Wong, S. Raoux, S. Kim, J. Liang, J. P. Reifenberg, B. Rajendran, M. Asheghi, and K. E. Goodson, "Phase change memory," *Proceedings of the IEEE*, vol. 98, no. 12, pp. 2201–2227, Dec 2010.

- [4] B. Rajendran and F. Alibart, "Neuromorphic computing based on emerging memory technologies," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 6, no. 2, pp. 198–211, June 2016.

- [5] P. A. Merolla, J. V. Arthur, R. Alvarez-Icaza, A. S. Cassidy, J. Sawada, F. Akopyan, B. L. Jackson, N. Imam, C. Guo, Y. Nakamura, B. Brezzo, I. Vo, S. K. Esser, R. Appuswamy, B. Taba, A. Amir, M. D. Flickner, W. P. Risk, R. Manohar, and D. S. Modha, "A million spiking-neuron integrated circuit with a scalable communication network and interface," *Science*, vol. 345, no. 6197, pp. 668–673, 2014. [Online]. Available: <http://science.sciencemag.org/content/345/6197/668>

- [6] J. s. Seo, B. Brezzo, Y. Liu, B. D. Parker, S. K. Esser, R. K. Montoye, B. Rajendran, J. A. Tierno, L. Chang, D. S. Modha, and D. J. Friedman, "A 45nm CMOS neuromorphic chip with a scalable architecture for learning in networks of spiking neurons," in *2011 IEEE Custom Integrated Circuits Conference (CICC)*, Sept 2011, pp. 1–4.

- [7] J. Gehlhaar, "Neuromorphic processing: A New Frontier in Scaling Computer Architecture," in *Proceedings of the 19th International Conference on Architectural Support for Programming Languages and Operating Systems*, ser. ASPLOS '14. New York, NY, USA: ACM, 2014, pp. 317–318. [Online]. Available: <http://doi.acm.org/10.1145/2541940.2564710>

- [8] J. Zhang, Z. Wang, and N. Verma, "In-Memory Computation of a Machine-Learning Classifier in a standard 6T SRAM Array," *IEEE Journal of Solid-State Circuits*, vol. 52, no. 4, pp. 915–924, April 2017.

- [9] Z. Xu, K. B. Sutaria, C. Yang, C. Chakrabarti, and Y. Cao, "Hierarchical modeling of Phase Change memory for reliable design," in *2012 IEEE 30th International Conference on Computer Design (ICCD)*, Sept 2012, pp. 115–120.

- [10] P. Fantini, A. Benvenuti, A. Pirovano, F. Pellizzer, D. Ventrice, and G. Ferrari, "A compact model for phase change memories," in *Simulation of Semiconductor Processes and Devices, 2006 International Conference on*. IEEE, 2006, pp. 162–165.

- [11] D. Ventrice, P. Fantini, A. Redaelli, A. Pirovano, A. Benvenuti, and F. Pellizzer, "A Phase Change Memory Compact Model for Multilevel Applications," *IEEE Electron Device Letters*, vol. 28, no. 11, pp. 973–975, Nov 2007.

- [12] C.-M. Jung, E.-S. Lee, K.-S. Min, and S.-M. S. Kang, "Compact Verilog-A model of phase-change RAM transient behaviors for multi-level applications," *Semiconductor Science and Technology*, vol. 26, no. 10, p. 105018, 2011.

- [13] L. Xi, S. Zhitang, C. Daolin, C. Xiaogang, and C. Houpeng, "An SPICE model for phase-change memory simulations," *Journal of Semiconductors*, vol. 32, no. 9, p. 094011, 2011.

- [14] K. Sonoda, A. Sakai, M. Moniwa, K. Ishikawa, O. Tsuchiya, and Y. Inoue, "A compact model of phase-change memory based on rate equations of crystallization and amorphization," *IEEE Transactions on Electron Devices*, vol. 55, no. 7, pp. 1672–1681, 2008.

- [15] R. Warren, J. Reifenberg, and K. Goodson, "Compact thermal model for phase change memory nanodevices," in *2008 11th Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems*, May 2008, pp. 1018–1045.

- [16] E. Covi, A. Kiouseoglou, A. Cabrini, and G. Torelli, "Compact model for phase change memory cells," in *2014 10th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME)*, June 2014, pp. 1–4.

- [17] P. Junsangsri and F. Lombardi, "A New Comprehensive Model of a Phase Change Memory (PCM) cell," *IEEE Transactions on Nanotechnology*, vol. 13, no. 6, pp. 1213–1225, Nov 2014.

- [18] C. Dao-Lin, S. Zhi-Tang, L. Xi, C. Hou-Peng, and C. Xiao-Gang, "A Compact SPICE Model with Verilog-A for Phase Change Memory," *Chinese Physics Letters*, vol. 28, no. 1, p. 018501, 2011. [Online]. Available: <http://stacks.iop.org/0256-307X/28/i=1/a=018501>

- [19] K. Kwong, L. Li, J. He, and M. Chan, "Verilog-A model for phase change memory simulation," in *Solid-State and Integrated-Circuit Technology, 2008. ICSICT 2008. 9th International Conference on*. IEEE, 2008, pp. 492–495.

- [20] A. G. Mahmutoglu, T. Wang, A. Gupta, and J. Roychowdhury, "Well-Posed Device Models for Electrical Circuit Simulation," Mar 2017. [Online]. Available: <https://nanohub.org/resources/26199>

- [21] T. Wang and J. Roychowdhury, "Well-posed models of memristive devices," *arXiv preprint arXiv:1605.04897*, 2016.

- [22] H. Y. Cheng, M. BrightSky, S. Raoux, C. F. Chen, P. Y. Du, J. Y. Wu, Y. Y. Lin, T. H. Hsu, Y. Zhu, S. Kim, C. M. Lin, A. Ray, H. L. Lung, and C. Lam, "Atomic-level engineering of phase change material for novel fast-switching and high-endurance pcm for storage class memory application," in *2013 IEEE International Electron Devices Meeting*, Dec 2013, pp. 30.6.1–30.6.4.

- [23] M. B. Sky, N. Sosa, T. Masuda, W. Kim, S. Kim, A. Ray, R. Bruce, J. Gonsalves, Y. Zhu, K. Suu, and C. Lam, "Crystalline-as-deposited ALD phase change material confined PCM cell for high density storage class memory," in *2015 IEEE International Electron Devices Meeting (IEDM)*, Dec 2015, pp. 3.6.1–3.6.4.

- [24] X. Yujun, K. Wanki, K. Yerin, K. Sangbum, G. Jemima, B. Matthew, L. Chung, Z. Yu, and C. J. J., "Self-healing of a confined phase change memory device with a metallic surfactant layer," *Advanced Materials*, vol. 30, no. 9, p. 1705587. [Online]. Available: <https://onlinelibrary.wiley.com/doi/abs/10.1002/adma.201705587>

- [25] A. Pirovano, A. L. Lacaita, D. Merlani, A. Benvenuti, F. Pellizzer, and R. Bez, "Electronic switching effect in phase-change memory cells," in *Digest. International Electron Devices Meeting*, Dec 2002, pp. 923–926.

- [26] S. Song, Z. Song, C. Peng, L. Gao, Y. Gu, Z. Zhang, Y. Lv, D. Yao, L. Wu, and B. Liu, "Performance improvement of phase-change memory cell using AlSb<sub>3</sub>Te and atomic layer deposition TiO<sub>2</sub> buffer layer," *Nanoscale Research Letters*, vol. 8, no. 1, p. 77, 2013. [Online]. Available: <http://dx.doi.org/10.1186/1556-276X-8-77>

- [27] M. Avrami, "Kinetics of phase change. I general theory," *The Journal of Chemical Physics*, vol. 7, no. 12, pp. 1103–1112, 1939. [Online]. Available: <https://doi.org/10.1063/1.1750380>

- [28] F. Pellizzer, A. Pirovano, F. Ottogalli, M. Magistretti, M. Scaravaggi, P. Zuliani, M. Tosi, A. Benvenuti, P. Besana, S. Cadeo, T. Marangon, R. Morandi, R. Piva, A. Spandre, R. Zonca, A. Modelli, E. Varesi, T. Lowrey, A. Lacaita, G. Casagrande, P. Cappelletti, and R. Bez, "Novel  $\mu$ trinch phase-change memory cell for embedded and stand-alone non-volatile memory applications," in *Digest of Technical Papers. 2004 Symposium on VLSI Technology*, 2004, June 2004, pp. 18–19.

- [29] R. Annunziata, P. Zuliani, M. Borghi, G. D. Sandre, L. Scotti, C. Prelini, M. Tosi, I. Tortorelli, and F. Pellizzer, "Phase change memory technology for embedded non volatile memory applications for 90nm and beyond," in *2009 IEEE International Electron Devices Meeting (IEDM)*, Dec 2009, pp. 1–4.

- [30] S. R. Nandakumar, I. Boybat, M. L. Gallo, A. Sebastian, B. Rajendran, and E. Eleftheriou, "Supervised learning in spiking neural networks with MLC PCM synapses," in *2017 75th Annual Device Research Conference (DRC)*, June 2017, pp. 1–2.