# Positive Bias Instability in ZnO TFTs with $\text{Al}_2\text{O}_3$ Gate Dielectric

Pavel Bolshakov, Rodolfo A. Rodriguez-Davila, Manuel Quevedo-Lopez, and Chadwin D. Young

Department of Materials Science and Engineering

University of Texas at Dallas

800 West Campbell Road, Richardson, TX, USA

[chadwin.young@utdallas.edu](mailto:chadwin.young@utdallas.edu)

**Abstract**— Positive bias instability stress (PBI) was done on ZnO thin-film transistors (TFTs) with  $\text{Al}_2\text{O}_3$  deposition at 100°C and 250°C. The threshold voltage ( $V_T$ ), transconductance ( $g_m$ ), and subthreshold slope (SS) were monitored where the 100°C samples demonstrated a “turn-around” phenomenon in the  $\Delta V_T$  compared to the 250°C samples. The 250°C samples show consistent  $+\Delta V_T$ , suggesting a higher  $\text{Al}_2\text{O}_3$  deposition temperature results in the absence of the defect responsible for the “turn-around” effect. Both sets also demonstrate negligible degradation in  $\Delta g_m$  and  $\Delta SS$  – suggesting little to no influence on the  $V_T$  shift by interfacial state generation.

**Index Terms**-- ZnO, TFTs,  $\text{Al}_2\text{O}_3$ ,  $V_T$ , PBI

## I. INTRODUCTION

Large-area/flexible electronics may rely on oxide-based semiconductors that are desirable because of their compatibility with low-temperature fabrication required for large-area/flex-compatible technologies. ZnO is an oxide-based candidate to be used as an active layer in thin-film transistors (TFT) circuitry due to inexpensive processing and noteworthy electrical performance [1]–[3] and possible uses in flexible circuits [1]. For flex compatibility, deposition of high-k gate dielectrics at these low temperatures will be required as well.

With all the low-temperature processing, thin-film transistor reliability must be evaluated due to threshold voltage ( $V_T$ ) instability experienced by TFTs with high-k dielectrics [4]–[6]. In this work, TFTs are constant voltage stressed while monitoring critical parameters to assess the reliability of ZnO-based TFTs.

## II. DEVICE AND STRESS PROCEDURE DESCRIPTION

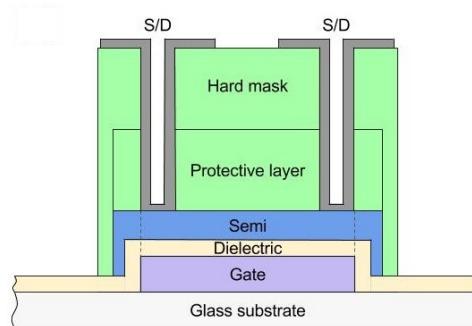

Zinc-oxide TFTs are fabricated using traditional photolithography to pattern staggered-bottom-gate and top-contacts, as previously reported[7], with the final device cross-section in Fig. 1. The devices are fabricated on a glass substrate with patterned 135 nm of indium tin oxide (ITO) to serve as the gate electrode. Then, a 15 nm  $\text{Al}_2\text{O}_3$  gate dielectric is deposited by atomic layer deposition (ALD) at 100°C or 250°C followed by 45 nm of zinc oxide (ZnO) as the semiconductor channel deposited by pulsed laser deposition (PLD). A protection layer (parylene) is used prior to patterning the ZnO, and then a hard mask (parylene) is deposited to protect the TFTs from ambient conditions. Finally, the gate and source/drain vias are opened in order to deposit Al contact metal followed by patterning. Stress testing was performed by applying stress voltages of either 5.5 V, 5.75 V, or 6 V to the gate only, with intermittent  $I_D$ - $V_G$  sense measurements.

- Pattern ITO (135nm) Gate

- ALD of  $\text{Al}_2\text{O}_3$  (15nm) at 100°C or 250°C

- PLD of ZnO (45nm) at 100°C and 20 mTorr

- Deposit and Pattern Protection Layer (Parylene)

- Pattern the ZnO Semiconductor

- Deposit and Pattern Hard Mask (Parylene)

- Open Gate and S/D Vias & Deposit/Pattern Al

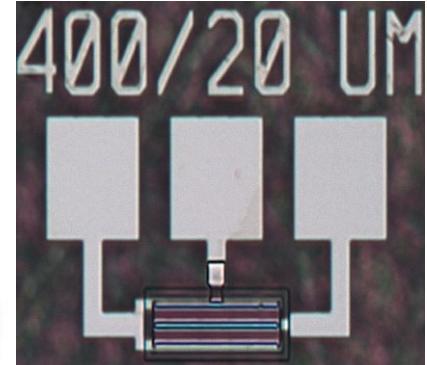

Figure 1. (left) Process flow for ZnO TFTs with  $\text{Al}_2\text{O}_3$ , (middle) cross-section schematic of the TFT structure, and (right) plan-view of the TFT structure.

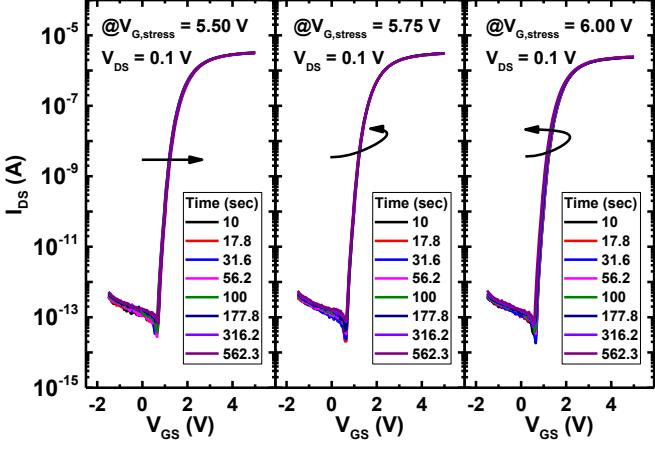

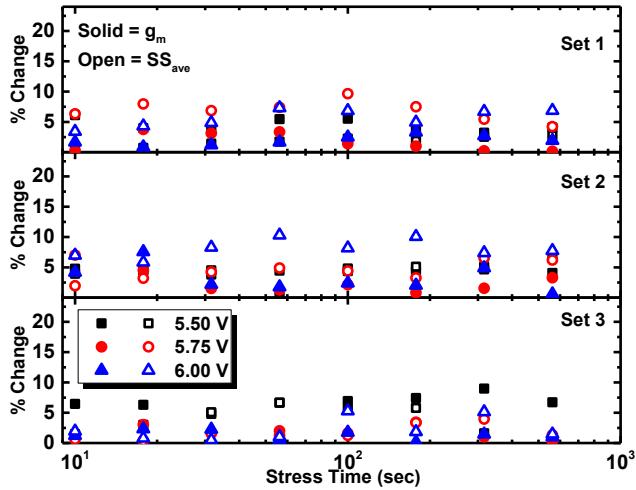

Figure 2. Example  $I_{DS}$ - $V_{GS}$  of TFTs with  $100^{\circ}\text{C}$   $\text{Al}_2\text{O}_3$  at 3 different stress biases. The threshold voltage ( $V_T$ ) shift appears to be minor with no apparent degradation in the subthreshold slope (SS); however, a “turn-around” effect is observed during stress.

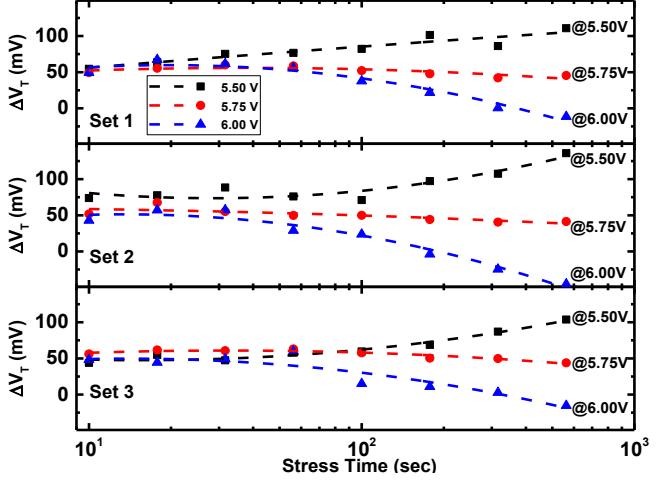

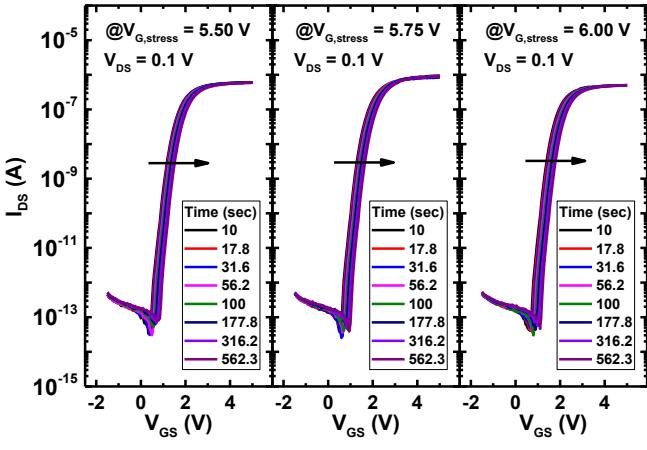

Figure 3. The  $\Delta V_T$  vs stress time for different sets of TFTs with  $100^{\circ}\text{C}$   $\text{Al}_2\text{O}_3$  at 3 different stress biases. The fitted lines show the  $\Delta V_T$  demonstrating the “turn-around” effect shown in Fig. 2.

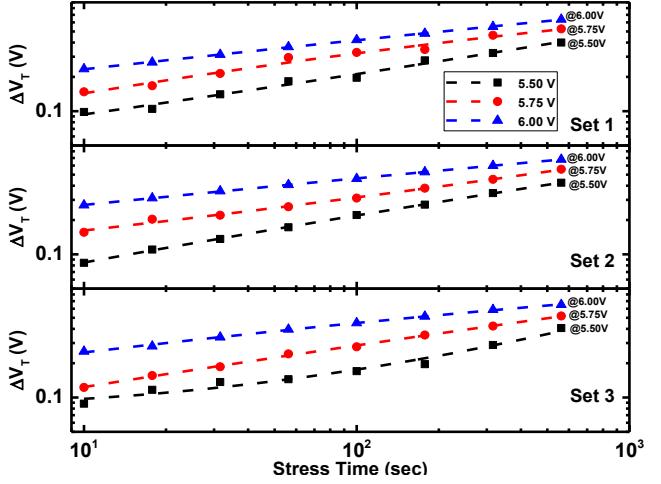

Figure 4. The % change in maximum transconductance ( $g_m$ ) and average subthreshold swing ( $SS_{ave}$ ) for TFTs with  $100^{\circ}\text{C}$   $\text{Al}_2\text{O}_3$  suggests that there is little to no interface state generation contributing to  $\Delta V_T$  during stress.

### III. DATA/RESULTS AND DISCUSSION

Low-temperature high-k dielectrics are essential for compatibility with large-area/flex electronics. A comparison between a  $100^{\circ}\text{C}$  and a more robust  $250^{\circ}\text{C}$  dielectric is needed for understanding the effect of dielectric deposition temperature on  $V_T$  instability. To demonstrate consistent trends across devices, multiple TFTs were measured for each deposition temperature at 3 different stress voltages.  $V_T$  is

extracted using linear extrapolation of  $I_D$ - $V_G$  at the point of maximum transconductance. All devices had dimension of  $W/L = 400/20 \mu\text{m}$ , as shown in the plan-view picture of a device in Fig. 1.

#### A. $\text{Al}_2\text{O}_3$ Deposited at $100^{\circ}\text{C}$

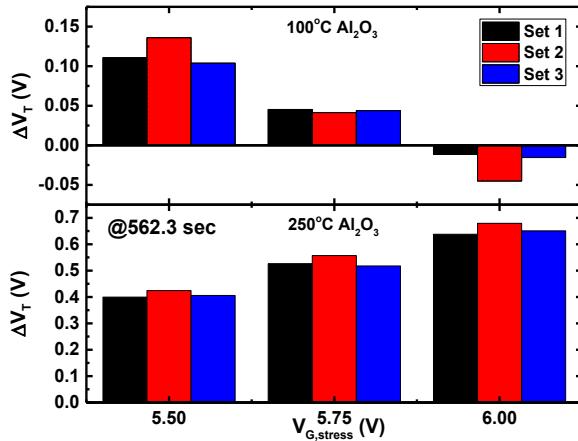

Fig. 2 illustrates the evolution of  $I_D$ - $V_G$  degradation for devices with  $100^{\circ}\text{C}$   $\text{Al}_2\text{O}_3$  at the three different stress bias conditions. One can observe a minor  $V_T$  shift with little to no degradation in either  $g_m$  or SS. Extraction of the  $\Delta V_T$  across all three sets of TFTs in Fig. 3 yields a more comprehensive understanding of the behavior of the  $V_T$  with stress time. At a stress voltage of  $5.5 \text{ V}$ , the  $V_T$  monotonically increases, but at voltages of  $5.75 \text{ V}$  and  $6 \text{ V}$ , an initial positive  $V_T$  shift is observed followed by a negative  $V_T$  shift. This “turn-around” phenomenon has been observed in Hf-based dielectrics [8], [9] as well more recently in IGZO TFTs [10]–[12]. This effect is exacerbated at higher voltages, consistent with previous reports [13]. This suggests that for TFTs with  $100^{\circ}\text{C}$   $\text{Al}_2\text{O}_3$ , the defect mechanism responsible for the negative  $\Delta V_T$  is dominant at higher voltages compared to the defect mechanism responsible for positive  $\Delta V_T$  observed at the lower voltage. This could be due to the lower temperature deposition of  $100^{\circ}\text{C}$ , where an additional defect may be present, which may be responsible for “turn-around” effect thereby enabling electron de-trapping to occur at the same time as electron trapping. Previous temperature dependent studies suggest that higher residual hydrogen content ( $>10 \text{ at.}\%$ ) in low temperature  $\text{Al}_2\text{O}_3$  may be the culprit [14]. Fig. 4 shows the negligible % change in the  $g_m$  and average SS (extracted using an exponential fit from  $10^{-11} \text{ A}$  to  $10^{-9} \text{ A}$ ) for all sets with  $100^{\circ}\text{C}$   $\text{Al}_2\text{O}_3$ , suggesting little to no interface state generation.

Figure 5. Example  $I_{DS}$ - $V_{GS}$  of TFTs with 250°C  $\text{Al}_2\text{O}_3$  at 3 different stress biases. The threshold voltage ( $V_T$ ) shift is significant in this dielectric with no apparent degradation in the subthreshold slope (SS). No “turn-around” effect is present during stress.

Figure 6. The  $\Delta V_T$  vs stress time for different sets of TFTs with 250°C  $\text{Al}_2\text{O}_3$  at 3 different stress biases. The fitted lines show trends consistent with traditional PBTI in MG/HK nMOS degradation.

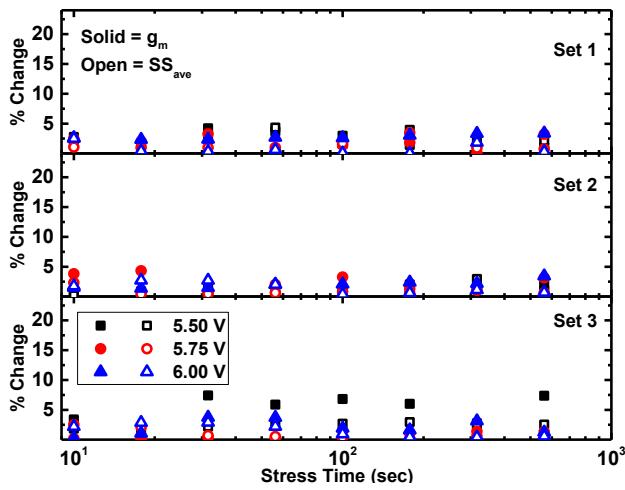

Figure 7. The % change in  $g_m$  and  $SS_{ave}$  for TFTs with 250°C  $\text{Al}_2\text{O}_3$  suggests that there is little to no interface state generation contributing to  $\Delta V_T$ , similar to the 100°C  $\text{Al}_2\text{O}_3$  samples.

### B. $\text{Al}_2\text{O}_3$ Deposited at 250°C

The Fig. 5 demonstrates the evolution of the  $I_D$ - $V_G$  for devices with 250°C  $\text{Al}_2\text{O}_3$  at three different stress conditions. One can observe a more prominent  $V_T$  shift, compared to the 100°C samples, with little to no degradation in either  $g_m$  or SS. The extracted  $\Delta V_T$  with stress in Fig. 6 shows monotonically increasing  $V_T$  across all sets, consistent with the trends observed for typical PBTI in MG/HK NMOS, suggesting an electron trapping mechanism. Fig. 7 shows negligible % change in  $g_m$  and  $SS_{ave}$  for the 250°C samples, similar to the 100°C samples in Fig. 4, suggesting little to no interface state generation contributing to the  $V_T$  shift.

### C. 100°C vs. 250°C $\text{Al}_2\text{O}_3$

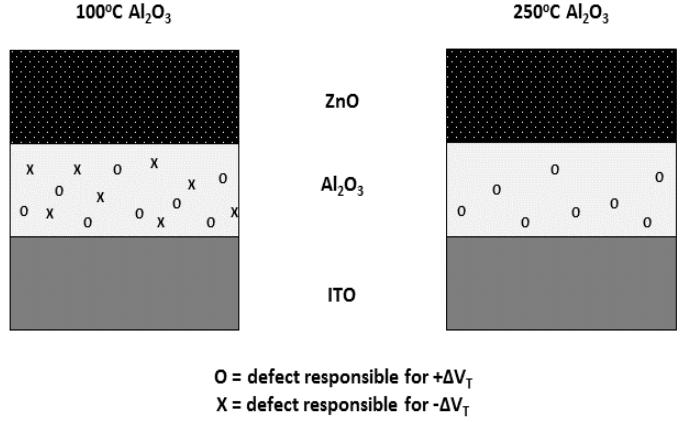

At first glance, comparing the  $I_D$ - $V_G$  measurements in Fig. 2 (100°C) with Fig. 5 (250°C), as well as Fig. 8, the low-temperature  $\text{Al}_2\text{O}_3$  appears to have smaller  $V_T$  shifts than the 250°C samples. Intuitively, the high-temperature  $\text{Al}_2\text{O}_3$  should have less  $V_T$  degradation, not more. This suggests that the two different defect mechanisms attributed to the  $+\Delta V_T$  and  $-\Delta V_T$  in the 100°C samples are competing, leading a smaller net  $\Delta V_T$ ; whereas, the 250°C samples only have contribution from the defect mechanism attributed to the  $+\Delta V_T$ , as illustrated in Fig. 9.

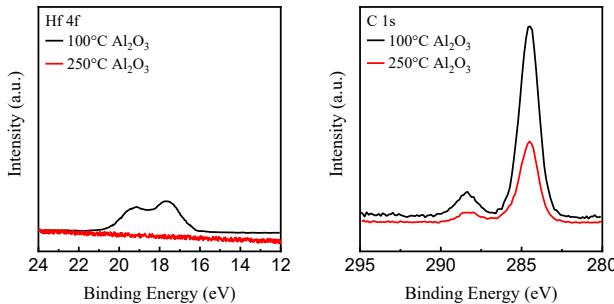

In an effort to comprehend why there appears to be this turn around effect, further analysis was conducted. As mentioned before, higher residual hydrogen content may be incorporated in low temperature  $\text{Al}_2\text{O}_3$ , where the at % of hydrogen present in low temperature  $\text{Al}_2\text{O}_3$  decreases significantly with increasing temperature [14]. This would further indicate that the higher concentration of hydrogen in 100°C  $\text{Al}_2\text{O}_3$  may be partially responsible for the observed “turn-around” effect, whereas at 250°C, the reduction in hydrogen content may not contribute significantly to the  $\Delta V_T$ . Furthermore, after device fabrication and stress measurements results, the “turn-around” effect prompted the investigation of the elemental composition of  $\text{Al}_2\text{O}_3$  thin films in order to ascertain if there was any other potential reason for the  $-\Delta V_T$ . The XPS spectra of the  $\text{Al}_2\text{O}_3$  used in this work in Fig. 10 show Hf content in the 100°C  $\text{Al}_2\text{O}_3$ , as well as carbon. Yet, the Hf is not present in the 250°C  $\text{Al}_2\text{O}_3$  sample, suggesting the Hf may be a contributing factor to the “turn-around” effect. There is also a reduction in carbon in the 250°C  $\text{Al}_2\text{O}_3$ , as has been shown in previous reports [14]. Upon further review, the 100°C  $\text{Al}_2\text{O}_3$  deposition was done first, then the 250°C deposition. Thus, prior contamination from a previous

Figure 8. Comparison of  $\Delta V_T$  at a fixed time between the TFTs with 100°C  $\text{Al}_2\text{O}_3$  and 250°C  $\text{Al}_2\text{O}_3$ . Results demonstrate lower  $\Delta V_T$  for the 100°C samples possibly caused by the proposed competing mechanisms of simultaneous electron trapping and de-trapping within stress duration.

Figure 9. The schematic cross-sections of the gate stack for ZnO TFTs with different  $\text{Al}_2\text{O}_3$  deposition temperature, illustrating an additional, plausible defect present away from the  $\text{Al}_2\text{O}_3/\text{ZnO}$  interface the defect mechanisms responsible for  $+\Delta V_T$  and  $-\Delta V_T$  in the 100°C  $\text{Al}_2\text{O}_3$  samples.

Figure 10. Comparison of XPS spectra of different temperature  $\text{Al}_2\text{O}_3$  with (left) Hf 4f and (right) C 1s. These spectra show Hf content in oxide state, not metallic state, in 100°C  $\text{Al}_2\text{O}_3$  as well as C content. For the 250°C  $\text{Al}_2\text{O}_3$ , the Hf is below the limit of detection and the C is still present but at a lower concentration.

$\text{HfO}_2$  deposition provided the residual Hf detected in the 100°C  $\text{Al}_2\text{O}_3$ .

Another future work would involve the deconvolution of the exact defect responsible, whether it be the hydrogen or the hafnium or both, and the removal of the defect attributed to  $-\Delta V_T$  to neutralize the “turn-around” effect in order to obtain a better comparison between the 100°C and 250°C samples.

#### IV. CONCLUSIONS

To study the impact of low  $\text{Al}_2\text{O}_3$  deposition temperature on  $V_T$  instability, ZnO TFTs were subjected to gate stress bias. For devices with  $\text{Al}_2\text{O}_3$  deposited at 100°C, the  $V_T$  degradation

in the interspersed  $I_D$ - $V_G$  measurements appears minimal. Extraction of  $\Delta V_T$  for multiple sets of devices demonstrates a “turn-around” phenomenon in samples with 100°C  $\text{Al}_2\text{O}_3$ , which is attributed to two competing defect mechanisms in  $\text{Al}_2\text{O}_3$  responsible for the  $+\Delta V_T$  and  $-\Delta V_T$  shifts. Compared to the 100°C samples, the samples with 250°C  $\text{Al}_2\text{O}_3$  demonstrate monotonically increasing  $V_T$  with stress time and voltage, consistent with trends observed for more traditional PBI in MG/HK nMOS. Both sets of samples show little to no degradation in  $g_m$  and  $SS_{ave}$ , suggesting that interface state generation is not a major contributor to the  $V_T$  instability.

#### ACKNOWLEDGMENT

This work was supported in part by the National Science Foundation CAREER Award under the NSF award number ECCS-1653343, and AFOSR project FA9550-18-1-0019. Furthermore, the authors thank CONACYT for Fellowship support of R.A. Rodriguez-Davila.

#### REFERENCES

- [1] G. Gutierrez-Heredia *et al.*, “Fully patterned and low temperature transparent ZnO-based inverters,” *Thin Solid Films*, vol. 545, pp. 458–461, Oct. 2013.

- [2] M. Horita, Y. Ishikawa, Y. Uraoka, and Y. Kawamura, “Effects of Gate Insulator on Thin-Film Transistors With ZnO Channel Layer Deposited by Plasma-Assisted Atomic Layer Deposition,” *J. Disp. Technol.*, Vol. 9, Issue 9, pp. 694–698, vol. 9, no. 9, pp. 694–698, Sep. 2013.

- [3] M. S. Oh, W. Choi, K. Lee, D. K. Hwang, and S. Im, “Flexible high gain complementary inverter using n-ZnO and p-pentacene channels on polyethersulfone substrate,” *Appl. Phys. Lett.*, vol. 93, no. 3, p. 033510, Jul. 2008.

- [4] R. A. Chapman, R. A. Rodriguez-Davila, I. Mejia, and M. Quevedo-Lopez, “Nanocrystalline ZnO TFTs Using 15-nm Thick  $\text{Al}_2\text{O}_3$  Gate Insulator: Experiment and Simulation,” *IEEE Trans. Electron Devices*, vol. 63, no. 10, pp. 3936–3943, Oct. 2016.

[5] D. Siddharth, G. Gutierrez-Heredia, I. Mejia, S. Benton, M. Quevedo-Lopez, and C. D. Young, "Investigation of  $V_t$  Instability in ZnO TFTs with an  $HfO_2$  Dielectric," in *18th International Workshop on Dielectrics in Microelectronics (WoDiM)*, 2014.

[6] D. Siddharth, P. Zhao, I. Mejia, S. Benton, M. Quevedo-Lopez, and C. D. Young, "Threshold Voltage Instabilities in Zinc Oxide Thin Film Transistors with High-k Dielectrics," in *IEEE International Integrated Reliability Workshop (IIRW)*, 2014.

[7] R. A. Rodriguez-Davila, I. Mejia, M. Quevedo-Lopez, and C. D. Young, "Hot Carrier Stress Investigation of Zinc Oxide Thin Film Transistors with an  $Al_2O_3$  Gate Dielectric," in *2018 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA)*, 2018, pp. 1–4.

[8] M. Sato *et al.*, "Study of a Negative Threshold Voltage Shift in Positive Bias Temperature Instability and a Positive Threshold Voltage Shift the Negative Bias Temperature Instability of Yttrium-Doped  $HfO_2$  Gate Dielectrics," *Jpn. J. Appl. Phys.*, vol. 49, no. 4, p. 04DC24, Apr. 2010.

[9] M. Houssa, *High-k Gate Dielectrics*. 2003.

[10] G. Reimbold, J. Mitard, X. Garros, C. Leroux, G. Ghibaudo, and F. Martin, "Initial and PBTI-induced traps and charges in Hf-based oxides/TiN stacks," *Microelectron. Reliab.*, vol. 47, no. 4–5, pp. 489–496, Apr. 2007.

[11] N. Sa *et al.*, "Mechanism of positive-bias temperature instability in sub-1-nm  $TaN/HfN/HfO_2$  gate stack with low preexisting traps," *IEEE Electron Device Lett.*, vol. 26, no. 9, pp. 610–612, Sep. 2005.

[12] H.-S. Jung *et al.*, "The Bias Temperature Instability Characteristics of In Situ Nitrogen Incorporated  $ZrO_xN_y$  Gate Dielectrics," *Electrochem. Solid-State Lett.*, vol. 13, no. 9, p. G71, Sep. 2010.

[13] G. Baek, L. Bie, K. Abe, H. Kumomi, and J. Kanicki, "Electrical Instability of Double-Gate a-IGZO TFTs With Metal Source/Drain Recessed Electrodes," *IEEE Trans. Electron Devices*, vol. 61, no. 4, pp. 1109–1115, Apr. 2014.

[14] O. M. E. Ylivaara *et al.*, "Aluminum oxide from trimethylaluminum and water by atomic layer deposition: The temperature dependence of residual stress, elastic modulus, hardness and adhesion," *Thin Solid Films*, vol. 552, pp. 124–135, Feb. 2014.