# InAs FinFETs Performance Enhancement by Superacid Surface Treatment

Yuping Zeng, Sourabh Khandelwal<sup>®</sup>, Kazy F. Shariar<sup>®</sup>, Zijian Wang, Guangyang Lin, Qi Cheng, Peng Cui, Robert Opila, Ganesh Balakrishnan, Sadhvikas Addamane, Peyman Taheri, Daisuke Kiriya, Mark Hettick, and Ali Javey

Abstract—In this paper, a post superacid (SA) treatment was proposed to enhance the performance of InAs FinFETs on SiO<sub>2</sub>/Si substrates. Typically, the subthreshold swing (SS) has reduced from 217 to 170 mV/decade and the transconductance  $(g_m)$  has increased from 6.44 to 26.5  $\mu$ S/ $\mu$ m after SA treatment. It was found that the interfacial In<sub>2</sub>O<sub>3</sub> at the InAs/ZrO<sub>2</sub> interface was effectively reduced after SA treatment due to the strong protonating nature of the SA solution. As a result, the interface trap density was reduced leading to a pronounced reduction of sheet resistance after SA treatment. The modeling of transfer characteristics indicates that the carrier mobility is enhanced by 5.8~7.1 folds after SA treatment due to interfacial traps reduction. The results suggest that SA treatment can be potentially extended to other III-V MOSFETs to enhance the device performances.

Index Terms—FinFETs, superacid (SA), surface treatment.

## I. INTRODUCTION

SILICON-BASED transistors have been the workhorse of the semiconductor industry for several decades, enabling ever-increasing performance, density, and functionality. However, at the nanoscale, for technology nodes 7 nm and beyond, traditional scaling of silicon transistors has become increasingly difficult and does not give any performance improvement. In recent years, much attention has been paid to III–V n-MOSFETs, such as InP [1],  $In_xGa_{1-x}As$  [2], and InAs [3] materials, due to their superior electron mobility and potential to enhance device performances. With Indium content

Manuscript received December 3, 2018; accepted February 20, 2019. Date of publication March 8, 2019; date of current version March 22, 2019. The review of this paper was arranged by Editor W. Tsai. (Yuping Zeng, Sourabh Khandelwal, Kazy F. Shariar, and Zijian Wang contributed equally to this work.) (Corresponding author: Yuping Zeng.)

Y. Zeng, K. F. Shariar, G. Lin, Q. Cheng, and P. Cui are with the Department of Electrical and Computer Engineering, University of Delaware, Newark, DE 19716 USA (e-mail: yzeng@udel.edu; shariar@udel.edu).

- S. Khandelwal is with the Department of Science and Engineering, Macquarie University, Sydney, NSW 2109, Australia (e-mail: sourabh.khandelwal@mq.edu.au).

- Z. Wang and R. Opila are with the Department of Materials Science and Engineering, University of Delaware, Newark, DE 19716 USA.

- G. Balakrishnan and S. Addamane are with the Department of Electrical and Computer Engineering, The University of New Mexico, Albuquerque, NM 87106 USA (e-mail: gunny@unm.edu).

- P. Taheri, D. Kiriya, M. Hettick, and A. Javey are with the Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, Berkeley, CA 94720 USA (e-mail: ajavey@eecs.berkeley.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2019.2901281

enrichment, the injection velocity of  $In_xGa_{1-x}As$  increases continuously rendering an attractive InAs channel material for n-MOSFET with an injection velocity of  $\sim 4 \times 10^7$  cm/s. Simultaneously, the integration of III–V devices on a silicon substrate is in great need due to the tremendous infrastructure available for silicon processing. Indeed, heterogeneous integration of these materials on Si substrates is being vigorously explored [4]–[6]. Such technology offers a desirable combination of high channel mobility and the well-established, low-cost processing of Si technology. One of such techniques is the epitaxial transfer of InAs layers with nanometer scale thicknesses onto Si/SiO<sub>2</sub> substrates demonstrated for use as high-performance nanoscale transistors [7].

By employing the transferred InAs nanoribbons from this platform, InAs FinFETs can be made. Realizing feature sizes at sub-20 nm is one of the key steps to make these FinFETs. The dry etching process is a conventional tool to create such fine features due to its anisotropic etching property. Chlorine-based dry etching is often used to etch III–V materials. However, most of the chlorine-containing gases contain carbon and often problems are encountered with the deposition of polymer films during etching, resulting in a poor material surface quality and, therefore, degraded device performances. Various surface treatment methods to improve surface quality have been investigated, such as oxygen plasma treatment [8] and surface passivation techniques. However, these methods seem to be complex, costly, and time-consuming.

In this paper, we propose a simple and low-cost approach to improve the performance of InAs FinFETs fabricated by a dry etching process with post surface treatment by superacid (SA). The low field-effect mobility was observed to increase by 5.8~7.1 folds reaching 671~1378 cm<sup>2</sup> · V<sup>-1</sup> · s<sup>-1</sup>. To the best of our knowledge, this is the first demonstration of InAs FinFET mobility improvement by SA treatment. The detailed mechanisms are investigated and discussed.

# II. EXPERIMENTAL DETAILS

The InAs FinFETs were fabricated from InAs ribbons on SiO<sub>2</sub>/Si substrate, which were obtained by the transfer method [7]. Epitaxially grown InAs films on AlGaSb/GaSb substrate were used as the InAs donor during the transfer process. Through standard lithography and wet etching, InAs ribbon arrays were first fabricated on the AlGaSb/GaSb substrate. After subsequent selective wet etch of the underlying

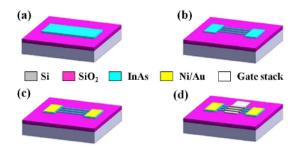

Fig. 1. Fabrication process flow of InAs FinFETs: (a) transfer of InAs ribbons on SiO<sub>2</sub>/Si substrate; (b) fin formation on InAs ribbons; (c) metallization of S/D; and (d) deposition of gate oxide and gate metal.

AlGaSb layer, InAs ribbon arrays were then transferred on the SiO<sub>2</sub>/Si substrate using an elastomeric PDMS slab, as shown in Fig. 1(a).

Fig. 1(b) and (c) further exhibits the schematic of the fabrication process for InAs FinFETs. By e-beam lithography (EBL) and inductively coupled plasma (ICP) dry etching methods, fins with widths of 20 and 25 nm were formed along the InAs ribbons [see Fig. 1(b)]. During this step, hydrogen silsesquioxane (HSQ) was used as EBL resist and subsequent dry etching mask. The ICP process was carried out at the ambient of CH<sub>4</sub>/H<sub>2</sub>/Cl<sub>2</sub>/Ar with a ratio of 8/5.5/5/15 for 25 s. The substrate holder was maintained at room temperature with ICP and RF power of 590 and 70 W, respectively. After dry etching, samples were dipped in diluted HF (HF: $H_2O = 2.98$ ) for 120 s to remove the HSQ mask. Next, contact windows were opened at the ends of the fins by EBL to form source/drain (S/D) metal contacts [see Fig. 1(c)]. After the removal of native oxide by diluted HF (HF: DI = 1:99), Ni/Au (40 nm/15 nm) metal was evaporated and lifted off. After that, 8-nm ZrO<sub>2</sub> was deposited as gate oxide by atomic layer deposition (ALD) at 130 °C with Tetrakis (ethylmethylamino) zirconium (IV) (TEMAZ) as Zr source and H<sub>2</sub>O as oxygen source. Ultimately, 50-nm Ni was selectively evaporated as gate metal forming the final device with a channel length of 1  $\mu$ m as shown in Fig. 1(d).

An organic SA, bis (trifluoromethane) sulfonamide (TFSI), which is a strong protonating agent and have a Hammett acidity function that is lower than pure sulfuric acid (H<sub>2</sub>SO<sub>4</sub>) [9], was prepared in a glove box for surface treatment on the completed InAs FinFETs. To prepare the TFSI solution, 24 mg TFSI powder was first dissolved in 12 mL 1, 2-dichloroethene (DCE) to form TFSI solution with solute concentration of 2 mg/mL; then 0.5 mL of the 2 mg/mL TFSI solution was diluted with 4.5 mL 1, 2-dichlorobenzene (DCB) forming a 0.2 mg/mL TFSI solution. The InAs FinFETs were immersed in the 0.2 mg/mL solution for 20 s at air ambient, then blow-dried with N<sub>2</sub>.

The electrical performance of the InAs FinFETs before and after SA treatment was characterized by HP4156B semiconductor parameter analyzer. To facilitate analysis of chemical components at gate oxide/channel interface before and after SA treatment, X-ray photoelectron spectroscopy (XPS) were taken by PHI model 5600 with Al K $\alpha$  dual sources (h $\nu$  = 1486.6 eV) under a base pressure of 4 × 10<sup>-9</sup> Torr [10], [11].

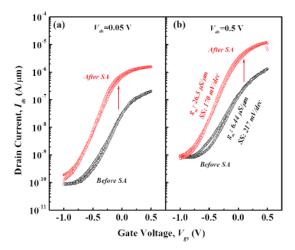

Fig. 2. Typical transfer characteristics of the InAs FinFETs with fin width of 25 nm before (black curve) and after SA (red curve) treatment under (a)  $V_{\rm ds}=0.05$  and (b)  $V_{\rm ds}=0.5$  V. A significant current increase and steeper SS after SA treatment can be observed.

## III. RESULTS AND DISCUSSIONS

# A. I∼V Measurement

Fig. 2 shows typical transfer characteristics ( $I_{ds}$ – $V_{gs}$ ) of the FinFET with fin width of 25 nm before and after SA treatment at  $V_{\rm ds} = 0.05$  V [see Fig. 2(a)] and  $V_{\rm ds} = 0.5$  V [see Fig. 2(b)], respectively. Before SA treatment, a hysteresis of  $I \sim V$  curves is observed when sweeping  $V_{gs}$  backward and forward due to the existence of abundant traps at the channel/gate oxide interface. With SA treatment, at  $V_{\rm ds} = 0.05$  V, the ON/OFF ratio increased from  $2.35 \times 10^3$  to  $8.18 \times 10^3$  $10^3(\sim 3.5 \times)$  with ON-current from 0.20 to 1.56  $\mu$ A/ $\mu$ m ( $\sim$ 7.8×). Similarly, at  $V_{\rm ds}=0.5$  V, the ON/OFF ratio increased from  $1.51 \times 10^3$  to  $12.1 \times 10^3 (\sim 8 \times)$  with on-current from 1.30 to 13.15  $\mu$ A/ $\mu$ m ( $\sim$ 10×). It should also be noted that, after SA treatment, the hysteresis phenomenon is not as pronounced. The extracted subthreshold swing (SS) is reduced from 217 to 170 mV/decade. The reduction of SS suggests that the density of interfacial traps  $(D_{it})$  was effectively reduced after SA treatment. From the extracted SS,  $D_{it}$  can be quantitatively calculated based on the following equation [12]:

$$\frac{2.3 \,\mathrm{kT}}{q} \left( 1 + \frac{C_{\mathrm{it}}}{C_{\mathrm{ZrO}_2}} + \frac{C_{\mathrm{body}}}{C_{\mathrm{ZrO}_2}} - \frac{\frac{C_{\mathrm{body}}^2}{C_{\mathrm{ZrO}_2} + C_{\mathrm{SiO}_2}}}{1 + \frac{C_{\mathrm{it}}}{C_{\mathrm{SiO}_2}} + \frac{C_{\mathrm{body}}}{C_{\mathrm{SiO}_2}}} \right) = \mathrm{SS},\tag{1}$$

where k, T, and q are Boltzmann [12]: sed, sample temperature, and elementary charge, respectively;  $C_{\rm ZrO2}$ ,  $C_{\rm SiO2}$ , and  $C_{\rm body}$  represent the capacitance of  ${\rm ZrO_2}$ ,  ${\rm SiO_2}$ , and the substrate per unit area, respectively;  $C_{\rm it}$  is the capacitance caused by interface traps per unit area and is given by  $C_{\rm it} = q D_{\rm it}$ . For the presented device,  $D_{\rm it}$  has reduced from  $1.21 \times 10^{13}$  cm<sup>-2</sup> before SA treatment to  $7.91 \times 10^{12}$  cm<sup>-2</sup> after SA treatment. The calculated  $D_{\rm it}$  along with SS before and after SA treatment for several different devices were summarized in Table I. For all devices, both of SS and  $D_{\rm it}$  values reduce

$W_{fin}=20 \text{ nm}$

| Device $(L_g=1 \mu m)$              |           | SS<br>(mV/decade) | $D_{it}$ (cm <sup>-2</sup> ) |

|-------------------------------------|-----------|-------------------|------------------------------|

| <i>W<sub>fin</sub></i> =25 nm       | Before SA | 156               | 6.74x10 <sup>12</sup>        |

|                                     | After SA  | 130               | 4.69x10 <sup>12</sup>        |

| W <sub>fin</sub> =25 nm (presented) | Before SA | 217               | 1.21x10 <sup>13</sup>        |

|                                     | After SA  | 170               | 7.91x10 <sup>12</sup>        |

| W <sub>fin</sub> =20 nm             | Before SA | 98                | 2.40x10 <sup>12</sup>        |

|                                     | After SA  | 70                | 6.20x10 <sup>11</sup>        |

|                                     | Before SA | 530               | 4.43x10 <sup>13</sup>        |

170

After SA

8.76x10<sup>3</sup>

TABLE I

SUMMARY OF SS AND DIT FOR DIFFERENT DEVICES

BEFORE AND AFTER SA TREATMENT

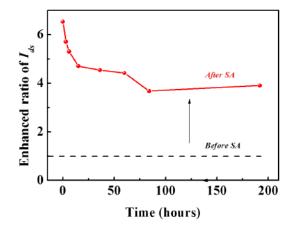

Fig. 3. Time-dependent study of  $I_{\rm ds}$  enhancement ratio for the reproduced device ( $W_{\rm fin}$ : 20 nm,  $L_g$ : 500 nm) after SA treatment under  $V_{\rm gs}$  of 0.9 V and  $V_{\rm ds}$  of 1 V.

distinctly after SA treatment indicating the passivation effect of SA on interfacial traps.

To verify the effectiveness of the proposed method, another batch of devices ( $W_{\rm fin}$ : 20 nm,  $L_g$ : 500 nm) were fabricated and the improvement of the device performance was reproduced in a second lab (Previously done in UC Berkeley and now reproduced in University of Delaware). Fig. 3 displays the time-dependent study of  $I_{\rm ds}$  for the reproduced device under  $V_{\rm gs}$  of 0.9 V and  $V_{\rm ds}$  of 1 V after SA treatment. The enhanced ratio of  $I_{\rm ds}$  decreases gradually from 6.54 to 3.68 after  $\sim$ 80 h. However, as time further elapses, the enhanced ratio becomes almost constant within the studied period indicating stable enhancement of the device performance after SA treatment.

#### B. TLM Measurement

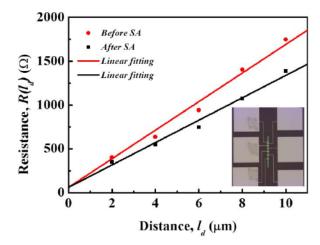

A linear transmission line model (TLM) was used to subsequently investigate the effect of SA treatment on the sheet resistance ( $R_s$ ) and contact resistance ( $R_c$ ) between InAs and Ni/Au. Electrodes with different gap spacing ( $l_d$ ) were fabricated along the InAs ribbons on SiO<sub>2</sub>/Si substrate, as shown in Fig. 4 (inset). The width of the ribbon was 4  $\mu$ m (W) with contact areas of 4 × 4  $\mu$ m<sup>2</sup>, while  $l_d$  varied from 2 to 12  $\mu$ m.

Fig. 4. Resistance (R) between adjacent pads as a function of gap spacing ( $I_d$ ) from transmission line measurement under different conditions before (red) and after (black) SA treatment.

Through measuring the resistance (R) between adjacent pads,  $R_s$  and  $R_c$  can be extracted from the linear fitting of the  $R \sim l_d$  curve by the following equation [13]:

$$R(l_d) = R_s \frac{l_d}{W} + 2R_c. \tag{2}$$

Fig. 4 shows the measured values of R under different  $l_d$  along with corresponding fitting results before and after SA treatment. External resistance had been eliminated by using Kelvin probes. The measured results reveal that  $R_s$  had reduced from 652.1 to 501.5  $\Omega/\Box$ , while  $R_c$  remained almost the same at 30.5  $\Omega$  after SA treatment suggesting enhancement of the InAs mobility due to the reduction of  $D_{it}$ . Consequently, the improvement of on-current of InAs FinFETs after SA treatment can be ascribed to a reduction of  $R_s$ .

It should be noted that the TLM measurements were carried out on InAs ribbons rather than on Fin structures. For InAs ribbons, the sidewalls were formed by wet etching instead of ICP dry etching. Therefore, the interface trap density at these sidewalls is expected to be less than that formed by dry etching. The reduction of sheet resistance was mainly due to the passivation of interfacial states on the top surface. While for Fin structures, the passivation effect on the two side walls should also be considered since the channel of FinFETs was controlled on both the top surface and side walls. Thus, the actual reduction of sheet resistance for FinFETs may be much more pronounced leading to a significant enhancement of carrier mobility.

# C. XPS Measurement

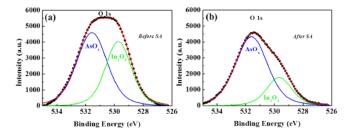

To shed light on passivation mechanisms of the interfacial traps after SA treatment, high-resolution XPS measurements were carried out. Fig. 5(a) and (b) displays the measured spectrum of O 1s for an InAs film on Si before and after SA treatment, respectively. The peak positions have been calibrated by C 1s peak (284.8 eV) and the background intensity has been subtracted. From peak fitting results by PHI MATLAB code, two subpeaks due to native oxides are observed in O 1s spectrum before SA treatment. The peak at

Fig. 5. Measured XPS spectra of O 1s and related fitting results for lnAs (a) before and (b) after SA treatment, respectively. The native oxide of lnAs, especially  $\ln_2 O_3$ , was effectively reduced after SA treatment.

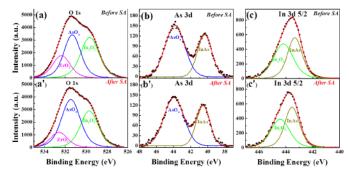

Fig. 6. XPS spectra of (a) O 1s, (b) As 3d and (c) In 3d 5/2 and related fitting results for InAs on Si substrate encapsulated with 4-nm ZrO<sub>2</sub> before SA treatment; XPS spectra of (a') O 1s, (b') As 3d and (c') In 3d 5/2 and related fitting results for InAs electronic device encapsulated with ZrO<sub>2</sub> after SA treatment.

529.7 eV corresponds to  $In_2O_3$  while the peak at 531.5 eV corresponds to  $AsO_x$ (a mixture of  $As_2O_3$  and  $As_2O_5$ ) [14]–[16]. After SA treatment, the intensity of  $AsO_x$  remains almost constant, while the intensity of  $In_2O_3$  reduces greatly. The integrated intensity ratio between  $AsO_x$  and  $In_2O_3$  has increased from 1.34 before SA treatment to 3.13 after SA treatment. The result suggests that the native oxide of InAs, especially  $In_2O_3$ , can be effectively reduced after SA treatment due to strong protonating nature of the SA solution.

Fig. 6(a)–(c) displays the XPS spectrum of O 1s, As 3d, and In 3d 5/2 and related fitting results for InAs on Si substrate encapsulated with 4-nm ZrO<sub>2</sub> [15]–[17] before SA treatment, respectively. The corresponding results after SA treatment are shown in Fig. 6(a')–(c'), respectively.

From Fig. 6(a) and (a'), an additional peak of ZrO<sub>2</sub> located at 532.5 eV is observed. The intensity of AsO<sub>x</sub> remains almost constant after SA treatment, while the intensities of In<sub>2</sub>O<sub>3</sub> and ZrO<sub>2</sub> components decrease. The integrated intensity ratio between AsO<sub>x</sub> and In<sub>2</sub>O<sub>3</sub> has increased from 0.98 before SA treatment to 1.38 after SA treatment. In Fig. 6(b) and (b'), the fitting peaks at 40.4 and 43.9 eV correspond to AsO<sub>x</sub> and InAs, respectively. The intensity of AsO<sub>x</sub> and InAs peaks remain almost constant after SA treatment, agreeing well with the result from O 1s spectra. As for In 3d 5/2 spectra, the fitting peaks at 444.3 and 443.4 eV correspond to In<sub>2</sub>O<sub>3</sub> and InAs, respectively. After SA treatment, the intensity of InAs remains almost constant, while the integrated intensity ratio between In<sub>2</sub>O<sub>3</sub> and InAs decreases from 1.14 to 0.90 after SA treatment. The aforementioned results demonstrate that the

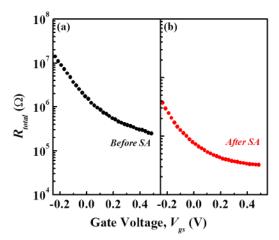

Fig. 7. Total series resistance ( $R_{\rm total}$ ) of InAs FinFET calculated by  $R_{\rm total} = V_{\rm ds}/I_{\rm ds}$  from experimental data (a) before and (b) after SA treatment.

interfacial oxide at the InAs/ZrO<sub>2</sub> interface, especially In<sub>2</sub>O<sub>3</sub>, is effectively reduced after SA treatment.

As reported, oxides are notorious for fast diffusion of hydrogen and its ion [18]. Although metal gate was deposited on ZrO<sub>2</sub> above the channel, hydrogen ions (H<sup>+</sup>) can first diffuse vertically in the ZrO<sub>2</sub> layer in the gap between gate and source (drain), which was not covered by Ni, then diffuse laterally under the Au/Ni gate through ZrO<sub>2</sub> rendering reactivation of H<sup>+</sup> with In<sub>2</sub>O<sub>3</sub> at the ZrO<sub>2</sub>/InAs interface. The interfacial trap density is thus effectively reduced, leading to a significant mobility enhancement.

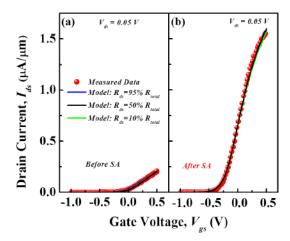

# D. BSIM Model

To further investigate the effect of SA treatment on the carrier mobility of InAs FinFETs, we have modeled I-V characteristics before and after SA treatment based on the industry standard compact model BSIM-CMG [19]. The BSIM-CMG model has considered the quantum-mechanical effects for charge calculations, which is of great significance for III–V materials. Before modeling the I-V curves, the parasitic series resistance between source and drain  $(R_{\rm ds})$  and the channel resistance  $(R_{\rm channel})$  should be given. However, the accurate extraction of  $R_{\rm ds}$  suffers from uncertainties due to limitations of the extraction methods which include data scalability and accuracy. Herein, we take a pragmatic approach to estimate the carrier mobility for our devices.

From linear  $I_{\rm ds}-V_{\rm ds}$  characteristics, the total resistance  $(R_{\rm total})$  between source and drain, which consists of  $R_{\rm ds}$  and  $R_{\rm channel}$ , can be calculated by  $R_{\rm total}=V_{\rm ds}/I_{\rm ds}$ . For the reported device shown in Fig. 2, the dependence of  $R_{\rm total}$  on  $V_{\rm gs}$  before and after SA treatment has been summarized in Fig. 7(a) and (b), respectively. Since  $R_{\rm channel}$  is inversely proportional to  $(V_{\rm gs}-V_{\rm th})$ , where  $V_{\rm th}$  is threshold voltage,  $R_{\rm total}$  becomes smaller at a higher value of  $V_{\rm gs}$ . For our goal of finding an estimated improvement of carrier mobility after SA treatment, we consider that  $R_{\rm ds}$  falls in the range from 10% to 95% of  $R_{\rm total}$  at the highest  $V_{\rm gs}$  ( $V_{\rm gs}=0.5$  V). The consideration follows from practical reasoning that a value

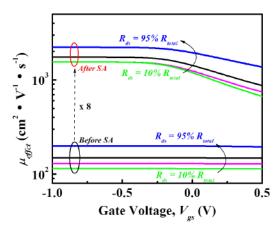

Fig. 8. Modeled  $l_{\rm ds}-V_{\rm gs}$  characteristics of InAs FinFETs (a) before and (b) after SA treatment at  $V_{\rm ds}$  of 0.05 V based on the BSIM-CMG model. The modeling was performed taking  $R_{\rm ds}$  10% -95% of  $R_{\rm total}$ .

Fig. 9. Extracted effective carrier mobility ( $\mu_{\rm effect}$ ) of InAs FinFETs versus  $V_{\rm gs}$  before and after SA treatment by  $I_{\rm ds}-V_{\rm gs}$  modeling based on the BSIM-CMG model. The modeling was performed taking  $R_{\rm ds}$  10%~95% of  $R_{\rm total}$ . After SA treatment, the carrier mobility is enhanced by 5.8~7.1 folds.

of  $R_{\rm ds}$  larger than 95% of  $R_{\rm total}$  would require nonphysical channel mobility to explain experimental drain current. For instance, if one attributes all  $R_{\text{total}}$  to  $R_{\text{ds}}$  (i.e.,  $R_{\text{ds}}$  is 100% of  $R_{\text{total}}$ ) at highest  $V_{\text{gs}}$ , it would require infinite channel mobility to match the measured drain current. The lower limitation of  $R_{ds}$  is summarized from typical values of actual devices [20]. With this range of  $R_{ds}$ , we have modeled the  $I_{ds}-V_{gs}$  characteristics of the InAs FinFETs before and after SA treatment taking  $R_{ds}$  10%–95% of  $R_{total}$ , as shown in Fig. 8(a) and (b), respectively. As can be seen, the modeled curves agree very well with the experimental data for the considered  $R_{ds}$  values. The extracted effective carrier mobility as a function of  $V_{gs}$  before and after SA treatment is exhibited in Fig. 9. Under  $V_{gs}$  of 0.5 V, the carrier mobility before SA treatment is estimated to be  $114 \sim 195 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$ . After SA treatment, the carrier mobility is increased to  $671-1378 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$ , about  $5.8 \sim 7.1$  folds enhancement.

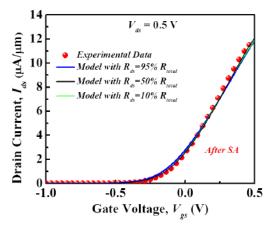

Ultimately, the extracted mobility values are validated by modeling the saturated transfer characteristics of InAs FinFET under  $V_{\rm ds}$  of 0.5 V taking  $R_{\rm ds}$  10%~95% of  $R_{\rm total}$ . With a

Fig. 10. Modeling of the saturation transfer characteristics of InAs FinFETs under  $V_{ds}$  of 0.5 V taking  $R_{ds}$  10%~95% of  $R_{total}$ . A physically reasonable range of 1-1.2  $\times$  10<sup>7</sup> cm/s for saturation velocity was considered for the modeling.

physically reasonable range of  $1-1.2 \times 10^7$  cm/s for saturation velocity  $(v_{\rm sat})$  [21], the modeled saturation  $I_{\rm ds}-V_{\rm gs}$  curves are presented in Fig. 10, which agree very well with the experimental data. The enhancement of carrier mobility is attributed to the reduction in interfacial traps between InAs and ZrO<sub>2</sub> after SA treatment as mentioned earlier since the interfacial charges have a trapping and scattering effect to the carriers. Such enhancement of device performance due to SA treatment can be potentially extended to other III–V MOSFETs consisting of III–V oxide interfacial layers.

# IV. CONCLUSION

In summary, we propose a surface treatment method by SA to improve the performance of InAs FinFETs on SiO<sub>2</sub>/Si substrate. For the reported device, the SS and  $g_m$  have reduced from 217 mV/decade and  $6.44 \times 10^{-6}$  S to 170 mV/decade and  $2.65 \times 10^{-5}$  S with SA treatment, respectively. Through XPS analysis, it was found that the interfacial oxide at the InAs/ZrO2 interface was effectively reduced after SA treatment due to strong protonating nature of the SA solution. The TLM measurements show that the sheet resistance of the InAs ribbon can be greatly reduced from 652.1 to 501.48  $\Omega/\Box$  while the contact resistance is not influenced after SA treatment. From modeling of the transfer characteristics based on the commercial BSIM-CMG model, it was found that the carrier mobility is enhanced from 114~195 cm<sup>2</sup>V<sup>-1</sup>·s<sup>-1</sup> before SA treatment to 671~1378 cm<sup>2</sup> V<sup>-1</sup>·s<sup>-1</sup> after SA treatment due to the reduction of interfacial traps. The results suggest that the SA treatment can be potentially extended to other III-V MOSFETs to enhance the device performances.

# REFERENCES

- Y. Song et al., "Ultra-high aspect ratio InP junctionless FinFETs by a novel wet etching method," *IEEE Electron Device Lett.*, vol. 37, no. 8, pp. 970–973, Aug. 2016. doi: 10.1109/LED.2016.2577046.

- [2] A. Vardi and J. A. del Alamo, "Sub-10-nm fin-width self-aligned InGaAs FinFETs," *IEEE Electron Device Lett.*, vol. 37, no. 9, pp. 1104–1107, Sep. 2016. doi: 10.1109/LED.2016.2596764.

- [3] R. Oxland et al., "InAs FinFETs with H<sub>fin</sub>=20 nm fabricated using a top-down etch process," *IEEE Electron Device Lett.*, vol. 37, no. 3, pp. 261-264, Mar. 2016. doi: 10.1109/LED.2016.2521001.

- [4] Y. Q. Wu, M. Xu, R. S. Wang, O. Koybasi, and P. D. Ye, "High performance deep-submicron inversion-mode InGaAs MOSFETs with maximum G<sub>m</sub> exceeding 1.1 mS/μm: New HBr pretreatment and channel engineering," in *IEEE IEDM Tech. Dig.*, Dec. 2009, pp. 1–4. doi: 10.1109/IEDM.2009.5424358.

- [5] S. Oktyabrsky and P. Ye, Fundamentals of III-V Semiconductor MOSFETs. Boston, MA, USA: Springer, 2010, pp. 31–46. doi: 10.1007/978-1-4419-1547-4.

- [6] M. Radosavljevic et al., "Advanced high-K gate dielectric for high-performance short-channel In<sub>0.7</sub>Ga<sub>0.3</sub>As quantum well field effect transistors on silicon substrate for low power logic applications," in *IEEE IEDM Tech. Dig.*, Baltimore, MD, USA, Dec. 2009, pp. 1–4. doi: 10.1109/IEDM.2009.5424361.

- [7] H. Ko et al., "Ultrathin compound semiconductor on insulator layers for high-performance nanoscale transistors," *Nature*, vol. 468, pp. 286–289, Nov. 2010. doi: 10.1038/nature09541.

- [8] F. N. Dultsev and V. G. Kesler, "Etching and oxidation of InAs in planar inductively coupled plasma," *Appl. Surf. Sci.*, vol. 256, no. 1, pp. 246–250, 2009. doi: 10.1016/j.apsusc.2009.08.009.

- [9] M. Amani, "Near-unity photoluminescence quantum yield in MoS<sub>2</sub>," *Science*, vol. 350, no. 6264, pp. 1065–1068, 2015. doi: 10.1126/science.aad2114.

- [10] J. R. Church, C. Weiland, and R. L. Opila, "Understanding the role of buried interface charges in a metal-oxide-semiconductor stack of Ti/Al<sub>2</sub>O<sub>3</sub>/Si using hard X-ray photoelectron spectroscopy," *Appl. Phys. Lett.*, vol. 106, no. 17, 2015, Art. no. 171601. doi: 10.1063/1.4919448.

- [11] N. A. Kotulak, M. Chen, N. Schreiber, K. Jones, and R. L. Opila, "Examining the free radical bonding mechanism of benzoquinone— and hydroquinone—methanol passivation of silicon surfaces," *Appl. Surf. Sci.*, vol. 354, pp. 469–474, Nov. 2015. doi: 10.1016/j.apsusc.2015.02.127.

- [12] K. Takei, R. Kapadia, H. Fang, E. Plis, S. Krishna, and A. Javey, "High quality interfaces of InAs-on-insulator field-effect transistors with ZrO<sub>2</sub> gate dielectrics," *Appl. Phys. Lett.*, vol. 102, no. 15, 2013, Art. no. 153513. doi: 10.1063/1.4802779.

- [13] H. H. Berger, "Models for contacts to planar devices," Solid-State Electron., vol. 15, no. 2, pp. 145–158, 1972. doi: 10.1016/0038-1101(72)90048-2.

- [14] M. Procop, "XPS data for sputter-cleaned In<sub>0.53</sub>Ga<sub>0.47</sub>As, GaAs, and InAs surfaces," *J. Electron Spectrosc. Related Phenomena*, vol. 59, no. 2, p. R1, 1992. doi: 10.1016/0368-2048(92)85006-S.

- [15] M. Losurdo et al., "InAs(100) surfaces cleaning by an as-free low-temperature 100 °C treatment," J. Electrochem. Soc., vol. 156, no. 4, pp. H263–H267, 2009. doi: 10.1149/1.3076194.

- [16] G. Hollinger, R. Skheyta-Kabbani, and M. Gendry, "Oxides on GaAs and InAs surfaces: An X-ray-photoelectron-spectroscopy study of reference compounds and thin oxide layers," *Phys. Rev. B, Condens. Matter*, vol. 49, no. 16, p. 11159, 1994. doi: 10.1103/PhysRevB.49. 11159.

- [17] X. Guo, Y.-Q. Sun, and K. Cui, "Darkening of zirconia: A problem arising from oxygen sensors in practice," Sens. Actuators B, Chem., vol. 31, no. 3, pp. 139–145, 1996. doi: 4005(96)80058-X.

- [18] H. Muta, Y. Etoh, Y. Ohishi, K. Kurosaki, and S. Yamanaka, "Ab initio study of hydrogen diffusion in zirconium oxide," *J. Nucl. Sci. Tech*nol., vol. 49, no. 5, pp. 544–550, 2012. doi: 10.1080/00223131.2012. 676820.

- [19] S. Khandelwal, J. P. Duarte, A. Medury, Y. S. Chauhan, and C. Hu, "New industry standard FinFET compact model for future technology nodes," in *Proc. Symp. VLSI Technol.*, Jun. 2015, pp. 4–6. doi: 10.1109/VLSIT.2015.7223704.

- [20] S. Sinha, G. Yeric, V. Chandra, B. Cline, and Y. Cao, "Exploring sub-20 nm FinFET design with predictive technology models," in *Proc. Design Automat. Conf.*, Jun. 2012, pp. 15.1–15.5. doi: 10.1145/ 2228360.2228414.

- [21] W. Liu et al., "BSIM 3v3.2 MOSFET model users' manual," Dept. EECS, Univ. California, Berkeley, CA, USA, Tech. Rep. UCB/ERL M98/51, 1998. [Online]. Available: http://www2.eecs.berkeley. edu/Pubs/TechRpts/1998/ERL-98-51.pdf