# A 100kW Switched-Tank Converter for Electric Vehicle Application

Yanchao Li, Ze Ni, Chengkun Liu, Mengxuan Wei and Dong Cao Electrical and Computer Engineering Department North Dakota State Univeristy Fargo, United States Yanchao.li@ndsu.edu

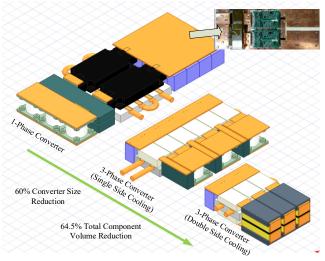

Abstract—This paper presents a 100kW one-cell switched-tank converter (STC) for electric vehicle (EV) application. A new evaluation method that evaluates different converter topologies has been proposed in this paper to show the advantages of the STC over the boost converter and 3-level flying capacitor multilevel (FCML) converter. Both non-interleaved (1-phase) and interleaved (2-phase and 3-phase) operation of the STC have been analyzed. The analytical study shows that it is difficult to achieve the optimum design of the passive components such as input and output capacitors in 1-phase converter because of the high RMS current flowing through them. This means the passive components need to be over-designed in order to meet the current stress requirement. For instance, the designed capacitance of input capacitor is several times of the required value, which leads to bulky capacitor size. Therefore, this paper evaluates the potentials of using 2-phase and 3-phase interleaved operation to address this issue. Two operation modes, zero-voltage switching (ZVS) mode and zero-current switching (ZCS) mode, are evaluated to show the ZCS operation mode is more suitable for the presented converter with interleaved operation. By using the interleaving concept, the predicted 100kW 3-phase interleaved converter can achieve 60% size reduction based on the 1-phase converter design. And the predicted power density of the 3-phase interleaved STC can achieve 115kW/L power density. Simulation results are provided to validate the theoretical analysis. Both 1-phase and 3-phase 100kW prototypes under developing are shown in this paper.

Keywords— resonant, switched-tank, DC-DC, electric vehicle, ZCS, ZVS, SiC

#### I. Introduction

As the growth of environmental awareness among the world, direct vehicle emissions of conventional vehicles are recognized to be harmful to human health and the major source of greenhouse gases. Battery electric vehicles start drawing more and more attention because they have zero direct vehicle emissions. And they could be the key solution to help improve the environment of the world. With the development of SiC technology, SiC devices are widely used in power electronics area, such as inverters[1]–[3], Also, how the leveraging the advantages of SiC devices in electric vehicle powertrain applications become hot topics in recent years[4]–[6].

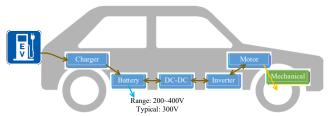

As shown in Fig. 1, the electric vehicle powertrain includes on-board charger, battery system, bi-directional dc-dc converter and motor drive system. The nominal battery voltage is usually around 300V, and the DC bus of the inverter is around 600~800V [7]. Thus, the bi-directional DC-DC converter will

Fig. 1 Powertrain of an electric vehicle

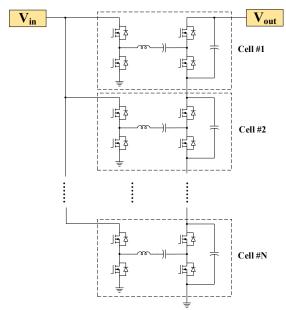

Fig. 2 Generalized circuit structure of the new STC

need to boost the battery voltage up to two times higher and feed to the motor drive system. In [8], a boost converter is optimized to achieve high power density and high efficiency. The volume of the converter is 9.15 liter and it achieves 6kW/L power density. In [9] and [10], a composite boost converter has been presented, it achieves lower loss than conventional boost converter. The predicted volume of the 39kW converter is 1.8 liter. In [11], a three-phase interleaved boost converter shows that interleaved topology can greatly reduce the volume of the converter. In [12], a 100kW boost converter with coupled inductor are presented. The converter achieves 27.9kW/L power density and 98% efficiency.

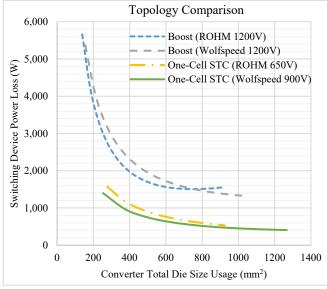

This paper proposed a new evaluation method that evaluates different converter topologies show the advantages of the

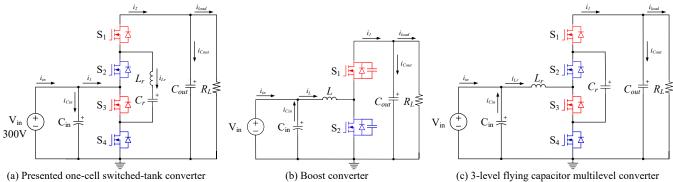

Fig. 3 Circuit configuration of the compared dc-dc converters

presented one-cell STC over the boost converter and 3-level flying capacitor multilevel (FCML) converter. This paper also evaluates the potential converter size reduction by using interleaving concept. Compared with the state-of-art solution that still uses conventional boost converter in the circuit (22kW/L) [10], this paper presents a 1-phase STC that can achieve higher density (45kW/L) with an estimated total volume of 2.2 liters in the second section. However, although the 1-phase converter achieves very high density, the size of passive components (e.g. input and output capacitors) is not optimized because of the high RMS current flowing through them. As a result, interleaved topology has been evaluated to reduce the size of passive components. Both ZVS operation mode and ZCS operation mode are studied in this paper, which shows the ZCS operation mode is more suitable for the interleaved operation. With 3-phase interleaved operation, the estimated converter size reduction can be as high as 60%. Simulation results are provided to show that the RMS current of the passive components has been significantly reduced with 3-phase interleaved operation. At last, a 100kW 1-phase prototype and a 3-phase prototype are demonstrated for size comparison purpose.

## II. CIRCUIT CONFIGURATION AND ANALYSIS

# A. Circuit Configuration and Topology Evaluation

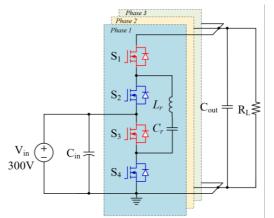

Fig. 2 shows the generalized circuit configuration of the new switched-tank converter. This structure is highly modular and scalable. Fig. 3(a) shows the circuit configuration of the presented one-cell STC. This converter has two operation modes, which are ZCS mode and ZVS mode. Under ZCS operation mode, the conversion ratio of the converter is fixed, which is 2 to 1. Under ZVS operation mode, the output of the converter can be regulated. However, because the converter achieves the highest efficiency when its conversion ratio is 2 to 1 and the DC bus voltage of the inverter does not need to be regulated to a specific value in the existing electric vehicles [13], voltage regulation is not within the scope of this paper.

First, three different converter topologies are compared, which are the one-cell switched-tank converter, 3-level FCML converter and boost converter, as shown in Fig. 3. In this comparison, we assume the boost converter is operating at continues conduction mode (CCM) and the inductor current ripple is 30% of its average current value. So, semiconductor

switching loss of the boost converter cannot be ignored in this topology evaluation part. Also, we assume the 3-level FCML converter and STC operating at ZCS mode. Thus, the semiconductor loss of this two converters is the same.

In order to ensure the fairness of the comparison, semiconductor loss index (SLI) is introduced to evaluate the utilization level of semiconductor devices in all the circuits, which is represented by  $P_{loss\_norm}(A_{die})$ . The semiconductor loss index  $P_{loss\_norm}(A_{die})$  can be calculated by using (1). Note that the  $P_{cond}(A_{die})$ ,  $P_{gate}(A_{die})$  and  $P_{switching}(A_{die})$  means the total semiconductor conduction loss, total gate drive loss and total switching loss of the converter when the total semiconductor die area usage is  $A_{die}$  in a converter. They can be calculated by using equation (2), (3) and (4). In the ZCS case, the total switching loss can be simplified as MOSFET output capacitor loss, as shown in (5). The  $P_{converter}$  is the power rating to the converter. According to (1), we can tell that if the total semiconductor die area usage of two converters are the same, then the converter that has lower semiconductor loss index value is more efficient than the other one. In summary, the converter with lower semiconductor loss index can better utilize the switching devices.

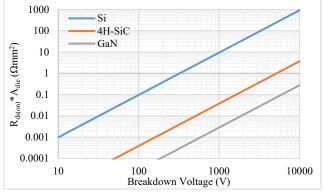

Fig. 4 Theoretical on-resistance and blocking voltage relationship for silicon, silicon-carbide, and gallium nitride devices [20]–[23]

Table I Die Information Used In the Comparison

| Part#           | Company   | Voltage<br>Rating | Current<br>Rating |

|-----------------|-----------|-------------------|-------------------|

| S4003           | Rohm      | 650 V             | 118 A             |

| S4103           | Rohm      | 1200 V            | 95 A              |

| CPM3-0900-0010A | Wolfspeed | 900 V             | 196 A             |

| CPM2-1200-0025B | Wolfspeed | 1200 V            | 98 A              |

$$P_{loss\_norm}(A_{die}) = \frac{P_{cond}(A_{die}) + P_{gate}(A_{die}) + P_{switching}(A_{die})}{P_{converter}}$$

(1)

$$P_{cond}(A_{die}) = \sum_{i} I_{rms_{i}}^{2} \frac{\alpha_{i}(\xi_{i} V_{B_{i}})}{k_{i} A_{die}} \quad \left(\alpha_{i}(\xi_{i}, V_{B_{i}}) = R_{ds(on)} A_{die}(V_{B_{i}})\right) \quad (2)$$

$$P_{gate}(A_{die}) = \sum_{i} V_{gs_i} f_{s_i} \beta_i k_i A_{die} \qquad (\beta_i = \frac{q_{g_i}}{A_{die}}) \qquad (3)$$

$$P_{switching}(A_{die}) = \sum_{i} [E_{on_i}(A_{die}) + E_{off_i}(A_{die})] f_{s_i}$$

(4)

$$P_{switching\_zcs}(A_{die}) = \sum_{i} V_{ds_i}^2 f_{s_i} \gamma_i k_i A_{die} \qquad (\gamma = \frac{c_{oss_i}}{A_{die}}) \qquad (5)$$

According to Fig. 4, with the same semiconductor technology, the value of R<sub>ds(on)</sub>\*A<sub>die</sub> is a fixed number when the breakdown voltage V<sub>B</sub> is fixed. This means for a certain semiconductor technology, the  $\alpha_i(\xi_i, V_{B_i})$  is a fixed value when  $V_{B_i}$  is determined. The  $\xi_i$  in (2) represents the coefficient of the semiconductor technology of the  $i^{th}$  device. In addition, we also assume the parameters  $\beta_i$  and  $\gamma_i$  shown in (3) and (5) are constant values. This means when we increase the total die area  $A_{die}$  by N times, the  $Q_g$  and  $C_{oss}$  will also be N times larger and the  $R_{ds(on)}$  will reduce by N times, which is the same as connecting N dies in parallel. The parameter  $k_i$  means the ratio of the  $i^{th}$  die's area over the total die area  $A_{die}$  since there are multiple switches been used in a converter, and  $\sum_i k_i = 1$ . By tuning the parameter  $k_i$ , the switch conduction loss of a converter can be optimized. It's worth mentioning that the semiconductor loss index values are the same for 3-level FCML converter and STC.

For converter with 300V input and 600V output, 1200V dies from both Rohm and Wolfspeed are used in the boost converter evaluation. And we assume the die area of the upper switch and the lower switch in the boost converter are the same, which means  $k_i$ =0.5. On the other hand, 900V die from Wolfspeed and 650V die from Rohm are used in the STC and 3-level FCML converter. Table I shows the SiC die information used for the evaluation. Fig. 5 shows that the power loss of switching devices in STC and 3-level FCML converter is less than 50% the total semiconductor loss of the boost converter under full load. This is because the switching loss is a major

Fig. 5 Topology comparison (300V input and 600V output, 100kW)

contributor to the total semiconductor power loss in boost converter. Note that although the 3-level FCML converter and STC have the same semiconductor loss index, the mechanical layout of 3-level FCML converter is more challenging since its inductor, input and output capacitors are on the dc side.

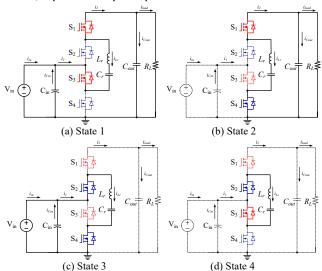

Fig. 6 Four switching states of the presented converter

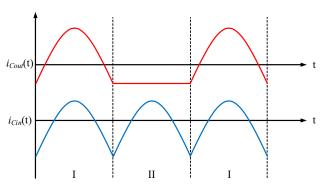

Fig. 7 Current waveforms of ZCS operation

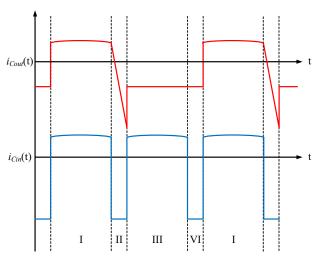

Fig. 8 Current waveforms of ZVS operation

### B. Design of Passive Components in 1-Phase Converter

Since the topology evaluation shows that the STC is a better choice than the other two converters, the next step is to figure out the potential improvement that can be done to reduce the passive component size of the one-cell STC, especially the input and output capacitors. Therefore, the current flowing through input and output capacitors should be analyzed. In order to analyze the current waveforms of passive components in the circuit, some assumptions have been made to simplify the analysis procedure. First, the voltage ripple across the input capacitor, output capacitor and resonant capacitor is small enough. Second, all the switching devices are ideal. It is worth mentioning that the mechanisms to achieve ZCS and ZVS operation of the presented converter will not be included in this paper since they have been analyzed in previous works [14]— [18]. This paper only focuses on obtaining the current waveforms of different passive component under different operation modes. In Fig. 6, state 1 and 3 shows the operation states of ZCS mode, while state 1 to 4 shows 4 operation states of ZVS mode. The waveforms of current flow through the passive components in both modes can be found in Fig. 7 and Fig. 8, respectively.

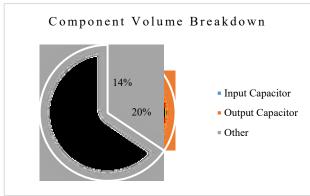

In order to study the actual size reduction that can be achieved by using interleaved topology. A 1-phase 100kW converter is developed at first. Table II shows the specifications of the designed 1-phase converter. The operating frequency of the designed converter is 100kHz. Table III shows the input and output capacitors that are used in the prototype. The capacitance of each input and output capacitor are 12uF and 5uF, respectively. According to Table IV, when we assume the voltage ripple of both input and output of the converter is less than 5%, then the minimum capacitance values of the input and output capacitor banks are 30uF and 40uF. On the other hand, the root mean square (RMS) values of the current flowing through input and output capacitors are 165A and 205.5A. As a result, in order to make sure the capacitor banks have enough current capability, the actual designed capacitance values of the input and output capacitors in the circuit are 120uF and 70uF, respectively. This means the capacitance in the circuit is overdesigned. Therefore, the size of input and output capacitors are

Table II Parameters of the Analyzed 1-Phase 100kW Converter

|                      | Symbols          | Values  |

|----------------------|------------------|---------|

| Power Rating         | P <sub>out</sub> | 100 kW  |

| Input Voltage        | $V_{in}$         | 300 V   |

| Output Voltage       | $V_{out}$        | 600 V   |

| Resonant Capacitance | $C_{\rm r}$      | 7.2 uF  |

| Resonant Inductance  | $L_{\rm r}$      | 350 nH  |

| Switching Frequency  | $f_s$            | 100 kHz |

| Input Capacitor      | $C_{in}$         | 120 uF  |

| Output Capacitor     | Cout             | 70 uF   |

Table III Capacitors Used In The 1-Phase Prototype

|                  | Part#       | Capacitance |

|------------------|-------------|-------------|

| Input Capacitor  | B32674D3126 | 12uF        |

| Output Capacitor | B32674D6505 | 5uF         |

Table IV Capacitance and Current Capability Requirements of Input and Output Capacitors (Assume Voltage Ripple <5%)

|                  | Current Capability<br>Requirement | Capacitance<br>Requirement |

|------------------|-----------------------------------|----------------------------|

| Input Capacitor  | 165 A                             | 30 uF                      |

| Output Capacitor | 205.5 A                           | 40 uF                      |

Fig. 9 Capacitors take 34% of the total component volume

not optimized. A component volume breakdown shows that the input capacitor and output capacitor take more than 30% of the total component size, as shown in Fig. 9.

#### III. INTERLEAVED TOPOLOGY AND COMPARISON

Interleaved concept provides a good solution to make use of the passive components in a more rational manner. In order to have a reasonable comparison between 1-phase converter, 2-phase interleaved converter and 3-phase interleaved converter, the values of resonant inductance and resonant capacitance frequency are always kept the same. This means switching frequency is always the same in the following analysis.

# A. Current Stress of Passive Components

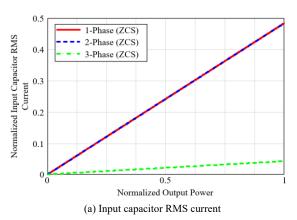

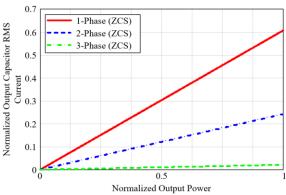

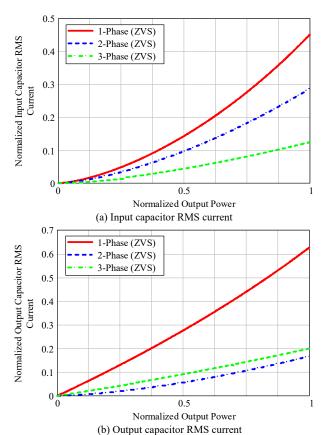

In the interleaved operation, the control signals of the converter in different phases shift 180-degree and 120-degree from each other in 2-phase interleaved connection and 3-phase interleaved connection, respectively. Fig. 10 shows the 3-Phase interleaved circuit connection of the presented circuit. Fig. 11 shows the normalized capacitor RMS current when the converter operates at ZCS mode. Similarly, Fig. 12 shows the

Fig. 10 3-Phase interleaved connection of the presented converter

(b) Output capacitor RMS current Fig. 11 Normalized current stress of capacitors (ZCS operation)

Fig. 12 Normalized current stress of capacitors (ZVS operation)

normalized current stress of the input and output capacitors when the converter operates at ZVS operation mode. According to these two figures, we can tell that the RMS values of the currents flowing through input capacitor bank and output capacitor bank are significantly reduced with the interleaved operation. Especially when the converter operates at ZCS mode, the current stress of the input and output capacitors can be reduced by more than ten times. This means the size of the input capacitor and the output capacitor can be significantly reduced with interleaved operation.

## B. Estimated Component Size and Inductor Size Reduction

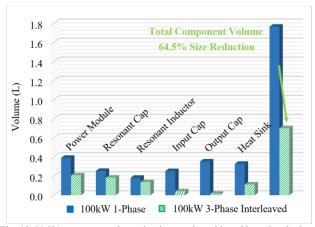

The inductance of the resonant inductor can be calculated using (6). And the relationship between the saturation current and the saturation flux density can be found in (8). Based on (8), the saturation current of a inductor can be represented by the mean length of the magnetic path  $l_m$ , length of the air gap  $l_g$ , inductor turn number N, permeability  $\mu_0$ , relative permeability  $\mu$  and the saturation flux density, as shown in (8). Thus, (9) has been derived from (6) and (8). According to (9), resonant inductance value and saturation current value of an inductor are proportional to the core's cross-section area and magnetic path length. In our case, the peak current of the inductors will become 1/N times in an interleaved N-phase converter, this means that the size of magnetic component size can also be significantly reduced in interleaved structure (e.g. ~9 times in a 3-phase converter). It's worth mentioning that a similar inductor volume reduction analysis is also proposed in [19]. At last, an estimated component size reduction of 64.5% can be achieved by using 3-phase interleaved operation, as shown in Fig. 13.

$$L = \frac{N^2 A_c}{\frac{l_g}{\mu_0} + \frac{l_m}{\mu * \mu_0}} \tag{6}$$

$$H = N * I_{sat} = (\frac{l_g}{\mu_0} + \frac{l_m}{\mu * \mu_0}) B_{sat}$$

(7)

$$I_{sat} = \frac{(\frac{l_g}{\mu_0} + \frac{l_m}{\mu * \mu_0})B_{sat}}{N}$$

(8)

$$LI_{sat}^{2} = B_{sat}^{2} A_{c} \left( \frac{l_{g}}{\mu_{0}} + \frac{l_{m}}{\mu * \mu_{0}} \right)$$

(9)

Fig. 13 64.5% component size reduction can be achieved by using 3-phase interleaved topology

### IV. SIMULATION RESULTS AND PROTOTYPE

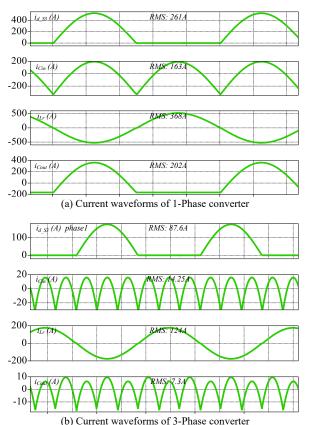

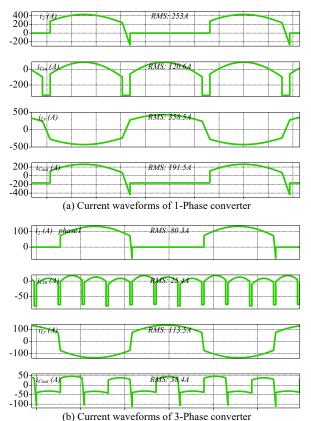

Simulation has been performed to validate the theoretical analysis on the current stress of passive components in the circuit. In ZCS mode, the 3-phase interleaved operation allows the current stress of input capacitor drop from 163A to 14.25A, which is 11.5 times lower. And the current stress of output capacitor is reduced by 28 times, from 202A to 7.3A, as shown in Fig. 14. On the other hand, according to Fig. 15, the current stress of input capacitor is 4.7 times lower in the 3-phase interleaved converter when it operates at ZVS mode, which is 25.4A. In comparison, the current stress of input capacitor in 1phase converter is 120.6A. In addition, the current stress values of output capacitors in 1-phase converter and 3-phase interleaved converter are 191.5A and 38.4A, respectively. We can tell that the current stress of output capacitors is reduced by five times with the interleaved operation. The simulated current stress values of input and output capacitors match the theoretical analysis. And according to the simulation, one can tell that the interleaved operation can better mitigate the high current stress issue on input and output capacitors when ZCS operation mode is enabled, which also suggest that the ZCS operation is more suitable for interleaved operation. A 1-phase 100kW converter prototype based on Rohm SiC power module BSM600D12P3G001 is designed to verify the theoretical analysis of the capacitor current, as shown in Fig. 16. The 1phase converter achieves 45kW/L density. Furthermore, a 3phase high power density converter based on Infineon CoolSiC FF11MR12W1M1 B11 is proposed. Both single side cooling

Fig. 14 Simulation for 100kW with 300V input/600V output (ZCS operation)

and double side cooling method are considered. With the double side cooling layout, the 3-phase converter achieves 115kW/L power density. Compared with the 1-phase converter, the converter volume reduction is 60%. The magnetic material used to build the inductor is Hitachi ML29D, which is very suitable for the applications range from 50kHz~250kHz.

Fig. 15 Simulation for 100kW with 300V input/600V output (ZVS operation)

Fig. 16 100kW 1-phase converter and 3-phase converter under developing

# V. CONCLUSION AND FUTURE WORK

This paper proposed a new topology evaluation method to evaluate different converter topologies. The study shows that the presented one-cell switched tank converter has the advantage of lower semiconductor index value and lower mechanical layout difficulty over the conventional boost converter and the 3-level FCML converter. Furthermore, this work evaluates the potential of utilizing interleaving concept to optimize the volume of passive components, thus to achieve size reduction of the 100kW one-cell STC that can be used in electric vehicles. With the interleaved operation, the capacitor over-design issue led by high current stress can be alleviated. The volume of the input capacitor, output capacitor can be reduced by 6 times and 17 times, respectively. An estimated 60% size reduction based on 1-phase converter and a density of 115kW/L can be achieved on a 3-phase one-cell STC with interleaved operation.

#### ACKNOWLEDGMENT

The authors would like to thank Hitachi and Rohm for their engineering samples and support. This work is supported under NSF Award Number 1810428.

#### REFERENCES

- [1] X. Lyu, N. Ren, Y. Li, and D. Cao, "A SiC-Based High Power Density Single-Phase Inverter With Inseries and In-Parallel Power Decoupling Method," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 4, no. 3, pp. 893–901, Sep. 2016.

- [2] Z. Ni, X. Lyu, O. P. Yadav, and D. Cao, "Review of SiC MOSFET based three-phase inverter lifetime prediction," in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), 2017, pp. 1007–1014.

- [3] K. Olejniczak *et al.*, "A compact 110 kVA, 140°C ambient, 105°C liquid cooled, all-SiC inverter for electric vehicle traction drives," in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), 2017, pp. 735–742.

- [4] J. B. Casady *et al.*, "First automotive reliability assessment and drive-train performance of large-area 900V, 10mOhm SiC MOSFETs," *Conf. Proc. IEEE Appl. Power Electron. Conf. Expo. APEC*, pp. 2259–2262, 2017.

- [5] H. Kim, H. Chen, J. Zhu, D. Maksimovic, and R. Erickson, "Impact of 1.2kV SiC-MOSFET EV traction inverter on urban driving," WiPDA 2016 4th IEEE Work. Wide Bandgap Power Devices Appl., pp. 78–83, 2016.

- [6] G. Calderon-Lopez and A. J. Forsyth, "High Power Density DC-DC Converter with SiC MOSFETs for Electric Vehicles," 7th IET Int. Conf. Power Electron. Mach. Drives (PEMD 2014), p. 1.4.01-1.4.01, 2014.

- [7] A. Merkert, J. Muller, and A. Mertens, "Component design and implementation of a 60 kW full SiC traction inverter with boost converter," in ECCE 2016 IEEE Energy Conversion Congress and Exposition, Proceedings, 2016, pp. 1–8.

- [8] X. Jia, D. Xu, S. Du, C. Hu, M. Chen, and P. Lin, "A High Power Density and Efficiency Bi-Directional DC

- / DC Converter for Electric Vehicles," *Proc. Int. Conf. Power Electron. ECCE Asia, Seoul*, pp. 874–880, 2015.

- [9] H. Chen, H. Kim, R. Erickson, and D. Maksimovic, "Electrified Automotive Powertrain Architecture Using Composite DC-DC Converters," *IEEE Trans. Power Electron.*, vol. 32, no. 1, pp. 98–116, 2017.

- [10] H. Kim *et al.*, "SiC-MOSFET composite boost converter with 22 kW/L power density for electric vehicle application," in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), 2017, pp. 134–141.

- [11] Serkan Öztürk, "Design of three phase interleaved DC/DC boost converter with all SiC semiconductors for electric vehicle applications," 2017 10th Int. Conf. Electr. Electron. Eng., 2017.

- [12] J. Scoltock, G. Calderon-Lopez, and A. J. Forsyth, "Topology and magnetics optimisation for a 100-kW Bi-directional DC-DC Converter," in 2017 IEEE Vehicle Power and Propulsion Conference, VPPC 2017 - Proceedings, 2018, vol. 2018–Janua, pp. 1–6.

- [13] J. Zhu, H. Kim, H. Chen, R. Erickson, and D. Maksimovic, "High efficiency SiC traction inverter for electric vehicle applications," in 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), 2018, vol. i, pp. 1428–1433.

- [14] K. Sano and H. Fujita, "Performance of a highefficiency switched-capacitor-based resonant converter with phase-shift control," *IEEE Trans. Power Electron.*, vol. 26, no. 2, pp. 344–354, 2011.

- [15] Y. Li, X. Lyu, D. Cao, S. Jiang, and C. Nan, "A high efficiency resonant switched-Capacitor converter for data center," in 2017 IEEE Energy Conversion Congress and Exposition, ECCE 2017, 2017, vol. 2017–Janua, pp. 4460–4466.

- [16] Y. Li, B. Curuvija, X. Lyu, and D. Cao, "Multilevel modular switched-capacitor resonant converter with voltage regulation," in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), 2017, pp. 88–93.

- [17] D. Cao, X. Lu, X. Yu, and F. Z. Peng, "Zero voltage switching double-wing multilevel modular switched-capacitor DC-DC converter with voltage regulation," *Conf. Proc. IEEE Appl. Power Electron. Conf. Expo. APEC*, no. Mmccc, pp. 2029–2036, 2013.

- [18] Y. Li, X. Lyu, D. Cao, S. Jiang, and C. Nan, "A 98.55% Efficiency Switched-Tank Converter for Data Center Application," *IEEE Trans. Ind. Appl.*, vol. 54, no. 6, pp. 6205–6222, Nov. 2018.

- [19] Y. Lei, W. Liu, and R. C. N. Pilawa-Podgurski, "An Analytical Method to Evaluate and Design Hybrid Switched-Capacitor and Multilevel Converters," *IEEE Trans. Power Electron.*, vol. 33, no. 3, pp. 2227–2240, Mar. 2018.

- [20] B. J. Baliga, "Power semiconductor device figure of merit for high-frequency applications," *IEEE Electron Device Lett.*, vol. 10, no. 10, pp. 455–457, Oct. 1989.

- [21] A. Lidow and J. Strydom, "Gallium Nitride (GaN) Technology Overview," 2012.

- [22] H. Matsunami, "State-of-the-art wide band-gap semiconductors for power electronic devices," in *International Meeting for Future of Electron Devices*, 2004., 2009, pp. 21–22.

- [23] B. J. Baliga, "Semiconductors for high-voltage, vertical channel field-effect transistors," *J. Appl. Phys.*, vol. 53, no. 3, pp. 1759–1764, 1982.