# Passivation of Thin Channel Zinc Tin Oxide TFTs Using $\text{Al}_2\text{O}_3$ Deposited by $\text{O}_3$ -Based Atomic Layer Deposition

Christopher R. Allemang<sup>✉</sup>, *Member, IEEE*, and Rebecca L. Peterson<sup>✉</sup>, *Senior Member, IEEE*

**Abstract**—Here, we fabricate solution processed zinc tin oxide bottom gate top contact thin film transistors (TFTs) with active layer thickness down to 6 nm by varying the solution molarity and number of layers. As-fabricated devices show hysteresis as large as 12.65 V. The hysteresis is then studied under vacuum to understand the important role of the back channel in electrical performance. After vacuum treatment, the hysteresis measured under vacuum was reduced to  $-0.05$  V. Alumina deposited on the back channel using atomic layer deposition (ALD) is used for passivation. The TFTs passivated with an  $\text{H}_2\text{O}$ -based ALD process show conductive behavior after passivation while an  $\text{O}_3$ -based ALD process results in a negative threshold voltage shift dependent on the thickness of the active layer.  $\text{O}_3$ -based passivated devices show good stability with a field effect mobility of  $8.3 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$ ,  $V_t$  of 5.5 V, and hysteresis of 0.85 V.

**Index Terms**—Amorphous semiconductors, thin-film transistors, stability, current-voltage characteristics.

## I. INTRODUCTION

METAL oxide semiconductors are gaining traction for thin film transistor (TFT) applications because of their transparency, variety of deposition techniques, and superior charge transport compared to amorphous-Si [1] and organics. In particular, amorphous oxide semiconductors (AOS) are interesting because of their large-area uniformity [2], [3]. Solution processed deposition does not require vacuum equipment, allowing the spatial uniformity of AOS to be inexpensively harnessed for large-area applications [4].

High device stability is a requirement for many AOS applications. Stability of devices can vary with humidity [5], active layer thickness [6], and the conductivity of the back channel of the TFT [7]. Various passivation layers have been applied to try to stabilize AOS TFTs [8], [9]. In ZnO TFTs, a thin semiconductor layer is required to achieve enhancement mode behavior after passivation using ALD  $\text{Al}_2\text{O}_3$  [10].

Manuscript received April 12, 2019; revised April 22, 2019; accepted April 28, 2019. Date of publication May 1, 2019; date of current version June 26, 2019. This work was supported in part by the SPAWAR through DARPA Young Faculty Award under Grant N66001-14-1-4046 and in part by the NSF Award under Grant 1727918. The review of this letter was arranged by Editor Z. Ma. (*Corresponding author: Christopher R. Allemang*.)

The authors are with the Electrical Engineering and Computer Science Department, University of Michigan, Ann Arbor, MI 48109-2122 USA (e-mail: allemang@umich.edu).

Color versions of one or more of the figures in this letter are available online at <http://ieeexplore.ieee.org>.

Digital Object Identifier 10.1109/LED.2019.2914238

Many studies have looked at the stability of indium-based AOS deposited using other deposition techniques for TFT applications [9], [11]–[14]. Due to the high cost of indium [15], here we investigate the back-channel stability of solution-processed zinc tin oxide (ZTO), an indium free AOS, using TFTs with varying thicknesses. Other groups investigating solution processed ZTO have used chloride-based processes which release harmful byproducts during the process [6], [16] or provide no solution to device instability [17]. Our solution process uses acetate precursors that do not create harmful byproducts and can be processed over a wide range of conditions [18].

Here, we present sub 10 nm, down to 6 nm, thick ZTO TFTs deposited using an indium-free acetate-based solution process and passivated using an ozone-based atomic layer deposition (ALD) alumina passivation layer. Passivated devices show enhancement-mode behavior with good stability, field effect mobility,  $\mu_{FE}$ , of  $8.3 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$ , threshold voltage,  $V_t$ , of 5.5 V, and hysteresis of 0.85 V.

## II. EXPERIMENTAL

Bottom-gate, top contact ZTO TFTs were fabricated on silicon substrates with a 100 nm thermally grown  $\text{SiO}_2$  layer acting as the gate and gate insulator, respectively. The active ZTO layer was deposited using our previously-reported solution process, but with varied solution molarity and number of layers to vary film thickness [18]. The ZTO was patterned by wet etching for device isolation, then source and drain electrodes were deposited by sputtering 100 nm of molybdenum and patterned using lift-off. The source/drain contacts are expected to be ohmic because the overlap with the semiconductor layer is approximately  $65 \mu\text{m}$ , much greater than the  $<1 \mu\text{m}$  transfer length of Mo to ZTO [19]. Some devices were passivated with approximately 30 nm of alumina deposited using a conventional  $\text{H}_2\text{O}$  and trimethylaluminum (TMA) process at  $150^\circ\text{C}$  in an Oxford OpAL ALD system [12], [20], [21]. Other samples were passivated by approximately 30 nm of alumina deposited using an ozone and TMA process, applied previously to sputtered ZTO [22] and IGZO [23] films, at  $100^\circ\text{C}$  in a Veeco Savannah system. Film thickness was measured using a J. A. Woollam M-2000 Ellipsometer. Electrical measurements were taken in the dark at room temperature in air ambient using a HP4156A semiconductor parameter analyzer or a Keysight B1505A power device analyzer. A Lake Shore Cryotronics TPPX Probe Station was used to take measurements under vacuum.

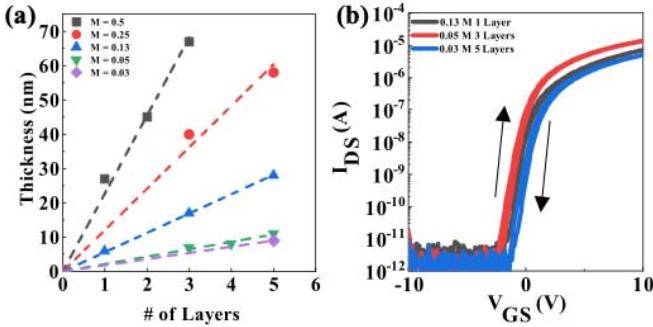

Fig. 1. (a) Film thickness as a function of number of layers for 0.5, 0.25, 0.13, 0.05, and 0.03 molar (M) solution with experimental data (symbols) and linear fits through the origin (dashed lines). (b) Transfer curves of ZTO TFTs with  $t_{channel} < 10$  nm, W/L of 10, and  $V_{DS} = 1$  V.

### III. RESULTS AND DISCUSSION

Fig. 1 (a) shows the relationship between the number of ZTO layers deposited during spin coating and the final active layer thickness. The relationship between thickness and number of spin-coated layers is approximately linear, indicating that the thickness of each coated layer making up the final film is approximately the same, for a given molarity, allowing the thickness of the active layer to be easily tuned. The thickness deposited per layer is dependent on the molarity of the film, where a higher molarity deposits a thicker layer. For the devices tested, electrical performance only depends on thickness of the film and not the molarity of the solution or number of spin-coating steps, as shown in Fig. 1 (b). Previous work with single-layer solution-processed ZTO has shown varying the spin coater speed can yield films as thin as 20 nm [16] and diluting the solution can yield a thickness down to 5 nm [6]. Here we vary both the molarity of the film and number of spin-coats to achieve sub-10 nm thickness. AFM measurements on a  $1 \mu\text{m}^2$  area (data not shown) indicate a uniform continuous film with RMS surface roughness  $< 1.2$  nm for even the thinnest film tested, much lower than 3.85 nm measured for 20 nm thick films in [16].

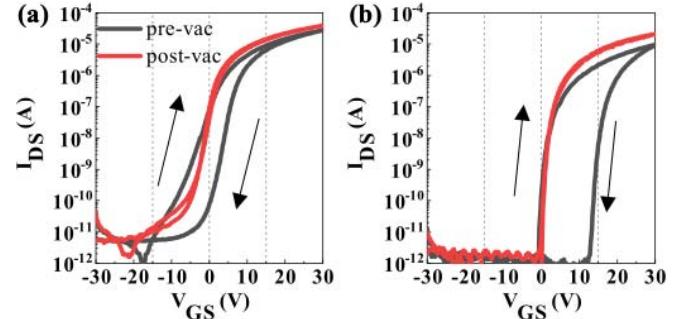

Samples with a thickness of  $\sim 70$  and 7 nm were measured both as-fabricated and under vacuum after a vacuum treatment. For vacuum treatment, the samples were kept under roughing vacuum for approximately 22 h. While under roughing vacuum, the samples were annealed at up to 400 K for approximately 1.75 h. Finally, while still under vacuum, the TFTs were measured again. As-fabricated devices show large hysteresis between forward and reverse sweeps of 5.28 V and 12.65 V for the 70 and 7 nm film, respectively, where hysteresis is measured at 100 nA  $I_{DS}$  and 1 V  $V_{DS}$  (Fig. 2). After vacuum treatment, the hysteresis is significantly reduced to  $-0.52$  V for the 70 nm film and  $-0.05$  V for the 7 nm film, leading to forward and reverse sweeps that are almost completely overlapping. The thicker film shows a kink in the subthreshold current, between  $-15$  and  $-5$  V  $V_{GS}$ , not seen in the thin device. We attribute this to water that remains adsorbed, causing traps in the channel [24].

The hysteresis seen in as-fabricated samples under ambient conditions is typical for AOS devices [25] and is attributed to desorption and adsorption of molecules, such as water and oxygen, on the back channel. Water can act as an electron donor [6] or an acceptor-like trap [26]. Whether water acts as an electron donor or acceptor-like trap can depend on

Fig. 2. Transfer curves of ZTO TFTs pre-vacuum and after vacuum treatment, with  $V_{DS} = 1$  V. The TFT in (a) has a film thickness of about 70 nm and W/L ratio of 10. The TFT in (b) has a film thickness of about 7 nm and W/L ratio of 12.5.

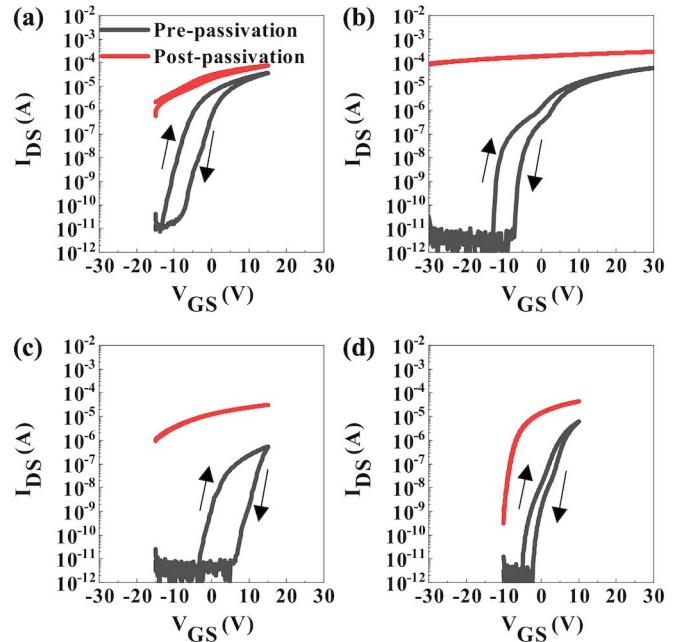

Fig. 3. Transfer curves for  $V_{DS} = 1$  V of ZTO TFTs pre-passivation and after  $\text{Al}_2\text{O}_3$  passivation using (a) and (c) a  $\text{H}_2\text{O}$  ALD process, or (b) and (d) an  $\text{O}_3$  ALD process. All devices have W/L of 10. (a) and (b) have a film thickness of  $\sim 70$  nm and (c) and (d) have a film thickness of  $\sim 28$  nm. Differences between the pre-passivation curves of devices with the same thickness are due to device-to-device variation or the temporal instability of unpassivated devices.

the thickness of the film [27] and parts per million of the water in the ambient environment (i.e., the relative humidity of air) [28]. Molecular oxygen will act as an electron trap when adsorbed to the back surface [6], [26]–[28]. When the devices are under vacuum, the molecules can freely desorb from the surface. This process is further assisted by annealing. In vacuum, there will be a limited number of molecules available for readsorption. With desorption occurring without readsorption, the hysteresis decreases. The superior characteristics of the thinner film under vacuum can be attributed to the ability of the gate to couple through the bulk of thinner films and control the back channel of the device [29]. As these were the thickest and thinnest films studied here, we believe films with intermediate thickness will act similarly. We next develop passivation methods to enable similar behavior without requiring impractical vacuum treatment or vacuum ambient.

In order to obtain devices that are stable and hysteresis-free in ambient, samples with film thicknesses of  $\sim 70$  and

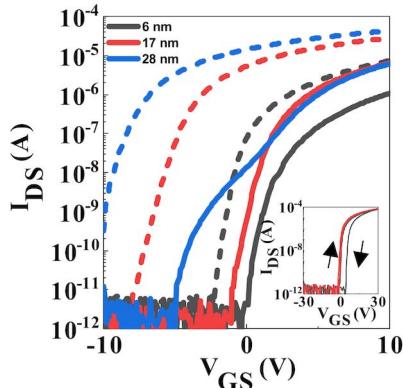

Fig. 4. Transfer curves with  $V_{DS} = 1$  V of ZTO TFTs with various thickness before passivation (solid line) and after passivation (dashed line) using an  $O_3$ -based  $Al_2O_3$  ALD process. Inset:  $I$ - $V$  curves from a 6 nm film before (black lines) and after (red lines) passivation.

28 nm were passivated using ALD-deposited  $Al_2O_3$ . Fig. 3 shows devices passivated using a  $H_2O$ -based process, resulting in conductive films for both the 70 and 28 nm thick device. One possible reason for the change in conduction is due to the removal of chemisorbed oxygen, or -OH groups, from the ZTO surface due to the highly reactive TMA [20]. Removal of chemisorbed oxygen increases the number of free carriers leading to a more conductive film. Additionally, the reaction of  $H_2O$  and TMA may generate and trap hydrogen, altering the conductivity of the film [21]. Using a  $O_3$ -based process, the 70 nm thick device is still conductive after passivation, but the 28 nm thick device resulted in a negative  $V_t$  shift of 9.9 V, a decrease in the hysteresis from 2.03 to 0.16 V, and a  $\mu_{FE}$  of  $8.6 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ . We believe the  $O_3$ -based process yields better results than the  $H_2O$ -based ALD process because ozone can reintroduce -OH groups to the ZTO surface that were stripped by the TMA precursor during ALD [22], [23].

To further investigate the relationship between thickness and  $V_t$ , devices with 6, 17, and 28 nm thick ZTO films were measured before passivation and after passivation using an  $O_3$ -based  $Al_2O_3$  ALD process. The as-fabricated devices show a more negative  $V_t$  with increasing film thickness (Fig. 4). Other researchers have attributed similar changes in  $V_t$  to a decrease in traps in thicker films [30] and therefore an increase in free carriers [16], [31]. The thickest film also shows a kink in the subthreshold current around 0 V  $V_{GS}$ . This can be explained by traps caused by water adsorption as discussed above. The subthreshold slope (SS) is similar for pre- and post-passivation devices with thickness of 6 and 17 nm. The 28 nm film shows a decrease in SS from 0.77 V/dec to 0.38 V/dec after passivation. The reduction in SS is likely due to a reduced trap density in the bulk of the film or at the back interface [13]. Post-passivation, the trend of threshold voltage and film thickness persists, and all devices show a negative  $V_t$  shift from their pre-passivation state. The shift in threshold voltage after passivation can be explained by the desorption of surface species as discussed above. Devices with 6 nm thick ZTO exhibit the best performance with  $\mu_{FE}$  of  $8.3 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ ,  $V_t$  of 5.5 V, and hysteresis of 0.85 V (Fig. 4 inset). The linear  $\mu_{FE}$  extracted here is typical for ZTO [6], [16], [18], [24].

To test stress stability of devices passivated using an  $O_3$ -based process, a constant current stress was applied for 5000 s,

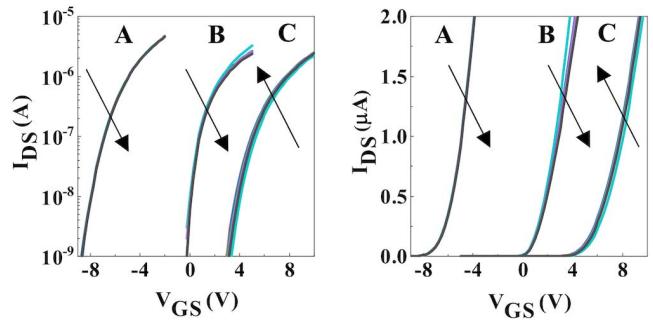

Fig. 5. Transfer curves with  $V_{DS} = 1$  V of ZTO TFTs during constant current stress testing. (A) and (B) are 7 and 28 nm thick, respectively, and are passivated using an  $O_3$ -based process. (C) is 7 nm and unpassivated. Arrows indicate the direction of  $V_t$  shift from 0 to 5000 s. All devices have  $W/L$  of 10.

an appropriate time to observe device instability [6], [11], [14], with the gate and drain shorted, the source grounded, and a constant  $I_{DS}$  of  $10 \mu\text{A}$  was performed in the dark at room temperature. Transfer curves, with the  $V_{GS}$  range set to approximately  $\pm 5$  V on either side of  $V_t$ , where  $V_t$  is defined as the value of  $V_{GS}$  required to produce  $10 \text{ nA } I_{DS}$ , were measured every 1000 s as shown in Fig. 5 for a 7 nm thick device with and without passivation, and a 28 nm device with passivation. The thin device without passivation yields a  $\Delta V_t$  of  $-0.18$  V after 5000 s stress and is reduced to  $0.08$  V after  $O_3$ -based passivation all while retaining enhancement mode behavior. These results indicate  $O_3$ -based passivation of thin ZTO TFTs enables enhancement mode devices with a significant reduction of  $V_t$  instability compared to unpassivated devices.

#### IV. CONCLUSION

Solution processed ZTO bottom-gate, top contact TFTs were fabricated with ZTO thickness as thin as 6 nm. After fabrication, devices show hysteresis as large as 12.65 V at  $100 \text{ nA } I_{DS}$  and  $1 \text{ V } V_{DS}$ . After vacuum treatment, the hysteresis is reduced to  $-0.05$  V due to desorption of molecules at the back channel without readsorption. Passivation of the back channel using a  $H_2O$ -based ALD alumina process resulted in conductive ZTO film but an  $O_3$ -based ALD alumina process resulted in a  $\mu_{FE}$  of  $8.3 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ ,  $V_t$  of 5.5 V, and hysteresis of 0.85 V. The threshold voltage decreases with increasing film thickness and  $O_3$ -based passivation results in a negative  $V_t$  shift for all films.  $O_3$ -based passivation also resulted in improved stress stability. Further work combining vacuum treatment, passivation using aluminum precursors such as dimethylaluminum hydride [32] or dimethylaluminum isopropoxide [33], and thin active layers could lead to further improvement in enhancement mode devices.

#### ACKNOWLEDGMENT

Portions of this work were performed at the Lurie Nanofabrication Facility, which is supported by the College of Engineering at the University of Michigan. The authors thank Neil P. Dasgupta and Carli Huber at University of Michigan for deposition of the  $O_3$ -ALD  $Al_2O_3$  films. Any opinion, findings, conclusions or recommendations expressed in this publication are those of the authors and do not necessarily reflect the views of DARPA, SPAWAR, or NSF.

## REFERENCES

[1] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors," *Nature*, vol. 432, no. 7016, pp. 488–492, Nov. 2004. doi: [10.1038/nature03090](https://doi.org/10.1038/nature03090).

[2] H. Hosono, "Transparent amorphous oxide semiconductors: Materials design, electronic structure, and device applications," in *Proc. 75th Annu. Device Res. Conf. (DRC)*, Jun. 2017, pp. 1–2. doi: [10.1109/DRC.2017.7999387](https://doi.org/10.1109/DRC.2017.7999387).

[3] L. Petti, N. Münzenrieder, C. Vogt, H. Faber, L. Büthe, G. Cantarella, F. Bottacchi, T. D. Anthopoulos, and G. Tröster, "Metal oxide semiconductor thin-film transistors for flexible electronics," *Appl. Phys. Rev.*, vol. 3, no. 2, p. 021303, Jun. 2016. doi: [10.1063/1.4953034](https://doi.org/10.1063/1.4953034).

[4] E. Fortunato, P. Barquinha, and R. Martins, "Oxide semiconductor thin-film transistors: A review of recent advances," *Adv. Mater.*, vol. 24, no. 22, pp. 2945–2986, Jun. 2012. doi: [10.1002/adma.201103228](https://doi.org/10.1002/adma.201103228).

[5] K. Hoshino, B. Yeh, and J. F. Wager, "Impact of humidity on the electrical performance of amorphous oxide semiconductor thin-film transistors," *J. Soc. Inf. Display*, vol. 21, no. 7, pp. 310–316, 2013. doi: [10.1002/jisd.184](https://doi.org/10.1002/jisd.184).

[6] L.-C. Liu, J.-S. Chen, and J.-S. Jeng, "Ambient constancy of passivation-free ultra-thin zinc tin oxide thin film transistor," *ECS Solid State Lett.*, vol. 4, no. 12, pp. Q59–Q62, Jan. 2015. doi: [10.1149/2.0051512ssl](https://doi.org/10.1149/2.0051512ssl).

[7] W. J. Maeng, J. S. Park, H.-S. Kim, E. S. Kim, K. S. Son, T. S. Kim, M. Ryu, and S. Lee, "The effect of active-layer thickness and back-channel conductivity on the subthreshold transfer characteristics of Hf–In–Zn–O TFTs," *IEEE Electron Device Lett.*, vol. 32, no. 8, pp. 1077–1079, Aug. 2011. doi: [10.1109/LED.2011.2156756](https://doi.org/10.1109/LED.2011.2156756).

[8] E. S. Sundholm, R. E. Presley, K. Hoshino, C. C. Knutson, R. L. Hoffman, D. A. Mourey, D. A. Keszler, and J. F. Wager, "Passivation of amorphous oxide semiconductors utilizing a zinc–tin–silicon–oxide barrier layer," *IEEE Electron Device Lett.*, vol. 33, no. 6, pp. 836–838, Jun. 2012. doi: [10.1109/LED.2012.2191530](https://doi.org/10.1109/LED.2012.2191530).

[9] K. Nomura, T. Kamiya, and H. Hosono, "Stability and high-frequency operation of amorphous In–Ga–Zn–O thin-film transistors with various passivation layers," *Thin Solid Films*, vol. 520, no. 10, pp. 3778–3782, Mar. 2012. doi: [10.1016/j.tsf.2011.10.068](https://doi.org/10.1016/j.tsf.2011.10.068).

[10] D. A. Mourey, M. S. Burberry, D. A. Zhao, Y. V. Li, S. F. Nelson, L. Tutt, T. D. Pawlik, D. H. Levy, and T. N. Jackson, "Passivation of ZnO TFTs," *J. Soc. Inf. Display*, vol. 18, no. 10, pp. 753–761, Oct. 2010. doi: [10.1889/JSID18.10.753](https://doi.org/10.1889/JSID18.10.753).

[11] Y. Li, Y. L. Pei, R. Q. Hu, Z. M. Chen, Y. Zhao, Z. Shen, B. F. Fan, J. Liang, and G. Wang, "Effect of channel thickness on electrical performance of amorphous IGZO thin-film transistor with atomic layer deposited alumina oxide dielectric," *Current Appl. Phys.*, vol. 14, no. 7, pp. 941–945, 2014. doi: [10.1016/j.cap.2014.04.011](https://doi.org/10.1016/j.cap.2014.04.011).

[12] S. Yang, D.-H. Cho, M. K. Ryu, S.-H. K. Park, C.-S. Hwang, J. Jang, and J. K. Jeong, "High-performance Al–Sn–Zn–In–O thin-film transistors: Impact of passivation layer on device stability," *IEEE Electron Device Lett.*, vol. 31, no. 2, pp. 144–146, Feb. 2010. doi: [10.1109/LED.2009.2036944](https://doi.org/10.1109/LED.2009.2036944).

[13] Y. Wang, X. W. Sun, G. K. L. Goh, H. V. Demir, and H. Y. Yu, "Influence of channel layer thickness on the electrical performances of inkjet-printed In–Ga–Zn Oxide thin-film transistors," *IEEE Trans. Electron Devices*, vol. 58, no. 2, pp. 480–485, Feb. 2011. doi: [10.1109/TED.2010.2091131](https://doi.org/10.1109/TED.2010.2091131).

[14] S.-E. Liu, M.-J. Yu, C.-Y. Lin, G.-T. Ho, C.-C. Cheng, C.-M. Lai, C.-J. Lin, Y.-C. King, and Y.-H. Yeh, "Influence of passivation layers on characteristics of a-InGaZnO thin-film transistors," *IEEE Electron Device Lett.*, vol. 32, no. 2, pp. 161–163, Feb. 2011. doi: [10.1109/LED.2010.2091620](https://doi.org/10.1109/LED.2010.2091620).

[15] P. Schlupp, F.-L. Schein, H. von Wenckstern, and M. Grundmann, "All amorphous oxide bipolar heterojunction diodes from abundant metals," *Adv. Electron. Mater.*, vol. 1, nos. 1–2, Feb. 2015, Art. no. 1400023. doi: [10.1002/aelm.201400023](https://doi.org/10.1002/aelm.201400023).

[16] C. Kim, N.-H. Lee, Y.-K. Kwon, and B. Kang, "Effects of film thickness and Sn concentration on electrical properties of solution-processed zinc tin oxide thin film transistors," *Thin Solid Films*, vol. 544, pp. 129–133, Oct. 2013. doi: [10.1016/j.tsf.2013.04.051](https://doi.org/10.1016/j.tsf.2013.04.051).

[17] Y. Jeong, K. Song, D. Kim, C. Y. Koo, and J. Moon, "Bias stress stability of solution-processed zinc tin oxide thin-film transistors," *J. Electrochem. Soc.*, vol. 156, no. 11, pp. H808–H812, Nov. 2009. doi: [10.1149/1.3212847](https://doi.org/10.1149/1.3212847).

[18] Y. Son, A. Liao, and R. L. Peterson, "Effect of relative humidity and pre-annealing temperature on spin-coated zinc tin oxide films made via the metal–organic decomposition route," *J. Mater. Chem. C*, vol. 5, no. 32, pp. 8071–8081, 2017. doi: [10.1039/C7TC02343J](https://doi.org/10.1039/C7TC02343J).

[19] W. Hu and R. L. Peterson, "Molybdenum as a contact material in zinc tin oxide thin film transistors," *Appl. Phys. Lett.*, vol. 104, no. 19, May 2014, Art. no. 192105. doi: [10.1063/1.4875958](https://doi.org/10.1063/1.4875958).

[20] P. Görnn, T. Riedl, and W. Kowalsky, "Encapsulation of zinc tin oxide based thin film transistors," *J. Phys. Chem. C*, vol. 113, no. 25, pp. 11126–11130, Jun. 2009. doi: [10.1021/jp9018487](https://doi.org/10.1021/jp9018487).

[21] T. T. T. Nguyen, B. Aventurier, T. Terlier, J. P. Barnes, and F. Templier, "Impact of passivation conditions on characteristics of bottom-gate IGZO thin-film transistors," *J. Display Technol.*, vol. 11, no. 6, pp. 554–558, Jun. 2015. doi: [10.1109/JDT.2015.2396476](https://doi.org/10.1109/JDT.2015.2396476).

[22] B. S. Yang, S. Park, S. Oh, Y. J. Kim, J. K. Jeong, C. S. Hwang, and H. J. Kim, "Improvement of the photo-bias stability of the Zn–Sn–O field effect transistors by an ozone treatment," *J. Mater. Chem.*, vol. 22, no. 22, pp. 10994–10998, May 2012. doi: [10.1039/C2JM30242J](https://doi.org/10.1039/C2JM30242J).

[23] S. H. Rha, U. K. Kim, J. Jung, E. S. Hwang, S. J. Lee, W. Jeon, Y. W. Yoo, J.-H. Choi, and C. S. Hwang, "Variation in the threshold voltage of amorphous-In<sub>2</sub>Ga<sub>2</sub>ZnO<sub>7</sub> thin-film transistors by ultrathin Al<sub>2</sub>O<sub>3</sub> passivation layer," *J. Vac. Sci. Technol. B*, vol. 31, no. 6, Oct. 2013, Art. no. 061205. doi: [10.1116/1.4827276](https://doi.org/10.1116/1.4827276).

[24] M. R. Shijeesh, A. C. Saritha, and M. K. Jayaraj, "Investigations on the reasons for degradation of zinc tin oxide thin film transistor on exposure to air," *Mater. Sci. Semicond. Process.*, vol. 74, pp. 116–121, Feb. 2018. doi: [10.1016/j.mssp.2017.10.015](https://doi.org/10.1016/j.mssp.2017.10.015).

[25] X. Xu, L. Feng, S. He, Y. Jin, and X. Guo, "Solution-processed zinc oxide thin-film transistors with a low-temperature polymer passivation layer," *IEEE Electron Device Lett.*, vol. 33, no. 10, pp. 1420–1422, Oct. 2012. doi: [10.1109/LED.2012.2210853](https://doi.org/10.1109/LED.2012.2210853).

[26] M. Fakhri, H. Johann, P. Görnn, and T. Riedl, "Water as origin of hysteresis in zinc tin oxide thin-film transistors," *ACS Appl. Mater. Interfaces*, vol. 4, no. 9, pp. 4453–4456, Sep. 2012. doi: [10.1021/am301308y](https://doi.org/10.1021/am301308y).

[27] J.-S. Park, J. K. Jeong, H.-J. Chung, Y.-G. Mo, and H. D. Kim, "Electronic transport properties of amorphous indium–gallium–zinc oxide semiconductor upon exposure to water," *Appl. Phys. Lett.*, vol. 92, no. 7, Feb. 2008, Art. no. 072104. doi: [10.1063/1.2838380](https://doi.org/10.1063/1.2838380).

[28] D. Kim, S. Yoon, Y. Jeong, Y. Kim, B. Kim, and M. Hong, "Role of adsorbed H<sub>2</sub>O on transfer characteristics of solution-processed zinc tin oxide thin-film transistors," *Appl. Phys. Express*, vol. 5, no. 2, Jan. 2012, Art. no. 021101. doi: [10.1143/APEX.5.021101](https://doi.org/10.1143/APEX.5.021101).

[29] J. Jeong and Y. Hong, "Debye length and active layer thickness-dependent performance variations of amorphous oxide-based TFTs," *IEEE Trans. Electron Devices*, vol. 59, no. 3, pp. 710–714, Mar. 2012. doi: [10.1109/TED.2011.2180908](https://doi.org/10.1109/TED.2011.2180908).

[30] S. Y. Lee, D. H. Kim, E. Chong, Y. W. Jeon, and D. H. Kim, "Effect of channel thickness on density of states in amorphous InGaZnO thin film transistor," *Appl. Phys. Lett.*, vol. 98, no. 12, Mar. 2011, Art. no. 122105. doi: [10.1063/1.3570641](https://doi.org/10.1063/1.3570641).

[31] Z. Yang, J. Yang, T. Meng, M. Qu, and Q. Zhang, "Influence of channel layer thickness on the stability of amorphous indium zinc oxide thin film transistors," *Mater. Lett.*, vol. 166, pp. 46–50, Mar. 2016. doi: [10.1016/j.matlet.2015.12.029](https://doi.org/10.1016/j.matlet.2015.12.029).

[32] D. C. Corsino, J. P. S. Bermundo, M. N. Fujii, K. Takahashi, Y. Ishikawa, and Y. Uraoka, "Dimethylaluminum hydride for atomic layer deposition of Al<sub>2</sub>O<sub>3</sub> passivation for amorphous InGaZnO thin-film transistors," *Appl. Phys. Express*, vol. 11, no. 6, Jun. 2018, Art. no. 061103. doi: [10.7567/APEX.11.061103](https://doi.org/10.7567/APEX.11.061103).

[33] S. E. Potts, G. Dingemans, C. Lachaud, and W. M. M. Kessels, "Plasma-enhanced and thermal atomic layer deposition of Al<sub>2</sub>O<sub>3</sub> using dimethylaluminum isopropoxide, [Al(CH<sub>3</sub>)<sub>2</sub>(μ-O<sup>+</sup>Pr)]<sub>2</sub>, as an alternative aluminum precursor," *J. Vac. Sci. Technol. A*, vol. 30, no. 2, Feb. 2012, Art. no. 021505. doi: [10.1116/1.3683057](https://doi.org/10.1116/1.3683057).