# Current collapse in high-Al Channel AlGaN HFETs

Shahab Mollah, Mikhail Gaevski, Kamal Hussain, Abdullah Mamun , Richard Floyd, Xuhong Hu, MVS Chandrashekhar, Grigory Simin and Asif Khan

*Department of Electrical Engineering, University of South Carolina, Columbia, SC 29208*

We report the first study of current collapse in ultra-wide bandgap high-Al AlGaN channel heterostructure field-effect transistors (HFETs) using short-pulse biasing. Our results show that, under applied pulsed gate and drain voltages, the current collapse results from increased resistance of the source- gate and gate-drain regions but not from the channel under the gate. We also show that passivation of access regions of the high-Al channel HFET with SiNx results in significant reduction in current collapse.

Although significant progress has been made in the III-N based high-power/ high-frequency electronic devices, the gate- and drain- lag also referred to as current collapse is still a major challenge as it degrades the microwave output performance as well as increases the dynamic on-resistance of power switches.<sup>1, 2, 3, 4, 5, 6</sup>. The most common way of suppressing current collapse in AlGaN/GaN HFETs is surface passivation using  $\text{Si}_3\text{N}_4$ <sup>7,8,9,10,11</sup>. Recently, several groups including ours, have reported HFETs with high-Al AlGaN channels<sup>12,13,14,15,16,17,18,19,20</sup>. These devices are promising for high-voltage and high-power applications due to increased critical fields in high-Al AlGaN material. However, to the best of our knowledge, to date there are no reports of studies on current collapse phenomena in high-Al AlGaN channel HFETs. In this work we for the first time report on the current collapse effects in

high Al AlGaN channel HFETs, identify the device regions responsible for the collapse and show that efficient suppression of current collapse can be achieved using  $\text{Si}_3\text{N}_4$  passivation.

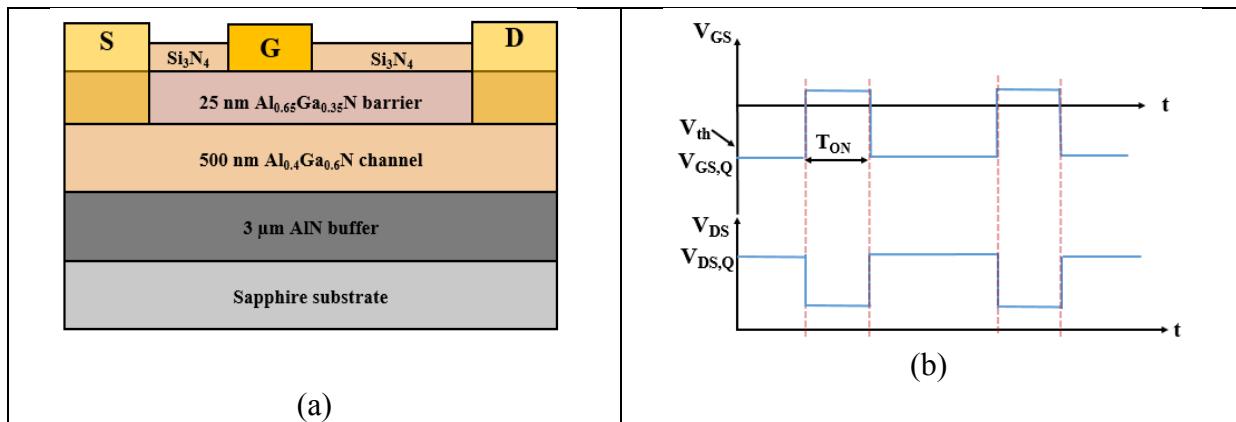

The device epilayer structure shown in Figure 1 was deposited on a 3  $\mu\text{m}$  thick AlN /sapphire template using a pulsed metalorganic- chemical-vapor deposition (MOCVD) process. Details of the growth procedure are reported in<sup>21</sup>. The off axis (102) X-ray peak line width for the AlN buffers was measured to be about 330 arcsecs, which based on our past calibrations, translates to an overall defect-density  $\sim (1-3) \times 10^8 \text{ cm}^{-2}$ . The thickness of undoped  $\text{Al}_{0.40}\text{Ga}_{0.60}\text{N}$  channel and the Si-doped  $n\text{-Al}_{0.65}\text{Ga}_{0.35}\text{N}$  barrier layers for our structures were 0.5  $\mu\text{m}$  and 300  $\text{\AA}$  respectively. The barrier layer carrier concentration due to Si-doping was approximately  $4-6 \times 10^{18} \text{ cm}^{-3}$ , as measured from the capacitance-voltage ( $1/C^2$  vs V) plot. The sheet resistance ( $R_{\text{sh}}$ ) value for our heterojunction was  $\sim 1900\Omega/\square$  as measured by the Eddy current method. The 2DEG electron sheet density in our sample was  $N_s = 1.9 \times 10^{13} \text{ cm}^{-2}$  according to C-V data. The total polarization charge at the interface calculated as per<sup>22</sup> is  $1.76 \times 10^{13} \text{ cm}^{-2}$ . The threshold-voltage  $V_T = -13.7 \text{ V}$  was determined by C-V measurements and it was in good agreement with that from device current-voltage (I-V) characteristics. Using the measured electron sheet density and the barrier thickness of 300A, we obtain the estimated voltage to deplete the 2DEG,  $V_{\text{2DEG}} = qN_s/C_1 \approx 11 \text{ V}$ , where  $C_1$  is the unit area barrier capacitance. The actual threshold voltage of 13.7 V is higher because the barrier layer in our structure is doped, and around 2 V is needed to deplete the barrier layer.

The device fabrication was started by mesa isolation step with  $\text{Cl}_2$ -based inductively coupled plasma reactive ion-etching (ICP-RIE) followed by source/drain ohmic metal deposition. The source-drain ohmic-contacts consisted of a  $\text{Zr}/\text{Al}/\text{Mo}/\text{Au}$  (150/1000/400/300  $\text{\AA}$ )<sup>12</sup> metal stack that was deposited using an e-beam process and it was annealed for 30 second at

950 °C under N<sub>2</sub> using rapid thermal annealing (RTA). We achieved linear source-drain ohmic-contacts with a contact resistance as low as 1.64 Ω-mm which gives an equivalent ohmic specific contact resistivity of  $\sim 1.4 \times 10^{-5}$  Ω-cm<sup>2</sup>. The gate-metal consisted of Ni/Au (1000 Å/2000 Å). Identical devices were passivated with a 300 nm thick Si<sub>3</sub>N<sub>4</sub> film deposited by plasma enhanced chemical vapor deposition (PECVD).

The static and pulsed output I-V characteristics (I<sub>DS</sub> vs V<sub>DS</sub>) were measured using the DIVA D265 dynamic IV analyzer. Positive gate and negative drain pulses with the quiescent points V<sub>GS,Q</sub> = -15 V (below the threshold voltage) and V<sub>DS,Q</sub> = 20 V correspondingly. Pulse widths for our study varied from 500 ns to 1 ms with duty cycle of 100.

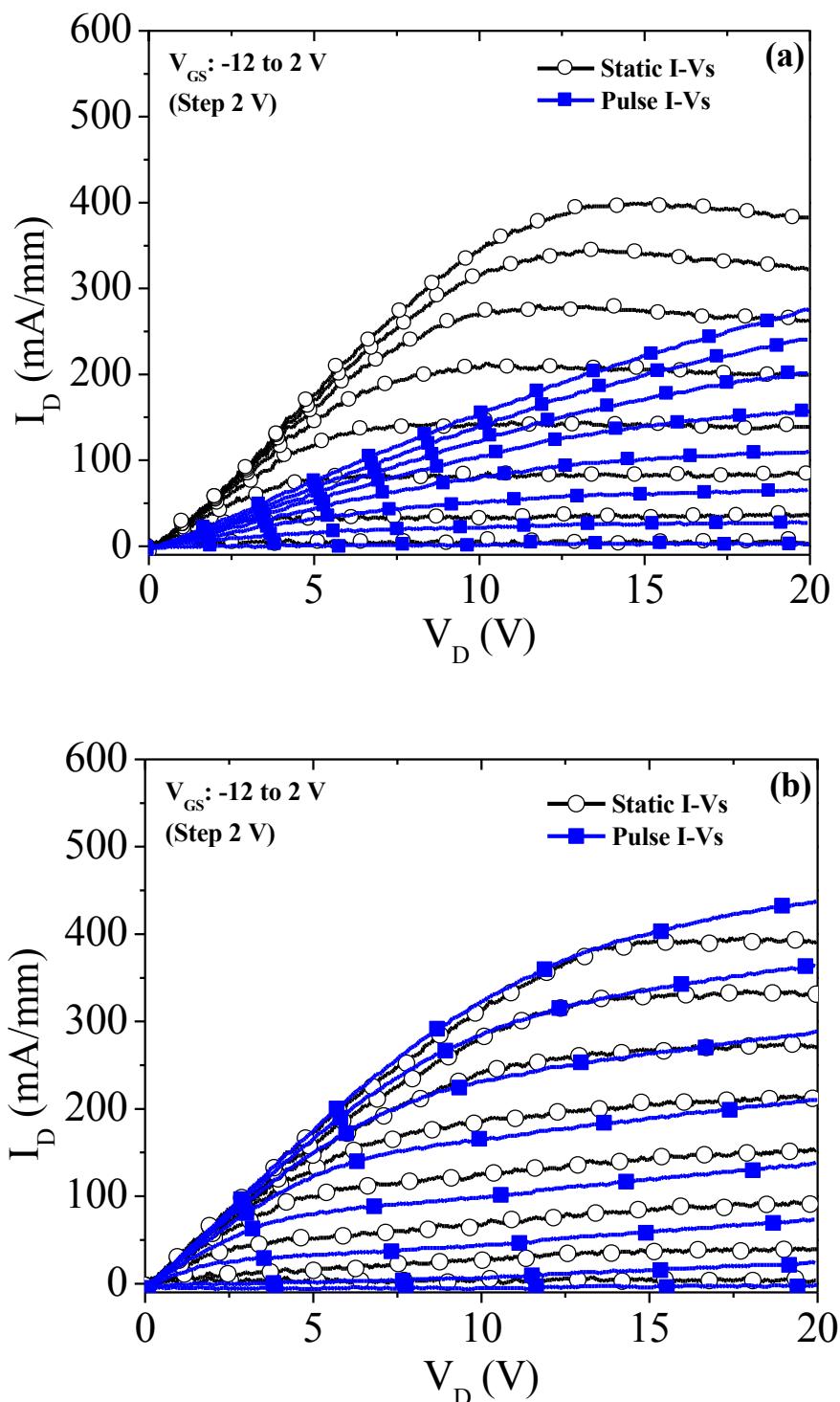

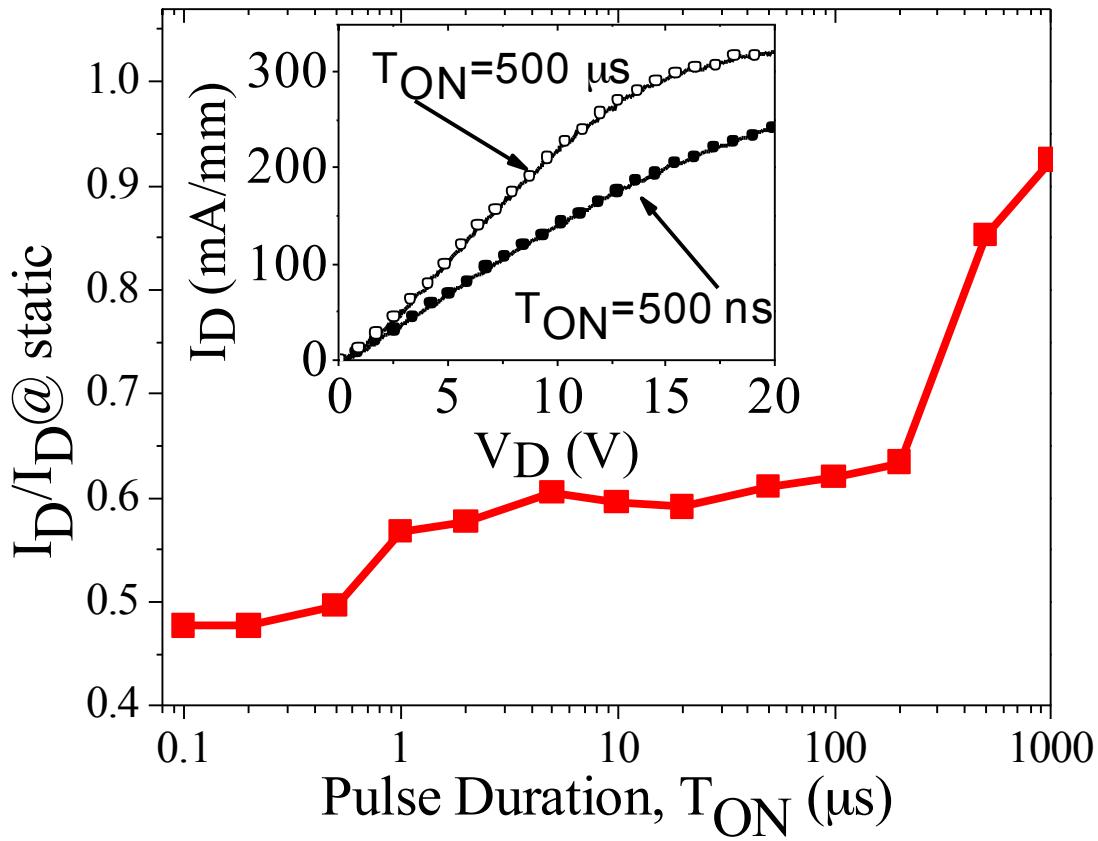

Fig 2 (a) shows the static and pulsed I-Vs of un-passivated Al<sub>0.65</sub>Ga<sub>0.35</sub>N/Al<sub>0.4</sub>Ga<sub>0.6</sub>N HFET, with a 1.8 μm long gate (L<sub>G</sub>), in a 6 μm source-drain spacing. Clear saturation is observed, with peak currents ~0.4 A/mm at V<sub>G</sub>=2V and V<sub>D</sub>=20V. Under gate and drain pulsing with above mentioned quiescent bias points, the device shows significant reduction in the drain current (current collapse). These observations are similar to those on unpassivated AlGaN/GaN HFETs<sup>3,4, 23,24,25,26,27</sup>. Fig. 2 (b) includes the same data for devices that were surface passivated using Si<sub>3</sub>N<sub>4</sub>. The data show that the Si<sub>3</sub>N<sub>4</sub> surface passivation layer effectively removes the current collapse in our high-Al AlGaN channel HFETs. Fig. 3 shows that, as pulse width increases from 100 ns to 1000 μs, the degree of collapse reduces due to sufficient time the device spends in the on- state for electron de-trapping. As seen from Fig. 3, the characteristic time for electron emission from traps range from approximately 1 μs to 1 ms. However, the most important contribution comes from traps with characteristic emission time of approximately 200 μs. The corresponding emission rate of  $5 \times 10^3$  s<sup>-1</sup> is considerably, by two-three orders of magnitude, lower than that observed in the work by O. Mitrofanov and M. Manfra<sup>28</sup> for

AlGaN/GaN HFETs. The difference is understandable considering larger bandgap of high-Al devices used in our study. Fig. 3 inset shows the drain current I-Vs for two different on-time pulse durations. At a pulse width of 1 ms, the degree of collapse is significantly lower and the dynamic drain current returns to ~90% of the static current value.

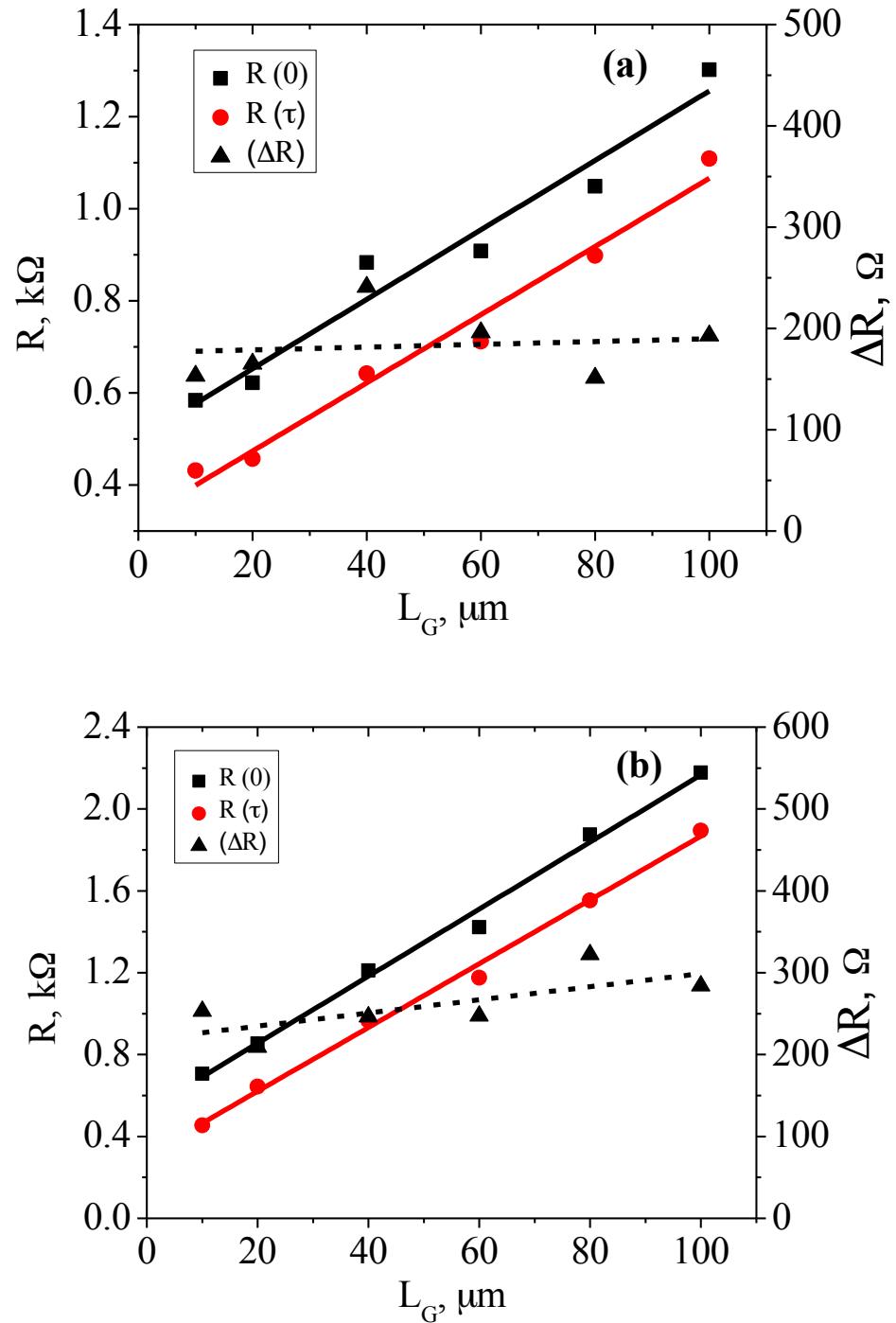

Next, we carried out additional experiments to establish which device regions are primarily responsible for the observed current collapse. For these, we used gated transmission line model (GTLM) measurements as described in.<sup>29</sup> The gate lengths in sequential sections of the GTLM varied from  $L_G=10\text{ }\mu\text{m}$  to  $L_G=100\text{ }\mu\text{m}$ , whereas the gate- source and the gate- drain openings were kept constant at  $L_{GS}=L_{GD}=10\text{ }\mu\text{m}$ . The width of all GTLM sections was  $W=200\text{ }\mu\text{m}$ . Two levels of drain bias have been used: below and above the knee voltage in order to study the device behavior in both linear and saturation regimes. The technique used is described below following the approach of<sup>29</sup>.

In linear regime, the total resistance of the GTLM section measured at any time during the transient process is given by:

$$R_T(t) = 2R_C + R_{GS} + R_{CH}(V_G) + R_{GD} \quad (1)$$

Where  $R_C$ ,  $R_{GS}$  and  $R_{GD}$  are the contact resistance and the resistances of the gate-source and the gate-drain openings, respectively and  $R_{CH}$  is the gate voltage dependent resistance of the channel under the gate. We assume that all components of the total resistance  $R_T$ , except  $R_C$ , can be time-dependent due to trapping effects. At low drain bias the components of the total resistance can be expressed as

$$R_{GS} = R_{GD} = R_{SA} \times L_{GS}/W \quad (2a)$$

$$R_{CH}(L_G) = R_{SG} \times L_G/W \quad (2b)$$

where  $R_{SA}$  and  $R_{SG}$  are the sheet resistances of the channel in the access regions and under the gate correspondingly. The total resistance of the GTLM section can therefore be rewritten as

$$R_T(t) = 2R_C + 2R_{SA} \times \frac{L_{GS}}{W} + R_{SG} \times \frac{L_G}{W} \quad (2c)$$

The total resistance of the GTLM sections  $R_T(0)$  and  $R_T(\tau)$  were measured in the beginning of the transient (instantaneous response) and at the end of the pulse (when the current is close to its steady state value), respectively. The corresponding dependencies of  $R_T(0)$  and  $R_T(\tau)$  are shown in Fig. 4 (a). The slope of the  $R_T(L_G)$  line represents the channel resistance under the gate, while the intercept  $R_T$  at  $L_G = 0$  provides the sum of the contact resistances  $2R_C$  and the gate-source and gate-drain access region resistances  $R_{GS} + R_{GD}$  in the beginning and at the end of the transient. Fig. 4 (a) also shows the change  $\Delta R = R_T(\tau) - R_T(0)$  of the total device resistance as a function of gate length  $L_G$ . Fig. 4(a) shows,  $R_T(\tau)$  and  $R_T(0)$  versus  $L_G$  to have near identical slopes but different intercepts. Therefore, the time dependence of the total resistance in the linear regime is caused by the dynamic modulation of the gate-source and gate-drain access region resistances, whereas the channel resistance under the gate remains unaffected.

Fig. 4 (b) shows the GTLM measurement results for a high drain bias case corresponding to the current saturation regime. Since the gate length in our GTLM exceeds 10  $\mu\text{m}$  one can see that the velocity saturation effects can be ignored (see, e.g. the estimates for AlGaN/GaN HFETs in <sup>29</sup>). The velocity saturation effects in high-Al AlGaN HFETs are even weaker due to lower electron mobility). In this case the saturation current of the HFET,  $I_{DS}$  is given by <sup>30</sup>

$$I_{DS} = \frac{g_{CH}(V_G - V_T)}{2(1 + g_{CH}R_S)}, \quad (3)$$

Where  $g_{CH} = \frac{1}{R_{CH}(L_G)}$ , is the channel conductance under the gate,  $R_{CH}(L_G)$  is given by Eq. 2(b),  $V_G$  is the gate voltage,  $V_T$  is the threshold voltage and  $R_S$  is the HFET source-gate series resistance (including the contact resistance). Using a term “trans-resistance”,  $R_{TR} = (V_G - V_T)/(2I_{DS})$ , the equation (3) can be rewritten as

$$R_{TR} = \frac{V_G - V_T}{2I_{DS}} = R_S + \frac{1}{g_{CH}} = R_S + R_{CH}(L_G) \quad (4)$$

Equation (4) describes similar gate length dependence of  $R_{TR}$  for the saturation regime as the equation 2(c) for the linear regime. The experimental dependence of  $R_{TR}(L_G)$  is plotted in Fig. 4(b). These results show that, in the saturation regime, the current transient process is also controlled by the variation of access region resistance rather than by the change of the resistance under the gate. Note that, the saturation current in HFETs is mainly affected by the source access resistance  $R_S$ , as seen from Eq. (3) and therefore, Fig. 4(b) shows the change of  $R_S$  during the transient. However, it is reasonable to expect that the drain resistance is also modulated and even to a larger degree because the voltage between drain and gate is higher than that between gate and source. The drain resistance modulation is evident from the dynamic I-Vs of Fig. 2a, where one can see significant knee voltage run away in spite of lower dynamic drain currents. This effect can be explained by additional voltage drop  $\Delta V_D$  across additional dynamic drain resistance  $\Delta R_D$ :  $\Delta V_D = I_{DS} \times \Delta R_D$ .

Our observations show that the manifestations of current collapse in high-Al AlGaN channel HFETs are qualitatively similar to those observed in AlGaN/GaN HFETs and other III-N devices (see, e.g.<sup>31</sup>); thus it can be mitigated by using similar passivation techniques and strategies. Therefore, we believe that the mechanism of current collapse in high-Al AlGaN channel HFETs includes one or both of: (i) carrier trapping in the access regions and (ii) strain modulation in the

access regions as first suggested in<sup>29</sup> and later also referred to as inverse piezoelectric effect.<sup>32</sup>

We are conducting more detailed studies to determine the exact dominant mechanism of current collapse in these new devices and the results will be published when available.

In conclusion, analysis of transient processes and dynamic I-Vs in high-Al AlGaN channel HFET showed that the access region resistances are mainly responsible for the current collapse. The channel resistance under the gate is practically not affected by electron trapping. The characteristic emission rates for trapped electrons is significantly lower than those observed in AlGaN/GaN HFETs due to larger bandgap of high-Al HFETs. The current collapse was successfully mitigated by using  $\text{Si}_3\text{N}_4$  surface passivation.

### **Acknowledgment:**

This research is partially supported by National Science Foundation (NSF), ECCS Award nos. 1711322 and 1810116 by program director Dr. Dimitris Pavlidis. The authors would like to acknowledge partial support of this work by DARPA DREAM contract (ONR N00014-18-1-2033), Program Manager Dr. Young-Kai Chen, monitored by ONR, Dr. Paul Maki and ARO contract W911NF-18-1-0029 monitored by Dr. M. Gerhold. The authors also acknowledge the support from the University of South Carolina through the ASPIRE program.

Fig. 1. (a) The Device structure of the HFET. (b) Time diagram of Gate and Drain pulses.

Fig. 2. Static and Pulse I-V characteristics of (a) HFET without passivation and (b)  $\text{Si}_3\text{N}_4$  passivated HFET. Pulse duration  $T_{\text{ON}} = 500$  ns, pulse period  $T = 500$   $\mu\text{s}$ .

Fig. 3. ON time ( $T_{\text{ON}}$ ) dependence of the non-passivated HFET drain current. The quiescent bias point is  $V_{GS,Q} = -15\text{V}$ ,  $V_{DS,Q} = 20\text{ V}$ . Inset shows pulse I-V characteristics of un-passivated HFET with different pulse width.

Fig. 4. Gate length dependencies of total resistance in the linear regime (a) and transfer resistance in the saturation regime (b). Rectangles and circles show the data measured in the beginning and at the end of the transient, respectively. Dashed lines with the triangles show the gate length dependencies of the change in device resistances  $\Delta R$ .

## References

<sup>1</sup> T. Hashizume, S. Ootomo and H. Hasegawa, *Applied Physics Lett.*, , 83, 2952 (2003)

<sup>2</sup> C. Nguyen, N.X. Nguyen and D. E. Grider, *Electron Lett.* 35, 1380 (1999)

<sup>3</sup> R. Vetary, N. Q. Zhang, S. Keller and U. K. Mishra, *IEEE Trans. Electron Devices*, 48, 560 (2001)

<sup>4</sup> S. C. Binari, P. B. Klein and T. E. Kazior, *Proc. IEEE*, 90, 1048 (2002).

<sup>5</sup> Tang Z., Jiang Q., Lu Y., Huang S., Yang S., Tang X. and Chen K. J., *IEEE Electron Device Lett.* 34, 1373 (2013).

<sup>6</sup> W. Saito, T. Nitta, Y. Kakiuchi, Y. Saito, K. Tsuda, I. Omura and M. Yamaguchi, *IEEE Trans. Electron Devices*, 54, 1825 (2007)

<sup>7</sup> B. M. Green, K. K Chu, E. M. Chumbers, J. A. Smart, J. R. Shealy, and L. F. Eastman, *IEEE Electron Device Lett.* 21, 268 (2003)

<sup>8</sup> L. F. Eastman, V. Tilak, J. Smart, B. M. Green, E. M. Chumbers, R. Dimitrov, H. Kim, O. S. Ambacher, N. Weimann, T. Prunty, M. Murphy, W. J. Schaff and J. R. Shealy, *IEEE Trans. Electron Devices*, 48, 479 (2001)

<sup>9</sup> X. Hu, A. Koudymov, G. Simin, J. Yang, M. Asif Khan, A. Tarakji, M. S. Shur and G. Gaska, *Applied Physics Lett.* 79, 2832 (2001)

<sup>10</sup> S. Arulkumaran and G. I. Ng, *Appl. Phys. Lett.* 90, 173504 (2007)

<sup>11</sup> S. Lin, M. Wang, B. Xie, C. P. Wen, M. Y. J. Wang, Y. Hao, W. Wu, S. Huang, K. J. Chen and B. Shen, *IEEE Electron Device Lett.*, 36, 757 (2015)

<sup>12</sup> Xuhong Hu , Seongmo Hwang, Kamal Hussain, Richard Floyd, Shahab Mollah, Fatima Asif, Grigory Simin, Asif Khan, *IEEE Electron Device Letters*, **39**, 10 (2018).

<sup>13</sup> S. Muhtadi, S. Hwang, A. Coleman, F. Asif, G. Simin, MVS Chandrashekhar and Asif Khan, IEEE Electron Device Lett, 38, 914 (2017)

<sup>14</sup> S. Muhtadi, S. Hwang, A. Coleman, F. Asif, A. Lunev, MVS Chandrashekhar and Asif Khan, Applied Physics Lett., 110, 193501 (2017)

<sup>15</sup> E. A. Douglas, B. Klein, A. A. Allerman, A. G. Baca, T. Fortune and A. M. Armstrong, J. Vac. Sci. Technol, B37 (2), 021208-1 (2019)

<sup>16</sup> B. A. Klein, E. A. Douglas, A. M. Armstrong, A. A. Allerman, V. M. Abate, T. R. Fortune and A. G. Baca, Appl. Phys. Lett., 114, 112104 (2019)

<sup>17</sup> A. G. Baca, B. A. Klein, J. R. Wendt, S. M. Lepkowski, C. D. Nordquist, A. M. Armstrong, A. Allerman, E. A. Douglas and R. J. Kaplar, IEEE Electron Device Lett., 40, 17 (2019)

<sup>18</sup> H. Tokuda, M. Hatano, N. Yafune, S. Hashimoto, K. Akita, Y. Yamamoto and M. Kuzuhara, Appl. Phys. Express 3, 121003 (2010).

<sup>19</sup> S. H. Sohel, A. Xie, E. Beam, H. Xue, J. A. Roussos, T. Razzak, S. Bajaj, Y. Cao, D. J. Meyer, W. Lu and S. Rajan, IEEE Electron Device Lett., 39, 1884 (2018)

<sup>20</sup> A. M. Armstrong, B. A. Klein, A. Colon, A. A. Allerman, E. A. Douglas, A. G. Baca, T. R. Fortune, V. M. Abate, S. Bajaj and S. Rajan, Jpn. J. Appl. Phys., 57, 074103 (2018)

<sup>21</sup> Qhalid Fareed, Vinod Adivarahan, Mikhail Gaevski, Thomas Katona, Jin Mei Fernando A. Ponce and Asif Khan, Metal–Organic Hydride Vapor Phase Epitaxy of Al<sub>x</sub>Ga<sub>1-x</sub>N Films over Sapphire, Japanese. J. App. Phys, **46**, 31, 110L754 (2007).

<sup>22</sup> O. Ambacher, J. Smart, J. R. Shealy, N. G. Weimann, K. Chu, M. Murphy, W. J. Schaff, and L. F. Eastman, J. Appl. Phys., 85, 6, 3222 (1999)

<sup>23</sup> Xi. Tang, Z. Zhang, J. Wei, B. Li, J. Wang, K. J. Chen, Appl. Phys. Express, 11, 071003 (2018)

<sup>24</sup> P. B. Klein, J. A. Freitas, S. C. Binari and A. E. Wickenden, *Appl. Phys. Lett.*, **75**, 4016, (1999)

<sup>25</sup> J. M. Tirado, J. L. S. Rojas and J. I. Izpura, *IEEE Trans. Electron Devices*, **54**, 410 (2007)

<sup>26</sup> J. I. Izpura, *Semicond. Sci. Technol.*, **17**, 1293 (2002).

<sup>27</sup> G. Meneghesso, G. Verzellesi, R. Pierobon, F. Rampazzo, A. Chini, U. K. Mishra, C. Canali, and E. Zanoni, *IEEE Trans. Electron Devices*, **51**, 1554 (2004).

<sup>28</sup> O. Mitrofanov and M. Manfra, *Journal of Appl. Phys.*, **95**, 6414 (2004)

<sup>29</sup> G. Simin, A. Koudymov, A. tarakji, X. Hu, J. Yang, M. Asif Khan, M. S. Shur and R. Gaska, *Appl. Phys. Lett.*, **79**, 2651 (2001)

<sup>30</sup> M. S. Shur, *Introduction to Electronic Devices* (Wiley, New York, 1996).

<sup>31</sup> J. Kuzmik, J.F. Carlin, M. Gonschorek, A. Kostopoulos, G. Konstantinidis, G. Pozzovivo, S. Golka, A. Georgakilas, N. Grandjean, G. Strasser, and D. Pogany, *phys. stat. sol. (a)* **204**, 6, 2019 (2007)

<sup>32</sup> J. Joh, F. Gao, T. Palacios and J. A. Del Alamo, *Microelectronics Reliability*, **50**, 767 (2010)