# Soft-FET: Phase transition material assisted Soft switching Field Effect Transistor for supply voltage droop mitigation

Subrahmanya Teja and Jaydeep P. Kulkarni

Department of Electrical and Computer Engineering, University of Texas at Austin, TX, USA

**Abstract**—Phase Transition Material (PTM) assisted novel soft switching transistor architecture named “Soft-FET” is proposed for supply voltage droop mitigation. By utilizing the abrupt phase transition mechanism in PTMs, the proposed Soft-FET achieves soft switching of the gate input of a logic gate resulting in reduced peak switching current as well as steep current variations ( $di/dt$ ). In addition, the Soft-FET incurs lower delay penalty across a wide voltage range compared to various baseline Complementary Metal Oxide Semiconductor (CMOS) logic gate variants for the same peak current. We perform a detailed PTM parameter optimization for optimum Soft-FET performance. Soft-FETs when used as power gates achieve  $\sim 20$ mV lower supply droop and when used as an I/O buffer achieves 46% lower ground bounce with 8.8% improved energy efficiency.

**Keywords**—Phase transition materials; Soft switching; Soft-FET; Voltage droop, power gate, I/O buffer

## I. INTRODUCTION

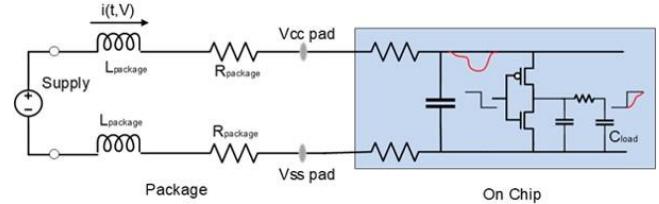

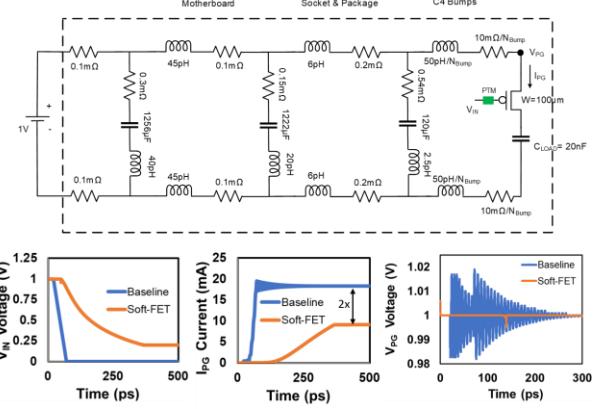

With the rapid advances in computing systems spanning from billions of IoTs (Internet of Things) to high performance exascale supercomputers, energy efficient design is an absolute must [1]. In a modern System-on-a-chip (SoC) design, supply voltage ( $V_{cc}$ ) scaling is the primary driver to reduce the energy consumption [2]. The IR drop and package inductance in a power delivery network (PDN) causes large voltage droops due to peak switching currents as well as sudden changes in current activity ( $di/dt$ ) as shown in Fig. 1 [3]. This voltage droop magnitude attributes to a significant portion of the supply voltage specifications. Furthermore, the deep proliferation of fine grain power domains and their complex power management strategies result in frequent Dynamic Voltage and Frequency Scaling (DVFS) [4]. This aggravates the voltage droop magnitude and translates into tighter specifications for the power delivery network, bulkier motherboard regulator components and ultimately degrading energy efficiency [5]. Therefore, there is a critical need to develop circuit topologies to reduce the peak switching current as well as sudden current fluctuations ( $di/dt$ ) to reduce the voltage droops and to realize compact and efficient power delivery network. To this effect, many circuit topologies have been proposed to reduce the peak switching current at the expense of larger delay and larger area [6-7].

In this paper, we propose a novel soft-switching transistor architecture abbreviated as “Soft-FET” utilizing abrupt phase change mechanism in transition metal oxides. To the best of author’s knowledge, this is the first ever application of phase transition materials in power delivery using Soft-FETs for supply voltage droop reduction. The key contributions of this paper are as follows:

1. We propose a novel integration of the PTM onto the gate of baseline CMOS for soft switching named as “Soft-FET”.

2. We analyze the DC and transient characteristics of the proposed Soft-FET based inverter and compare with multiple variants of the baseline CMOS inverter and quantify the effectiveness of the Soft-FET in reducing the peak current and/or  $di/dt$ .

DAC '18, June 24–29, 2018, San Francisco, CA, USA

© 2018 Association for Computing Machinery.

ACM ISBN 978-1-4503-5700-5/18/06..\$15.00

<https://doi.org/10.1145/3195970.3196117>

Fig. 1 Supply voltage droop in a power delivery network

3. We perform a detailed PTM device parameters variations and analyze their sensitivity to the Soft-FET peak current, and/or  $di/dt$  reduction.

4. We show the relationship between the PTM switching time and the input slew rate for optimum soft switching.

5. We present two case studies with Soft-FET power-gates and Soft-FET I/O buffer drivers and quantify the reduction in the peak switching current, supply and ground bounce.

The rest of the paper is organized as follows. In Section II, we describe the principle of operation of Phase Transition Material and the proposed Soft-FET. Section III compares the proposed Soft-FET based inverter with other CMOS variants. Section IV presents the PTM device optimization for best soft-switching benefits. Section V discusses the Soft-FET applications in power gates and I/O buffers. Section VI concludes the paper summarizing the proposed Soft-FET benefits and its effectiveness in power delivery networks.

## II. PHASE TRANSITION MATERIAL AND SOFT-FET

### A. Phase Transition Materials (PTM)

Transition metal oxides (such as Vanadium Dioxide ( $VO_2$ ) or Niobium Dioxide ( $NbO_2$ )) exhibit abrupt insulator-metal transition on the application of external electric field [8, 9]. This unique property is currently being utilized to realize transformational circuit topologies [10-14]. Table 1 illustrates the earlier proposed applications of PTM for logic and memory applications.

For logic applications, the PTM when placed in series with the source terminal of a MOSFET (called as Hyper-FET) reduces the sub-threshold current thereby improving the  $I_{ON}/I_{OFF}$  ratio [10, 11]. Another application of PTM is a metal-insulator tunnel junction with abrupt phase transition for potential applications in TFET (Tunnel Field Effect Transistors) design [12]. For memory applications, the

|               | Logic                                                         |                                                           | Memory                                                   |                                                               |

|---------------|---------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------|

|               | Hyper-FET                                                     | MTJ                                                       | PCM                                                      | Selector Switch                                               |

| Structure     |                                                               |                                                           |                                                          |                                                               |

| Key Mechanism | Resistivity difference between insulating and metallic phases | Bandgap difference between insulating and metallic phases | Resistivity difference between Crystalline and amorphous | Resistivity difference between insulating and metallic phases |

| Benefits      | Steep Sub-threshold swing                                     | Efficient control over tunneling                          | Dense reliable non-volatile memory                       | Reduced sneak path current                                    |

Table 1: Qualitative comparison of PTM applications

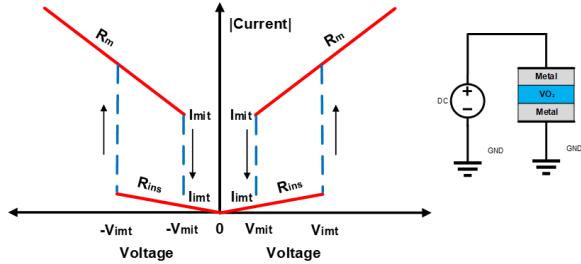

Fig. 2 Phase Transition Material: I-V characteristics

phase transition materials have been known and used extensively in Phase Change Memory (PCM) designs [13]. The resistivity difference between the crystalline and amorphous states of the material has been exploited to store the information. Recently, VO<sub>2</sub> based MIM (Metal-Insulator-Metal) PTM device has been shown to exhibit excellent behavior as the selector switch for the crossbar memory arrays [14]. The VO<sub>2</sub> MIM selector device significantly reduces the crossbar sneak path current due to its superior R<sub>OFF</sub>/R<sub>ON</sub> ratio and can operate at a lower voltage compared to other crossbar selector switch candidates [14].

The application of voltage bias across the two-terminal device with PTM sandwiched between metal electrodes exhibits the I-V characteristics as shown Fig. 2. Under no bias condition, PTM behaves like a resistor with resistance R<sub>INS</sub> (insulator), typically in the range of few Mega-ohms (MΩ). As the voltage bias increases, current (I=V/R<sub>INS</sub>) flows through the device. When this current (I) reaches a threshold (I<sub>MIT</sub>), abrupt phase transition takes place from insulating phase to the metallic phase and the resistance drops to very low value (R<sub>MET</sub>), typically in the range of few kilo-ohms (KΩ). The device continues to stay in the metallic phase (R<sub>MET</sub>) for any further increase in the voltage bias. The two terminal PTM device exhibits hysteresis behavior with respect to voltage bias (Fig. 2) Reducing the voltage bias, reduces the current (I=V/R<sub>MET</sub>) in the circuit. When the current reaches a lower threshold value (I<sub>MIT</sub>), again a phase transition takes place and the resistance of the device increases back to R<sub>INS</sub>. The voltage corresponding to insulating-to-metallic transition is referred as V<sub>MIT</sub> (V<sub>MIT</sub> = I<sub>MIT</sub>\*R<sub>INS</sub>) and the voltage corresponding to metallic-to-insulating transition is referred as V<sub>MIT</sub> (V<sub>MIT</sub> = I<sub>MIT</sub>\*R<sub>MET</sub>).

#### B. Soft-FET principle of operation

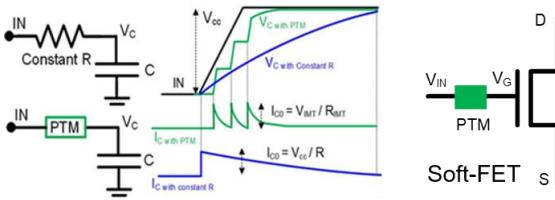

The two terminal PTM device when placed in series with a capacitor as shown in the Fig. 3 exhibits a unique transient behavior of the circuit. Under no voltage bias (V<sub>IN</sub>=0), the PTM is in insulating phase with resistance (R<sub>PTM</sub>) equal to R<sub>INS</sub>. The transient behavior can be understood by approximating the gate of MOSFET to a capacitor as shown in Fig.3. As the voltage V<sub>IN</sub> increases, the current starts charging the capacitor with a large time constant (R<sub>INS</sub>\*C) leading to slow charging of the capacitor. Thus, the V<sub>C</sub> node voltage rises slowly (lateral portion of the staircase V<sub>C</sub> waveform in Fig. 3) in comparison to the V<sub>IN</sub> node voltage resulting in increasing voltage difference (V<sub>IN</sub>-V<sub>C</sub>) across the PTM. When this voltage difference (V<sub>IN</sub>-V<sub>C</sub>) reaches the V<sub>MIT</sub>, abrupt phase transition from insulating to

Fig. 3 Soft charging using phase transition materials

Fig. 4 Soft-FET based inverter schematics and layout; PTM device parameters; transient voltage and current waveforms

metallic phase takes place. This phase transition is accompanied by a large current flow due to transition from large insulating state resistance (R<sub>INS</sub>) to a low metallic state resistance (R<sub>MET</sub>) of the PTM. In the metallic phase the capacitor charges quickly owing to small time constant (R<sub>MET</sub> \* C) causing the V<sub>C</sub> node voltage to rise steeply (vertical portion of the staircase V<sub>C</sub> waveform in Fig. 3). Consequently, when the voltage across the PTM (V<sub>IN</sub>-V<sub>C</sub>) drops below the V<sub>MIT</sub> threshold, phase transition from metallic to insulating state occurs. Again, the slow charging of the V<sub>C</sub> node eventually leads to phase transition to the metallic phase. This cycle is repeated until steady state of the circuit is attained (V<sub>IN</sub>=V<sub>CC</sub>). With V<sub>IN</sub> node at constant voltage (V<sub>CC</sub>) and the V<sub>C</sub> node charging slowly (insulating phase), the voltage difference (V<sub>IN</sub>-V<sub>C</sub>) reduces steadily leading to no further transitions. Thus, the V<sub>C</sub> node slowly raises with R<sub>INS</sub>\*C time constant and finally reaches the V<sub>IN</sub> at a later time instant as evident from Fig.3. Notice that, during the metallic phase, PTM conducts large capacitor charging current. When compared with the constant R charging with a uniform RC time constant scenario, the PTM device exhibits stepwise capacitor charging. A similar sequence of events can be observed when the V<sub>IN</sub> node voltage ramps down and exhibiting downward staircase waveform across the capacitor.

#### C. Soft-FET

The gradual charging of a capacitor explained in the previous subsection is central to the notion of Soft-FET transistor. Series connected PTM device at the gate terminal of a baseline MOSFET causes the gate voltage (V<sub>G</sub>) to rise slowly compared to the input voltage (V<sub>IN</sub>) leading to soft-switching operation. Hence, the proposed transistor architecture is abbreviated as “Soft-FET” to reflect its soft-transition mechanism.

### III. SOFT-FET LOGIC APPLICATIONS

#### A. Soft-FET based inverter DC characteristics

The concept of soft (slow) charging the capacitor with the aid of a PTM can be utilized to reduce the peak switching current drawn by the logic circuits from the V<sub>CC</sub> voltage rail. In this section, we present the analysis for the specific case of Soft-FET based inverter. As shown in Fig.4, the Soft-FET inverter is realized by placing the PTM in series with the common gate terminal of pull-up (P<sub>1</sub>) and pull-down (N<sub>1</sub>) transistors. The PTM layout can be envisioned as a ‘special via’ contact at the gate input and would not incur any area penalty for standard logic cell layouts. The DC characteristics of the inverter such as noise margin and dc output level are unperturbed by the presence of the PTM. This is unlike the earlier proposed Hyper-FET which results in slight DC noise margin degradation due to presence of insulating state PTM in its output

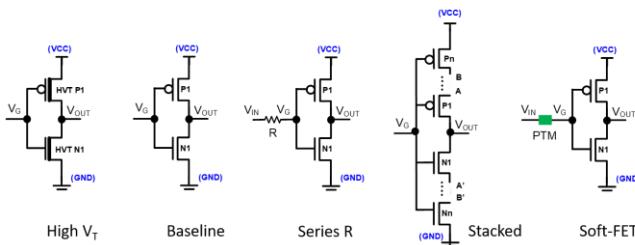

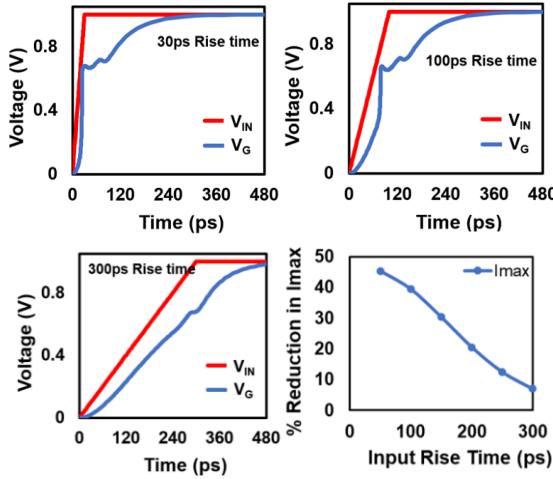

**Fig. 5 Comparison of Soft-FET with various CMOS topologies for peak switching current reduction**

series path. Absence of series resistance doesn't degrade Soft-FET DC ON current compared to the baseline MOSFET. However, the proposed Soft-FET doesn't reduce sub-threshold leakage current as observed in the Hyper-FET which leads to better  $I_{ON}/I_{OFF}$  ratio. The PTM device only modulates the charging/discharging of the input gate capacitor without affecting the dc behavior of the underlying MOSFET. The voltage dependent abrupt resistance change in PTMs rapidly changes the RC time constant at the gate input resulting in a soft switching transistor behavior.

#### B. Soft-FET based inverter transient characteristics

The Soft-FET inverter transient behavior is strongly governed by the PTM device parameters which modulates the staircase capacitor charging behavior. As the input supply voltage ( $V_{IN}$ ) rises/falls, the gate of the inverter ( $V_G$ ) experiences a slow rise/fall in voltage. This variation in the gate voltage modulates the current drawn from the  $V_{CC}$  rail and the current sunk into the ground. Fig. 4 describes a detailed description for the current dynamics during the falling transition of the Soft-FET inverter. SPICE simulations are performed using 40nm commercial CMOS process transistor models and a Verilog-A PTM model [15]. The PTM device parameters listed in Fig. 4 are based on the experimental  $VO_2$  demonstrations [11][16]. As the supply voltage ( $V_{IN}$ ) starts ramping down, the PTM in insulating phase causes the slow discharge of the gate voltage ( $V_G$ ) due to the large ( $R_{INS} \cdot C$ ) time constant. So, the gate voltage ( $V_G$ ) stays close to  $V_{CC}$  forcing the PMOS  $P_1$  to remain turned off resulting in a very low current being drawn from the  $V_{CC}$  rail. The increasing voltage difference ( $V_G - V_{IN}$ ) when reaches  $V_{IMT}$  induces a phase transition to metallic phase. Following this transition, the gate voltage ( $V_G$ ) drops below the threshold voltage ( $V_{TP}$ ) and turns the  $P_1$  transistor ON. During the metallic phase, the current drawn from the  $V_{CC}$  rail starts increasing. Note that unlike baseline CMOS, the current waveform of the Soft-FET inverter is shifted in time depending on input slew rate and the phase transition switching time. Also, in the metallic phase  $V_G$  reduces steeply and attempts to approach  $V_{IN}$  resulting in a decreasing ( $V_G - V_{IN}$ ). A reverse phase transition to insulating phase occurs when the voltage across the PTM ( $V_G - V_{IN}$ ) reduces below  $V_{MIT}$ . In the insulating phase, the slow discharge of  $V_G$  and corresponding slow increase in the output voltage ( $V_{OUT}$ ) results in almost constant current being drawn from the  $V_{CC}$  rail. Note that the peak switching current is significantly reduced compared to the baseline CMOS due to the weak turn on of the PMOS ( $P_1$ ) transistor. This implies that the PMOS transistor is weakly turned on for a longer duration exhibiting a smooth current waveform which results in reduced  $di/dt$ . Similarly, the input voltage

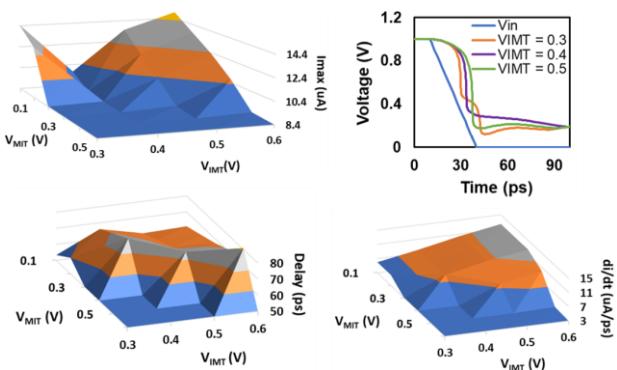

**Fig. 6 Variation of  $I_{MAX}$ ,  $di/dt$  and delay with the PTM device parameters  $V_{IMT}$  and  $V_{MIT}$**

ramp results in weak turn on of the NMOS transistor ( $N_1$ ) lowering the current sunk into the ground. Thus, the Soft-FET based logic circuits can exhibit reduced peak switching current and lower  $di/dt$  compared to baseline design.

#### C. Comparison with other peak current reduction techniques

The peak switching current and  $di/dt$  in the proposed Soft-FET is achieved using novel material properties. The same effect can also be achieved through multiple variants of baseline CMOS technology using additional transistors and/or passive resistors. It is imperative to perform a comparative study of the proposed Soft-FET inverter and CMOS inverter variants for peak current and  $di/dt$  reduction. The comparison (Fig. 5) is performed by tuning the baseline CMOS parameters (threshold voltage  $V_T$ , constant series resistance, # of transistors in the stack) such that all the cases result in approximately same  $I_{MAX}$  (peak switching current) as that of the Soft-FET inverter (i.e., iso- $I_{MAX}$  at  $V_{CC}=1V$ ). High supply voltage of 1V is used for iso- $I_{MAX}$  comparison as  $I_{MAX}$  is typically highest (worst) at the higher  $V_{CC}$ . SPICE simulations for minimum sized inverters are performed over a wide voltage range to evaluate the impact of iso- $I_{MAX}$  matching on the inverter delay. For a fair comparison, all inverter topologies drive a constant FO4 load (Fan Out of 4).

In the case of High  $V_T$  (HVT) CMOS, the threshold voltages of transistors (both NMOS and PMOS) are adjusted to match the  $I_{MAX}$  of the Soft-FET inverter when operated at 1V. This HVT variant shows output delay (time between 50% input to 20 (or 80) % output rise (fall)) comparable to the Soft-FET. However, when operated at lower  $V_{CC}$ , the high  $V_T$  transistors exhibits lower  $I_{MAX}$ , but significantly larger delay compared to the Soft-FET inverter (Fig. 5). This delay degradation can be attributed to the extremely low saturation current in HVT transistors operating at lower voltages (smaller  $V_{GS}-V_T$  term). Hence, the HVT transistors although achieve same  $I_{MAX}$  as that of the proposed Soft-FET while operating at higher voltages, incur significant delay penalty at low voltages. In the second scenario, an equivalent constant gate series resistance is used in the baseline CMOS inverter to match the same  $I_{MAX}$  as that of the Soft-FET inverter (at  $V_{CC}=1V$ ). This variant exhibit similar  $I_{MAX}$  but results in longer delay across the  $V_{CC}$  range compared to the Soft-FET inverter. The constant resistor in the gate causes the charging/discharging the output capacitor with large time constant leading to significantly larger delays compared to voltage dependent variable time constants in the Soft-FET. In the third scenario, stacked transistors are used (both NMOS and PMOS) to reduce the switching current in the CMOS inverter. This case also results in larger delay across the  $V_{CC}$  range compared to the Soft-FET inverter. The large delay in this scenario can be associated with the additional current required to charge the intermediate voltage nodes (A, B). Thus, the proposed Soft-FET achieves substantial peak switching current

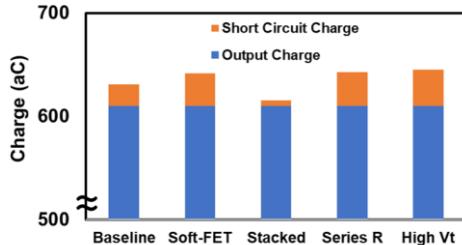

Fig. 7 Total charge comparison of Soft-FET inverter with various CMOS topologies

reduction with minimal delay penalty compared to the other CMOS topologies, over a wide operating voltage range.

#### IV. PTM DESIGN SPACE ANALYSIS

##### A. Design space exploration

The Soft-FET performance ( $I_{MAX}$  and  $di/dt$  reduction) is strongly dependent on the intrinsic device parameters ( $V_{IMT}$ ,  $V_{MIT}$ ,  $R_{INS}$ ,  $R_{MET}$ ,  $T_{PTM}$ ) of the PTM material. Varying device parameters affects the soft-switching behavior of the Soft-FET. This can lead to varying peak current drawn from the  $V_{CC}$  rail for the same output load and transistor size. So, there is a need to explore the PTM device parameter design space and optimize the PTM for the best Soft-FET performance. For this analysis, we have fixed the  $R_{INS}$  ( $= 500\text{k}\Omega$ ),  $R_{MET}$  ( $= 5\text{k}\Omega$ ),  $T_{PTM}$  ( $= 10\text{ps}$  PTM switching time) values and varied the voltage thresholds ( $V_{IMT}$ ,  $V_{MIT}$ ). The peak current,  $di/dt$  and delay of the Soft-FET inverters are compared for the varying  $V_{IMT}$  and  $V_{MIT}$  values. The input rise time of  $30\text{ps}$  and  $V_{CC}$  of  $1\text{V}$  are fixed for these comparisons. Fig. 6, shows the variation in the peak current of the Soft-FET inverter as a function of both  $V_{IMT}$  and  $V_{MIT}$ . As it is evident from the Fig. 6, there is a dip in the  $I_{MAX}$  around certain values of  $V_{IMT}$  (around  $0.4\text{V}$ ) which is an ideal zone for the Soft-FET operation. This behavior can be understood by analyzing the transient behavior of the inverter for  $V_{IMT}$  values around  $0.4\text{V}$ . Fig. 6 shows the gate voltage ( $V_G$ ) transients for three  $V_{IMT}$  values ( $0.3\text{V}$ ,  $0.4\text{V}$  and  $0.5\text{V}$ ). When the supply voltage ( $V_{IN}$ ) falls, the first pair of transition occurs, and the  $V_G$  attained when  $V_{IMT}$  equal to  $0.3\text{V}$  is more ( $V_G - V_{IN} > V_{IMT}$ ) compared to the cases when  $V_{IMT}$  equals  $0.4$  or  $0.5\text{V}$ . Thus, the voltage across the insulating PTM can reach  $V_{IMT}$  again causing a second pair of transition. Whereas, in the case of  $V_{IMT}$  equal to  $0.4$  or  $0.5\text{V}$ , the  $V_G$  attained is small enough ( $V_G - V_{IN} < V_{IMT}$ ) such that the voltage across the insulating PTM cannot reach  $V_{IMT}$ . Thus, the Soft-FET with  $V_{IMT}$  equal to  $0.3\text{V}$  makes the phase transition twice (two iterations of insulator-metal transition) but the Soft-FET with  $V_{IMT}$  equal to  $0.4\text{V}$  or  $0.5\text{V}$  makes only one iteration of phase transition. Followed by the second phase transition (at  $50\text{ps}$ ) in the  $V_{IMT}$  equal to  $0.3\text{V}$ , the gate voltage approaches a value close to  $V_{SS}$ . So, the PMOS is strongly turned on (large  $V_{GS}$ ) leading to larger peak current drawn from the  $V_{CC}$  rail. Similarly, the Soft-FET with  $V_{IMT}$  equal to  $0.5\text{V}$  also makes the transition to the region with strongly turned on PMOS leading to relatively large transient current. Whereas, the Soft-FET with  $V_{IMT}$  equal to  $0.4\text{V}$  attains a higher  $V_G$  (lower  $V_{GS}$ ) leading to lower peak current being drawn from the  $V_{CC}$  rail. This implies that the Soft-FET with  $V_{IMT}$  values  $0.3$  and  $0.5\text{V}$  turn on the PMOS transistor strongly compared to the Soft-FET with optimum  $V_{IMT}$  value equal to  $0.4\text{V}$ .

Similar analysis for delay variation with intrinsic PTM parameters is in shown in Fig. 6. It is evident that the delay is large for the same range of  $V_{IMT}$  values having low peak current. This is because the inverters with higher peak current charge the output voltage quickly compared to low peak current inverters. However, the maximum of  $di/dt$  (derivative of the current drawn from the  $V_{CC}$  rail) variation with intrinsic parameters shows a different trend. The maximum  $di/dt$  of the Soft-FET inverter increases for increasing

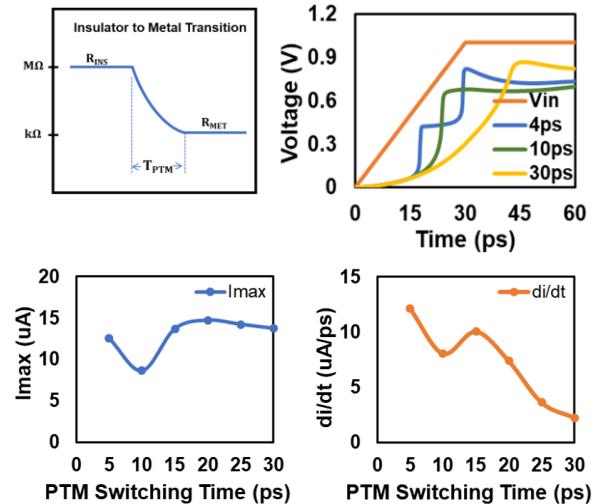

Fig. 8 Effect of PTM switching time ( $T_{PTM}$ ) on  $I_{MAX}$  and  $di/dt$

values of  $V_{IMT}$  threshold. Once again, this can be understood by looking at the gate voltage transients shown in Fig. 6. As explained earlier, the Soft-FET inverter with  $V_{IMT}$  equal to  $0.3\text{V}$  makes two transitions, so the pull up transistor is weakly turned on during the first phase change transition followed by strong turn on during the second transition. So, both the transitions lead to smaller  $di/dt$  because of the gradual increase in the current (off current - weakly turned on - strongly turned on). Whereas, the Soft-FET inverter with  $V_{IMT}$  equal to  $0.4\text{V}$  makes single transition to moderately turn ON condition leading to higher  $di/dt$  compared to  $V_{IMT}$  equal to  $0.3\text{V}$ . Similarly, the  $V_{IMT}$  equal to  $0.5\text{V}$  case makes even larger transition to strongly turned ON condition leading to a larger  $di/dt$  in comparison with other cases. Thus, the intrinsic parameters of the PTM material play a crucial role in the Soft-FET performance and must be appropriately tuned with careful device fabrication for enhancing the Soft-FET performance.

##### B. Design tradeoffs

The proposed Soft-FET incurs delay penalty for slow charging/discharging the output nodes as it is evident from the output characteristics shown in Fig. 5. However, as explained earlier it provides the minimal delay penalty across a wide voltage range. Moreover, a portion of the Soft-FET delay penalty can be attributed to the switching time taken by the PTM to make transition from insulating to metallic phase. Reducing the PTM switching time ( $T_{PTM}$ ) can reduce the overall delay of the Soft-FET transistors.

In addition, the Soft-FET incurs increased short circuit charge compared to the baseline inverter. Soft-FET inverter short circuit duration comprises of two parts. First time interval consists of fast transition of the gate input once  $V_{IN}$  crosses  $V_{IMT}$  threshold. This narrow time duration results in lower short circuit charge compared to the baseline CMOS inverter. On the other hand, the second-time interval consists of a slowly changing gate input once the PTM has switched to the insulating phase. This longer time duration results in significant short circuit charge. The net result of compensating effects of these time intervals decide the overall short circuit charge consumed by the Soft-FET inverter. Fig. 7 shows the short circuit and output charge consumed during the falling input transition ( $V_{CC} = 1\text{V}$ ) for various current reduction techniques discussed in earlier section. Soft-FET performs on par with HVT and series-R cases with respect to the short circuit charge.

##### C. Intrinsic PTM switching time

The intrinsic switching time ( $T_{PTM}$ ) is the time taken by the PTM to make the transition from insulating phase to

**Fig. 9 Effect of input slew rate on the PTM switching behavior**

metallic phase and vice versa. After the voltage across the PTM reaches the switching thresholds, the resistance of the PTM increases/decreases and reaches the desired value after  $T_{PTM}$  duration. Recent experiments have demonstrated femto-second phase transition times in  $VO_2$  PTMs using optical excitations and switching time of  $\sim 8$ ps with electrical excitations [16] [17]. The switching time determines the shape of the  $V_G$  waveform and thus plays a crucial role in the performance of the Soft-FET based logic. Hence, the performance of the Soft-FET inverter is assessed for varying intrinsic switching speeds. For this analysis, all the other PTM parameters are fixed to the standard values shown in Fig. 4. For smaller  $T_{PTM}$  values  $V_G$  experiences multiple phase transitions as shown in Fig. 8. This is due to the fast switching of PTM resulting in a rapid catch up of  $V_G$  node to the  $V_{IN}$  node. The final phase transition occurs close to  $V_{CC}$  causing a strong MOSFET turn on leading to larger peak current. The number of phase transitions decrease with increasing  $T_{PTM}$ . Large  $T_{PTM}$  also results in a strong transistor turn on leading to higher peak current. However, if the  $T_{PTM}$  is properly optimized then the transition occurs in a region where PMOS transistor is weakly ON leading to lower peak current drawn from the  $V_{CC}$  rail. The delay of the Soft-FET varies in a complimentary manner leading to a peak at moderate  $T_{PTM}$  values. However, the  $di/dt$  shows a decreasing trend with increasing  $T_{PTM}$ .

#### D. Slew rate of input signal

The slew rate of the input signal is also an important factor in the Soft-FET performance. The switching behavior of the Soft-FET is determined by the  $(\text{input slew-rate}/R_{PTM} \cdot C)$  ratio. At higher ratios, the  $V_G$  cannot increase at the rate of  $V_{IN}$  due to large time constant. This creates an increasing voltage across the PTM and leads to the phase transition. However, at smaller ratios, the  $V_G$  can rise at the same rate of  $V_{IN}$  and thus fewer phase transition behavior is observed. Hence, the slew rate of the input signal must be appropriately tuned for obtaining the best Soft-FET performance. Fig. 9 shows the  $V_G$  waveforms for three different values of the input slew rate. The simulations are performed keeping all the intrinsic parameters of the PTM as shown in Fig. 4 and  $V_{CC}=1V$ . It is evident that the soft-switching behavior of the Soft-FET vanishes with decreasing slew rate. The reduced switching

**Fig. 10 Soft-FET applications in power gate design**

behavior makes the Soft-FET behave more like the baseline CMOS but with increased delay. Thus, the peak current and  $di/dt$  reduction are not significant. Fig. 9 shows the percentage  $I_{MAX}$  reduction for varying values of the input slew rate. The  $di/dt$  follows similar trend to  $I_{MAX}$  but delay increases with decreasing slew rate.

#### E. Design recommendations

It is apparent from the previous two sections that switching speed of the PTM and the input slew rate need to be optimized for the desired reduction in peak current and  $di/dt$ . We recommend the ratio of input slew rate to the PTM switching time need be around 1.5-3. However, this ratio is strong function of  $V_{CC}$  and/or  $V_{IMT}$  parameters.

### V. SOFT-FETS FOR VOLTAGE DROOP MITIGATION

This section presents two application case studies of the proposed Soft-FET transistor in mitigating the voltage droop due to high capacitive load driving.

#### A. Soft-FETs for power gate design

As power management is becoming crucial for extending the battery lifetime of handheld devices, the frequency of entering/exiting the sleep states become quite frequent [18]. While exiting the sleep mode, sudden surge of load charging current can cause large  $di/dt$  and can induce a voltage droop on the neighboring active units sharing the same supply rail ( $V_{CC}$ ). This voltage droop needs to be marginated in the supply voltage specifications which degrades the energy efficiency. The proposed Soft-FET concept can be utilized in a power-gate design with soft-transitioning gate voltage as shown in Fig. 10. The power delivery network parameters are adopted from [19]. The proposed Soft-FET concept slows down the ramp rate of the power-gate gate voltage and which reduces the current by 2X. The supply voltage droop is reduced by  $\sim 20$ mV using Soft-FET power gate which would result in improved energy efficiency.

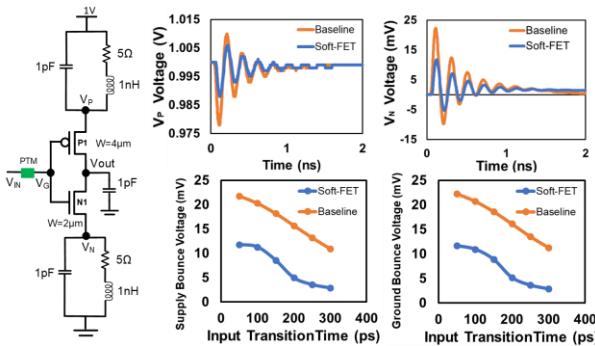

#### B. Soft-FETs for I/O buffer design

The rapid changes in the current consumption of a circuit block having many logic gates and I/O buffers switching simultaneously combined with the series inductance of the power distribution network (PDN) results in Simultaneous Switching Noise (SSN) [20]. The SSN causes

Fig. 11 Soft-FET applications in I/O buffer design

ringing on the  $V_{CC}$  and  $V_{SS}$  rails and needs to be accounted in the supply voltage specifications. The increased voltage guard bands necessitate higher operating voltage for achieving target performance degrading the energy efficiency. Fig. 11 shows a case study of an I/O buffer driving a pad load capacitance of  $1\text{pF}$  and experiencing a  $V_{CC}$  and  $V_{SS}$  bounce of  $\sim 22\text{mV}$ . The proposed Soft-FET can be effectively used to control the I/O buffer input slew rate by utilizing the abrupt phase change in the PTM. The soft-switching mechanism reduces the peak current and the  $di/dt$  lowering the SSN noise in Soft-FET I/O drivers by 46% compared to the baseline I/O drivers. In this analysis, the PTM parameters are same as shown in Fig. 4. Furthermore, the Soft-FET I/O driver achieves higher SSN improvement with increasing input transition times as shown in Fig. 11. The reduced SSN would lead to a lower operating voltage improving the energy efficiency by 8.8% when operating at  $V_{CC}=1\text{V}$ .

## VI. CONCLUSION

In this paper, we proposed a soft-switching transistor architecture named “Soft-FET” utilizing the abrupt phase change mechanism in the phase transition materials. By placing an optimized PTM in series with the gate terminal of a MOSFET, its gate voltage can be changed smoothly resulting in reduced peak switching current and lower  $di/dt$ . The proposed Soft-FET based inverter shows minimal delay penalty across a wide voltage range compared to other CMOS inverter variants under  $\text{Iso-}I_{MAX}$  conditions. We presented detailed PTM parameter optimization for the best Soft-FET performance and showed its applications in power gate design and I/O buffer design to mitigate the voltage supply droops for improved energy efficiency. Preliminary experiments on  $\text{VO}_2$  material have shown reliability  $> 10^9$  cycles [21]. Further studies in this domain are required for obtaining high quality phase transitions in these materials.

## VII. REFERENCES

1. M. Ravindiran, M. Cotter, V. Saripalli, M. J. Irwin, S. Datta, and V. Narayanan, "Ultra low power circuit design using tunnel FETs," in *Proc. IEEE Computer Society Annual Symposium on VLSI (ISVLSI)*, 2012, pp. 153-158.

2. M. Horowitz, T. Indermaur, and R. Gonzalez, "Low-power digital design," in *Proc. IEEE International Symposium on Low Power Electronics Design*, 1994, pp. 8-11.

3. S. Bobba, T. Thorp, K. Aingaran, and D. Liu, "IC power distribution challenges," in *Proc. IEEE/ACM international conference on Computer-aided design*, 2001, pp. 643-650.

4. D. Ma, and R. Bondade; "Enabling power-efficient DVFS operations on silicon," *IEEE Circuits and Systems Magazine* 10, no. 1, pp.14-30, 2010.

5. M. D. Seeman, V. W. Ng, H. P. Le, M. John, E. Alon, and S. R. Sanders; "A comparative analysis of Switched-Capacitor and inductor-based DC-DC conversion technologies," in *Proc. 12<sup>th</sup> IEEE Workshop on Control and Modeling for Power Electronics (COMPEL)*, 2010, pp. 1-7.

6. S. Kim, C. J. Choi, D. K. Jeong, S. V. Kesonocky, and S. B. Park; "Reducing Ground-Bounce Noise and Stabilizing the Data-Retention Voltage of Power-Gating Structures," *IEEE Transactions on Electron Devices*, pp. 197-205 Vol. 55, No. 1, January 2008.

7. S. Gong, H. Hentzell, S. T. Persson, H. Hesselbom, B. Lofstedt, and M. Hansen; "Techniques for reducing switching noise in high speed digital systems," in *Proc. Eighth International Application Specific Integrated Circuits Conference*, 1995, pp. 21-24.

8. N. F. Mott, and L. Friedman; "Metal-insulator transitions in  $\text{VO}_2$ ,  $\text{Ti}_2\text{O}_3$  and  $\text{Ti}_{2-x}\text{V}_x\text{O}_3$ ," *Philosophical Magazine* 30, no. 2, pp.389-402, 1974.

9. J. Park, T. Hadamek, A. B. Posadas, E. Cha, A. A. Demkov and H. Hwang; "Multilayered  $\text{NiO}_x/\text{NbO}_x/\text{NiO}_y$  fast drift free threshold switch with high  $Ion/Ioff$  ratio for selector application," *Scientific Reports*, February 2017.

10. N. Shukla, A. V. Thathachary, A. Agrawal, H. Paik, A. Aziz, D. G. Schlom, S. K. Gupta, R. E. Herbert, and S. Datta; "A steep-slope transistor based on abrupt electronic phase transition," *Nature communications* 6, pp.7812, 2015.

11. A. Aziz, N. Shukla, S. Datta, and S. K. Gupta; "Steep Switching Hybrid Phase Transition FETs (Hyper-FET) for Low Power Applications: A Device-Circuit Co-design Perspective-Part I," *IEEE Transactions on Electron Devices* 64, no. 3, pp.1350-1357, 2017.

12. E. Freeman, A. Kar, N. Shukla, R. Misra, R. E. Herbert, D. Schlom, V. Gopalan, K. Rabe, and S. Datta; "Characterization and modeling of metal-insulator transition (MIT) based tunnel junctions," in *Proc. Device Research Conference (DRC), 2012 70th Annual*, 2012, pp. 243-244.

13. H. S. P. Wong, S. Raoux, S. B. Kim, J. Liang, J. P. Reifenberg, B. Rajendran, M. Asheghi, and K. E. Goodson; "Phase change memory," *Proceedings of the IEEE* 98, no. 12, pp.2201-27, 2010.

14. M. Son, J. Lee, J. Park, J. Shin, G. Choi, S. Jung, W. Lee, S. Kim, S. Park, and H. Hwang; "Excellent Selector Characteristics of Nanoscale  $\text{VO}_2$  for High-Density Bipolar ReRAM Applications," *IEEE Electron Device Letters* 32, no. 11, pp.1579-1581, 2011.

15. W. Y. Tsai, X. Li, M. Jerry, B. Xie, N. Shukla, H. Liu, N. Chandramoorthy, M. Cotter, A. Raychowdhury, D. M. Chiarulli, S. P. Levitan, S. Dutta, J. Sampson, N. Ranganathan, V. Narayanan; "Enabling new computation paradigms with hyperFET-an emerging device," *IEEE Transactions on Multi-Scale Computing Systems* 2, no. 1, pp.30-48, 2016.

16. P. U. Jepsen, B. M. Fischer, A. Thoman, H. Helm, J. Y. Suh, R. Lopez, and R. F. Haglund Jr; "Metal-insulator phase transition in a  $\text{VO}_2$  thin film observed with terahertz spectroscopy," *Physical Review B*, 74(20), p.205103, 2006.

17. A. Grupp, B. Mayer, C. Schmidt, J. Oelmann, R. E. Marvel, R. F. Haglund, A. Leitenstorfer, and A. Pashkin; "Femtosecond insulator-metal transition in  $\text{VO}_2$  induced by intense multi-THz transients," in *Proc. CLEO: QELS Fundamental Science*, Optical Society of America, June 2014, pp. FTh1C-4.

18. A. Sinha and A. Chandrakasan; "Dynamic power management in wireless sensor networks," *IEEE Design and Test of Computers*, pp. 62-74, Vol. 18, 2001.

19. X. Zhang, T. Tong, S. Kaney, S. K. Lee, G. Y. Wei and D. Brooks; "Characterizing and evaluating voltage noise in multi-core near-threshold processors," in *Proc. International Symposium on Low Power Electronics Design*, 2013, pp. 82-87.

20. H. Wang and E. Salman; "Closed-Form Expressions for I/O Simultaneous Switching Noise Revisited"; *IEEE Transactions on VLSI Systems*, pp. 769-773, Vol. 25, No. 2, February 2017.

21. J. Frougier, N. Shukla, D. Deng, M. Jerry, A. Aziz, L. Liu, G. Lavallee, T. S. Mayer, S. K. Gupta, and S. Datta; "Phase-transition-FET exhibiting steep switching slope of 8mV/decade and 36% enhanced ON current," in *Proc. IEEE VLSI Technology Symposium*, 2016, pp. 1-2.