# YBa<sub>2</sub>Cu<sub>3</sub>O<sub>7- $\delta$</sub> -CeO<sub>2</sub>-YBa<sub>2</sub>Cu<sub>3</sub>O<sub>7- $\delta$</sub> Multilayers Grown by Reactive Co-Evaporation on Sapphire Wafers

Yan-Ting Wang <sup>✉</sup>, Member, IEEE, Robert Semerad, Stephen J. McCoy, Han Cai, Jay LeFebvre <sup>✉</sup>, Holly Grezdo, Ethan Y. Cho <sup>✉</sup>, Member, IEEE, Hao Li <sup>✉</sup>, and Shane A. Cybart <sup>✉</sup>, Member, IEEE

**Abstract**—High- $T_C$  superconductor thin film heterostructures were deposited using reactive co-evaporation for dual layer electronic applications. The epitaxial structure consisted of 35-nm YBa<sub>2</sub>Cu<sub>3</sub>O<sub>7- $\delta$</sub> (YBCO), 75-nm CeO<sub>2</sub>, 150-nm YBCO, and 20-nm CeO<sub>2</sub> on *r*-plane sapphire wafers. The critical temperature was measured to be 83.6 K and 84.8 K for the bottom and top YBCO layers, respectively. Atomic force microscopy reveals smooth surfaces with RMS roughness of the top YBCO layer to be 4.7 nm. The CeO<sub>2</sub> insulating layer exhibited hopping conduction that freezes out at low temperature, making these structures suitable for electrical circuits with isolated ground planes.

**Index Terms**—Multilayer, heterostructures, YBCO, CeO<sub>2</sub>, reactive co-evaporation.

## I. INTRODUCTION

HIGH-TEMPERATURE superconductors (HTS) are promising candidates for superconducting electronics operating at elevated temperatures. Improvements in the ability to grow, pattern and interconnect multiple HTS layers are needed, in particular at the commercial wafer scale level. Several applications would greatly benefit.

HTS SQUID magnetometers can achieve high sensitivity through integration with multi-turn flux transformers which require vias and crossovers between layers [1]. This allows the primary and secondary coils to cross over one another to maintain a continuous superconducting loop. Ground planes are needed for high frequency RF electronic applications and those that

Manuscript received November 5, 2018; accepted January 30, 2019. Date of publication February 11, 2019; date of current version March 12, 2019. This work was supported in part by ARO Grant W911NF1710504, in part by AFOSR Grant FA955015-1-0218, in part by NSF Grant 1664446, and in part by UCOP MRPI Award 009556-002. (Corresponding author: Shane A. Cybart.)

Y.-T. Wang, S. J. McCoy, and S. A. Cybart are with the Department of Material Science and Engineering, University of California, Riverside, CA 92521 USA (e-mail: ywang502@ucr.edu; smcco003@ucr.edu).

R. Semerad is with the Ceraco Ceramics Coating GmbH, Ismaning 85737, Germany (e-mail: semerad@ceraco.de).

H. Cai, H. Grezdo, E. Y. Cho, H. Li, and S. A. Cybart are with the Department of Mechanical Engineering, University of California, Riverside, CA 92521 USA (e-mail: hcai017@ucr.edu; hgrez001@ucr.edu; eycho@ucr.edu; haoli@ucr.edu; cybart@ucr.edu).

J. LeFebvre is with the Department of Physics, University of California, Riverside, CA 92521 USA (e-mail: jlefe001@ucr.edu).

Color versions of one or more of the figures in this paper are available online at <http://ieeexplore.ieee.org>.

Digital Object Identifier 10.1109/TASC.2019.2898778

require low sheet inductance, such as single flux quantum (SFQ) logic circuits [2].

For optimizing SFQ circuits, inductance is especially important because the product of inductance and the Josephson junction critical current ( $I_C$ ) must be of the order of the flux quantum ( $\Phi_0$ ). This is essential so that only a single flux quantum can be stored or processed per each SFQ cell. At the temperatures where HTS SFQ operate,  $I_C$  must be higher than that used in low temperature SFQ to suppress thermal noise, which is necessary for maintaining a low bit-error-rate. Larger values of  $I_C$  increase the need for small HTS sheet inductance. In prior work, comparing multilayer devices prepared by pulsed laser deposition, Terai *et al.* showed that the inductance can be lowered by almost three times through the inclusion of a superconducting ground plane [3].

Several other previous studies have also been performed on HTS multilayers grown by PLD using both SrTiO<sub>3</sub> [4], [5], and CeO<sub>2</sub> [6] as the insulating layer. These works clearly demonstrated the potential of multilayer stacks, however there is still a need for a larger scale commercial process.

Controllable high quality multilayer structures could lead to the realization of more complex multilevel circuits such as those fabricated using Nb-Al<sub>2</sub>O<sub>x</sub>-Nb Josephson junctions [7], [8]. However, there are still many challenges that need to be overcome to bring this to fruition, such as large area growth of HTS epitaxial thin films with small surface roughness, high critical current density ( $J_C$ ) and high-transition temperature ( $T_C$ ). Furthermore, there is a need for isolation of multiple layers with no leakage. These properties are intertwined and are important to be optimized simultaneously. For example, if surface roughness is not minimized, pinhole shorts will occur through the insulating layer. Therefore, it is important to investigate and examine the properties of a thin electronics grade HTS layer with an isolated ground plane grown with a commercial deposition process.

Commercial production of very high quality films has been available for decades using reactive coevaporation (RCE) [9]. In the RCE process, metallic elements such as yttrium, barium, and copper, (in the case of YBCO) are thermally evaporated from resistive sources onto a substrate attached to a rotating plate that revolves at 5 Hz, cycling the wafers between the evaporation vacuum chamber at  $7.5 \times 10^{-6}$  torr (1 mPa) and a higher

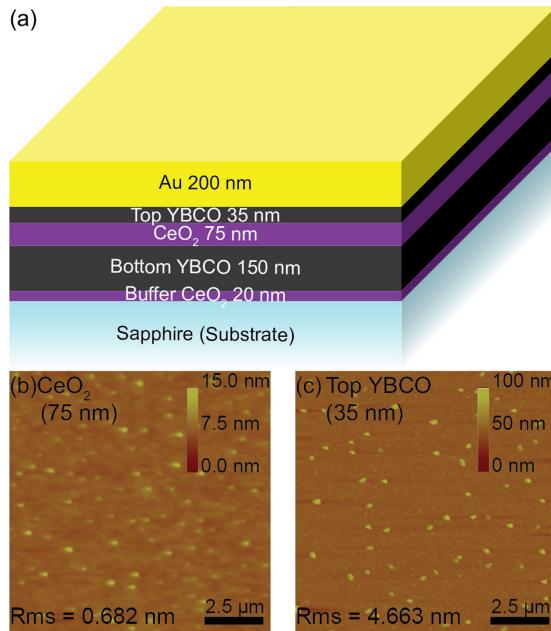

Fig. 1. (a) Schematic illustration of the multilayer structure consisted with 200-nm Au, 35-nm top YBCO, 75-nm CeO<sub>2</sub>, 150-nm bottom YBCO and 20-nm CeO<sub>2</sub> buffer layer on sapphire substrate. (b) 75-nm CeO<sub>2</sub> surface topography scanned by AFM. (c) Top 35-nm YBCO surface topography scanned by AFM.

pressure oxygen “pocket” blackbody heater at  $7.5 \times 10^{-4}$  torr (0.1 Pa) [9]. The evaporation rate of the metal sources are monitored using quartz crystal micro balances with collimators to keep the accuracy within 1%. Moreover, the growing temperature at 650 °C is about 150 degrees lower in temperature than other techniques. Lower temperature decreases the possibility of the film cracking upon cool down [10], [11]. It also minimizes the formation of inter-metallic phases such as BaCeO<sub>3</sub>.

RCE HTS coated substrates have been routinely produced in large numbers for commercial purposes. When the films stoichiometry is precisely tuned very smooth ultra thin films with thickness of the order of a few tens of nanometer can be produced for electronics grade material. Another key advantage to RCE is that the deposition area can be very large and the nature of the rotating pocket heater facilitates deposition of many wafers simultaneously or very large wafer sizes [9].

In this work, we grow and investigate the properties of a thin electronics grade HTS layer with an isolated ground plane grown with RCE for multilayer wafer production.

## II. EXPERIMENTS AND RESULTS

A multilayer heterostructure consisting of 35-nm YBCO, 75-nm CeO<sub>2</sub>, 150-nm YBCO and 20-nm CeO<sub>2</sub> (top to bottom) on *r*-plane sapphire was grown at Ceraco GmbH using RCE as shown in Fig. 1(a). In our heterostructures, the layer thicknesses were chosen to be optimized for Josephson devices with junctions fabricated using the focused helium ion beam process (FHB) [12] in the top layer. Using FHB, high quality nanoscale devices can be created, but they require very smooth and thin films (35 nm) [13], [14].

The thickness of the bottom YBCO ground plane layer was chosen to be of the same order of the penetration depth of YBCO to ensure that the ground plane can shield effectively. For the insulating CeO<sub>2</sub> layer, the thickness is maximized while keeping the total multilayer thickness under 300 nm to prevent cracking of which is common in films grown on sapphire.

For our multilayer structure, five 2” *r*-plane sapphire wafers were placed at the center of the plate(n) for deposition. First a 20-nm buffer CeO<sub>2</sub> layer was grown followed by a 150-nm thick YBCO film to serve as the bottom ground plane. In order to make the film as smooth as possible, to prevent pinhole shorts through the subsequent layers, the copper content was reduced. This eliminates copperoxide precipitates on the surface at the expense of a reduced  $T_C$  and  $J_C$ . Second, a 75-nm CeO<sub>2</sub> layer was deposited, and the  $T_C$  and  $J_C$  of the bottom YBCO were measured to be 83.6 K and 1.0 MA/cm<sup>2</sup> respectively using an inductive Cryoscan.

The wafers were returned to the vacuum chamber along with an additional CeO<sub>2</sub> buffered sapphire test substrate and a 35-nm thick YBCO layer was grown followed by a 200 nm gold contact layer. For this deposition the copper content was increased to obtain better electrical properties. Following this second deposition  $T_C$  and  $J_C$  were measured to be 84.8 K and 2.3 MA/cm<sup>2</sup> using a cryoscan of the test substrate. A third cryoscan of the hetero structure exhibited a  $J_C$  of 1.2 MA/cm<sup>2</sup> for the two layers combined. Assuming a  $J_C$  of 1.0 MA/cm<sup>2</sup> for the bottom layer and 2.3 MA/cm<sup>2</sup> for the top layer, one would expect for the double layer a  $J_C$  of  $(1.0 \text{ MA/cm}^2 \times 150 \text{ nm} + 2.3 \text{ MA/cm}^2 \times 35 \text{ nm})/185 \text{ nm} = 1.25 \text{ MA/cm}^2$ , consistent with the measured value 1.2 MA/cm<sup>2</sup> of the stack. This suggests that the quality of the 35-nm YBCO on top of the CeO<sub>2</sub>/YBCO is similar to the film on the test substrate.

To characterize the surface morphology, atomic force microscopy (AFM) was used to inspect the surfaces. To scan the top YBCO surface, the gold capping layer is removed with KI<sup>+</sup> gold etch. The insulating 75-nm CeO<sub>2</sub> surface topography is acquired from the samples removed from the chamber after the 75-nm CeO<sub>2</sub> deposition. The YBCO top layer and CeO<sub>2</sub> surfaces were both smooth with the exception of a small number of particles on the top YBCO surface as shown in 1(b) and (c). Large scale defects were not observed. Surface roughness was determined to be 0.7 nm and 4.7 nm for the CeO<sub>2</sub> and top YBCO respectively.

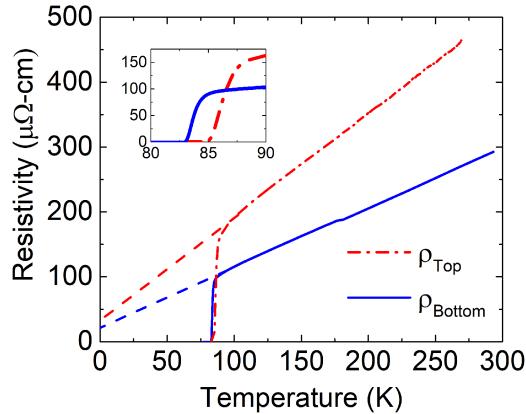

Resistivity as a function of temperature was measured for each layer using a 4-point Van der Pauw geometry and lock-in amplifier. The results are shown in Fig. 2. To access only the bottom layer for this measurement, the top YBCO layer is fully removed with phosphoric acid and the insulating CeO<sub>2</sub> layer is scribed through to make contact with bottom YBCO layer.

Both layers exhibit sharp transitions with residual resistivities of 22  $\mu\Omega\text{-cm}$  and 35  $\mu\Omega\text{-cm}$  for the top and bottom layers respectively which suggest that there is low temperature independent defect scattering. We remark that the top YBCO shows an apparent room temperature resistivity of 500  $\mu\Omega\text{-cm}$  that is much larger than the ground plane layer resistivity of 275  $\mu\Omega\text{-cm}$ . We interpret this result to be due to an overestimate of the electrical thickness of the top layer. Process damage, surface roughness

Fig. 2. Resistivity-Temperature of top YBCO layer (red dash dot line) and bottom YBCO layer (blue solid line), and the red and blue dash lines are extrapolations for residual resistivity of 22  $\mu\Omega\text{-cm}$  and 35  $\mu\Omega\text{-cm}$  of top and bottom YBCO layer respectively. The curves are zoomed in around transition in the inset.

and a possible dead layer at the CeO<sub>2</sub> interface likely contribute to a reduction of the electrical thickness. Assuming that the actual resistivity of the two layers is the same yields a reasonable electrical thickness of 20 nm for the top layer.

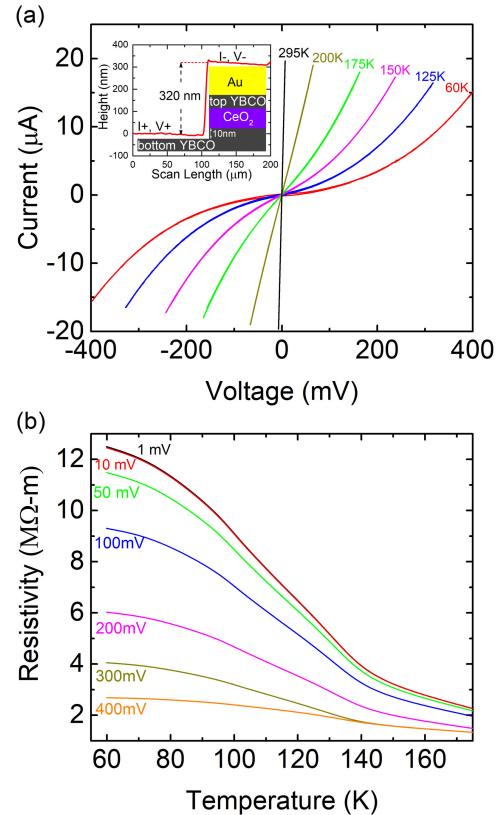

To characterize the electrical properties of the CeO<sub>2</sub> insulating layer to test for the presence of pinhole shorts we prepared the samples for a four-point resistance measurement. In order to make contact with the buried YBCO, a 3 mm diameter circle was printed on top of the sample using photolithography. The pattern was transferred into both gold and the top YBCO layer by chemical etching with KI-I<sup>+</sup> and 0.1% phosphoric acid respectively. The CeO<sub>2</sub> layer was etched using a 500 V argon ion mill. To ensure proper milling down to the bottom YBCO layer, electrical continuity was tested between the bottom contacts and the etch step height of the stack was measured to be 320 nm with a KLA Tencor P-7 profilometer in the inset of Fig. 3.

Four electrical contacts were attached to the sample for a four-point measurement. Two contacts were attached to the top Au electrode and the other two were attached to the bottom YBCO layer with silver paint. Current as a function of voltage ( $I - V$ ) was measured by using a function generator to drive the sample and a series resistor at 1 Hz. Low noise preamplifiers were used to measure the voltage across the CeO<sub>2</sub> ( $V$ ) and the series resistor ( $I$ ). Curves were continuously recorded and the sample was cooled to low temperature. Selected curves are shown in Fig. 3(a) for a series of different temperatures. At room temperature, the insulating layer appeared ohmic with a resistance of 351  $\Omega$ . However as temperature was reduced below 200 K non-linearity was observed (Fig. 3(a)).

To investigate the temperature dependence further we calculate the resistivity assuming a uniform current density through the patterned area from the resistance obtained from data in Fig. 3(a) and the result is plotted for several voltages in Fig. 3(b). We observe a strong dependence of the resistivity on both temperature and voltage that is reminiscent with variable range hopping transport. We note that the appearance of our data to approach an asymptotic value at low temperature is likely an artifact from using a measurement voltage much greater than the

Fig. 3. (a) Current-Voltage across 75-nm CeO<sub>2</sub> insulating layer measured at different temperatures. The inset is the step height obtained by the profilometer to ensure etching was through the layers. (b) Resistivity-Temperature of 75-nm CeO<sub>2</sub> insulating layer obtained from (a) for different constant voltage ranges.

thermal energy  $k_B T$ . From these large area measurements we conclude that there are no pinhole shorts through the dielectric and that the transport mechanism is thermally activated variable range hopping.

### III. CONCLUSION

In conclusion we have investigated superconducting YBCO-CeO<sub>2</sub>-YBCO thin films in multilayer heterostructures grown by reactive co-evaporation. Both the top 35-nm and the bottom 150-nm YBCO layers have high transition temperatures at 83.6 K and 84.8 K and large critical current densitys with moderate surface roughness. The CeO<sub>2</sub> insulator exhibited activated transport but provides substantial insulation with resistivity of 11.5 M $\Omega\text{-m}$  at 77 K. While additional structural characterization such as XRD and transmission electron microscopy could yield more insight into the quality of these structures electrically these films look very suitable for thin film electronics. This is another step forward towards a large scale commercial multilayer RCE process for HTS electronics. In the future, we envision the incorporation of vias and crossovers for more complex integrated YBCO circuits.

### ACKNOWLEDGMENT

The authors would like to thank Bob Dynes for insightful advice.

## REFERENCES

- [1] J. Jaycox and M. Ketchen, "Planar coupling scheme for ultra low noise dc SQUIDS," *IEEE Trans. Magn.*, vol. MAG-17, no. 1, pp. 400–403, Jan. 1981.

- [2] H. Wakana *et al.*, "Improvement in reproducibility of multilayer and junction process for HTS SFQ circuits," *IEEE Trans. Appl. Supercond.*, vol. 15, no. 2, pp. 153–156, Jun. 2005.

- [3] H. Terai, M. Hidaka, T. Satoh, and S. Tahara, "Direct-injection high- $T_c$  dc-SQUID with an upper  $\text{YBa}_2\text{Cu}_3\text{O}_{7-x}$  ground plane," *Appl. Phys. Lett.*, vol. 70, pp. 2690–2692, 1997.

- [4] J. J. Kingston, F. C. Wellstood, P. Lerch, A. H. Miklich, and J. Clarke, "Multilayer  $\text{YBa}_2\text{Cu}_3\text{O}_{7-x}$ - $\text{SrTiO}_3$ - $\text{YBa}_2\text{Cu}_3\text{O}_{7-x}$  films for insulating crossovers," *Appl. Phys. Lett.*, vol. 56, no. 2, pp. 189–191, 1990.

- [5] X. Xi, Q. Li, C. Doughty, C. Kwon, S. Bhattacharya, A. Findikoglu, and T. Venkatesan, "Electric field effect in high  $T_c$  superconducting ultrathin  $\text{YBa}_2\text{Cu}_3\text{O}_{7-x}$  films," *Appl. Phys. Lett.*, vol. 59, no. 26, pp. 3470–3472, 1991.

- [6] M. Van Wijck, M. Verhoeven, E. Reuvekamp, G. Gerritsma, D. H. Blank, and H. Rogalla, "CeO<sub>2</sub> as insulation layer in high  $T_c$  superconducting multilayer and crossover structures," *Appl. Phys. Lett.*, vol. 68, no. 4, pp. 553–555, 1996.

- [7] P. Bunyk *et al.*, "High-speed single-flux-quantum circuit using planarized niobium-trilayer Josephson junction technology," *Appl. Phys. Lett.*, vol. 66, no. 5, pp. 646–648, 1995.

- [8] S. K. Tolpygo *et al.*, "Advanced fabrication processes for superconducting very large-scale integrated circuits," *IEEE Trans. Appl. Supercond.*, vol. 26, no. 3, Apr. 2016, Art. no. 1100110.

- [9] B. Utz, R. Semerad, M. Bauer, W. Prusseit, P. Berberich, and H. Kinder, "Deposition of YBCO and NBCO films on areas of 9 inches in diameter," *IEEE Trans. Appl. Supercond.*, vol. 7, no. 2, pp. 1272–1277, Jun. 1997.

- [10] R. Wordenweber *et al.*, "Large-area YBCO films on sapphire for microwave applications," *IEEE Trans. Appl. Supercond.*, vol. 9, no. 2, pp. 2486–2491, Jun. 1999.

- [11] E. Hollmann, O. Vendik, A. Zaitsev, and B. Melekh, "Substrates for high- $T_c$  superconductor microwave integrated circuits," *Superconductor Sci. Technol.*, vol. 7, no. 9, pp. 609–622, 1994.

- [12] S. A. Cybart *et al.*, "Nano Josephson superconducting tunnel junctions in  $\text{YBa}_2\text{Cu}_3\text{O}_{7-\delta}$  directly patterned with a focused helium ion beam," *Nature Nanotechnol.*, vol. 10, no. 7, pp. 598–602, 2015.

- [13] E. Y. Cho, H. Li, J. C. LeFebvre, Y. W. Zhou, R. Dynes, and S. A. Cybart, "Direct-coupled micro-magnetometer with Y-Ba-Cu-O nano-slit SQUID fabricated with a focused helium ion beam," *Appl. Phys. Lett.*, vol. 113, no. 16, 2018, Art. no. 162602.

- [14] E. Y. Cho, Y. W. Zhou, J. Y. Cho, and S. A. Cybart, "Superconducting nano Josephson junctions patterned with a focused helium ion beam," *Appl. Phys. Lett.*, vol. 113, no. 2, 2018, Art. no. 022604.