# CAS-Lock: A Security-Corruptibility Trade-off Resilient Logic Locking Scheme

Bicky Shakya<sup>1\*</sup>, Xiaolin Xu<sup>2\*</sup>, Mark Tehranipoor<sup>1</sup> and Domenic Forte<sup>1</sup>

<sup>1</sup> ECE Department, University of Florida bshakya@ufl.edu, {tehranipoor, dforte}@ece.ufl.edu <sup>2</sup> ECE Department, University of Illinois at Chicago xiaolin8@uic.edu

**Abstract.** Logic locking has recently been proposed as a solution for protecting gatelevel semiconductor intellectual property (IP). However, numerous attacks have been mounted on this technique, which either compromise the locking key or restore the original circuit functionality. SAT attacks leverage golden IC information to rule out all incorrect key classes, while bypass and removal attacks exploit the limited output corruptibility and/or structural traces of SAT-resistant locking schemes. In this paper, we propose a new lightweight locking technique: CAS-Lock (cascaded locking) which nullifies both SAT and bypass attacks, while simultaneously maintaining nontrivial output corruptibility. This property of CAS-Lock is in stark contrast to the well-accepted notion that there is an inherent trade-off between output corruptibility and SAT resistance. We theoretically and experimentally validate the SAT resistance of CAS-Lock, and show that it reduces the attack to brute-force, regardless of its construction. Further, we evaluate its resistance to recently proposed approximate SAT attacks (i.e., AppSAT). We also propose a modified version of CAS-Lock (mirrored CAS-Lock or M-CAS) to protect against removal attacks. M-CAS allows a trade-off evaluation between removal attack and SAT attack resiliency, while incurring minimal area overhead. We also show how M-CAS parameters such as the implemented Boolean function and selected key can be tuned by the designer so that a desired level of protection against all known attacks can be achieved.

Keywords: Logic locking; SAT attack

# 1 Introduction

Globalization of the semiconductor industry has led to the outsourcing of integrated circuit (IC) fabrication to untrusted, off-shore foundries. As a result, semiconductor companies as well as government agencies are now facing threats of IP piracy, counterfeiting, and overproduction [1]. Therefore, new techniques are required for combating these issues of untrusted foundries. Towards this end, logic locking has emerged as a promising solution. A majority of logic locking schemes insert extra key-gates into the netlist of the circuit design. The locked circuit works correctly only when the correct key is provided. However, recent work has shown that most of these locking techniques are vulnerable to Boolean satisfiability (SAT) based attacks [2]. In SAT attack, a set of distinguishing input patterns (DIPs) are collected from the locked circuit to rule out incorrect keys that do not satisfy the DIPs and the corresponding known-good responses from an unlocked IC. In order to mitigate SAT attacks, several SAT-resistant countermeasures have been proposed [3] [4], which aim to limit the ability of the attack to rule out wrong keys, given the golden

<sup>\*</sup>These authors contributed equally to this work.

observations. However, they have been proven to be vulnerable to bypass attacks [5], which exploit the low corruptibility of these locking schemes. In the bypass attack, functionality of the locked circuit can be fully restored with a linear-sized bypass circuitry. This avoids the difficulty of recovering the correct key and allows the circuit to operate in a functionally correct manner even in the presence of an incorrect key.

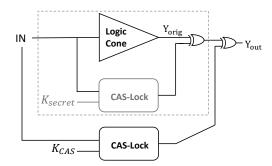

To mitigate the threats from bypass attack and at the same time, ensure robustness against SAT attack, we propose a new logic locking technique: CAS-Lock (Cascaded Locking). In CAS-Lock, a logic block comprising of a cascade of key controlled AND/OR gates is stitched into the original circuit. The block exponentially increases the complexity of SAT attacks while simultaneously allowing the locked design to maintain non-trivial output corruptibility for defeating bypass attacks. Note that this property contradicts the results from recent literature, which show an unavoidable trade-off between output corruptibility and SAT resistance. Specifically, we show that the CAS-Lock scheme is the only locking technique proposed so far that can ensure SAT resistance with non-trivial output corruptibility, and can remain secure under a black-box attack model, where the attacker aims to recover the key using input-output observations. Our main contributions in this paper can be summarized as follows:

- We adopt the merits of two SAT-resistant techniques: SARLock [3] and Anti-SAT [4], and propose a more secure countermeasure CAS-Lock which is simultaneously resistant against SAT and bypass attacks.

- We provide a proof to show that breaking CAS-Lock with SAT attack requires, at a minimum, brute force through the entire input space of the circuit. We also show that its non-trivial and tunable output corruptibility leads to high overheads for bypass attack and incomplete bypass pattern extraction, as well as resistance against approximate SAT (AppSAT) attacks. The newly proposed countermeasure is also lightweight, as its overhead is only dependent on the number of inputs used.

- We also propose an extension to CAS-Lock (termed Mirrored-CAS or 'M-CAS') to protect against removal attacks from white-box adversaries such as untrusted foundries. We show that some trade-offs exist in this regard: strong resiliency to removal (through increased output corruptibility) leads to reduced SAT resistance (and vice-versa). We compare M-CAS to a recently proposed stripped functionality logic locking (SFLL) technique [6] and show that it achieves similar SAT and bypass resistance at reduced area overheads.

The rest of the paper is organized as follows. Section 2 reviews the background on logic locking, attacks on logic locking, and several recent countermeasures. Section 3 introduces CAS-Lock and its security properties. It also provides a series of proofs to show the SAT attack resiliency against CAS-Lock. Section 4 describes a modified version of CAS-Lock (M-CAS) that is required for preventing removal attacks. Section 5 provides a comparison of CAS-Lock and M-CAS with other pre-existing logic locking techniques. Finally, Section 6 concludes the paper.

# 2 Background and Related Work

Logic locking (also referred to as logic encryption) locks a logic circuit by adding keycontrolled gates, and correct functionality of the circuit is ensured only when the correct key is applied. An incorrect key leads to corrupted outputs, thereby preventing unauthorized parties from making use of the locked circuit. In the case of an untrusted foundry, the locking prevents them from engaging in overproduction or IC piracy. Note that logic locking usually assumes that there is one master key per design, and the security of the design is dependent on this single key. This is because there is only one mask set per design, from which many chips can be produced. However, there may be unique per-chip keys related to public key protocols, that are used in conjunction with the master key to unlock the design [7]. In this paper, we are mainly concerned with the master key that is used to implement the gate-level locking mechanism.

In recent years, several techniques have been proposed to perform logic locking, based on the position and impact of the inserted key gate logic; this includes techniques such as random insertion [8] and fault analysis-based key gate insertion [9]. Unfortunately, all these approaches have been shown to be vulnerable to SAT attacks [2].

# 2.1 SAT Attacks on Logic Locking

In SAT attacks [2], the threat model is as follows: an attacker is assumed to have access to: 1) A locked netlist: This can be either obtained from a malicious foundry or through reverse-engineering a chip from the open market [10]. The netlist can be simulated to derive the outputs for given inputs. 2) Unlocked IC: An unlocked 'golden' IC can be purchased from the open market or obtained through a malicious insider in the design house. Such a chip can be used by the attacker to check whether the output for a given key from the locked netlist is correct, i.e., he/she can perform chip-level functional/structural tests to obtain golden responses. The goal of the attacker is to find the correct key by inquiring the least number of input patterns from the unlocked IC. Note that only combinational circuits (or sequential circuits with scan capabilities) are considered in such attacks [2].

Using the same threat model, test-based attacks have been developed, which use automatic test pattern generation (ATPG) techniques [11] to generate a set of inputs that can propagate the correct key to observable outputs in the circuit. The problem of finding the correct key is modeled after the problem of generating patterns to detect stuck-at faults in a circuit [12]. In SAT-based attacks, such propagations are not required. Instead, the attacker constructs a 'miter circuit' with two copies of the locked netlist, which are loaded with two different wrong keys, respectively. The miter helps in finding a set of distinguishing input patterns (DIPs) for which the two circuits produce different outputs; since the outputs are different, it is assured that at least one of the keys chosen for the miter are wrong. Since the unlocked IC is available to the attacker, she can then apply this DIP to the unlocked IC and decide which of the keys is incorrect. Further, the known good input-output pair is also added as an additional constraint to the key formulation. The algorithm then iteratively uses these DIPs (and the added constraints) to guide a SAT solver to a correct key value, by ruling out all incorrect key classes. The algorithm terminates when no more DIPs can be found and as a result, the remaining key(s) is guaranteed to be the functionally correct key(s). The results in [2] show that the algorithm converges in a short time, when applied on a variety of logic locked circuits.

# 2.2 SAT-Resistant Logic Locking

Various SAT-resistant techniques have been recently developed, most notably SARlock [3] and Anti-SAT [4], to counter SAT attacks. Both of these techniques attach additional logic to the circuit in order to reduce the ability of the DIPs to rule out wrong keys. In other words, the attack is only able to rule out a negligible amount of the entire key space in a single attack iteration, forcing it to take an exponential time to find the correct key.

#### 2.2.1 SARLock

SARLock ensures that at most one incorrect key is ruled out by each DIP [3]. This is realized with a comparator circuit that inverts the circuit output for only one input pattern for a wrong key. Thus, the SAT attack algorithm is forced to observe at least  $2^N$  DIPs (where N is the number of inputs used for the SARLock logic) to rule out all incorrect key

classes. While SARLock renders SAT attack ineffective, it cannot protect against attacks exploiting gate-level structural traces. In *removal attack*, an attacker can analyze the netlist and then identify and remove the SARLock gates from the design. The removal attack is feasible since the SARLock logic has an extremely low signal probability on its output, which makes it distinct from other gates in the netlist. To counter such vulnerabilities, the authors in [3] proposed a hybrid logic-locking mechanism: SARLock + strong logic locking (SLL)[12]. This hybrid technique combines SARLock with regular logic locking (i.e., insertion of XOR/XNOR/MUX key-gates into the netlist), and also combines the two keys (SARLock key and SLL key) using permutations.

#### 2.2.2 Anti-SAT

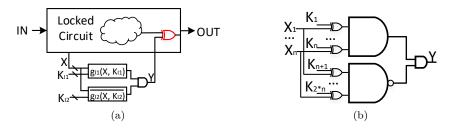

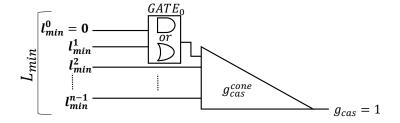

Anti-SAT is another locking technique proposed to counter SAT attacks [4][13]. The Anti-SAT block is illustrated in Figure 1, which is composed of the logic blocks  $B_1 = g_{l1}(X, K^{l1})$ and  $B_2 = \overline{g_{l2}(X, K^{l2})}$ . The blocks share a common input X but are locked by two different keys  $K^{l1}$  and  $K^{l2}$ . Circuit integration is done by stitching the Anti-SAT output Y to a high observability net in the design (e.g., the primary output). The two blocks  $g_{l1}$  and  $\overline{g_{l2}}$  are designed to be complementary in nature. They can also be denoted by g and  $\bar{g}$ . The output signal Y is generated by the logical AND of  $B_1$  and  $B_2$ . Similar to SARLock, a wrong key applied on Anti-SAT will enable Y = 1 for some input pattern(s), and flip the correct outputs. Assuming the Boolean function g has N inputs, the number of input patterns that make g evaluate to "1" is denoted as p. The authors in [4] prove that the ability of the SAT attack to obtain the correct Anti-SAT key is greatly limited if p is sufficiently close to 1 (or  $2^N - 1$ ); this choice of Anti-SAT logic, along with choosing the primary inputs as inputs to the Anti-SAT block, is termed as 'secure integration'. An Anti-SAT block satisfying p=1 forces the conventional SAT attack to enumerate the largest number of possible input patterns to reveal the correct ones. They also note that natural candidates for q and  $\bar{q}$  that satisfy p=1 can be AND and NAND, respectively. 'Random integration' is also proposed, where random internal signals of the circuit (instead of the primary inputs) are used as inputs to the Anti-SAT block. The usage of 'Random integration' offers increased output corruptibility, albeit at reduced SAT resistance, as not all input pattern combinations are possible at the input of the Anti-SAT block.

Figure 1: (a) Integration of Anti-SAT into a circuit. (b) Anti-SAT implemented with AND and NAND gates.

#### 2.2.3 Removal Attack on Anti-SAT

Although the Anti-SAT block can be integrated in the whole netlist, it has been shown that an attacker can still identify the flip signal Y generated by the Anti-SAT block. This is accomplished by analyzing the signal probability skew (SPS) of the g and  $\bar{g}$  blocks in the circuit [14]. In an SPS-based attack, the attacker computes the static probabilities (P) and skew (s=P-0.5) of all the gates in the design. Due to the complementary construction between g and  $\bar{g}$ , the Y signal in the Anti-SAT block demonstrates the highest

absolute difference in signal skew (ADS), i.e.,  $ADS(Y) = |s(g) - s(\bar{g})|$ , of all the gates in the design. As a result, the attacker could identify the AND gate with the Y signal and remove all the gates in the transitive-fanin cone of this net. This would effectively remove the entire Anti-SAT logic from the design. Additionally, the attacker could also set the flip signal of the Anti-SAT block to 0 and then apply the conventional SAT attack if there are additional key gates (e.g., XOR/XNOR) in the design.

#### 2.2.4 AppSAT

A modified version of the original SAT attack ('AppSAT') that approximately de-obfuscates a locked circuit was proposed in [15]. The motivation behind AppSAT is that hybrid obfuscation schemes (e.g., SARLock + SLL) cause the original SAT attack algorithm to get stuck in resolving the point function  $^1$  (e.g., AntiSAT/SARLock). This leads to an exponential number of iterations for the attack to rule out all incorrect keys. AppSAT, on the other hand, forces the original SAT algorithm to terminate early, when the error rate (i.e., number of patterns that are incorrect among a sampling of input-output patterns, calculated periodically between iterations) settles below a given threshold. Further, multiple distinguishing input patterns and their correct outputs are added as constraints in a single iteration. Therefore, given a sufficient number of iterations/DIPs, AppSAT is able to resolve the correct XOR/XNOR keys while not being impeded by the point function. Therefore, the error rate of the key resolved by AppSAT is claimed to be approximately  $2^{-n}$ .

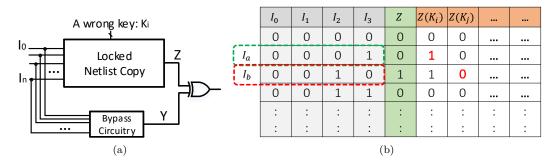

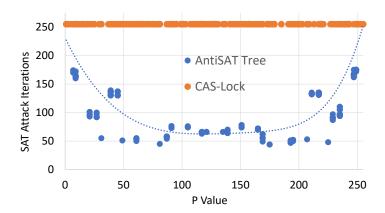

#### 2.2.5 Bypass Attack

Bypass attack was proposed to exploit the low corruptibility of SAT resistant logic locking schemes such as SAR-Lock and Anti-SAT [5]. In this technique, a miter is formed between two copies of the circuit locked with two different wrong keys, in the same way as SAT attacks. After this, the set of input patterns whose outputs disagree with each other (i.e., distinguishing input pattern) are collected. These patterns are used to create a bypass circuitry, which is then stitched back into the locked circuit, as shown in Figure 2. As these limited set of input patterns are the only ones on which the circuit is corrupted, the bypass circuitry corrects these errors on the original circuit and restores the circuit's functionality. The effectiveness of bypass attack is mainly dependent on the ability of the miter circuit to find the DIPs, as well as the corruptibility of the SAT resistant scheme. Lower corruptibility implies smaller bypass attack overhead, whereas high corruptibility forces the attacker to create a large bypass circuit, which might not be feasible. For example, there exists only one DIP for every wrong key in 'secure integration' Anti-SAT, leading to a bypass circuit that only has to correct for one wrong input pattern. On the other hand, 'random integration' Anti-SAT ensures a large number of DIPs per wrong key but renders drastically reduced SAT resistance.

#### 2.2.6 Stripped Functionality Logic Locking (SFLL)

Stripped functionality logic locking (SFLL) is an approach that has been proposed to combat SAT, bypass, and removal attacks [6]. In this approach, select logic cones of the original design are modified, such that they are corrupted on a pre-defined set of input patterns. A logic block is then stitched into the design (in a fashion similar to Anti-SAT or SARLock), which corrects the errors in the original design once the correct key is provided. The assumption is that even if the logic block that provides SAT resistance is removed, the design is still non-functional. This is because the block is also required to correct the injected errors in the design. A suggested choice for the logic block is a

$<sup>^1\</sup>mathrm{A}$  point function is a function which evaluates to 1 at a particular input, and 0 elsewhere

Figure 2: (a) shows that for a locked netlist, a bypass circuit can be inserted to detect the DIP for the wrong key  $K_i$ . (b) shows an example truth table for finding the two DIPs with two wrong keys  $K_i$  and  $K_j$  for SARLock and Anti-SAT (Secure Integration).

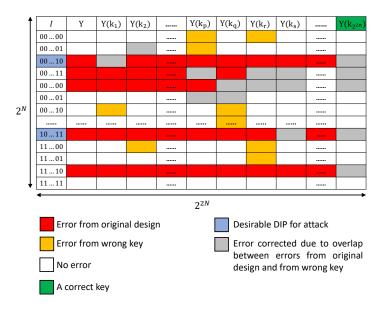

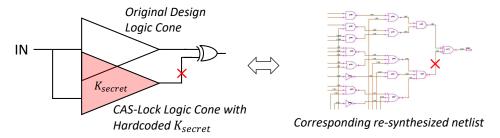

hamming distance(HD)-based comparator, which computes the HD between the input and the key and corrupts/corrects the circuit output if the HD is equal to a publicly known parameter h. An overhead improvement to SFLL, that uses fault injection and failing pattern detection to modify the original circuit, is proposed in [16]. A functional attack on SFLL ('FALL') has been recently proposed in [17], where the logic that corrupts the original design (which is also a HD comparator) is identified. After identification, the hard-coded key value in the netlist, which drives the comparator and is supposed to be hidden after re-synthesis, is extracted. The key is decoded by specifically exploiting the logical properties of the HD comparator block, such as non-overlapping errors between two input pairs. Results showed that as much as 81% of SFLL locked combinational benchmark circuits could be decoded using FALL attack.

#### 2.3 Other Countermeasures and Attacks

Yasin et al. have proposed to use one-way functions (such as AES) for combating SAT attacks [18]. However, as the cipher and the original circuit are functionally and structurally independent, it becomes trivial for the attacker to identify and circumvent the AES block. To prevent similar vulnerabilities, Xie et al. proposed structural obfuscation techniques to secure the Anti-SAT block against removal [4]. This is done by adding MUX/XOR key gates into the design, so that the original circuit and the Anti-SAT block are entangled with each other and structural traces are removed. Some approaches have also been proposed to restrict or prevent scan access to a circuit, so that SAT attacks can be rendered infeasible in the first place [19]. However, these approaches follow a weaker security notion i.e., they consider a much weaker adversary who cannot access the scan chain. Further, there is no formal treatment of the security of such approaches. Logic locking based on re-use of DFT test points has also been proposed [20]. Unfortunately, no concrete security evaluation (in terms of SAT and/or structural attacks) has been provided for such approaches. The work in [21] proposes a locking mechanism based on the insertion of routing blocks that are inherently hard for SAT solvers, similar to [18]. However, the technique makes use of lookup tables (LUTs), which are not compatible with ASIC designs and are high in overhead. All locking approaches proposed so far also assume the secrecy of the key, and do not take into account attacks such as invasive/direct probing of the key (e.g., as they are being loaded from memory, or directly from fuses). Such attacks require their own set of countermeasures, and are beyond the scope of this paper.

# 3 CAS-Lock

## 3.1 Requirements for Attack-Resilient Logic Locking

Based on the numerous attacks discussed above, it can be concluded that any single countermeasure against a certain attack is not secure enough. Therefore, to comprehensively protect the locked circuit, all the aforementioned attacks need to be considered in unison to formulate a new secure logic locking scheme.

In [4], Xie et al. thoroughly evaluated the security of the Anti-SAT block when changing the p value (output-one count) of the  $g/\bar{g}$  function from 1 to  $2^N$ , where N is the number of inputs used in the Anti-SAT block. It was found that by changing more AND gates of the  $g/\bar{g}$  function in the AND-tree structure to OR gates (or conversely, changing more of the OR gates in the OR-tree structure to AND gates) decreased the resiliency to SAT attacks. However, we've found that for certain structures of the AND/NAND tree, it is still possible to maximize SAT attack resistance (i.e., reduce it to brute force) even when  $p \neq 1$  or  $p \neq 2^N - 1$ .

Before discussing these structures, we outline some requirements for an ideal Anti-SAT block.

- (1) **Lightweight**: The overhead (i.e., the number of gates in Anti-SAT) should be a linear function of the number of circuit inputs [4]. Otherwise, if the overhead increases exponentially with the number of inputs used or is large, it would not be a feasible solution for industry to adopt.

- (2) Strong resilience against bypass attack: There are two scenarios that can limit the successful application of bypass attack: (a) The hardware overhead of the bypass circuitry is prohibitively high; or (b) The number of output errors across all possible input patterns for a wrong key is random, undetectable and hard to calculate as N scales. For example, the baseline Anti-SAT (with p=1) was always incorrect on only one unique input pattern for a given wrong key, which made it easily defeated by bypass attack [5].

- (3) Strong resilience against SAT-based attacks: The attacker should be forced to iterate through a very large number of input patterns to discover the correct key(s) (i.e., near brute force<sup>2</sup>).

- (4) **Resistance to removal attacks**: It should be difficult for the attacker to use structural information to isolate and remove the Anti-SAT block from the locked netlist (e.g., by using the signal probability skew attack proposed in [14]).

As was shown in [5], there exists a trade-off between SAT and bypass attack resistance. This is because a countermeasure is most robust against SAT attack if the number of wrong keys that can be ruled out by each distinguishing input pattern is minimized. Conversely, such low corruptibility facilitates bypass attack. To mitigate both these attacks with one single countermeasure, we propose a more general constraint and rewrite requirements (2) and (3) as: For any input pattern  $X_i$ , there exists at least one wrong key  $WK^i$  that can only be ruled out by this input pattern, and the number of corrupted outputs for a given wrong key is neither constant nor unique across all possible keys. The first half of the new constraint implies that there should exist unique wrong key(s) for any input pattern. Therefore, to rule out all possible wrong keys, the attacker is forced to iterate through all possible input patterns. The second half of the constraint relates to bypass attack difficulty. If the circuit is incorrect on a random (and large) number

<sup>&</sup>lt;sup>2</sup>If the no. of inputs used is N, the number of input-output observations needed to prune all wrong keys is  $2^N$ .

of input patterns for any given wrong key, the bypass overhead can be unpredictable (and large). Further, if the output errors are not unique across different wrong keys, it becomes hard to detect and correct all of them.

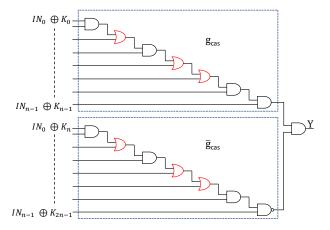

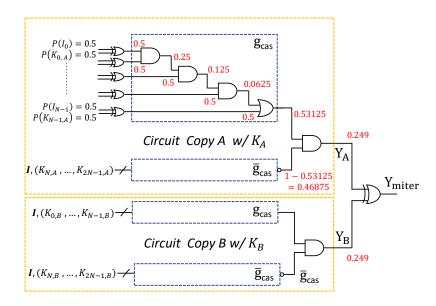

## 3.2 CAS-Lock Analysis

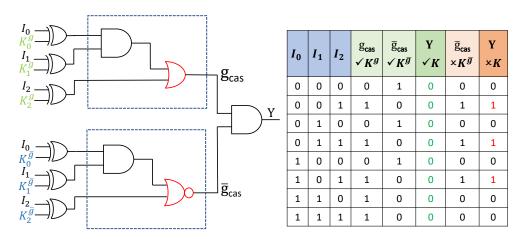

To fulfill these requirements, we propose a new countermeasure called CAS-Lock, which is shown in Figure 3. It can be seen that CAS-Lock adopts a structure similar to Anti-SAT, where the outputs of two complementary Boolean functions  $g_{cas}$  and  $\bar{g}_{cas}$  are ANDed together to produce the output (Y). The difference lies in the structure of the logic gates implementing g and  $\bar{g}$ , where instead of a tree structure, we adopt a daisy-chained or cascaded structure for the AND/OR gates.

Figure 3: One possible instantiation of CAS-Lock (Note that g and  $\bar{g}$  are still symmetric and complementary.)

It can be noted that for input length N, the gate count of CAS-Lock is the same as that of Anti-SAT i.e.,  $\approx 2 \cdot (N-1)$ . This satisfies **Requirement (1)** listed above (i.e., the overhead increases linearly with input size). Requirement (2), which relates to bypass attack resistance, is ensured as the number of unique wrong keys is controllable by changing the location and number of OR/AND gates in  $g_{cas}$  and  $\bar{g}_{cas}$ . Further, the number and location of incorrect input/output patterns for a given wrong key can only be resolved by brute force (i.e., by evaluating the CAS-Lock structure for all possible patterns or by iterative SAT solving). This becomes prohibitive for large N. Requirement (3) is fulfilled as CAS-Lock ensures the existence of at least one unique wrong key for every possible input pattern. A proof of this property, along with some precursor lemmas, is given below. For the proof, we show the existence of  $2^N$  wrong keys, each of which can only be eliminated by a unique DIP. More importantly, we show that regardless of the output-one count (p) of  $g_{cas}$ , such keys always exist in CAS-Lock (Lemma 1). This is due to its logical behavior, whereby a certain number of input patterns cause  $g_{cas}$  to output logic 1 and  $\bar{g}_{cas}$  to output logic 0 (Lemma 2). Since there are an odd number of such patterns (shown by Lemma 3),  $g_{cas}$  and  $\bar{g}_{cas}$  both evaluate to 1 (and thus, produce an incorrect output) only on one unique input pattern when one of the  $2^N$  wrong keys is applied. Note that requirement (4), i.e., resistance to removal attack, will be considered in Section 3.5.

Following the notation in [4], we denote the n-bit inputs to the CAS-Lock component with  $\mathbf{X}$  and the 2n-bit key with  $\mathbf{K}$ .  $|\mathbf{X}|$  refers to the size of the inputs used in CAS-Lock, and  $|\mathbf{K}|$  refers to the key size of 2n. Similar to [13],  $\mathbf{X}$  is assumed to be directly connected

to the primary inputs  $IN^3$ . We also define  $L = X \oplus K$ , i.e., XOR or XNOR of the inputs with the key, as shown in Figure 1.

**Lemma 1.** Given the countermeasure built with Boolean functions  $g_{cas}$  and  $\bar{g}_{cas}$ , there exists  $2^N$  wrong keys, each of which can only be ruled out by a unique input pattern  $X_i$ . Thus, to rule out all the wrong keys, the attacker has to iterate through all possible  $2^N$  input patterns (i.e., brute force through the entire input space).

*Proof.* Lemma 1 is true if we can find at least one unique wrong key that can only be ruled out by a specific input pattern  $X_i$ .

Based on the design scheme of CAS-Lock, we denote a correct 2n-bit key as  $\mathbf{K} = \langle CK_i^1, CK_i^2 \rangle$ , where  $CK_i^1$  and  $CK_i^2$  are fed into Boolean functions  $g_{cas}$  and  $\bar{g}_{cas}$ , respectively. Then, for any input pattern  $X_i$ , we have:

$$Y_i = g_{cas}(X_i \oplus CK_i^1) \land \bar{g}_{cas}(X_i \oplus CK_i^2) = 0 \tag{1}$$

Therefore, for the correct key, the output  $Y_i$  of the AntiSAT block is **always zero** and the circuit output is never inverted.

|             |          | L                  | g <sub>cas</sub> (L) | $\bar{g}_{cas}(L)$ |

|-------------|----------|--------------------|----------------------|--------------------|

|             | $L_0$    | 0000000            | 0                    | 1                  |

|             | $L_1$    | 0000001            | 0                    | 1                  |

|             | $L_2$    | 0000010            | 0                    | 1                  |

|             | _        |                    | 0                    | 1                  |

|             |          | ${ m L}_{\sf min}$ | 1                    | 0                  |

| N - min = p |          |                    | 1                    | 0                  |

| ı           | <b>│</b> | 1111110            | 1                    | 0                  |

|             | $L_N$    | 1111111            | 1                    | 0                  |

Figure 4: A truth table for  $g_{cas}$  and  $\bar{g}_{cas}$ , where  $L_{min}$  stands for the smallest input pattern that makes the Boolean function  $g_{cas}$  equal to 1.

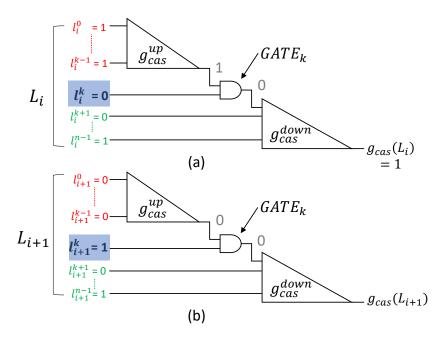

As shown in Figure 4, there always exists the smallest input pattern  $L_{min}$  where, for  $\forall L_i < L_{min}$ , we have  $g_{cas}(L_i) = 0^4$ . In other words, if we count the input patterns incrementally from  $0000 \dots 000$  to  $1111 \dots 111$  and observe the corresponding output of function  $g_{cas}$ ,  $L_{min}$  is the smallest input pattern that makes  $g_{cas} = 1$ . For example, if  $g_{cas}$  is built with all AND gates, then  $L_{min} = 1111 \dots 111$ . Thus, we now have the expression in Eqn. 2, where  $(L_{min} - 1) \oplus 1 = L_{min}$ . These two scenarios are highlighted in green in Figure 5(a), where the output  $Y_i$  is always zero.

$$g_{cas}(L_{min}) = \bar{g}_{cas}(L_{min} - 1) = 1$$

$$\bar{g}_{cas}(L_{min}) = g_{cas}(L_{min} - 1) = 0$$

(2)

Now, let us assume a wrong key  $WK_j = \langle WK_j^1, WK_j^2 \rangle$  that satisfies Eqn. 3.

$$WK_{j}^{1} \oplus CK_{i}^{1} = 000...00$$

$WK_{j}^{2} \oplus CK_{i}^{2} = 000...01$  (3)

<sup>&</sup>lt;sup>3</sup>**X** could also be connected to random internal wires instead of **IN**. However, this reduces SAT resistance, as shown in [4] and as such, is not considered.

<sup>&</sup>lt;sup>4</sup>This is proven in Lemma 2

$<sup>^5{\</sup>rm This}$  is proven in Lemma 3

| (2)                      |                                  |                               |                                        |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                    |                                         |

|--------------------------|----------------------------------|-------------------------------|----------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------|

| (a)                      | $X_i$                            | $X_i \oplus CK_i^1$           | $X_i \oplus CK_i^2$                    | $g_{cas}(X_i \oplus CK_i^1)$   | $\bar{\mathbf{g}}_{cas}(X_i \oplus \mathcal{C}K_i^2)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $Y_i$                              |                                         |

|                          | 0000000                          | 0000000                       | 0000000                                | 0                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                  |                                         |

|                          | 0000001                          | 0000001                       | 0000001                                | 0                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                  |                                         |

|                          |                                  |                               |                                        | 0                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                  |                                         |

| $L_{min} - 1$            | 0                                | 0                             | 0                                      | 0                              | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                  |                                         |

| $ m L_{min}$             | 1                                | 1                             | 1                                      | 1                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                  |                                         |

|                          |                                  |                               |                                        | 1                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                  |                                         |

|                          | 1111110                          | 1111110                       | 1111110                                | 1                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                  |                                         |

|                          | 1111111                          | 1111111                       | 1111111                                | 1                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                  |                                         |

|                          |                                  |                               |                                        |                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                    |                                         |

|                          |                                  |                               |                                        |                                | $X_i$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ⊕ W<br>⊕ CI                        | $K_j^2 = K_i^2 \oplus 000 \dots 001$    |