OPEN

# Ferroelectric Tunneling Junctions Based on Aluminum Oxide/Zirconium-Doped Hafnium Oxide for Neuromorphic Computing

Hojoon Ryu<sup>1</sup>, Haonan Wu<sup>1</sup>, Fubo Rao<sup>2</sup> & Wenjuan Zhu<sup>1\*</sup>

Ferroelectric tunneling junctions (FTJs) with tunable tunneling electroresistance (TER) are promising for many emerging applications, including non-volatile memories and neurosynaptic computing. One of the key challenges in FTJs is the balance between the polarization value and the tunneling current. In order to achieve a sizable on-current, the thickness of the ferroelectric layer needs to be scaled down below 5 nm. However, the polarization in these ultra-thin ferroelectric layers is very small, which leads to a low tunneling electroresistance (TER) ratio. In this paper, we propose and demonstrate a new type of FTJ based on metal/Al<sub>2</sub>O<sub>3</sub>/Zr-doped HfO<sub>2</sub>/Si structure. The interfacial Al<sub>2</sub>O<sub>3</sub> layer and silicon substrate enable sizable TERs even when the thickness of Zr-doped HfO<sub>2</sub> (HZO) is above 10 nm. We found that F-N tunneling dominates at read voltages and that the polarization switching in HZO can alter the effective tunneling barrier height and tune the tunneling resistance. The FTJ synapses based on Al<sub>2</sub>O<sub>3</sub>/HZO stacks show symmetric potentiation/depression characteristics and widely tunable conductance. We also show that spike-timing-dependent plasticity (STDP) can be harnessed from HZO based FTJs. These novel FTJs will have high potential in non-volatile memories and neural network applications.

Recently, brain-inspired computing, or neuromorphic computing, has garnered intense research attention. Neuromorphic computing aims to realize electronic systems that emulate the computational energy-efficiency and fault tolerance of the biological brain in a compact space<sup>1–3</sup>. Traditional computing systems based on von Neumann architecture have severe limitations in energy consumption, deep-learning capability and scalability to large networks<sup>4,5</sup>. In contrast, the human brain is capable of performing much more intelligent functions and yet consumes much less power and occupies less space<sup>3</sup>. To bridge this gap, researchers are actively investigating the possibilities to construct electronic systems emulating the neuronal organization and function of nervous systems. In the past, a broad spectrum of devices with programmable conductance, such as phase change memories and resistive change memories, have been explored as potential synaptic devices<sup>1,6–11</sup>. As compared to these candidates, the ferroelectric-based synaptic devices have several advantages including high symmetry in potentiation/depression operations and fast response, which are important traits for data processing and on-chip learning<sup>12–16</sup>. In this paper, we investigate ferroelectric tunneling junctions (FTJs) as the synaptic devices for neuromorphic computing.

FTJ is a two-terminal device composed of a thin ferroelectric layer sandwiched in between two electrodes. The tunneling resistance in an FTJ can be switched between a high and a low value by the reversal of the polarization in the ferroelectric material. Traditionally, the FTJs are mainly based on perovskites, such as Barium titanate (BaTiO<sub>3</sub>) and lead zirconate titanate (PZT)<sup>17,18</sup>. However, these materials are incompatible with CMOS processes, and their thickness is not easily scaled. Recently, it was discovered that doped hafnium oxide (HfO<sub>2</sub>) has strong ferroelectricity<sup>19–28</sup>. As compared to traditional perovskites, doped HfO<sub>2</sub> has many advantages, including excellent scalability and full compatibility with CMOS processes<sup>28–31</sup>. Among various doped HfO<sub>2</sub>, Zr-doped HfO<sub>2</sub> (HZO) is particularly attractive due to its low annealing temperature and excellent scalability<sup>25,31–34</sup>. In FTJs based on metal/HZO/metal structure, in order to achieve a sizable on-current, the thickness of HZO needs to be scaled down below 5 nm<sup>35,36</sup>. However, the polarization in these ultra-thin HZO films is very small, which leads to a

<sup>1</sup>Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana, IL, 61801, USA. <sup>2</sup>Materials Research Laboratory, University of Illinois at Urbana-Champaign, Urbana, IL, 61801, USA. \*email: [wjzhu@illinois.edu](mailto:wjzhu@illinois.edu)

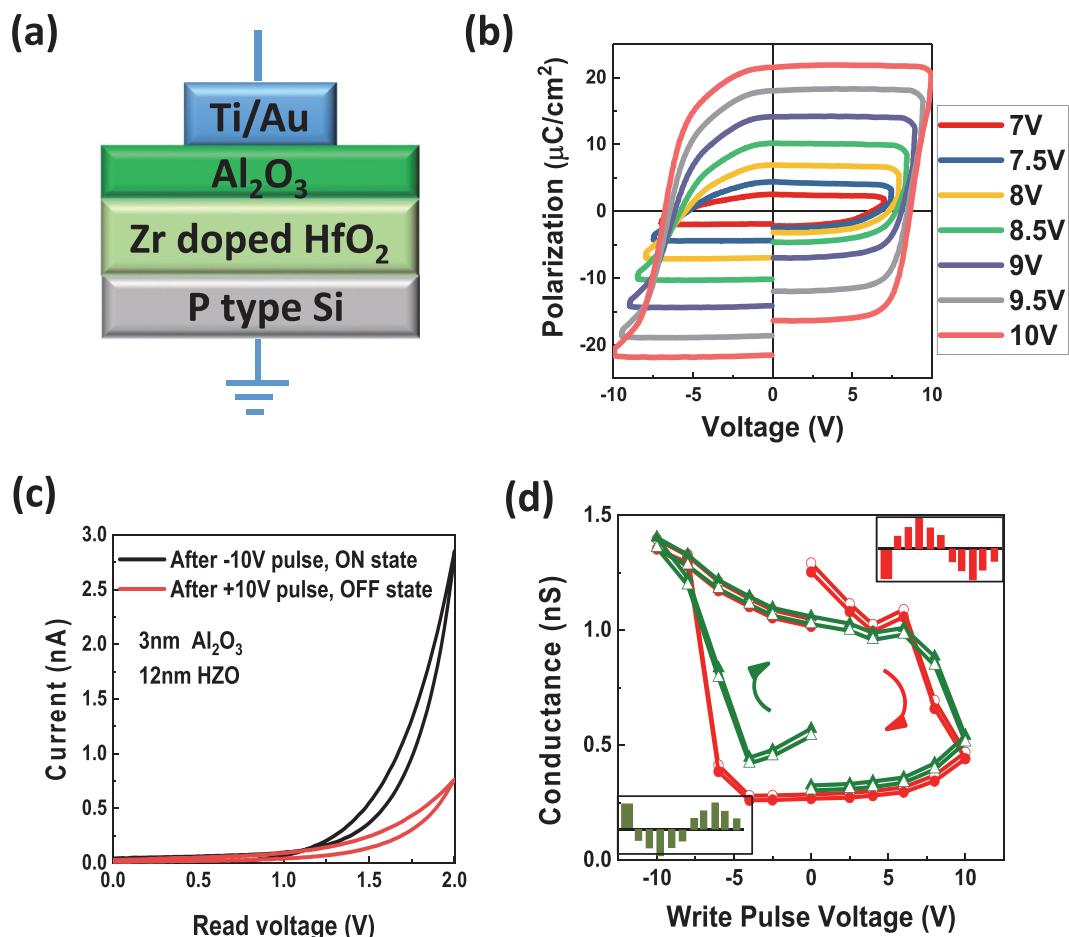

**Figure 1.** Polarization and hysteresis loop in FTJs based on Ti/Al<sub>2</sub>O<sub>3</sub>/HZO/p-Si. (a) Illustration of FTJs based on Al<sub>2</sub>O<sub>3</sub>/HZO/Si. (b) Polarization-Voltage (P-V) loops of an FTJ with 3 nm Al<sub>2</sub>O<sub>3</sub>/12 nm HZO. (c) The DC IV curves of the FTJs measured after  $-10$  V and  $+10$  V program pulses. (d) Hysteresis loops of the tunneling conductance of FTJs based on Ti/Al<sub>2</sub>O<sub>3</sub>/HZO/p-Si at  $2$  V read voltage. The pulse trains are shown schematically in the insets. The red conductance lines correspond to the red pulse sequence shown in the upper right corner, while the green conductance lines correspond to the green pulse sequence shown in the lower left corner. The orange circle between two pulses means dc IV measurement for reading the conductance of the FTJ. The solid symbols are the conductance taken from the forward dc IV sweep ( $0$  V to  $2$  V), while the open symbols are the conductance taken from the backward dc IV sweep ( $2$  V to  $0$  V).

low TER ratio<sup>37</sup>. In this project, we propose and demonstrate a new type of FTJ based on metal/Al<sub>2</sub>O<sub>3</sub>/HZO/Si structure. The interfacial Al<sub>2</sub>O<sub>3</sub> layer and semiconducting substrate enable sizable TERs even when the thickness of HZO is above  $10$  nm. We demonstrate FTJ synapses with symmetric potentiation/depression characteristics and widely tunable conductance. We also show that spike-timing-dependent plasticity (STDP) can be harnessed from HZO based FTJs.

## Results and Discussion

The FTJs based on Al<sub>2</sub>O<sub>3</sub>/HZO stacks were fabricated on highly-doped Si substrates using atomic layer deposition (ALD). The device structure is illustrated in Fig. 1a. We alternately stacked HfO<sub>2</sub> and ZrO<sub>2</sub> layers by using the Hf precursor [tetrakis(dimethylamido)hafnium] and Zr precursor [tetrakis(dimethylamido)zirconium]. Then, we deposited Al<sub>2</sub>O<sub>3</sub> by using Al precursor [trimethylaluminium]. The encapsulated HZO films were then annealed in a rapid thermal annealing (RTA) system. Ti/Au electrodes ( $10/40$  nm) were deposited by e-beam evaporation. The polarization of the doped HfO<sub>2</sub> is measured using the positive-up-negative-down (PUND) method. The polarization-voltage (P-V) loops are shown in Fig. 1b. The remanent polarization in the FTJs can reach  $21$  μC/cm<sup>2</sup> and is tunable by the pulse amplitude. The tunneling currents as a function of voltage after positive and negative program pulses are shown in Fig. 1c. The tunneling conductance at  $2$  V is plotted as function of program pulse value, shown in Fig. 1d. The insets show the pulse sequences. Non-volatile resistance switching is clearly observed. The positive pulses set the device to the low conductance OFF-state, whereas negative pulses switch the device to the high conductance ON-state. Notice that the two hysteresis loops (red and green) measured using two different pulse sequences are nearly identical, indicating that the TER hysteresis is reproducible.

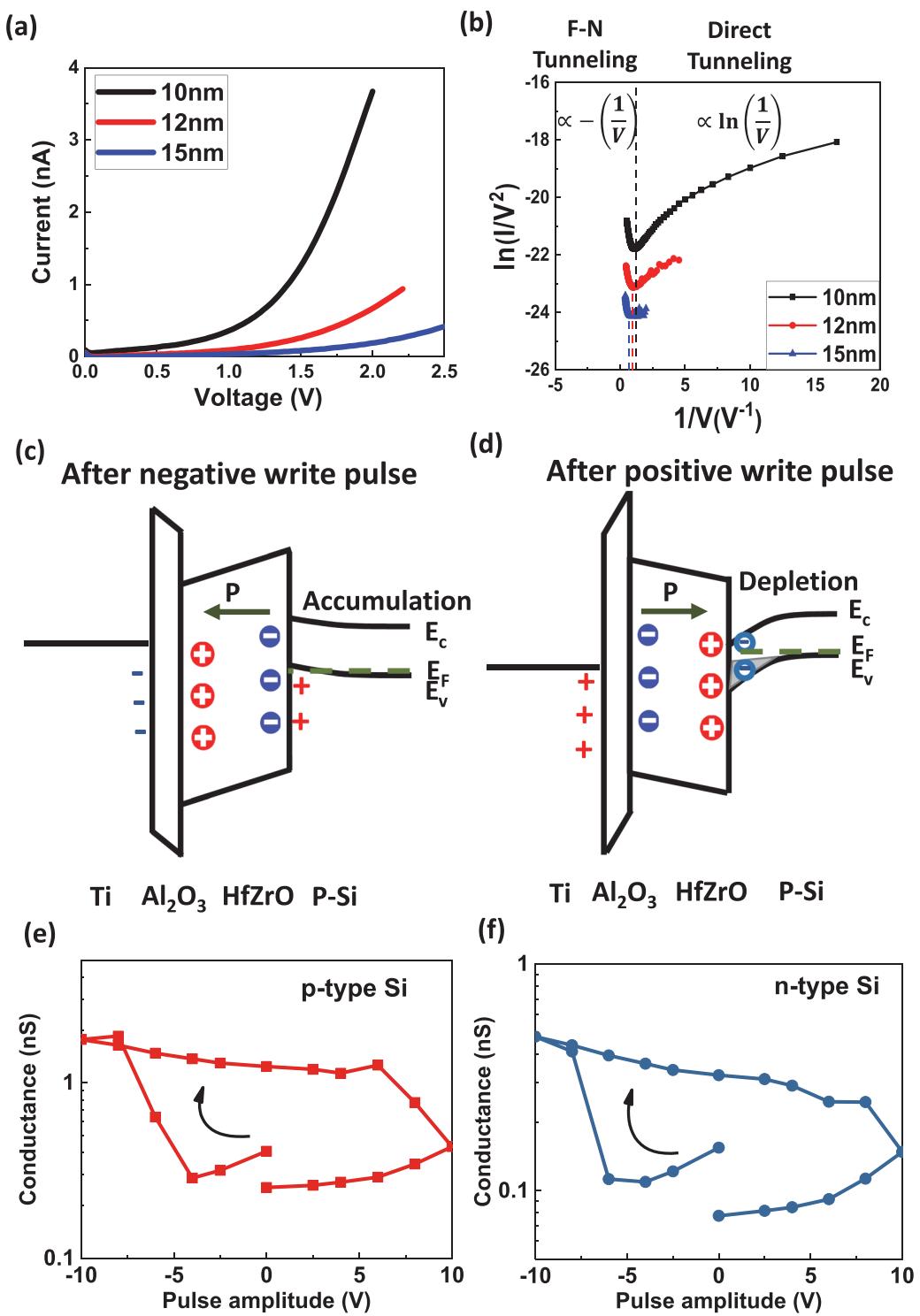

**Figure 2.** Mechanism of the hysteresis loops in FTJs based on Ti/Al<sub>2</sub>O<sub>3</sub>/HZO/p-Si. (a) Tunneling current as a function of voltage for FTJs with various HZO thicknesses at ON-state. (b)  $\ln(I/V^2)$  as a function of  $1/V$  for the data shown in (a). (c,d) Energy band diagrams of the FTJ after negative and positive write pulses respectively. (e,f) Hysteresis loops of the tunneling conductance at 2 V of FTJs based on Ti/Al<sub>2</sub>O<sub>3</sub>/HZO on p-type and n-type Si substrates respectively.

These TER hysteresis loop can be explained by the following analysis. Figure 2a shows the tunneling current as a function of applied voltage for FTJs based on metal/Al<sub>2</sub>O<sub>3</sub>/HZO/Si structure with various HZO thicknesses (10 nm, 12 nm and 15 nm) at ON-state. We plotted  $\ln(I/V^2)$  versus  $1/V$ , where  $I$  is the ON-state tunneling current and  $V$  is the applied voltage, shown in Fig. 2b. At high bias,  $\ln(I/V^2)$  decreases linearly with  $1/V$ , indicating that

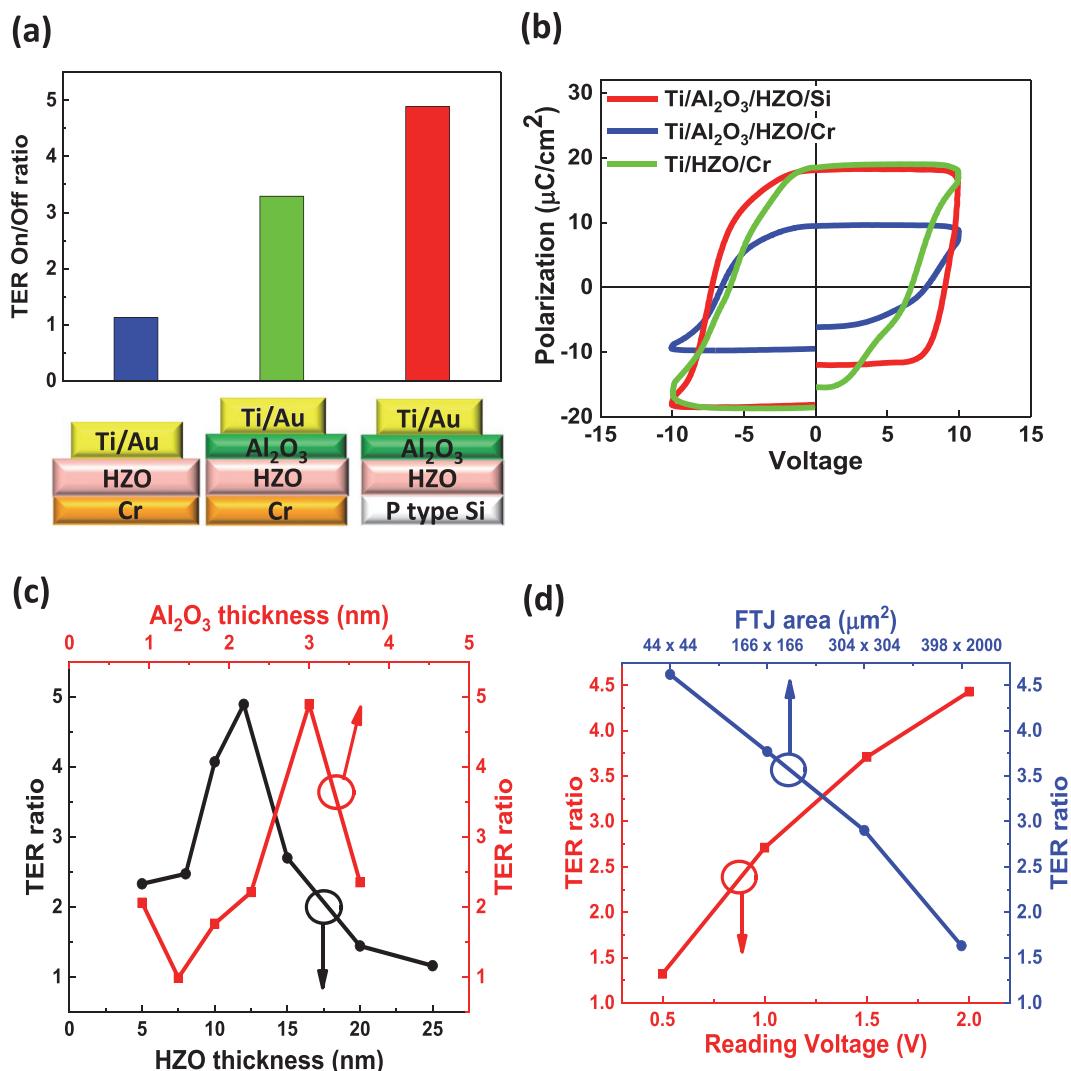

**Figure 3.** FTJs based on various structures. **(a)** TER ratios and **(b)** P-V loops of the FTJs based on Ti/HZO/Cr, Ti/Al<sub>2</sub>O<sub>3</sub>/HZO/Cr, and Ti/Al<sub>2</sub>O<sub>3</sub>/HZO/p-Si structures. **(c)** TER ratio as a function of Al<sub>2</sub>O<sub>3</sub> thickness (top x axis) and HZO thickness (bottom x axis). **(d)** TER ratio as a function of FTJ area (top x axis) and read voltage (bottom x axis).

Fowler-Nordheim (F-N) tunneling dominates. At low bias,  $\ln(I/V^2)$  increases logarithmically with  $1/V$ , which is consistent with direct tunneling<sup>38</sup>. For the TER hysteresis loop shown in Fig. 1d, the read voltage is 2 V, which is in the F-N tunneling regime. The energy diagrams of the FTJs after positive and negative program pulses are shown in Fig. 2c,d respectively. When a negative pulse is applied on the top electrode, the polarization in HZO points to the electrode, which will induce a band tilt in HZO. In addition, the screening charge drives p-type silicon into accumulation, which will reduce tunneling width and increase the tunneling current. A positive read voltage will further enhance the band tilt in HZO and increase the F-N tunneling. These two factors will lead to high conductance in the FTJ. To further understand the impact of these two factors, we fabricated FTJs with p-type and n-type substrates and compared their TER hysteresis, shown in Fig. 2e,f. The hysteresis loops of these two devices are both clockwise with similar TER ratios. If the substrate depletion/accumulation is the dominant factor for the hysteresis loop, we would expect that the direction of the hysteresis loop will be opposite for FTJs with n- and p-type substrates. This result confirms that the polarization induced F-N tunneling barrier change is the main source for the hysteresis loop observed in these FTJs.

The ultra-thin Al<sub>2</sub>O<sub>3</sub> tunneling layer plays an important role in these FTJs. As shown in Fig. 3a, the TER ratio of the FTJ based on metal/Al<sub>2</sub>O<sub>3</sub>/HZO/Si is much higher than that on metal/HZO/metal and metal/Al<sub>2</sub>O<sub>3</sub>/HZO/metal structures. Here, the interfacial Al<sub>2</sub>O<sub>3</sub> layer facilitates the tuning of the band offset between HZO and metal, which can effectively enhance the TER ratio. Silicon substrate is also an important component in the FTJs. As shown in Fig. 3b, the remanent polarization of the FTJ based on a silicon substrate is much higher than that on Cr metal substrate, which explains the higher TER ratio observed in the FTJ based on silicon structure as compared to that on a metal substrate.

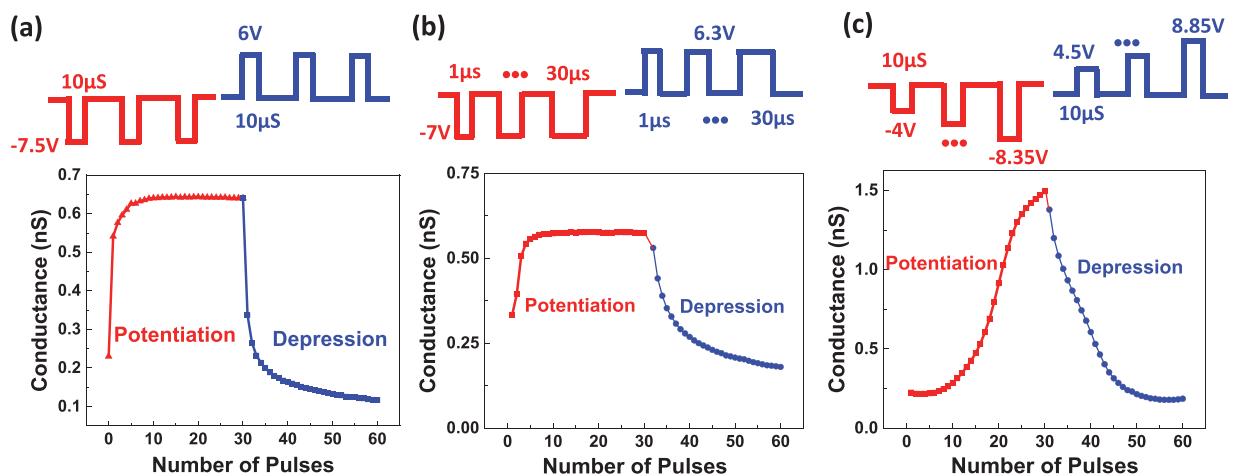

**Figure 4.** Tunneling conductance of FTJs as a function of pulse numbers. (a) Scheme 1: constant pulse amplitude and width. (b) Scheme 2: modulation of pulse width. (c) Scheme 3: modulation of pulse amplitude.

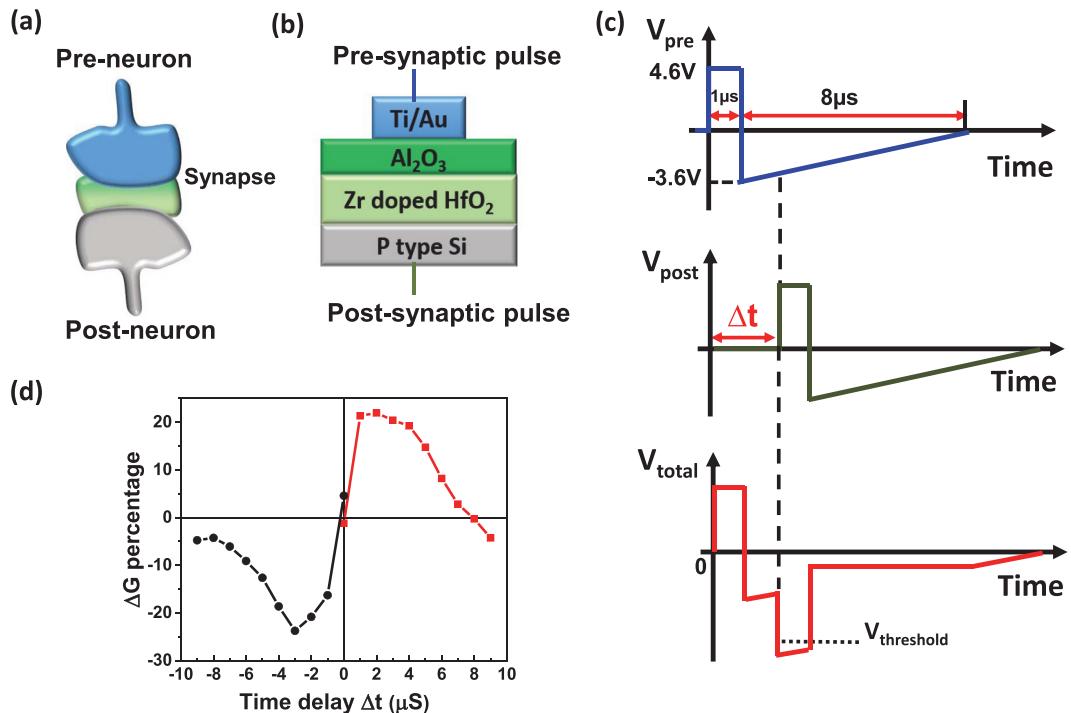

**Figure 5.** STDP of FTJs based on Al<sub>2</sub>O<sub>3</sub>/HZO stack. (a) Sketch of pre- and post-neurons connected by a synapse. (b) Schematic of HZO FTJ. (c) The waveforms of the pre-synaptic pulse  $V_{pre}$ , post-synaptic pulse  $V_{post}$  and the total voltage  $V_{total} = V_{pre} - V_{post}$  on a FTJ. The pre-synaptic pulse is applied on the top gate, while the post-synaptic pulse is applied on the back gate of the FTJ. (d) Measurement of STDP in a FTJ based on Al<sub>2</sub>O<sub>3</sub>/HZO stack.

For FTJs based on metal/Al<sub>2</sub>O<sub>3</sub>/HZO/Si structure, the optimal Al<sub>2</sub>O<sub>3</sub> thickness is ~3 nm, shown in Fig. 3c. An ultra-thin Al<sub>2</sub>O<sub>3</sub> layer cannot provide enough tunability on the band offset, while too thick an Al<sub>2</sub>O<sub>3</sub> layer can impede the tunneling current. The optimal HZO thickness is 10–12 nm, where ultrathin HZO does not have sufficient polarization, while thick HZO is difficult to tunnel through. TER ratios can be enhanced by using a smaller device area due to increased homogeneity and by using higher read voltage due to enhanced F-N tunneling (Fig. 3d).

For the synaptic application, the tunneling resistance needs to be continuously tunable to emulate biological synapses. Figure 4a–c show the TER as a function of the pulse number with various pulse schemes. Scheme 1 consists of identical pulses with constant pulse amplitude and width. Scheme 2 consists of pulses with increasing pulse width while keeping the amplitude of the pulse constant. The pulse width for the  $n$ th pulse is  $t_n = t_1 + (n - 1)\Delta t$ , where  $t_1$  is the width of the first pulse and  $\Delta t$  is the increment of pulse width between two

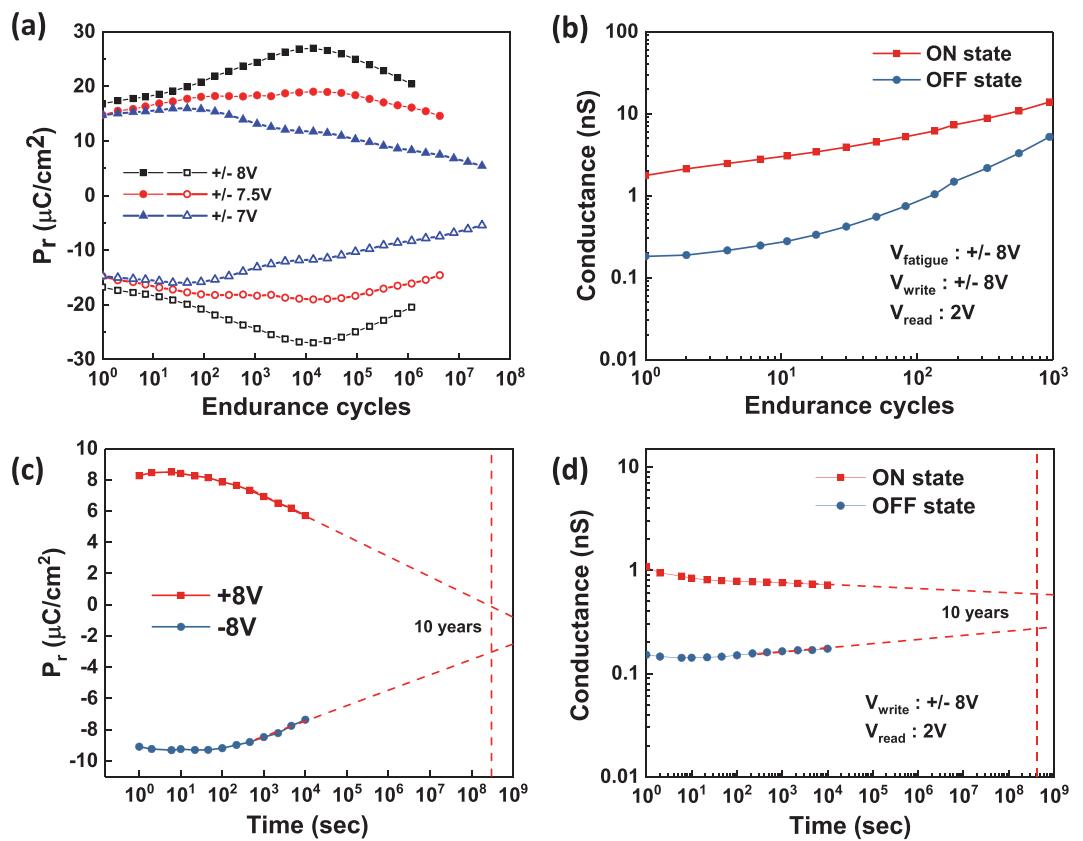

**Figure 6.** The reliability of the FTJs based on  $\text{Al}_2\text{O}_3/\text{HZO}/\text{Si}$  structure. (a) Remanent polarization as a function of endurance cycles measured at different cycling voltages:  $\pm 7\text{ V}$ ,  $\pm 7.5\text{ V}$ , and  $\pm 8\text{ V}$ . The amplitudes of the cycling and the PUND read pulses are the same. The pulse width is  $10\text{ }\mu\text{s}$  for all cases. (b) Tunneling conductance at ON- and OFF-states as a function of endurance cycles. The amplitude of the cycling and program pulse is  $8\text{ V}$ . The tunneling conductance is extracted at  $2\text{ V}$  from the dc IV measurement. (c) Remanent polarization as a function of retention time. The amplitudes of the program and the PUND read pulses are  $8\text{ V}$ . The program pulse width is  $10\text{ }\mu\text{s}$ . The read pulse width is  $100\text{ ns}$ . (d) Tunneling conductance at ON- and OFF-states as a function of retention time. The program pulse amplitude is  $8\text{ V}$  and the tunneling conductance is extracted at  $2\text{ V}$  from the dc IV measurement.

consecutive pulses. Scheme 3 consists of pulses with increasing pulse amplitude while keeping the pulse width constant. In all three cases, the FTJ conductance increases with the number of potentiation pulses and decreases with the number of depression pulses, indicating that the synaptic weight is continuously tunable. Among the three schemes, pulse amplitude modulation shows the best performance in terms of discrete multilevel states, linearity, and symmetry. The analog behavior due to partial polarization switching observed in these devices indicates the high potential of ferroelectric FTJs in neuromorphic application.

In biologic synapses, STDP is considered an important mechanism for memory and learning. We characterized the STDP characteristics of the FTJ synapses using pairs of pulses, emulating the spikes from pre- and post-neurons as illustrated in Fig. 5c. When the pre- and post-synaptic pulses reach the FTJs with a time delay  $\Delta t$ , their superposition produces the waveforms  $V_{\text{total}} = V_{\text{pre}} - V_{\text{post}}$ . If the resulting combined waveform momentarily exceeds the threshold voltage, it will lead to an increase or a decrease of the FTJ conductance, depending on the sign of  $\Delta t$ . Figure 5d shows the measured conductance change as a function of time delay between pre- and post-synaptic pulses  $\Delta t$  in a FTJ based on  $\text{Al}_2\text{O}_3/\text{HZO}$  stack. Here the conductance change percentage is defined as  $\% \Delta G = \frac{G_f - G_i}{\min(G_i, G_f)}$ , where  $G_i$  is the initial conductance before applying a pair of pulses,  $G_f$  is the final conductance after applying a pair of pulses and  $\min(G_i, G_f)$  is the minimum of  $G_i$  and  $G_f$ <sup>39,40</sup>. As can be seen in Fig. 5d, the conductance increases when  $\Delta t > 0$ , while decreases when  $\Delta t < 0$ . Close-timed pulses lead to a large conductance change, whereas long delays between two pulses leave the FTJ unchanged. These phenomena can be understood through the waveform of the total voltage  $V_{\text{total}}$ . If the post-synaptic pulse arrives after the pre-synaptic pulse ( $\Delta t > 0$ ), the peak total voltage is negative, which will increase the conductance of the FTJ (the synapse is strengthened), as illustrated in supplementary information (Fig. S2). When the post-synaptic pulses come before the pre-synaptic pulse ( $\Delta t < 0$ ), the peak total voltage is positive, thus the conductance of FTJ decreases (the synapse is weakened). The absolute value of  $|\Delta t|$  can influence the amplitude of the conductance change. As illustrated in Fig. S3, small time gap  $|\Delta t|$  results in large amplitude of peak voltage  $|V_{\text{total}}|$ , which leads to dramatic

change of conductance in FTJ. These results indicate that the FTJs based on  $\text{Al}_2\text{O}_3/\text{HZO}$  stacks can mimick the STDP function of biologic synapses.

We further investigated the reliability of the FTJs based on the  $\text{Al}_2\text{O}_3/\text{HZO}/\text{Si}$  structure. Figure 6a shows the remanent polarization as a function of the cycle numbers. At the  $\pm 7\text{ V}$  cycling voltage, the device shows the characteristic fatigue behavior and the endurance is over  $10^7$  cycles. At a higher cycling voltage ( $\pm 8\text{ V}$ ), a wake-up effect at early stage and a fatigue effect at the late stage followed by a hard breakdown were observed. The endurance is  $\sim 10^6$  cycles at  $\pm 8\text{ V}$  cycling voltage. The evolution of the tunneling conductance in the ON- and OFF-states with cycling numbers is shown in Fig. 6b. Both the ON- and OFF-conductance increases with the cycle numbers due to the stress-induced leakage current, which can be attributed to interface and bulk traps formed in the dielectric during the high voltage pulses. A TER ratio of  $\sim 2.65$  remains after  $10^3$  cycles at  $\pm 8\text{ V}$  cycling voltage. The retention of the FTJs is also characterized. Figure 6c shows the remanent polarization as a function of retention time. The remanent polarization reduces gradually with time due to the depolarization field, which can be attributed to the incomplete charge compensation at the  $\text{Al}_2\text{O}_3/\text{HZO}$  and  $\text{HZO}/\text{Si}$  interfaces. As a result, the tunneling conductance contrast between ON- and OFF-states reduces with time accordingly, shown in Fig. 6d. At room temperature, a TER ratio of  $\sim 2.64$  remains after extrapolation to 10 years.

## Conclusion

In conclusion, we demonstrated a new type of FTJ based on  $\text{Al}_2\text{O}_3/\text{HZO}/\text{Si}$  structure for neurosynaptic applications. We found that an  $\text{Al}_2\text{O}_3$  interfacial layer and the silicon substrate can significantly enhance the TER ratio. The ferroelectricity in Zr-doped  $\text{HfO}_2$  can be as high as  $21\text{ }\mu\text{C}/\text{cm}^2$  and is tunable by the program pulse amplitude and duration, which is critical for synaptic applications. We found that the current in these devices is dominated by direct tunneling at low bias and by F-N tunneling at high bias. The polarization switching in HZO can alter the tunneling barrier height and lead to different tunneling resistance states. The TER ratios of the FTJs are influenced by the thickness of  $\text{Al}_2\text{O}_3$  and HZO, the area of the device, and the read voltage. These FTJs show tunable multilevel resistance states, linear potentiation/depression characteristics, and strong STDP behavior, which are the critical traits for artificial synapses. The retention of the FTJs is longer than 10-years at room temperature and the FTJs can endure over  $10^7$  cycles at  $7\text{ V}$  program voltage. These novel FTJs will have high potential in both energy-efficient non-volatile memories and artificial neural network applications.

Received: 13 June 2019; Accepted: 7 December 2019;

Published online: 31 December 2019

## References

1. Xia, Q. & Yang, J. J. Memristive crossbar arrays for brain-inspired computing. *Nature materials* **18**, 309 (2019).

2. Eryilmaz, S. B. *et al.* Brain-like associative learning using a nanoscale non-volatile phase change synaptic device array. *Front Neurosci-Switz*, **8**, <https://doi.org/10.3389/fnins.2014.00205> (2014).

3. Merolla, P. *et al.* A Digital Neurosynaptic Core Using Embedded Crossbar Memory with 45pJ per Spike in 45nm. *Ieee Cust Integr Cir* (2011).

4. Shanbhag, N. R. *et al.* The search for alternative computational paradigms. *Ieee Des Test Comput* **25**, 334–343, <https://doi.org/10.1109/Mdt.2008.113> (2008).

5. Merolla, P. A. *et al.* A million spiking-neuron integrated circuit with a scalable communication network and interface. *Science* **345**, 668–673, <https://doi.org/10.1126/science.1254642> (2014).

6. Moon, K. *et al.* RRAM-based synapse devices for neuromorphic systems. *Faraday Discuss* **213**, 421–451, <https://doi.org/10.1039/c8fd00127h> (2019).

7. Kuzum, D., Jeyasingh, R. G. D., Lee, B. & Wong, H. S. P. Nanoelectronic Programmable Synapses Based on Phase Change Materials for Brain-Inspired Computing. *Nano Letters* **12**, 2179–2186, <https://doi.org/10.1021/nl201040y> (2012).

8. Suri, M. *et al.* Phase Change Memory as Synapse for Ultra-Dense Neuromorphic Systems: Application to Complex Visual Pattern Extraction. *2011 Ieee International Electron Devices Meeting (Iedm)* (2011).

9. Sebastian, A. *et al.* Tutorial: Brain-inspired computing using phase-change memory devices. *J Appl Phys*, **124**, <https://doi.org/10.1063/1.5042413> (2018).

10. Boybat, I. *et al.* Neuromorphic computing with multi-memristive synapses. *Nat Commun*, **9**, <https://doi.org/10.1038/s41467-018-04933-y> (2018).

11. Burr, G. W. *et al.* Neuromorphic computing using non-volatile memory. *Adv Phys-X* **2**, 89–124, <https://doi.org/10.1080/23746149.2016.1259585> (2017).

12. Jerry, M. *et al.* In 2017 IEEE International Electron Devices Meeting (IEDM). 6.2. 1–6.2. 4 (IEEE 2017).

13. Yu, S. Neuro-inspired computing with emerging nonvolatile memories. *Proceedings of the IEEE* **106**, 260–285 (2018).

14. Jerry, M. *et al.* A ferroelectric field effect transistor based synaptic weight cell. *J Phys D Appl Phys*, **51**, <https://doi.org/10.1088/1361-6463/aad6f8> (2018).

15. Kim, M. K. & Lee, J. S. Ferroelectric Analog Synaptic Transistors. *Nano Letters* **19**, 2044–2050, <https://doi.org/10.1021/acs.nanolett.9b00180> (2019).

16. Oh, S. *et al.* HfZrOx-Based Ferroelectric Synapse Device With 32 Levels of Conductance States for Neuromorphic Applications. *Ieee Electr Device L* **38**, 732–735, <https://doi.org/10.1109/led.2017.2698083> (2017).

17. Wang, L. F. *et al.* Overcoming the Fundamental Barrier Thickness Limits of Ferroelectric Tunnel Junctions through  $\text{BaTiO}_3/\text{SrTiO}_3$  Composite Barriers. *Nano Letters* **16**, 3911–3918, <https://doi.org/10.1021/acs.nanolett.6b01418> (2016).

18. Yoon, C. *et al.* Synaptic Plasticity Selectively Activated by Polarization-Dependent Energy-Efficient Ion Migration in an Ultrathin Ferroelectric Tunnel Junction. *Nano Letters* **17**, 1949–1955, <https://doi.org/10.1021/acs.nanolett.6b05308> (2017).

19. Müller, J., Polakowski, P., Mueller, S. & Mikolajick, T. Ferroelectric Hafnium Oxide Based Materials and Devices: Assessment of Current Status and Future Prospects. *ECS Journal of Solid State Science and Technology* **4**, N30–N35, <https://doi.org/10.1149/2.0081505jss> (2015).

20. Muller, J., Polakowski, P., Mueller, S. & Mikolajick, T. Ferroelectric Hafnium Oxide based Materials and Devices: Assessment of Current Status and Future Prospects. *Ecs Transactions* **64**, 159–168, <https://doi.org/10.1149/06408.0159ecst> (2014).

21. Mueller, S. *et al.* Incipient Ferroelectricity in Al-Doped  $\text{HfO}_2$  Thin Films. *Adv Funct Mater* **22**, 2412–2417, <https://doi.org/10.1002/adfm.201103119> (2012).

22. Boscke, T. S. *et al.* Phase transitions in ferroelectric silicon doped hafnium oxide. *Appl Phys Lett*, **99**, <https://doi.org/10.1063/1.3636434> (2011).

23. N. Gong, X. S., H. Jiang, Q. Xia and T.P.Ma. In *46th IEEE Semiconductor Interface Specialists Conference* (Arlington, VA, 2015).

24. Müller, J. *et al.* Ferroelectricity in yttrium-doped hafnium oxide. *J Appl Phys* **110**, 114113, <https://doi.org/10.1063/1.3667205> (2011).

25. Müller, J. *et al.* Ferroelectricity in Simple Binary ZrO<sub>2</sub> and HfO<sub>2</sub>. *Nano Letters* **12**, 4318–4323, <https://doi.org/10.1021/nl302049k> (2012).

26. Mueller, S. *et al.* Ferroelectricity in Gd-Doped HfO<sub>2</sub>. *Thin Films. Ecs J Solid State Sc* **1**, N123–N126, <https://doi.org/10.1149/2.002301jss> (2012).

27. Schenk, T. *et al.* In *Solid-State Device Research Conference (ESSDERC) Proceedings of the European*. 260–263, (2013).

28. Muller, J. *et al.* Ferroelectric Hafnium Oxide: A CMOS-compatible and highly scalable approach to future ferroelectric memories. *2013 Ieee International Electron Devices Meeting (Iedm)* (2013).

29. Yurchuk, E. *et al.* Impact of Scaling on the Performance of HfO<sub>2</sub>-Based Ferroelectric Field Effect Transistors. *Ieee Transactions on Electron Devices* **61**, 3699–3706, <https://doi.org/10.1109/Ted.2014.2354833> (2014).

30. Schroeder, U. *et al.* Hafnium Oxide Based CMOS Compatible Ferroelectric. *Materials. Ecs J Solid State Sc* **2**, N69–N72, <https://doi.org/10.1149/2.010304jss> (2013).

31. Chernikova, A. *et al.* Ultrathin Hf0.5Zr0.5O<sub>2</sub> Ferroelectric Films on Si. *AcS Appl Mater Inter* **8**, 7232–7237, <https://doi.org/10.1021/acsami.5b11653> (2016).

32. Park, M. H., Kim, H. J., Kim, Y. J., Moon, T. & Hwang, C. S. The effects of crystallographic orientation and strain of thin Hf0.5Zr0.5O<sub>2</sub> film on its ferroelectricity. *Appl Phys Lett*, **104**, <https://doi.org/10.1063/1.4866008> (2014).

33. Chen, L. *et al.* Ultra-low power Hf0.5Zr0.5O<sub>2</sub> based ferroelectric tunnel junction synapses for hardware neural network applications. *Nanoscale* **10**, 15826–15833, <https://doi.org/10.1039/C8NR04734K> (2018).

34. Jerry, M. *et al.* Ferroelectric FET Analog Synapse for Acceleration of Deep Neural Network Training. *Int El Devices Meet* (2017).

35. Ambriz-Vargas, F. *et al.* A Complementary Metal Oxide Semiconductor Process-Compatible Ferroelectric Tunnel Junction. *AcS Appl Mater Inter* **9**, 13262–13268, <https://doi.org/10.1021/acsami.6b16173> (2017).

36. Chouprik, A. *et al.* Electron transport across ultrathin ferroelectric Hf0.5Zr0.5O<sub>2</sub> films on Si. *Microelectron Eng* **178**, 250–253, <https://doi.org/10.1016/j.mee.2017.05.028> (2017).

37. Mittmann, T. *et al.* Optimizing process conditions for improved Hf-1 - ZrxO<sub>2</sub> ferroelectric capacitor performance. *Microelectron Eng* **178**, 48–51, <https://doi.org/10.1016/j.mee.2017.04.031> (2017).

38. Ikuno, T. *et al.* Electron transport properties of Si nanosheets: Transition from direct tunneling to Fowler-Nordheim tunneling. *Appl Phys Lett*, **99**, <https://doi.org/10.1063/1.3610486> (2011).

39. Panwar, N., Rajendran, B. & Ganguly, U. Arbitrary spike time dependent plasticity (STDP) in memristor by analog waveform engineering. *IEEE Electron Device Letters* **38**, 740–743 (2017).

40. Jackson, B. L. *et al.* Nanoscale electronic synapses using phase change devices. *ACM Journal on Emerging Technologies in Computing Systems (JETC)* **9**, 12 (2013).

## Acknowledgements

We would like to acknowledge support from the NSF under grant ECCS 16-53241 CAR, from ONR under grant NAVY N00014-17-1-2973, and from the Kwanjeong Educational Foundation.

## Author contributions

H.R. fabricated and characterized the devices. H.W. contributed to the setup of the ferroelectric testing program and characterization of some devices. F. R. helped on the development of ALD process of the HZO film. W.Z. initiated and supervised the project. H.R. and W.Z. wrote the manuscript with inputs from all coauthors.

## Competing interests

The authors declare no competing interests.

## Additional information

**Supplementary information** is available for this paper at <https://doi.org/10.1038/s41598-019-56816-x>.

**Correspondence** and requests for materials should be addressed to W.Z.

**Reprints and permissions information** is available at [www.nature.com/reprints](http://www.nature.com/reprints).

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit <http://creativecommons.org/licenses/by/4.0/>.

© The Author(s) 2019