# Electronic synapses with near-linear weight update using MoS<sub>2</sub>/graphene memristors

Cite as: Appl. Phys. Lett. **115**, 103104 (2019); https://doi.org/10.1063/1.5108899 Submitted: 03 May 2019 . Accepted: 20 August 2019 . Published Online: 06 September 2019

Adithi Krishnaprasad, Nitin Choudhary, Sonali Das, Durjoy Dev (10), Hirokjyoti Kalita, Hee-Suk Chung, Olaleye Aina, Yeonwoong Jung (10), and Tania Roy (10)

ARTICLES YOU MAY BE INTERESTED IN

Gasistor: A memristor based gas-triggered switch and gas sensor with memory Applied Physics Letters 115, 093504 (2019); https://doi.org/10.1063/1.5099685

Characterization of Ge ions implantation in Sb<sub>2</sub>Te<sub>3</sub> thin films for high speed phase change memory application

Applied Physics Letters 115, 103105 (2019); https://doi.org/10.1063/1.5109178

Perspective: A review on memristive hardware for neuromorphic computation Journal of Applied Physics 124, 151903 (2018); https://doi.org/10.1063/1.5037835

## Electronic synapses with near-linear weight update using MoS<sub>2</sub>/graphene memristors

Cite as: Appl. Phys. Lett. **115**, 103104 (2019); doi: 10.1063/1.5108899 Submitted: 3 May 2019 · Accepted: 20 August 2019 · Published Online: 6 September 2019

Adithi Krishnaprasad,<sup>1,2</sup> Nitin Choudhary,<sup>1</sup> Sonali Das,<sup>1</sup> Durjoy Dev,<sup>1,2</sup> (b) Hirokjyoti Kalita,<sup>1,2</sup> Hee-Suk Chung,<sup>4</sup> Olaleye Aina,<sup>5</sup> Yeonwoong Jung,<sup>1,2,3</sup> (b) and Tania Roy<sup>1,2,3,a)</sup> (b)

#### **AFFILIATIONS**

- NanoScience Technology Center, University of Central Florida, Orlando, Florida 32826, USA

- <sup>2</sup>Department of Electrical and Computer Engineering, University of Central Florida, Orlando, Florida 32816, USA

- <sup>3</sup>Department of Materials Science and Engineering, University of Central Florida, Orlando, Florida 32816, USA

- <sup>4</sup>Analytical Research Division, Korea Basic Science Institute, Jeonju, Jeollabuk-do 54907, South Korea

#### **ABSTRACT**

Emulating the human brain's circuitry composed of neurons and synapses is an emerging area of research in mitigating the "von Neumann bottleneck" in present computer architectures. The building block of these neuromorphic systems—the synapse—is commonly realized with oxide-based or phase change material-based devices, whose operation is limited by high programming currents and high reset currents. In this work, we have realized nonvolatile resistive switching MoS<sub>2</sub>/graphene devices that exhibit multiple conductance states at low operating currents. The MoS<sub>2</sub>/graphene devices exhibit essential synaptic behaviors, such as short and long-term potentiation, long-term depression, and the spike timing dependent plasticity learning rule. Most importantly, they exhibit a near-linear synaptic weight update, without any abrupt reset process, allowing their use in unsupervised learning applications. These electronic synapses are built with chemical vapor deposited MoS<sub>2</sub> and graphene, demonstrating potential for large-scale realizations of machine learning hardware.

Published under license by AIP Publishing. https://doi.org/10.1063/1.5108899

The von Neumann architecture in current processors involves physically separated memory and processing units. Additionally, with memory speeds lagging behind processor speeds, latency in accessing data from the memory has resulted in the von Neumann bottleneck. To alleviate this issue, several alternative non-von Neumann architectures are being explored. 1,2 Neuromorphic computing is one such approach inspired by the human brain's capability of cognitive processing.<sup>3</sup> The building blocks of neuromorphic systems are electronic neurons and synapses. In 2008, after the discovery of memristive behavior in oxides, researchers have explored the idea of mimicking synaptic behavior with a single memristive device. 4-9 Albeit significant advances, synaptic devices using phase change materials<sup>6,10-12</sup> and metal oxide-based resistive switching devihave some limitations. These devices exhibit a high programming current in the range of microampere-milliampere, increasing the energy consumption by the device. 15 Additionally, the synaptic weight update, i.e., the increase (decrease) of the synapse's conductance with the application of a continuous stream of identical positive (negative) input voltage pulses, is nonlinear. Nonlinearity in the weight update increases the complexity of using these devices for real-time unsupervised

learning.<sup>15</sup> So, it becomes necessary to employ a material system which exhibits a low programming current as well as a linear weight update.<sup>15</sup> Recently, two-dimensional (2D) materials are being largely explored to demonstrate their viability as electronic synapses.<sup>16–20</sup> However, a linear synaptic weight update with identical voltage pulses using memristive switching in 2D materials has not been reported yet. Also, some of these 2D memristive synapses exhibit a high programming current; having low-power operation in neuromorphic circuits is infeasible.<sup>19</sup>

In this work, we demonstrate a memristive synapse using chemical vapor deposited (CVD) molybdenum disulfide (MoS<sub>2</sub>) as the switching medium and large area CVD grown monolayer graphene as the bottom electrode. The synaptic devices exhibit gradual potentiation and depression, with a near-linear weight update when identical input voltage pulses are applied. They display excellent retention characteristics of  $10^4$  s at 1 nA operating current, demonstrating their applicability in low-power neuromorphic systems. They also exhibit the essential synaptic characteristics of short-term potentiation (STP) and long-term potentiation (LTP) in the same device, and spike timing dependent plasticity (STDP).

<sup>&</sup>lt;sup>5</sup>BAE Systems FAST Labs, Columbia, Maryland 21046, USA

a) Author to whom correspondence should be addressed: tania.roy@ucf.edu

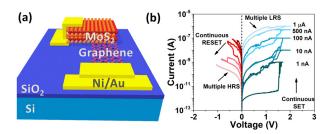

**FIG. 1.** (a)  $\rm MoS_2$ /graphene device schematic (not to scale) and (b) DC potentiation and depression with continuous SET at 1 nA, 10 nA, 100 nA, 500 nA, and 1  $\mu$ A, followed by continuous RESET using negative reset stop voltages with increasing magnitude from -0.2 V to -1 V.

Figure 1(a) shows the schematic of a single MoS<sub>2</sub>/graphene device, with a large array of  $\sim$ 2000 devices shown in Fig. S1(a). CVDgrown monolayer graphene was wet-transferred<sup>21</sup> on p<sup>+</sup>-Si/SiO<sub>2</sub>. The graphene layer was patterned using photolithography and etched in oxygen plasma to form the bottom electrode of the device. Mo films (3 nm) were patterned using photolithography and e-beam evaporated on the etched graphene strips. The Mo films were sulfurized to form layered MoS<sub>2</sub> in a low-pressure CVD furnace at 200 mTorr and a substrate temperature of 770 °C in an inert environment. Top contacts on MoS<sub>2</sub> and bonding pads on graphene were patterned using photolithography, followed by e-beam evaporation of Ni/Au (30 nm/30 nm) and lift-off. The region where MoS2 overlaps graphene forms the active area  $(24-36 \mu m^2)$  for switching. The large-scale growth of graphene and MoS<sub>2</sub> enables the fabrication of multiple arrays of 2000 MoS<sub>2</sub>/graphene devices. Raman spectra of the MoS<sub>2</sub>/graphene system, atomic force microscopy (AFM) image of MoS2 and cross-sectional high-resolution transmission electron microscopy (HRTEM) image are shown in Figs. S1(b)-S1(d).

The electrical characterization studies of the MoS<sub>2</sub>/graphene devices are performed using a Keysight B1500A semiconductor device analyzer. The devices exhibit a pinched hysteresis loop when subjected to a sinusoidally varying input voltage, indicating their memristive behavior [Fig. S2(a)]. During the DC characterization of these devices, the voltage on the top electrode (Ni/Au) is held constant at 0 V, while the voltage on the bottom graphene electrode is swept. The devices exhibit nonvolatile resistive switching for an SET current compliance of 100 nA [Fig. S2(b)]. A continuous SET process is performed by increasing the SET current compliance from 1 nA to 1 µA,

immediately followed by a continuous RESET by increasing the magnitude of the negative reset stop voltage from -0.2 V to -1 V. Figure 1(b) shows that five distinct states are obtained during the continuous DC SET and RESET processes. Figure S2(c) shows the same plot on the linear scale. This demonstrates the potential of the MoS2/graphene devices to display a gradual change in conductance both in the low resistance and high resistance regimes, which is mandatory for emulating the potentiation and depression of a synapse. The MoS2/graphene devices also exhibit excellent retention characteristics for  $\sim\!10^4$  s at 1 nA and 1  $\mu\rm A$  current compliances (Fig. S3). We note that the higher conductance state is more stable than the lower conductance state. Figure S4 shows stable switching for 100 DC cycles at 1 nA and 100 nA in the same device, establishing a reasonable endurance of the MoS2/graphene system.

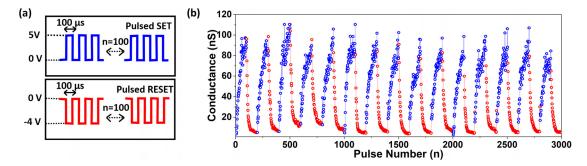

Next, pulsed I-V measurements are performed to determine the synaptic behavior of these devices. The current flowing through the memristive synapse as a response to the incoming voltage pulses is defined as the postsynaptic current (PSC). The device conducts current when the voltage pulse is ON, and the short pulse duration restricts the abrupt formation of the conducting channel. This facilitates the gradual formation of the conduction path during the pulsing intervals.9 Because of this gradual formation of the channel, the device exhibits a higher number of conductance states during pulsed measurements than during a continuous DC SET process.<sup>22</sup> This process of conductance tuning is characteristic of a biological synapse, and is termed as synaptic weight update. <sup>15</sup> A hundred pulses with a pulse width of 100  $\mu$ s and an amplitude of 5 V are applied to cause potentiation, immediately followed by another 100 pulses with a width of 100  $\mu$ s and an amplitude of -4 V to cause depression. A total of 15 pairs of such identical positivenegative voltage pulse trains are applied to an MoS<sub>2</sub>/graphene device, as shown in the Fig. 2(a). The corresponding conductance is plotted against the pulse number in Fig. 2(b). We observe distinct conductance states with a pulsed voltage input. The MoS<sub>2</sub>/graphene device exhibits an almost linear weight update with identical input voltage pulses. We calculate the nonlinearity factor (NLF) for the potentiation and depression regimes using a behavioral model described by Chen et al.<sup>23</sup> Our MoS<sub>2</sub>/graphene device exhibits an exceptional NLF of 0.276 in the potentiation regime, with an NLF of 0 indicating a completely linear weight update.<sup>23</sup> The weight update during depression exhibits an NLF of ~5. The near-linear weight update observed in the MoS<sub>2</sub>/graphene synapse holds potential for unsupervised learning applications. 1 Although ~100 distinct conductance states during potentiation and

FIG. 2. (a) Pulsing scheme: 15 pulse trains, with each pulse train comprising 100 identical positive pulses and 100 identical negative pulses. (b) Near-linear weight update observed in the MoS<sub>2</sub>/graphene synapse with the application of symmetric voltage pulses shown in (a).

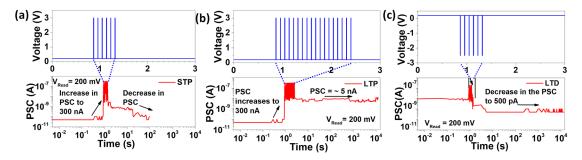

FIG. 3. (a) STP of the  $MoS_2$ /graphene synapse with the input pulsing scheme (top) and PSC as a function of time (bottom). (b) LTP of the same device for  $10^4$  s with the input pulsing scheme (top) and PSC as a function of time (bottom). (c) LTD of the  $MoS_2$ /graphene synapse for  $10^4$  s with the pulsing scheme (top) and PSC as a function of time (bottom).

depression are observed for all 15 pulse trains, we note that the instability of the lower conductance states would result in significant write noise for system level applications, thus reducing the number of resolvable conductance states. This issue can be circumvented using a write/verify algorithm, which is costly from the standpoint of power consumption.

The MoS<sub>2</sub>/graphene memristors are also tested for essential characteristics of a biological synapse, such as short-term potentiation (STP), long-term potentiation (LTP), and long-term depression (LTD). Figure 3(a) shows the STP characteristics of a typical MoS<sub>2</sub>/ graphene synaptic device. Here, note that we use a different measurement protocol than that for retention measurements of Fig. S3(a). Six identical voltage pulses of 5 ms pulse width and an amplitude of 3 V are applied to the bottom graphene electrode. The PSC through the synapse increases to 300 nA as the train of voltage pulses are applied. Following the train of 6 pulses, a read voltage of 0.2 V is applied to record the PSC. The PSC decreases to  $\sim$ 100 pA approximately 100 s after the withdrawal of the pulse train, indicating STP of the synaptic device. In Fig. 3(b), 18 identical voltage pulses (pulse width 5 ms, amplitude 3 V) are applied to the same MoS<sub>2</sub>/graphene synaptic device after it exhibits STP. The PSC again increases to 300 nA during the pulsing period. After the pulsing period, a constant read voltage of 0.2 V is applied to record a PSC of  $\sim$ 5 nA for  $10^4$  s. This indicates the stabilization of the conduction path in the MoS<sub>2</sub>/graphene device, inducing LTP. The synaptic weight update due to LTP is irreversible unless the device is RESET to its original state. This measurement also indicates that the synaptic device can retain its weight for  $>10^4$  s. The observation of LTP and STP in the same device by modulating the strength of the stimulus has been already reported in other memristive devices.<sup>24,25</sup> Now, we study LTD in a different device. Initially, the device is SET at 300 nA (Fig. S5). Six identical pulses of amplitude  $-2.5\,\mathrm{V}$  and a duration of 5 ms are applied. The PSC reduces from 209 nA to 13 nA as shown in the Fig. 3(c). After the withdrawal of the negative voltage pulses, a constant read voltage of 0.2 V is applied to record the PSC. The PSC is 500 pA [High Resistance State (HRS)], indicating that the device was reset by the applied pulses and continues to be in the HRS for at least 10<sup>4</sup> s.

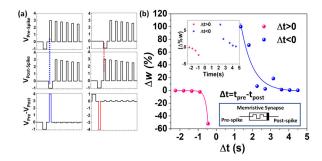

Spike timing dependent plasticity (STDP) as the biological rule of Hebbian learning can be implemented in a hardware neural network for unsupervised learning. The Hebbian learning rule attributes the temporal correlation between the prespike and the postspike signals as the cause for the synaptic weight modulation. As the timing between the firing of the prespike and the postspike signals increases, the synaptic efficacy decreases. If the prespike signal precedes the postspike

signal, the synapse potentiates, and for the reverse, the synapse undergoes depression. <sup>6,9</sup>

We now demonstrate the STDP of the MoS<sub>2</sub>/graphene memristive synapse. The pulse scheme is designed such that the overlap of the prespike and the postspike signals happens only at one instance of time. A train of voltage pulses with a decreasing amplitude is applied as the prespike and postspike signals. The resultant voltage across the synapse is the difference between the prespike and the postspike voltage amplitudes. In Fig. 4(a), the resultant pulse when the prespike signal fires at time  $\Delta t$  before the postspike is shown in blue, while the resultant pulse when the postspike signal fires before the prespike, with the time difference  $-\Delta t$ , is shown in red. The first pulse of the train is a negative voltage pulse of width 300 ms and amplitude -1 V. It is followed by positive pulses of decreasing amplitude with 150 ms pulse width. The negative pulse is wider than other pulses to compensate for the interconnect delay of the instrumentation used and to provide stabilization time for the device response. The normalized synaptic weight change,  $\Delta w$  (%) is calculated as the ratio of conductance at that overlap interval  $\Delta t$  to the maximum conductance observed. The weight change  $\Delta w$  (%) is plotted against  $\Delta t$  to obtain the STDP response curve as shown in Fig. 4(b). The MoS<sub>2</sub>/graphene synaptic device obeys the asymmetric Hebbian learning rule where the synaptic weight change decreases as the time between the firing of prespike and postspike signals increases.

Generally, the switching mechanism can either be attributed to the formation of a conductive filament through the memristive

**FIG. 4.** (a) Pulsing scheme for the STDP characterization. (b) Synaptic weight change as a function of timing difference of the prespike and the postspike signals. Inset: the same plot zoomed-in from -5  $\Delta w$  (%) to 8  $\Delta w$  (%).

material or due to trapping/detrapping of carriers at the interface of the memristive material and the electrode. Memristive switching observed in 2D materials has been associated with the formation of a conductive filament.<sup>20,26,27</sup> In ultrathin switching media, such as in monolayer MoS<sub>2</sub>, the evidence of filamentary switching is noted from the fact that the SET current does not increase with the increasing area of the memristive device.<sup>26</sup> However, we cannot rule out the influence of the Schottky barrier between graphene and MoS<sub>2</sub> from playing a major role in the resistive switching observed in our devices. The linearity observed in the weight update of the MoS<sub>2</sub>/graphene memristive synapses could be attributed to the interface mediated switching. The exact mechanism behind the resistive switching observed in the MoS<sub>2</sub>/graphene memristive synapses deserves a dedicated study, which is currently beyond the scope of this work.

In conclusion, we have fabricated MoS<sub>2</sub>/graphene memristors using large area CVD-grown MoS<sub>2</sub> and graphene. These memristive devices are nonvolatile and exhibit multiple conductance levels, which cause them to behave as synapses. Also, these devices exhibit a near linear weight update with identical input pulses, and obey the asymmetric Hebbian learning rule, which is advantageous for their applications in unsupervised learning. The devices exhibit excellent room temperature data retention for  $\sim\!10^4$  s. Additionally, the devices exhibit STP, and undergo LTP and LTD for  $>\!10^4$  s. These MoS<sub>2</sub>/graphene memristive devices show the necessary characteristics of a biological synapse, making them perfect for implementation in neuromorphic hardware for machine learning applications.

See the supplementary material for material characterization of the MoS<sub>2</sub>/graphene memristor, I-V characteristics, data retention, DC endurance, SET characteristics of the MoS<sub>2</sub>/graphene synapse prior to LTD, and comparison of MoS<sub>2</sub>/graphene memristors with other analog synapse devices.

This work was partially supported by BAE Systems through Award No. 1020180. T.R. acknowledges support of the NSF CAREER Award No. NSF-ECCS-1845331. N.C. acknowledges partial support from the Preeminent Postdoctoral Program (P3) at the University of Central Florida. A.K. acknowledges Yi Ding and Professor Laurene Tetard for the help with Raman spectroscopy.

### REFERENCES

- <sup>3</sup>C. Mead, Proc. IEEE 78(10), 1629 (1990).

- <sup>4</sup>L. Chua, IEEE Trans. Circuit Theory **18**(5), 507 (1971).

- <sup>5</sup>S. H. Jo, T. Chang, I. Ebong, B. B. Bhadviya, P. Mazumder, and W. Lu, Nano Lett. **10**(4), 1297 (2010).

- <sup>6</sup>D. Kuzum, R. G. Jeyasingh, B. Lee, and H.-S. P. Wong, Nano Lett. **12**(5), 2179 (2011)

- <sup>7</sup>D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, Nature 453(7191), 80 (2008).

- <sup>8</sup>S. Yu, B. Gao, Z. Fang, H. Yu, J. Kang, and H. S. P. Wong, Adv. Mater. **25**(12), 1774 (2013).

- <sup>9</sup>S. Yu, Y. Wu, R. Jeyasingh, D. Kuzum, and H.-S. P. Wong, IEEE Trans. Electron Devices 58(8), 2729 (2011).

- <sup>10</sup>B. L. Jackson, B. Rajendran, G. S. Corrado, M. Breitwisch, G. W. Burr, R. Cheek, K. Gopalakrishnan, S. Raoux, C. T. Rettner, A. Padilla, A. G. Schrott, R. S. Shenoy, B. N. Kurdi, C. H. Lam, and D. S. Modha, J. Emerg. Technol. Comput. Syst. 9(2), 12 (2013).

- <sup>11</sup>Y. Li, Y. Zhong, L. Xu, J. Zhang, X. Xu, H. Sun, and X. Miao, Sci. Rep. 3, 1619 (2013)

- <sup>12</sup>M. Suri, O. Bichler, D. Querlioz, O. Cueto, L. Perniola, V. Sousa, D. Vuillaume, C. Gamrat, and B. DeSalvo, in IEEE International Electron Devices Meeting (2011).

- <sup>13</sup>A. Prakash, J. Park, J. Song, J. Woo, E.-J. Cha, and H. Hwang, IEEE Electron Device Lett. 36(1), 32 (2015).

- <sup>14</sup>L. Zhang, R. Huang, M. Zhu, S. Qin, Y. Kuang, D. Gao, C. Shi, and Y. Wang, IEEE Electron Device Lett. 31(9), 966 (2010).

- <sup>15</sup>S. Yu, Proc. IEEE **106**(2), 260 (2018).

- <sup>16</sup>A. J. Arnold, A. Razavieh, J. R. Nasr, D. S. Schulman, C. M. Eichfeld, and S. Das, ACS Nano 11(3), 3110 (2017).

- <sup>17</sup>J. Jiang, J. Guo, X. Wan, Y. Yang, H. Xie, D. Niu, J. Yang, J. He, Y. Gao, and Q. Wan, Small 13(29), 1700933 (2017).

- <sup>18</sup>V. K. Sangwan, H.-S. Lee, H. Bergeron, I. Balla, M. E. Beck, K.-S. Chen, and M. C. Hersam, Nature 554(7693), 500 (2018).

- <sup>19</sup>Y. Shi, X. Liang, B. Yuan, V. Chen, H. Li, F. Hui, Z. Yu, F. Yuan, E. Pop, and H.-S. P. Wong, Nat. Electron. 1(8), 458 (2018).

- <sup>20</sup>H. Zhao, Z. Dong, H. Tian, D. DiMarzi, M. G. Han, L. Zhang, X. Yan, F. Liu, L. Shen, and S. J. Han, Adv. Mater. 29(47), 1703232 (2017).

- <sup>21</sup>J. Chan, A. Venugopal, A. Pirkle, S. McDonnell, D. Hinojos, C. W. Magnuson, R. S. Ruoff, L. Colombo, R. M. Wallace, and E. M. Vogel, ACS Nano 6(4), 3224 (2012).

- <sup>22</sup>H. Tian, W. Mi, H. Zhao, M. A. Mohammad, Y. Yang, P.-W. Chiu, and T.-L. Ren, Nanoscale 9(27), 9275 (2017).

- <sup>23</sup>P.-Y. Chen, B. Lin, I.-T. Wang, T.-H. Hou, J. Ye, S. Vrudhula, J.-S. Seo, Y. Cao, and S. Yu, in IEEE/ACM International Conference on Computer-Aided Design (ICCAD) (2015).

- <sup>24</sup>T. Ohno, T. Hasegawa, T. Tsuruoka, K. Terabe, J. K. Gimzewski, and M. Aono, Nat. Mater. 10, 591 (2011).

- <sup>25</sup>T. Chang, S.-H. Jo, and W. Lu, ACS Nano 5(9), 7669 (2011).

- <sup>26</sup>R. Ge, X. Wu, M. Kim, J. Shi, S. S. Sonde, L. Tao, Y. Zhang, J. Lee, and D. Akinwande, Nano Lett. 18, 434 (2017).

- <sup>27</sup>H. Tian, L. Zhao, X. Wang, Y.-W. Yeh, N. Yao, B. P. Rand, and T.-L. Ren, ACS Nano 11(12), 12247 (2017).

<sup>&</sup>lt;sup>1</sup>A. W. Burks, in International Conference on Parallel Processing (1986).

<sup>&</sup>lt;sup>2</sup>B. Urgaonkar and P. Shenoy, IEEE Trans. Parallel Distrib. Syst. 15(1), 2 (2004).