## High-yield fabrication method for high-frequency graphene devices using titanium sacrificial layers

Panagiotis C. Theofanopoulos, Scott Ageno, Yuqi Guo, Suneet Kale, Qing Hua Wang, and Georgios C. Trichopoulos

Citation: Journal of Vacuum Science & Technology B 37, 041801 (2019); doi: 10.1116/1.5098324

View online: https://doi.org/10.1116/1.5098324

View Table of Contents: https://avs.scitation.org/toc/jvb/37/4

Published by the American Vacuum Society

#### **ARTICLES YOU MAY BE INTERESTED IN**

Remote plasma-assisted low-temperature large-area graphene synthesis

Journal of Vacuum Science & Technology B **37**, 041201 (2019); https://doi.org/10.1116/1.5093241

One-step transfer printing of patterned nanogap electrodes

Journal of Vacuum Science & Technology B 37, 040602 (2019); https://doi.org/10.1116/1.5100560

High temperature plasma immersion ion implantation using hollow cathode discharges in small diameter metal tubes

Journal of Vacuum Science & Technology B 37, 042902 (2019); https://doi.org/10.1116/1.5092435

Interface trap characterization of AIN/GaN heterostructure with Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, and HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> dielectrics Journal of Vacuum Science & Technology B **37**, 041203 (2019); https://doi.org/10.1116/1.5094174

Validation of current formula for a metallic nanotipped field emitter

Journal of Vacuum Science & Technology B 37, 040603 (2019); https://doi.org/10.1116/1.5110207

Maskless random antireflective nanotexturing of single crystal SiC

Journal of Vacuum Science & Technology B 37, 040601 (2019); https://doi.org/10.1116/1.5108513

# High-yield fabrication method for high-frequency graphene devices using titanium sacrificial layers

Panagiotis C. Theofanopoulos, <sup>1</sup> Scott Ageno, <sup>2</sup> Yuqi Guo, <sup>3</sup> Suneet Kale, <sup>4</sup> Qing Hua Wang, <sup>3</sup> and Georgios C. Trichopoulos <sup>1</sup>

<sup>1</sup>School of Electrical, Computer and Energy Engineering, Arizona State University, Tempe, Arizona 85287

<sup>2</sup>NanoFab, Arizona State University, Tempe, Arizona 85287

(Received 1 April 2019; accepted 11 June 2019; published 28 June 2019)

The authors present a fabrication process for the development of high-frequency (>30 GHz) on-wafer graphene devices with the use of titanium sacrificial layers. Graphene patterning requires chemical processes that have deleterious effects on graphene resulting in very low yield. The authors prevent delamination of the delicate graphene from the substrate during the fabrication steps by depositing a blanketing 30 nm titanium layer at the beginning of the process. Additionally, titanium is a low cost, hazardless, and well-established material in the semiconductor industry and, therefore, constitutes an attractive solution for graphene protection. With the proposed blanketing approach, the authors obtain more than 90% device yield, allowing the development of graphene-based reconfigurable, large-area, high-frequency topologies such as antenna arrays. Without the use of this titanium sacrificial layer, they show that the expected yield plummets. In addition, they validate the proposed fabrication procedure through on-wafer measurements in the 220–330 GHz range. *Published by the AVS.* https://doi.org/10.1116/1.5098324

#### I. INTRODUCTION

A significant research effort has been devoted to developing dynamically reconfigurable millimeter-wave/terahertz (mmW/THz) devices (operating in the 30 GHz to 1 THz frequency range) that has led to various novel configurations for both imaging and communication applications. 1-17 In general, reconfigurability is achieved using tunable capacitors, diodes, and tunable materials 4 (e.g., indium tin oxide). In recent years, an increased research effort has been steered toward reconfigurable switches and other devices that exploit the tunable electromagnetic properties (e.g., conductivity) of 2D materials, including graphene and molybdenum disulfide (MoS<sub>2</sub>).<sup>5,6</sup> These materials exhibit reconfigurable properties that are regulated with the use of external biasing, as in the case of field-effect-transistors. Moreover, these materials are very attractive for broadband applications, since their tunable properties are expected to be uniform across the electromagnetic spectrum. 6-11 Nonetheless, most of the works concerning the development and fabrication of radiofrequency (RF) graphene devices are either limited to low frequencies (<100 GHz)<sup>6-8</sup> or used for terahertz "out-of-plane" propagation<sup>9–11</sup> applications. Furthermore, the graphene sheet resistances reported in these works reflect either single frequency responses or averaged values, thus concealing the actual graphene properties over a broad range of frequencies.

Herein, we focus on "in-plane" topologies where electromagnetic waves travel across the devices (e.g., transmission lines), in contrast to "out-of-plane" devices where waves travel through the structure (e.g., lenses). In-plane devices are commonly integrated into antenna arrays' RF-front-end networks and are used to feed the antennas using a complex network of components including switches, phase-shifters,

and power dividers.<sup>16</sup> To achieve reconfigurability of these components, topologies including graphene have been proposed;<sup>17,18</sup> however, they are predominantly studied using full-wave simulations and theoretical models, due to the challenges in the fabrication and on-wafer characterization. Specifically, to implement graphene-loaded, large-scale reconfigurable antenna arrays of hundreds or even thousands of elements, high-yield fabrication processes are needed. However, the delicate nature of graphene often leads to its delamination from the substrate during standard nanofabrication processes, including development and lift-off. Therefore, the proliferation of large-scale graphene devices for RF applications is hindered.

Another important challenge toward developing on-wafer RF graphene devices is metal losses. Namely, to achieve low losses in these wavelengths, the metal thickness should be larger than the skin depth. 16 Specifically, in the case of RF-front-end networks that are used to feed antenna arrays, the circuitry can extend up to a few millimeters; therefore, to obtain high-frequency, low-loss reconfigurable devices, we need to use thick metallic layers. For example, at 300 GHz the skin depth of gold (Au) is 140 nm; hence, the Au thickness for a 300 GHz transmission line should be at least 280 nm to avoid excess ohmic losses. However, developing thick metal layers ( $>0.3 \mu m$ ) with integrated graphene patches is nontrivial, due to the compatibility of graphene with the chemicals used during the fabrication steps. To fabricate thick metal layers, it is preferable to use double layer lift-off photoresists to achieve fine resolution with higher yield and easier processes; 19 however, the chemicals used during this process (e.g., PG Remover or 400 T) significantly increase the risk of graphene delamination.

2166-2746/2019/37(4)/041801/6/\$30.00

<sup>&</sup>lt;sup>3</sup>Materials Science and Engineering, School for Engineering of Matter, Transport and Energy, Arizona State University, Tempe, Arizona 85287

<sup>&</sup>lt;sup>4</sup>School of Molecular Sciences, Arizona State University, Tempe, Arizona 85287

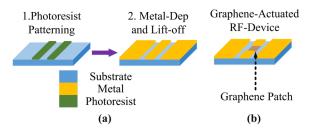

Fig. 1. (a) Steps for fabricating a metal CPW line using standard nanofabrication procedures. (b) Graphene-actuated RF-switch.

In Fig. 1(a), we depict the steps for the fabrication of coplanar-waveguide (CPW) transmission line using thick metal layers: (1) spin coat a double layer photoresist (3-4 times the metal thickness), pattern it using photolithography followed by development and (2) deposit a metal layer using electron-beam evaporation deposition (EVD) and pattern it using lift-off. The aforementioned process is a well-known procedure used for the development of high-frequency passive RF devices. On the contrary, in Fig. 1(b), we present a graphene-actuated RF-device configuration with a graphene patch intersecting the center conductor of the CPW. To develop this configuration, we have to cover the substrate with a delicate graphene sheet and then pattern the metal topology using the aforementioned steps. However, the wet processes of development and lift-off used for metal pattering often lead to graphene delamination due to its delicate nature. 20,21 This becomes a significant roadblock for largeformat arrays of devices, including reconfigurable metasurfaces and phased arrays (e.g., Refs. 2, 3, 14, and 15), where yield is crucial.

In this work, we propose a high-yield fabrication procedure that uses titanium (Ti) sacrificial layers to cover graphene during the fabrication procedure and prevent delamination. In addition, using Ti layers cleans the graphene monolayer leading to intrinsic performance.<sup>20</sup> Hence, we are able to develop large-scale mmW/THz graphene reconfigurable devices using a high-yield fabrication process. A similar procedure using yttrium (Y) sacrificial layers has been proposed recently;<sup>21</sup> although this previous work presents promising results, the use of a rare element like Y is not compatible for the development of a high-yield, high-throughput standardized process. Namely, such processes demand low-cost materials, but Y is typically six times more expensive than Ti. In addition, Ti is a well-known material used in industrial procedures; hence, no adaptation is needed for the existing equipment to the new material properties (melting point, sputtering profiles, etc.). Moreover, the fabrication residues of Y and its oxides are damaging to human health and the environment in contrast to Ti.<sup>22,23</sup> Hence, we selected Ti instead of Y as a sacrificial layer for our high-yield fabrication process.

#### **II. PROPOSED FABRICATION METHOD**

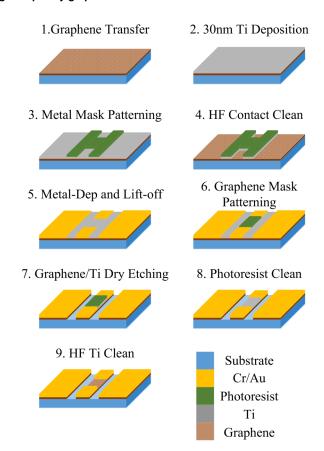

The fabrication process we follow to develop the graphene devices is illustrated in Fig. 2. Initially, we clean the high resistivity (>10 000  $\Omega\,cm$ ) silicon wafer that serves as the substrate and is commonly used in high-frequency RF

Fig. 2. Proposed fabrication procedure for the development of on-wafer mmW/THz graphene devices with a Ti sacrificial layer to protect the graphene.

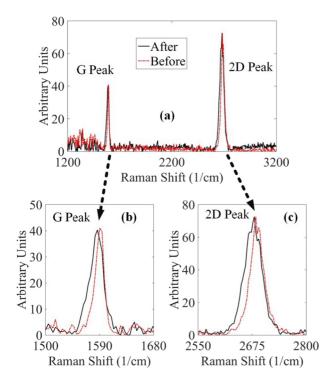

applications, using a 1:10 hydrofluoric acid (HF):deionized (DI) water solution. In this step, we remove the native oxide layer of the silicon surface before the graphene transfer and passivate the silicon surface with hydrogen (H) atoms. The advantages of this clean are twofold. Firstly, the H-passivated surface minimizes the effects of the graphenesilicon interaction leading to intrinsic graphene performance.<sup>24</sup> Secondly, the native oxide of silicon is hydrophilic;<sup>25</sup> hence, by removing and replacing it with a hydrophobic H-passivated surface, we minimize the risk of delaminating the transferred graphene monolayer during the wet processes. In addition, transferring the graphene onto a hydrophobic surface hinders doping and other effects that undermine the graphene performance.<sup>26</sup> After the cleaning is completed, we transfer a graphene monolayer onto the silicon substrate using wet transfer<sup>27</sup> (this step was carried out by ACS Materials<sup>28</sup>). The full processing steps in our new method are illustrated in Fig. 2. The Raman spectrum of the graphene monolayer on high resistivity silicon is shown in Fig. 3 (acquired on a WITec alpha300R system with 532 nm excitation laser) and shows the clear G and 2D peaks for monolayer graphene, and no D peak suggesting that there are very few defects. After the processing steps, both the 2D and G peaks are slightly shifted toward lower wavenumbers, suggesting a lower degree of doping.<sup>29</sup> In addition, the widths of both peaks have slightly increased, which can be associated with an increase in the spatial variation of doping.<sup>29</sup>

Fig. 3. (a) Raman spectra of the graphene monolayer acquired before and after the fabrication procedure focusing on the (b) G and (c) 2D peaks (60 s total accumulation time).

Even though the wet transfer procedure is robust, due to the use of poly(methyl methacrylate), residual polymer, and other particles tend to adhere to the graphene monolayer leading to deteriorated performance.<sup>21</sup> Hence, using a Ti sacrificial layer also helps remove those residual contaminants and achieve intrinsic performance.<sup>20</sup> After the transfer is completed, we deposit a 30 nm Ti sacrificial layer using EVD at a rate of 1 Å/s (chamber pressure less than  $5 \times 10^{-7}$  mTorr). We used a reasonably thick (>20 nm) blanketing layer to ensure uniform coverage, thus minimizing graphene exposure to the strong chemicals used during the fabrication procedure that might lead to its delamination. This step could also be carried out at the beginning of the process, before the graphene monolayer transfer.<sup>30</sup> Then, we spin coat the double layer photoresist (MIR-701 and LOR-10A) for the metal mask on the wafer, expose at 63 m J/cm<sup>2</sup> using 365 nm light, and develop using AZ-300MIF (45–60 s). The two layers of the photoresist develop in different rates in the base solution, creating an undercut that is necessary to perform the lift-off process that follows.<sup>19</sup> Afterward, to clean the Ti from the metal contact areas, we submerge the wafer in a 1:72 HF:DI water solution for 2 min.

Next, we deposit the Cr/Au (10 nm/300 nm) metal layer with a rate of 1 and 1.4 Å/s, respectively (chamber pressure less than  $5\times 10^{-7}$  mTorr). After the deposition, we lift-off the metal mask using heated Remover PG at 80 °C. Thereafter, we spin coat the double layer photoresist (MIR-701 and LOR-10A) with the mask to pattern the graphene into rectangular patches, expose at 63 m J/cm² using 365 nm light, and develop using AZ-300MIF (45–60 s).

After the dry etching, the hardened fluorinated single layer photoresist cannot be removed completely without the use of 400 T, which is an aggressive tetramethylammonium hydroxide based chemical that delaminates graphene even when covered with a 30 nm Ti layer. Therefore, instead of using a single layer of photoresist, which is common in dry etching procedures, we decided to use a double layer photoresist, 31 which is easily removed by Remover PG. After the development of the graphene patch mask, we use dry etching with SF<sub>6</sub>/Ar (20/5 sccm) plasma (75 W, 10 mTorr) for 7 min. In Fig. 2 (step 6), we show that the photoresist covers only the graphene patches, since the Cr/Au layer is not etched by the plasma, hence acting as a self-aligned hard mask. In addition, the DC-bias of the dry etching procedure was optimized to minimize the resputtering of the gold, while retaining an acceptable etching rate. After the dry etching is completed, we clean the remaining photoresist using a fast (less than a minute) O<sub>2</sub> plasma dry-etch and heated Remover PG at 80 °C. Finally, we remove the Ti sacrificial layer by submerging the wafers in a 1:36 HF:DI water solution for 2 min. In Fig. 3, we depict a representative Raman spectrum of the monolayer graphene pieces on the final devices, establishing the fabrication process. The G and the 2D peaks before and after the full fabrication process are similar in height and position, indicating no significant changes in doping, while there is no D peak, indicating that the graphene remains intact and free of defects.<sup>32</sup>

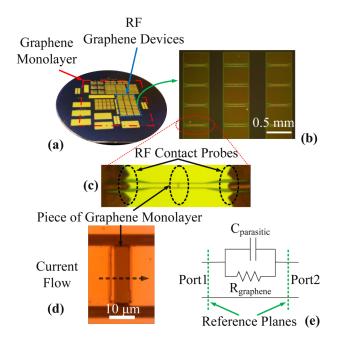

We transfer the graphene at the beginning of the process, to increase the overlapping metal-graphene area achieving good ohmic contact and providing mechanical rigidity by

Fig. 4. (a) Photograph of the fabricated on-wafer RF devices. (b) An optical microscope image of the wafer depicting an array of the developed graphene-based devices. (c) An optical microscope image of a single graphene device during the high-frequency RF-measurements. (d) An optical image of a single graphene patch with dimensions  $5 \times 20 \,\mu\text{m}^2$  (four squares for the current flow). (e) The equivalent R-C model of the graphene devices.

robustly anchoring the graphene on the substrate. The final wafer is shown in Fig. 4(a), where the total graphene dimensions are  $2 \times 2 \text{ cm}^2$  and the wafer has more than 280 graphene RF devices. Also in Figs. 4(b)–4(d), we depict a fabricated on-wafer CPW transmission line that has a small piece of monolayer graphene  $(5 \times 20 \, \mu\text{m}^2)$  intersecting the center conductor. These devices are used to characterize the graphene properties (namely, the sheet resistance as a function of frequency) in the 220–330 GHz band and provide an estimate of the yield of the proposed fabrication process.

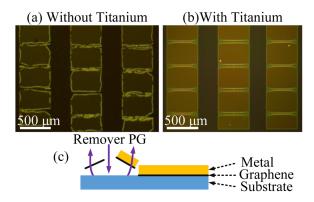

To demonstrate the severity of graphene delamination during the standard no-Ti nanofabrication process, in Fig. 5(a) we depict the resulting wafer where the lift-off solution (Remover PG) clearly delaminates the graphene monolayer [Fig. 5(c)], leading to a nearly 0% yield.

### III. HIGH-FREQUENCY GRAPHENE MEASUREMENTS

To validate the outcome of our procedure, we carry out on-wafer, in-plane measurements of the graphene sheet resistance at the 220–330 GHz band for the first time. The acquired data are compared with related works that either measure the graphene characteristics in lower frequencies using in-plane topologies (transmission lines) or characterize the out-of-plane properties using quasi-optical setups. 7–10 However, none of the aforementioned studies presents the graphene sheet resistance (or conductance) over a wide frequency range as in our present work. Specifically, the previously published measurement results are obtained over wide frequency ranges, but the reported data refer to either single frequency responses or averaged values (over frequency). These comparisons are summarized in Table I.

To characterize the in-plane graphene sheet resistance, we devised the topology shown in Figs. 4(c) and 4(d), consisting of a CPW line with a piece of monolayer graphene, embedded as the device-under-test.

The measurements were carried out using a Rohde & Schwarz network analyzer that probed two Virginia Diodes

Fig. 5. (a) Optical microscope images of an array of graphene devices for the standard no-Ti wafer after the lift-off procedure and (b) the final wafer with the use of Ti sacrificial layer. (c) Graphene delamination during lift-off in Remover PG solution (metal pattering), leading to excessive deformation of the metal layer.

TABLE I. Reported graphene sheet resistances.

| Sheet resistance $(\Omega/\Box)$ | Frequency range (GHz) | Measurement configuration | Reference |

|----------------------------------|-----------------------|---------------------------|-----------|

| 1100                             | 1–20                  | In-plane                  | 8         |

| 1260                             | DC-110                | In-plane                  | 7         |

| 1307                             | 220-330               | In-plane                  | This work |

| 1600                             | 200-1000              | Out-of-plane              | 9         |

| 1490                             | 250–2000              | Out-of-plane              | 10        |

Inc. frequency extenders covering the 220–330 GHz band. The RF signal was then coupled on the CPW line using GGB contact probes [Fig. 4(c)]. To accurately extract the graphene sheet resistance without including the errors from the contact probes, mismatches, etc., we performed a

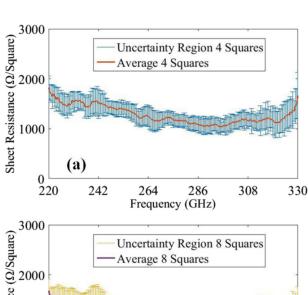

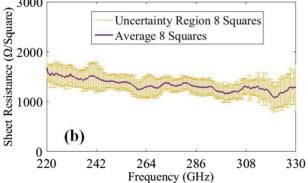

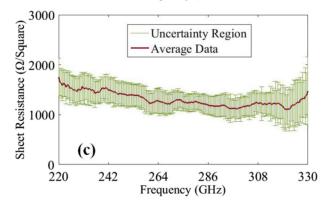

Fig. 6. Acquired sheet resistance of graphene in the 220–330 GHz range: (a) four squares, (b) eight squares, and (c) averaged data. The uncertainty region in all figures includes both the measurement error and the device variability.

wideband thru-reflect-line calibration across the 220-330 GHz region.<sup>33</sup> In addition, we measured the device without including the graphene to extract the parasitic capacitance [Fig. 4(e)]. Namely, we model the device as a parallel circuit consisting of a resistance that represents the monolayer graphene sheet and a capacitor that accounts for the high capacitive coupling [Fig. 4(e)]. Two different sets of devices were developed with four  $(5 \times 20 \,\mu\text{m}^2)$  and eight  $(3 \times 24 \,\mu\text{m}^2)$  and  $5 \times 40 \,\mu\text{m}^2$ ) parallel squares for the current flow. Using different configurations of graphene dimensions, we are able to extract the graphene sheet resistances for different capacitance values, thus establishing our measurement process. Specifically, the total resistance for the three different groups of devices differs, since the capacitance depends on the CPW discontinuity's dimensions. However, the monolayer graphene's sheet resistance should be identical regardless of the capacitance.

The calculated graphene sheet resistances for both the four and eight square devices are given in Fig. 6. The graphene sheet resistance is almost uniform across the entire bandwidth. In Table I, the average measured sheet resistance value is presented along with those found in the literature, validating our high-yield fabrication and measurements procedure. To the best of our knowledge, previous works that have measured the graphene characteristics using in-plane propagation devices (i.e., transmission lines, etc.) are limited to lower frequencies and do not apply proper calibration (only numerical de-embedding) and/or use graphene multilayers.<sup>6,7</sup> On our prototype wafer, we measured 39 functional devices out of 42 in total, leading to a 92% yield. Even though we fabricated more than 280 devices, extensive measuring using RF contact probes leads to their degradation, so we decided to measure only 42 devices.

#### IV. SUMMARY AND CONCLUSIONS

Concluding, we presented a high-yield fabrication procedure for the development of on-wafer mmW/THz graphene devices. Using the proposed procedure, we achieved 92% fabrication yield enabling the implementation of large-format, multiwavelength reconfigurable graphene devices, including metasurfaces and phased arrays. To achieve high functional device yield, we covered the graphene monolayer with a Ti sacrificial layer throughout the nanofabrication procedure preventing delamination. In addition, we characterized the in-plane graphene sheet resistance in the 220–330 GHz band for the first time. The measured data are in good agreement with the existing literature, verifying the robustness of the proposed fabrication method.

Future work includes optimization of the fabrication steps to acquire even higher yields. Specifically, we aim to optimize the lift-off process that is a long and aggressive procedure with the use of a heated chemical (PG Remover), hence minimizing graphene delamination even further. Alternatively, we can change the thickness of the protective Ti sacrificial layer to provide further protection during the lift-off process. A limiting aspect of this work is metal

degradation at the landing pads due to the contact force applied by the RF probes and the poor metal to graphene adhesion. Namely, after a few landings (4–5) the metal completely delaminates, preventing any further access to the RF graphene devices. In future revisions of the process, the metal contact degradation can be mitigated by adding another fabrication step that cleans the landing areas from graphene using dry etching, thus providing rigid metal to substrate adhesion. Finally, although this work has focused on high resistivity silicon substrates, the method can be extended to wafers that are coated with thin insulating layers (e.g., aluminum oxide and silicon nitride).

#### **ACKNOWLEDGMENTS**

For their valuable contribution to this work, we would like to acknowledge the use of facilities within the ASU NanoFab supported in part by the NSF program (No. NNCI-ECCS-1542160).

- <sup>1</sup>M. Haghzadeh and A. Akyurtlu, J. Appl. Phys. **120**, 184901 (2016).

- <sup>2</sup>O. Yurduseven, D. L. Marks, T. Fromenteze, and D. R. Smith, Opt. Express **26**, 5281 (2018).

- <sup>3</sup>A. Forouzmand and H. Mosallaei, J. Opt. **18**, 125003 (2016).

- <sup>4</sup>P. C. Theofanopoulos, C. S. Lavranos, K. E. Zoiros, G. C. Trichopoulos, G. Granet, and G. A. Kyriacou, IEEE Trans. Microw. Theory Tech. **65**, 36 (2017).

- <sup>5</sup>M. Kim, S. Park, A. Sanne, S.K. Banerjee, and D. Akinwande, *2018 IEEE/MTT International Microwave Symposium (IMS)*, Philadelphia, 10–15 June 2018 (IEEE, New York, 2018), pp. 352–354.

- <sup>6</sup>D. Fadil, W. Wei, M. Deng, S. Fregonese, W. Strupinski, E. Pallecchi, and H. Happy, 2018 IEEE/MTT International Microwave Symposium (IMS), Philadelphia, 10–15 June 2018 (IEEE, New York, 2018), pp. 228–231.

- <sup>7</sup>H. S. Skulason, H. V. Nguyen, A. Guermoune, V. Sridharan, M. Siaj, C. Caloz, and T. Szkopek, Appl. Phys. Lett. **99**, 153504 (2011).

- <sup>8</sup>L. Pierantoni, D. Mencarelli, M. Bozzi, R. Moro, S. Moscato, L. Perregrini, F. Micciulla, A. Cataldo, and S. Bellucci, IEEE Trans. Microw. Theory Tech. 63, 2491 (2015).

- <sup>9</sup>J. Liu et al., Opt. Lett. 41, 816 (2016).

- <sup>10</sup>N. Kakenov, M. S. Ergoktas, O. Balci, and C. Kocabas, 2D Mater. 5, 035018 (2018).

- <sup>11</sup>M. M. Jadidi, A. B. Sushkov, R. L. Myers-Ward, A. K. Boyd, K. M. Daniels, D. K. Gaskill, M. S. Fuhrer, H. D. Drew, and T. E. Murphy, Nano Lett. 15, 7099 (2015).

- <sup>12</sup>W. Fuscaldo, P. Burghignoli, P. Baccarelli, and A. Galli, IEEE Trans. Antennas Propag. 65, 1651 (2017).

- <sup>13</sup>M. Tamagnone and J. R. Mosig, IEEE Antennas Wirel. Propag. Lett. 15, 1549 (2016).

- <sup>14</sup>X. Wang, W. Zhao, J. Hu, and W. Yin, IEEE Trans. Nanotechnol. 14, 62 (2015)

- <sup>15</sup>P. Chen and A. Alù, IEEE Trans. TeraHertz Sci. Technnol. **3**, 748 (2013).

- <sup>16</sup>D. M. Pozar, *Microwave Engineering*, 2nd ed. (Wiley, New York, 1998).

- <sup>17</sup>P. Chen, C. Argyropoulos, and A. Alû, IEEE Trans. Antennas Propag. 61, 1528 (2013).

- <sup>18</sup>Y. Wu, M. Qu, and Y. Liu, Sci. Rep. 6, 31760 (2016).

- <sup>19</sup>J. Golden, H. Miller, D. Nawrocki, and J. Ross, "Optimization of bi-layer lift-off resist process," in *CS Mantech, Technical Digest*, (MicroChem, 2009).

- <sup>20</sup>C. A. Joiner, T. Roy, Z. R. Hesabi, B. Chakrabarti, and E. M. Vogel, Appl. Phys. Lett. **104**, 223109 (2014).

- <sup>21</sup>N. C. Wang, E. A. Carrion, M. C. Tung, and E. Pop, Appl. Phys. Lett. 110, 223106 (2017).

- <sup>22</sup>K. T. Rim, K. H. Koo, and J. S. Park, Saf. Health Work 4, 12 (2013).

- <sup>23</sup>D. B. Warheit, C. M. Sayes, K. L. Reed, and K. A. Swain, Pharmacol. Ther. **120**, 35 (2008).

- <sup>24</sup>Y. Xu, K. T. He, S. W. Schmucker, Z. Guo, J. C. Koepke, J. D. Wood, J. W. Lyding, and N. R. Aluru, Nano Lett. 11, 2735 (2011).

- <sup>30</sup>A. Matruglio, S. Nappini, D. Naumenko, E. Magnano, F. Bondino, M. Lazzarino, and S. D. Zilio, Carbon N. Y. 103, 305 (2016).

- <sup>31</sup>B. Gorissen, C. Van Hoof, D. Reynaerts, and M. De Volder, Microsystems & Nanoengineering **2**, 16045 (2016).

32A. C. Ferrari and D. M. Basko, Nat. Nanotechnol. **8**, 235 (2013).

- <sup>33</sup>D. Rytting, Network Analyzer Error Models and Calibration Methods (Agilent Technologies, Santa Clara, California, 1998).

<sup>&</sup>lt;sup>25</sup>X. Xi, J. Shi, S. Maghsoudy-Louyeh, and B. R. Tittmann, AIP Conf. Proc. **1211**, 1493 (2010).

<sup>&</sup>lt;sup>26</sup>M. Lafkioti, B. Krauss, T. Lohmann, U. Zschieschang, H. Klauk, K. v. Klitzing, and J. H. Smet, Nano Lett. 10, 1149 (2010).

<sup>&</sup>lt;sup>27</sup>Y. Chen, X.-L. Gong, and J.-G. Gai, Adv. Sci. **3**, 1500343 (2016). <sup>28</sup>See: https://www.acsmaterial.com/materials/graphene-series.html.

<sup>&</sup>lt;sup>29</sup>Q. H. Wang et al., Nat. Chem. **4**, 724 (2012).