SUBMITTED TO IEEE ELECTRON DEVICE LETTERS

# GaN HEMTs on Si with Regrown Contacts and Cutoff/Maximum Oscillation Frequencies of 250/204 GHz

Lei Li, Kazuki Nomoto, *Member, IEEE*, Ming Pan, *Member, IEEE*, Wenshen Li, Austin Hickman, Jeffrey Miller, Kevin Lee, Zongyang Hu, Samuel James Bader, Soo Min Lee, James C.M. Hwang, *Life Fellow, IEEE*, Debdeep Jena, *Senior Member, IEEE*, and Huili Grace Xing, *Senior Member, IEEE*

Abstract—This work demonstrates the high-frequency and high-power performance capacity of GaN high electron mobility transistors (HEMTs) on Si substrates. Using a T-gate and  $n^{++}$ -GaN source/drain contacts, the InAlN/GaN HEMT with a gate length of 55 nm and a source-drain spacing of 175 nm shows a maximum drain current  $I_{D,MAX}$  of 2.8 A/mm and a peak transconductance  $g_m$ of 0.66 S/mm. The same HEMT exhibits a forward-current-gain cutoff frequency  $f_T$  of 250 GHz and a maximum frequency of oscillation  $f_{MAX}$  of 204 GHz. The  $I_{D,MAX}$ , peak  $g_m$  and  $f_T$ - $f_{MAX}$ product are among the best reported for GaN HEMTs on Si, which are very close to the state-of-the-art depletion-mode GaN HEMTs on SiC without a back barrier. Given the low cost of Si and the high compatibility with CMOS circuits, GaN HEMTs on Si prove to be particularly attractive for cost-sensitive applications.

*Index Terms*—HEMTs, millimeter wave transistors, T-gate, gallium nitride, silicon.

## I. INTRODUCTION

GAN high electron mobility transistors (HEMTs) have high breakdown voltages, high two-dimensional electron gas (2DEG) densities, and a high electron saturation velocity. These properties make them ideal for high-power and highfrequency applications, such as switches in power systems and amplifiers in wireless communication systems. To date, the highest speed GaN HEMTs are demonstrated on SiC substrates,

Manuscript received on January 1, 2020; revised on February 20, 2020. This work was supported in part by the Semiconductor Research Corporation Joint University Microelectronics Program, and Air Force Office of Scientific Research under Grant FA9550-17-1-0048. This work uses the Cornell NanoScale Facility, Cornell Center for Material Research, and CESI Shared Facilities partly sponsored by MRSEC program (DMR-1719875) and MRI DMR-1338010, as well as Kavli Institute at Cornell.

L. Li, K. Nomoto, A. Hickman, K. Lee, J. Miller, Z. Hu, and W. Li are with the School of Electrical and Computer Engineering, Cornell University, Ithaca, NY 14853 USA (e-mail: Il886@cornell.edu).

M. Pan and S. M. Lee are with Veeco Instruments Inc., Somerset, NJ 08873 USA (e-mail: mpan@veeco.com).

S. J. Bader is with the School of Applied and Engineering Physics, Cornell University, Ithaca, NY 14853 USA.

J. C. M. Hwang is with the Department of Materials Science and Engineering, Cornell University, Ithaca, NY 14853 USA.

D. Jena and H. G. Xing are with the School of Electrical and Computer Engineering, Department of Materials Science and Engineering, and Kavli Institute for Nanoscience, Cornell University, Ithaca, NY 14853 USA. all of which employ regrown ohmic contacts to minimize source/drain resistances.

1

For double-heterostructure HEMTs on SiC, a forward current gain cutoff frequency  $f_T$  of 454 GHz and a maximum frequency of oscillation  $f_{MAX}$  of 444 GHz were realized in D-mode AlN/GaN/AlGaN HEMTs with a 20-nm T-gate and an ultra-scaled source-drain distance  $L_{SD}$  of 120 nm [1]. These devices show an average electron velocity as high as  $2.8 \times 10^7$  cm/s, benefiting from enhanced velocity overshoot. Given the large electron-phonon interaction in GaN [2], it is necessary to scale the drain-gate distance below 70 nm in order to observe velocity overshoot, thus termed as ultra-scaled  $L_{SD}$  [3].

For HEMTs on SiC without a back barrier, the highest  $f_T$  of 400 GHz was reported with a  $f_{MAX}$  of 33 GHz at room temperature ( $f_T/f_{MAX}$  increased to 430/36 GHz at 77 K) in D-mode InAlN/GaN HEMTs employing a 30-nm I-gate and a  $L_{SD}$  of 270 nm [4]; the highest balanced  $f_T/f_{MAX}$  of 230/300 GHz in un-scaled HEMTs were reported employing a quaternary barrier InAlGaN with a 40-nm T-gate and a long  $L_{SD}$  of 800 nm [5], showing an average electron velocity of  $1.36 \times 10^7$  cm/s; the highest balanced  $f_T/f_{MAX}$  of 302/301 GHz were realized in D-mode InAlN/GaN HEMTs with a 27-nm T-gate and an ultra-scaled  $L_{SD}$  of 140 nm [6].

Although GaN HEMTs on SiC have shown excellent performance, their large-scale applications are limited by the high cost and small size (typically 100-mm or 4-inch in diameter) of SiC. In comparison, GaN HEMTs on Si can reduce the cost with a moderate penalty on performance. For example, GaN HEMTs on up to 12-inch (300-mm) Si substrates promise much lower cost than GaN on SiC, yet much better performance

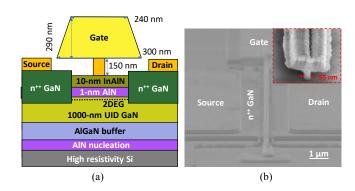

Fig. 1. (a) Schematic HEMT cross section, no back barrier is employed. (b) SEM image of a completed GaN HEMT on Si. Inset shows details of the T gate.

## SUBMITTED TO IEEE ELECTRON DEVICE LETTERS

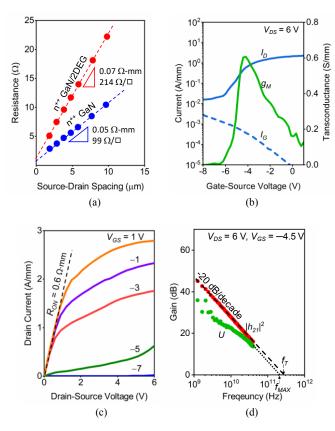

Fig. 2. (a) TLM measurement results. (b) Transfer characteristics, (c) output characteristics, and (d) cutoff frequencies measured on the same GaN HEMT on Si with a 55-nm T-gate and  $L_{SD}$  of 175 nm (HEMT A in Table I).

than laterally-diffused metal-oxide semiconductor (LDMOS) Si-FETs.

To this end, high-speed GaN HEMTs on Si have been pursued, nearly all of which use device structures without a back barrier. Marti et al. reported a balanced  $f_T/f_{MAX}$  of 141/232 GHz employing 50-nm T-gate [7]. Since both  $f_T$  and  $f_{MAX}$  are critical to high-frequency and high-power performance, the combined figure of merit  $(f_T \cdot f_{MAX})^{1/2} = 181$  GHz serves as a convenient gauge for the performance of GaN HEMTs on Si. Recently, there are reports of higher  $f_T$  for GaN HEMTs on Si [8]–[10]. However, their  $(f_T \cdot f_{MAX})^{1/2}$  values are actually lower than 181 GHz because  $f_{MAX}$  is suppressed by high gate resistances.

In this work, by using a T-shaped gate and regrown  $n^{++}$ -GaN source and drain contacts, we reduced gate and source/drain resistances thus improving  $f_{MAX}$  to 204 GHz with a gate length of 55 nm, while keeping  $f_T$  at 250 GHz for GaN HEMTs on Si without a back barrier. This amounts to a record  $(f_T \cdot f_{MAX})^{1/2}$  of 226 GHz among GaN HEMTs on Si, showing that the performance of GaN HEMTs on Si is approaching that of GaN HEMTs on SiC without a back barrier [5], where the HEMTs exhibit a  $(f_T \cdot f_{MAX})^{1/2}$  of 262 GHz with a 40-nm T-gate and 227 GHz with a 60-nm T-gate. The biggest challenge in further reducing the gate length thus improving speed is the shortchannel effect (SCE). The SCE can be best curbed in double heterostructures, where an effective back barrier is present to confine the electrons in the channel but not degrade the electron mobility. However, such GaN double-heterostructure epitaxy is yet to be developed on Si substrates.

TABLE I

GAN HEMTS ON SI OF DIFFERENT GEOMETRIES

Gate

S-D

Peak Trans Maximum

Unity-Gain

Max

2

|      | Gate      | S-D           | Peak Trans-  | Maximum                 | Unity-Gain | Max Freq.       |

|------|-----------|---------------|--------------|-------------------------|------------|-----------------|

| HEMT | Length    | Spacing       | conductance  | Current                 | Frequency  | Oscillat.       |

|      | $L_G(nm)$ | $L_{SD}$ (nm) | $g_M$ (S/mm) | I <sub>MAX</sub> (A/mm) | $f_T(GHz)$ | $f_{MAX}$ (GHz) |

| А    | 55        | 175           | 0.66         | 2.8                     | 250        | 204             |

| В    | 55        | 175           | 0.76         | 2.8                     | 248        | 193             |

| С    | 55        | 280           | 0.62         | 2.6                     | 235        | 196             |

| D    | 60        | 175           | 0.56         | 2.8                     | 230        | 170             |

| E    | 65        | 280           | 0.50         | 2.0                     | 200        | 176             |

| F    | 60        | 1000          | 0.71         | 1.73                    | 150        | 155             |

$L_G$  refers to the length of the T gate stem.

#### II. EXPERIMENTS

Figure 1(a) shows that the present GaN HEMTs on a highresistivity Si substrate have no back barrier, comprising an AIN nucleation layer, an AlGaN buffer, a 1-µm unintentionally doped GaN channel, a 1-nm AlN spacer, and a 10-nm In<sub>0.17</sub>Al<sub>0.83</sub>N barrier. The layers are grown by metal-organic chemical vapor deposition (MOCVD) on 200-mm-diameter 725-µm -thick high-resistivity (3000  $\Omega$ ·cm) Si substrates in a Propel® HVM system at Veeco Instruments. Despite the large substrate, the grown layers are very uniform with a surface roughness of 0.72 nm and a standard deviation of 1.5% in the sheet resistance  $R_{SH}$ . The surface roughness is mapped by a Bruker Icon atomic force microscope over a randomly chosen 5  $\mu$ m × 5  $\mu$ m area.  $R_{SH}$  is mapped by a Lehighton contactless system across the entire 200-mm diameter substrate. The average  $R_{SH}$  of 206.4  $\Omega/\Box$  is consistent with the Hall measurement, which shows that the 2DEG has a density of 2.27  $\times 10^{13}$  cm<sup>-2</sup> and a mobility of 1430 cm<sup>2</sup>/V·s.

Device fabrication follows a previously established process flow [11]. First, to facilitate low-resistance ohmic contacts, the source and drain contact regions of the HEMTs are patterned by photolithography and plasma etching using a Cr/SiO<sub>2</sub> hard mask. Second, the etched regions are backfilled with 80-nmthick Si-doped  $n^{++}$  GaN using molecular beam epitaxy (MBE) at 750 °C. Limited by the MBE reactor size, the 200-mm Si wafer is diced into  $3.7 \times 3.7$  cm<sup>2</sup> chips. The Si doping density is on the order of  $10^{20}$  cm<sup>-3</sup>, consistent with the  $R_{SH,n++GaN}$  of 99  $\Omega/\Box$  as measured by the transfer length method (TLM). Defining the  $n^{++}$ -GaN regions through the Cr/SiO<sub>2</sub> hard mask, the source-drain spacing  $L_{SD}$  is purposely varied by electronbeam lithography (EBL) between 175 nm and 1 µm. Then, 40nm-thick Ti and 200-nm-thick Au are sequentially deposited on  $n^{++}$  GaN to form ohmic contacts without annealing. The Ti/Au contacts are pulled back by 1  $\mu$ m from the *n*<sup>++</sup>-GaN edge as shown in Fig. 1(b). A contact resistance  $R_C$  of 0.05  $\Omega$ ·mm is measured between the metal and the n++GaN (Fig. 2).

Last, T gates are defined by EBL with evaporation and liftoff of 50-nm-thick Ni and 240-nm-thick Au. As shown in Fig. 1(b), the trapezoid hat of the T gate has a height of 290 nm, a length of 300 nm on the bottom and 240 nm on the top, whereas the stem of the T gate has a height of 150 nm; the gate length  $L_G$ has been varied to be 55, 60 or 65 nm. With two parallel gate fingers, the total gate width is 2 × 25 µm.

The fabricated HEMTs were characterized on a Cascade Technologies Summit 9000 probe station with Infinity GSG microwave wafer probes. DC characterization is performed by using a Keithley 4200 semiconductor characterization system; This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/LED.2020.2984727, IEEE Electron Device Letters

#### SUBMITTED TO IEEE ELECTRON DEVICE LETTERS

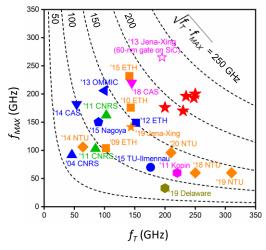

Fig. 3. Comparison of  $f_T$  and  $f_{MAX}$  of GaN HEMTs on Si from [7]–[10], [17]–[31], and this work ( $\bigstar$ ). Hollow star ( $\bigstar$ ) is a GaN HEMT on SiC [5] with similar structures as this work. Different colors represent different top barriers: orange for InAlN, blue for AlGaN, green for AlN, magenta for InAlGaN, Olive green for InAlN/InGaN (top/back).

RF characterization is performed by using an Agilent Technologies 8722ES network analyzer. For RF characterization, scattering parameters are measured from 50 MHz to 40 GHz. The measurements are calibrated using short, open, load, and through impedance standards on an alumina substrate. The parasitics are de-embedded using open and short test structures on the same chip as the HEMTs [12]. After de-embedding,  $f_T$  is extrapolated from the current gain  $|h_{2I}|^2$ , whereas  $f_{MAX}$  is extrapolated from the unilateral gain U. In both cases, the gain is assumed to follow -20 dB/dec.

#### III. RESULTS AND DISCUSSION

TLM test structures, 100-µm wide and fabricated on the same chip as the HEMTs, reveal excellent ohmic contact to the 2DEG. Figure 2(a) shows an extracted  $R_C$  of 0.07  $\Omega$ ·mm between the ohmic metal and the 2DEG and a 2DEG channel  $R_{SH}$  of 214  $\Omega/\Box$ . Furthermore, the 2DEG  $R_{SH}$  on processed chips is very close to that measured before device fabrication. These  $R_C$  and  $R_{SH}$  values are significantly lower than the state of the art GaN HEMTs on Si [7], [8], which contribute to the high speed observed in these InAIN/GaN on Si HEMTs. The low  $R_C$ is ascribed to the regrown  $n^{++}$ -GaN contacts and the high 2DEG concentration [13], whereas the low  $R_{SH}$  is mainly attributed to the minimal degradation in the 2DEG density and mobility thanks to the regrown contact process [14], [15].

Figures 2 show the transfer and output characteristics, and cutoff frequencies measured on HEMT A in Table I with  $L_G =$ 55 nm and  $L_{SD} = 175$  nm. The observed maximum drain current  $I_{D,MAX}$  of 2.8 A/mm and the on resistance  $R_{ON}$  of 0.6  $\Omega$ ·mm, along with the peak transconductance  $g_m$  of 0.66 S/mm, are among the best in GaN HEMTs on Si, comparable to GaN HEMTs on SiC without a back barrier. HEMT A shows a high output conductance, suggesting it suffers from severe SCE. This is confirmed in Fig. 2(b), where  $I_D$  under off-state is higher than the gate leakage, i.e. a residue current flowing between source and drain that can't be turned off by the gate voltage. At low  $V_{DS}$ , these HEMTs typically exhibit a decent  $I_{ON}/I_{OFF}$  ratio ~10<sup>5</sup>; HEMT A has the highest gate leakage among all the tested

3

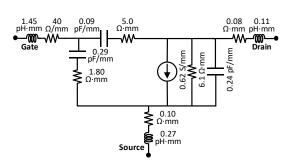

Fig. 4. Small-signal equivalent-circuit model of HEMT A under  $V_{GS} = -4.5$  V and  $V_{DS} = 6$  V.

devices, most likely due to processing non-uniformity. The gate leakage can be further reduced by adopting a plasma treatment [4], [9, [16]. Also adversely influenced by the SCE, i.e. high drain leakage, the device breakdown voltage is  $\sim$ 12 V. In HEMTs without a back barrier, the SCE sensitively depends on the quality of the gate definition and GaN buffer. A more straightforward design is to implement a back barrier such as InGaN, AlGaN, InAlN or AlN back barrier technologies.

The  $f_T/f_{MAX}$  of 250/204 GHz are obtained after de-embedding in HEMT A; in comparison, neglecting the short de-embedding test structure renders similar  $f_T/f_{MAX}$  values of 245/187 GHz. Table I lists  $f_T$  and  $f_{MAX}$  measured on HEMTs of different geometries on the same chip. In general, HEMTs with longer  $L_G$  and  $L_{SD}$  have lower  $f_T$  and  $f_{MAX}$ . In Fig. 3, the  $f_T$  and  $f_{MAX}$ values achieved in this work are compared to other reported GaN HEMTs on Si, as well as the state-of-the-art GaN HEMTs on SiC with similar epi-structures and device dimensions [5] (gate length, barrier materials, and its thickness, no back barrier). It can be seen the present HEMTs are clustered near the upper right corner as desired, with  $(f_T \cdot f_{MAX})^{1/2}$  very close to that of the GaN HEMTs on SiC with a comparable gate length.

To help explain the high  $f_{MAX}$ , Fig. 4 shows the small-signal equivalent-circuit model of HEMT A with the model parameters extracted by a standard procedure [32]. The extracted AC  $g_m$  is similar to its DC value, indicating little dispersion, also confirmed by the pulsed I-V measurement (not shown), which is consistent with our prior learnings on InAlN HEMTs with the non-alloyed regrown contact process [14]. The maximum errors between the simulated and measured  $S_{11}$ ,  $S_{12}$ ,  $S_{21}$ , and  $S_{22}$  are 1%, 90% ( $S_{12}$  is a very small number thus a higher error margin), 2%, and 5%, respectively. Using the small-signal model, the simulated  $f_T$  and  $f_{MAX}$  are 248 GHz and 197 GHz, respectively, which are very close to the measured values. Had  $n^{++}$  GaN not been used, assuming  $R_S = R_D = 0.5$  $\Omega \cdot \text{mm}, f_T / f_{MAX}$  would have reduced to 202/171 GHz. Similarly, any increase in  $R_G$  would reduce  $f_{MAX}$ . Thus, the small-signal analysis confirms the benefits of  $n^{++}$  GaN and T gate, especially in increasing  $f_{MAX}$ .

#### IV. CONCLUSION

GaN HEMTs on Si with different geometries were fabricated, measured, and analyzed. The analysis confirms the benefits of  $n^{++}$ -GaN source/drain contacts and T-shaped gates, especially in achieving both high  $f_{MAX}$  and  $f_T$ . With the state-of-the-art regrown ohmics, scaled source-drain separation and T-gates, GaN HEMTs on Si achieve comparable metrics with that on SiC in terms of DC and small-signal performance.

# SUBMITTED TO IEEE ELECTRON DEVICE LETTERS

#### References

- Y. Tang, K. Shinohara, D. Regan, A. Corrion, D. Brown, J. Wong, A. Schmitz, H. Fung, S. Kim, and M. Micovic, "Ultrahigh-speed GaN high-electron-mobility transistors with *fi/fmax* of 454/444 GHz," *IEEE Electron Device Lett.*, vol. 36, no. 6, pp. 549–551, Jun. 2015, doi: 10.1109/LED.2015.2421311.

- [2] T. Fang, R. Wang, H. Xing, S. Rajan, and D. Jena, "Effect of optical phonon scattering on the performance of GaN transistors," *IEEE Electron Device Lett.*, vol. 33, no. 5, pp. 709–711, May 2012, doi: 10.1109/LED.2012.2187169.

- [3] K. Shinohara, D. Regan, A. Corrion, D. Brown, Y. Tang, J. Wong, G. Gandia, A. Schmitz, H. Fung, S. Kim, and M. Micovic, "Self-aligned-gate GaN-HEMTs with heavily-doped n<sup>+</sup>-GaN ohmic contacts to 2DEG," in *Proc. IEEE IEDM*, Dec. 2012, pp. 27.2.1–27.2.4, doi: 10.1109/IEDM.2012.6479113.

- [4] Y. Yue, Z. Hu, J. Guo, B. Sensale-Rodriguez, G. Li, R. Wang, F. Faria, B. Song, X. Gao, S. Guo, T. Kosel, G. Snider, P. Fay, D. Jena, and H. G. Xing, "Ultrascaled InAlN/GaN high electron mobility transistors with cutoff frequency of 400 GHz," *Jpn. J. Appl. Phys.*, vol. 52, no. 8S, p. 08JN14, May 2013, doi: 10.7567/JJAP.52.08JN14.

- [5] R. Wang, G. Li, G. Karbasian, J. Guo, B. Song, Y. Yue, Z. Hu, O. Laboutin, Y. Cao, W. Johnson, G. Snider, P. Fay, D. Jena, and H. G. Xing, "Quaternary barrier InAlGaN HEMTs with *f<sub>T</sub>/f<sub>max</sub>* of 230/300 GHz," *IEEE Electron Device Lett.*, vol. 34, no. 3, pp. 378–380, Mar. 2013, doi: 10.1109/LED.2013.2238503.

- [6] M. L. Schuette, A. Ketterson, B. Song, E. Beam, T. M. Chou, M. Pilla, H. Q. Tserng, X. Gao, S. P. Guo, P. J. Fay, H. G. Xing, and P. Saunier, "Gate-recessed integrated E/D GaN HEMT technology with *fi (fmax >300GHz," IEEE Electron Device Lett.*, vol. 34, no. 6, pp. 741–743, Jun. 2013, doi: 10.1109/LED.2013.2257657.

- [7] D. Marti, S. Tirelli, V. Teppati, L. Lugani, J.-F. Carlin, M. Malinverni, N. Grandjean, and C. R. Bolognesi, "94-GHz large-signal operation of AlInN/GaN high-electron-mobility transistors on silicon with regrown ohmic contacts," *IEEE Electron Device Lett.*, vol. 36, no. 1, pp. 17–19, Jan. 2015, doi: 10.1109/LED.2014.2367093.

- [8] W. Xing, Z. Liu, H. Qiu, K. Ranjan, Y. Gao, G. I. Ng, and T. Palacios, "InAlN/GaN HEMTs on Si with high f<sub>T</sub> of 250 GHz," *IEEE Electron Device Lett.*, vol. 39, no. 1, pp. 75–78, Jan. 2018, doi: 10.1109/LED.2017.2773054.

- [9] P. Cui, A. Mercante, G. Lin, J. Zhang, P. Yao, D. W. Prather, and Y. Zeng, "High-performance InAlN/GaN HEMTs on silicon substrate with high f<sub>T</sub> × L<sub>g</sub>," Appl. Phys. Express, vol. 12, no. 10, pp. 104001-1–104001-4, Dec. 2019, doi: 10.7567/1882-0786/ab3e29.

- [10] H. Xie, Z. Liu, Y. Gao, K. Ranjan, K. E. Lee, and G. I. Ng, "Deeply-scaled GaN-on-Si high electron mobility transistors with record cut-off frequency f<sub>T</sub> of 310 GHz," *Appl. Phys. Express*, vol. 12, no. 12, pp. 126506-1–126506-5, Dec. 2019, doi: 10.7567/1882-0786/ab56e2.

- [11] A. Hickman, R. Chaudhuri, S. Bader, K. Nomoto, K. Lee, H. Xing, and D. Jena, "High breakdown voltage in RF AlN/GaN/AlN quantum well HEMTs," *IEEE Electron Device Lett.*, vol. 40, no. 8, pp. 1293–1296, Aug. 2019, doi: 10.1109/LED.2019.2923085.

- [12] M. C. A. M. Koolen, J. A. M. Geelen, and M. P. J. G. Versleijen, "An improved de-embedding technique for on-wafer high-frequency characterization," in *Proc. BCTM*, pp. 188–191, Sep. 1991, doi: 10.1109/BIPOL.1991.160985.

- [13] J. Guo, G. Li, F. Faria, Y. Cao, R. Wang, J. Verma, X. Gao, S. Guo, E. Beam, A. Ketterson, M. Schuette, P. Saunier, M. Wistey, D. Jena, and H. Xing, "MBE-regrown ohmics in InAlN HEMTs with a regrowth interface resistance of 0.05 mm," *IEEE Electron Device Lett.*, vol. 33, no. 4, pp. 525–527, Apr. 2012, doi: 10.1109/LED.2012.2186116.

- [14] R. Wang, G. Li, J. Guo, B. Song, J. Verma, Z. Hu, Y. Yue, K. Nomoto, S. Ganguly, S. Rouvimov, X. Gao, O. Laboutin, Y. Cao, W. Johnson, P. Fay, D. Jena, and H. G. Xing, "Dispersion-free operation in InAlNbased HEMTs with ultrathin or no passivation," *Proc. IEEE IEDM*, Dec. 2013, pp. 28.6.1–28.6.4, doi: 10.1109/IEDM.2013.6724712.

- [15] B. Song, M. Zhu, Z. Hu, M. Qi, K. Nomoto, X. Yan, Y. Cao, D. Jena, and H. G. Xing, "Ultralow-leakage AlGaN/GaN high electron mobility transistors on Si with non-alloyed regrown ohmic contacts," *IEEE Electron Dev. Lett.*, vol. 37, no. 1, pp. 16–19, Jan. 2016, doi: 10.1109/LED.2015.2497252.

- [16] R. Wang, G. Li, O. Laboutin, Y. Cao, W. Johnson, Gregory Snider, P. Fay, D. Jena, and H. G. Xing, "210-GHz InAlN/GaN HEMTs with dielectric-free passivation," *IEEE Electron Dev. Lett.*, vol. 32, no. 7, pp.892-894, July 2011, doi: 10.1109/LED.2011.2147753.

- [17] A. Minko, V. Hoel, S. Lepilliet, G. Dambrine, J. C. de Jaeger, Y. Cordier, F. Semond, F. Natali, and J. Massies, "High microwave and noise performance of 0.17-µm AlGaN-GaN HEMTs on high-resistivity silicon substrates," *IEEE Electron Device Lett.*, vol. 25, no. 4, pp. 167–169, Apr. 2004, doi: 10.1109/LED.2004.825208.

- [18] H. Sun, A. R. Alt, H. Benedickter, C. R. Bolognesi, E. Feltin, J.-F. Carlin, M. Gonschorek, N. Grandjean, T. Maier, and R. Quay, "102-GHz AlInN/GaN HEMTs on silicon with 2.5-W/mm output power at 10 GHz," *IEEE Electron Device Lett.*, vol. 30, no. 8, pp. 796–798, Aug. 2009, doi: 10.1109/LED.2009.2023603.

- [19] H. Sun, A. R. Alt, H. Benedickter, C. R. Bolognesi, E. Feltin, J.-F. Carlin, M. Gonschore, and N. Grandjean, "Ultrahigh-speed AlInN/GaN high electron mobility transistors grown on (111) high-resistivity silicon with *f<sub>T</sub>* = 143 GHz," *Appl. Phys. Express*, vol. 3, no. 6, pp. 094–101, Sep. 2010, doi: 10.1143/APEX.3.094101.

- [20] O. Laboutin, Y. Cao, R. Wang, G. Li, D. Jena, H. Xing, C.-F. Lo, L. Liu, S. J. Pearton, F. Ren, and W. Johnson, "The resurgence of III-N materials development: AlInN HEMTs and GaN-on-Si," *ECS Trans.*, vol. 41, no. 8, pp. 301–311, Jan. 2011, doi: 10.1149/1.3631507.

- [21] F. Medjdoub, N. Waldhoff, M. Zegaoui, B. Grimbert, N. Rolland, and P. A. Rolland, "Low-noise microwave performance of AIN/GaN HEMTs grown on silicon substrate," *IEEE Electron Device Lett.*, vol. 32, no. 9, pp. 1230–1232, Sep. 2011, doi: 10.1109/LED.2011.2161261.

- [22] F. Medjdoub, M. Zegaoui, and N. Rolland, "Beyond 100 GHz AlN/GaN HEMTs on silicon substrate," *IET Electron. Lett.*, vol. 47, no. 24, pp. 1345–1346, Nov. 2011, doi: 10.1049/el.2011.3166.

- [23] D. Marti, S. Tirelli, A. R. Alt, J. Roberts, and C. R. Bolognesi, "150-GHz cutoff frequencies and 2-W/mm output power at 40 GHz in a millimeterwave AlGaN/GaN HEMT technology on silicon," *IEEE Electron Device Lett.*, vol. 33, no. 10, pp. 1372–1374, Oct. 2012, doi: 10.1109/LED.2012.2204855.

- [24] S. Bouzid-Driad, H. Maher, N. Defrance, V. Hoel, J.-C. de Jaeger, M. Renvoise, and P. Frijlink, "AlGaN/GaN HEMTs on silicon substrate with 206-GHz f<sub>MAX</sub>," *IEEE Electron Device Lett.*, vol. 34, no. 1, pp. 36–38, Jan. 2013, doi: 10.1109/LED.2012.2224313.

- [25] S. Huang, K. Wei, G. Liu, Y. Zheng, X. Wang, L. Pang, X. Kong, X. Liu, Z. Tang, S. Yang, Q. Jiang, and K. J. Chen, "High-*f<sub>MAX</sub>* high Johnson's figure-of-merit 0.2-μm gate AIGaN/GaN HEMTs on silicon substrate with AIN/SiN<sub>x</sub> passivation," *IEEE Electron Device Lett.*, vol. 35, no. 3, pp. 315–317, Mar. 2014, doi: 10.1109/LED.2013.2296354.

- [26] S. Arulkumaran, K. Ranjan, G. I. Ng, C. M. M. Kumar, S. Vicknesh, S. B. Dolmanan, and S. Tripathy, "High-frequency microwave noise characteristics of InAlN/GaN high-electron mobility transistors on Si (111) substrate," *IEEE Electron Device Lett.*, vol. 35, no. 10, pp. 992–994, Oct. 2014, doi: 10.1109/LED.2014.2343455.

- [27] W. Jatal, U. Baumann, K. Tonisch, F. Schwierz, and J. Pezoldt, "High-frequency performance of GaN high-electron mobility transistors on 3C-SiC/Si substrates with Au-free ohmic contacts," *IEEE Electron Device Lett.*, vol. 36, no. 2, pp. 123–125, Feb. 2015, doi: 10.1109/LED.2014.2379664.

- [28] P. D. Christy, Y. Katayama, A. Wakejima, and T. Egawa, "High  $f_T$  and  $f_{MAX}$  for 100 nm unpassivated rectangular gate AlGaN/GaN HEMT on high resistive silicon (111) substrate," *IET Electron. Lett.*, vol. 51, no. 17, pp. 1366–1367, Aug. 2015, doi: 10.1049/el.2015.1395.

- [29] S. Dai, Y. Zhou, Y. Zhong, K. Zhang, G. Zhu, H. Gao, Q. Sun, T. Chen, and H. Yang, "High f<sub>T</sub> AlGa(In)N/GaN HEMTs grown on Si with a low gate leakage and a high on/off current ratio," *IEEE Electron Device Lett.*, vol. 39, no. 4, pp. 576–579, Apr. 2018, doi: 10.1109/LED.2018.2809689.

- [30] K. Nomoto, M. Pan, Z. Hu, J. Miller, W. Li, A. Hickman, K. Lee, S. Bader, S. M. Lee, D. Jena, and H. Xing, "Fully passivated InAlN/GaN HEMTs on silicon with  $f_T/f_{MAX}$  of 144/141 GHz," in 13th Topical Workshop on Heterostructure Microelectronics, Toyama, Japan, Aug. 2019.

- [31] H. Xie, Z. Liu, Y. Gao, K. Ranjan, K. E. Lee, and G. I. Ng, "CMOScompatible GaN-on-Si HEMTs with cut-off frequency of 210 GHz and high Johnson's figure-of-merit of 8.8 THz·V," *Appl. Phys. Express*, vol. 13, no. 2, pp. 026503-1–026503-4, Jan. 2020, doi: 10.7567/1882-0786/ab659f.

- [32] G. Dambrine, A. Cappy, F. Heliodore, and E. Playez, "A new method for determining the FET small signal equivalent circuit," *IEEE Trans. Microw. Theory Techn.*, vol. 36, no. 7, pp. 1151–1159, Jul. 1988, doi: 10.1109/22.3650.