# Valley Spin Logic Gates

L. L. Tao<sup>1</sup>, Azad Naeemi<sup>2</sup>, and Evgeny Y. Tsymbal<sup>1</sup>

<sup>1</sup> Department of Physics and Astronomy & Nebraska Center for Materials and Nanoscience University of Nebraska, Lincoln, Nebraska 68588, USA

Valleytronics is an emerging field of research utilizing the valley pseudospin degree of freedom. In this work, we propose to exploit spin-valley locking in 2D materials, such as silicene, germanene, stanene and 1T' transition metal dichalcogenides, to realize novel logic devices with multiple voltage-controlled gate contacts. These materials possess space-inversion and time-reversal symmetries and have two valleys at the non-time-reversal invariant momenta, *K* and *K'*, related by time-reversal symmetry. Due to these properties, the valley spin polarization in these materials can be switched by electric field, and the device conductance and the output voltage can be controlled by the polarity of the input gate voltage. Based on the explicit quantum-transport calculations, we demonstrate the realization of seven logic gates, namely NOT, XNOR, XOR, AND, NAND, OR, and NOR. Our results validate the practical use of the electrically controlled valley-spin locking in emerging 2D materials in novel logic devices.

#### I. INTRODUCTION

Spintronics exploits the spin degree of freedom in novel electronic devices<sup>1,2</sup>. Such devices have aroused considerable interest due to their nonvolatility, high integration densities, and low-power operation. Several spin logic devices have been theoretically proposed<sup>3-6</sup> and experimentally demonstrated<sup>7-10</sup>. For example, Ney et al.<sup>3</sup> proposed a programmable spin logic based on a single magnetoresistive element whose inputs are represented by the input current directions, while the logic outputs are represented by the device resistance states. Dery et al.4 reported a spin logic gate based on a semiconductor structure with multiple magnetic contacts. The logic inputs are encoded in the magnetization directions, while the logic output is defined by a transient current response. Behin-Aein et al.<sup>5</sup> proposed all-spin logic, where input and output information are represented by the magnetization of nanomagnets that communicate through spin-coherent channels. Wan et. al.8 demonstrated the spin logic operations in magnetized trilayer Pt/Co/MgO via the spin Hall effect. Manipatruni et al.9 proposed a scalable spintronic logic device that operates via spin-orbit transduction combined with magnetoelectric switching. Spin logic gates were also theoretically proposed utilizing graphene nanoribbons<sup>11</sup> and molecular magnets<sup>12</sup> via the electrical control of spin-polarized current. Recently, spin logic gates were also proposed utilizing a Kagome spin ice<sup>13</sup> and polarized spin waves<sup>14</sup>. However, many of the proposed spin logic gates suffer from a concatenation problem when integrated into circuits. Due to the logic input and output being encoded in different physical quantities<sup>3,4,11,12</sup>, the logic output cannot be used as the input of the successive gate. Solving this problem is important for device cascading in integrated circuits.

More recently, valleytronics – a field of research based on exploitation and manipulation of the valley pseudospin degree

of freedom, has attracted great attention<sup>15,16</sup>. In addition to the rich valley physics<sup>17,18</sup>, the valley pseudospin can be utilized to design promising valley-based devices. For example, in analogy to the spin valve effect<sup>19,20</sup>, the valley valve effect, i.e. the change of electrical resistance between two values due to the valley-dependent transport, has been predicted in graphene nanoribbons <sup>21</sup>, <sup>22</sup> and WS<sub>2</sub>/MoS<sub>2</sub> van der Waals heterostructures<sup>23</sup>. In addition, valley-based logic gates have been proposed in a quasi-two-dimensional system with merging Dirac cones, which reveal all-electric-controlled valley filter and valley valve effects<sup>24</sup>.

Recently, we have proposed a valley spin valve (VSV), which exploits the spin-valley locking in two-dimensional (2D) materials, such as silicene, germanene, stanene, and 1T'transition metal dichalcogenides 25. These materials possess space-inversion and time-reversal symmetries and have two valleys at the non-time-reversal invariant momenta, K and K', related by time-reversal symmetry. The valley spin polarization in these materials can be switched by an electric field, which enables functionalities of a valley spin polarizer or a valley spin analyzer. When placed in series, they constitute the VSV – a device whose conductance state is ON or OFF depending on the relative valley spin polarization of the polarizer and the analyzer<sup>25</sup>. In this work, we utilize the predicted giant VSV effect to design valley-spin logic gates, which enable various logic operations, such as NOT, XNOR, XOR, AND, NAND, OR, and NOR. Since both logic input and output are encoded by the polarity of voltage, the cascading is thus realized.

## II. THEORETICAL FORMALISM

Without losing generality, we consider stanene as a representative channel material for the proposed devices. The low-energy tight-binding Hamiltonian is given by<sup>26-28</sup>

<sup>&</sup>lt;sup>2</sup> Department of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, Georgia 30332, USA

$$H = -t \sum_{\langle i,j \rangle \alpha} c^{\dagger}_{i\alpha} c_{j\alpha} + i \frac{\lambda_{SO}}{3\sqrt{3}} \sum_{\langle \langle i,j \rangle \rangle \alpha,\beta} v_{ij} c^{\dagger}_{i\alpha} \sigma_z^{\alpha\beta} c_{j\beta}$$

$$+ i \lambda_{R1} \sum_{\langle i,j \rangle \alpha,\beta} c^{\dagger}_{i\alpha} \left( \mathbf{\sigma} \times \hat{\mathbf{d}}_{ij} \right)^z c_{j\beta}$$

$$- i \frac{2\lambda_{R2}}{3} \sum_{\langle \langle i,j \rangle \rangle \alpha,\beta} \xi_i c^{\dagger}_{i\alpha} \left( \mathbf{\sigma} \times \hat{\mathbf{d}}_{ij} \right)^z c_{j\beta} + l E_z \sum_{i\alpha} \xi_i c^{\dagger}_{i\alpha} c_{i\alpha},$$

$$(1)$$

where the first term is the nearest-neighbor hopping,  $c_{i\alpha}^{\dagger}$  ( $c_{i\alpha}$ ) is an electron creation (annihilation) operator at the site i(j) with spin  $\alpha = \uparrow$ ,  $\downarrow$ , t is the hopping parameter and  $\langle i, j \rangle$  denotes the sum over the nearest-neighbor sites. The second term represents the intrinsic spin-orbit coupling (SOC) with strength  $\lambda_{SO}$ ,  $\langle\langle i,j\rangle\rangle$  denotes the sum over the next-nearest-neighbor sites,  $\sigma_z$ is the z-component of the Pauli matrix, and  $v_{ij} = +1$  (-1) selects anticlockwise (clockwise) hopping with respect to the z axis. The third term represents the Rashba SOC induced by an external electric field, and the fourth term is the intrinsic Rashba SOC. Our previous work demonstrates that  $\lambda_{R1}$  is significantly smaller than  $\lambda_{SO}$ , and the intrinsic Rashba SOC ( $\lambda_{R2}$ ) has a negligible effect<sup>25</sup>. Both Rashba terms are therefore ignored in this work. The last term arises from the applied electric field  $E_z$ ,  $\xi_i = +1$  (-1) distinguishes site i = A (B), and 2l is the buckling height. According to Eq. (1), when  $\lambda_{R1} = \lambda_{R2} = 0$ ,  $[\sigma_z, H] = 0$ , and the spin component  $\sigma_z$  is a good quantum number. In the calculations, we use the tight-binding parameters: t = 1.3 eV,  $\lambda_{SO} = 0.1 \text{ eV}$ , and l = 0.4 Å, appropriate for stanene<sup>29</sup>.

Conductance G at energy E is calculated by using the Landauer-Büttiker formula<sup>30</sup>

$$G(E) = \frac{e^2}{h} \sum_{\sigma, k_y} T_{\sigma}(E, k_y), \qquad (2)$$

where e the is electron charge, h the Planck's constant,  $T_{\sigma}$  is the transmission for spin  $\sigma$ .  $k_y$  is the transverse Bloch wave vector, which is conserved in the transports process. For the numerical calculations, we set the gate width  $d_1 = 40a$ , separation distance  $d_2 = 20a$  (where a is the lattice constant), the Fermi energy  $E_F = 0.01$  eV, and calculate G using 101 irreducible  $k_y$  points.

### III. RESULTS AND DISCUSSION

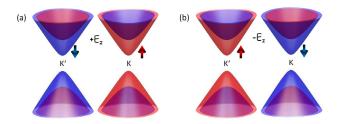

Fig. 1 shows the calculated band structure around the valleys K and K' for positive and negative  $E_z$ . Although the net spin polarization in the system is zero, the spin polarization around each valley is 100%. Importantly, such a valley-dependent spin polarization can be reversed by an electric field, which can be understood as follows. The band energies around the valleys are given by<sup>27</sup>

$$\varepsilon_{\eta s}^{\pm} = \pm \sqrt{3a^2t^2q_{\eta}^2/4 + (\eta s\lambda_{SO} - lE_z)^2},$$

(3)

where  $\eta=\pm 1$  and  $s=\pm 1$  are valley and spin indices, respectively, and  $q_{\eta}=\left|k-K_{\eta}\right|$  is the wave vector measured from the  $K\left(K'\right)$  point. It is seen that the band energies are spin degenerate if either  $E_z=0$  or  $\lambda_{\mathrm{SO}}=0$ . If both  $E_z$  and  $\lambda_{\mathrm{SO}}$  are finite, the bands are spin split at the  $K\left(K'\right)$  valley. From Eq. (3),  $\varepsilon_{\eta\uparrow}^{\pm}=\varepsilon_{-\eta\downarrow}^{\pm}$ ; hence, the spin polarization is opposite between the K and K' valleys. In addition,  $\varepsilon_{\eta\uparrow}^{\pm}(+E_z)=\varepsilon_{\eta\downarrow}^{\pm}(-E_z)$ , and hence the polarity of the valley-dependent spin polarization can be switched by changing the sign of  $E_z$ .

FIG. 1. The calculated band structure of stanene around the K and K' valleys for the electric field (a)  $E_z = 1.25$  V/nm and (b)  $E_z = -1.25$  V/nm. Red and blue colors represent spin-up and spin-down branches, respectively. Arrows denote the spin directions. The energy range in the plot is [-0.3, 0.3] eV.

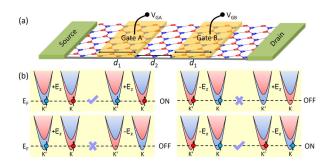

FIG. 2. (a) Schematic of the four-terminal device model with two gates A and B.  $d_1$  and  $d_2$  denote the gate width and gate separation distance, respectively. (b) Band alignments at the gate regions for different gate polarities determined by the electric field  $E_z$ . Dashed lines denote the Fermi energy  $E_F$ . Electrons (filled circles) can be transmitted (ON state) or blocked (OFF state) depending on  $E_z$  in the gated regions.

Fig. 2(a) schematically shows a prototype four-terminal building block for the design of XNOR and XOR gates. The device has a source and a drain connected by a 2D channel, whose transport properties are controlled by gates A and B. Positive and negative voltages on gates A and B are the logic inputs 1 and 0, respectively. As a result of the VSV effect<sup>25</sup>, depending on the relative voltage polarities on gates A and B, the device conductance is high (ON state) or low (OFF state).

This is due to the spin and pseudospin (valley) conservation in the transport process, which makes the transmission high (low) when the gate polarities are same (opposite), as illustrated in Fig. 2(b).

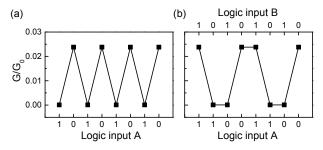

Fig. 3(a) shows the calculated zero-bias conductance as a function of the input gate A when B is set to negative. For a positive gate A voltage (logic input A = 1), the device is in the low conductance state. For a negative A gate voltage (logic input A = 0), the device is in the high conductance state. For the parameters used in the calculation, the ON/OFF conductance ratio exceeds 300. This value can be further enhanced by increasing gate width  $d_1$  (e.g., the ON/OFF ratio is enhanced by a factor of 10 when  $d_1$  is increased from 40a to 50a). Fig. 3(b) shows the dependence of zero-bias conductance on the two logic inputs A and B. It is seen that A = B = 1 or A = B = 0 yields the high conductance state. In all other cases, the device is in the low conductance state.

FIG. 3. (a, b) Total conductance in units of  $G_0=2e^2/h$  as a function of logic inputs on gates A and B (bottom and top axes, respectively). In (a), the gate B is set to negative (B = 0).  $|E_z| = 1.25 \text{ V/nm}$ .

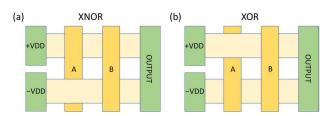

FIG. 4. Schematics of (a) XNOR and (b) XOR gates. The light yellow regions represent 2D channels. Gates A and B act as two logic inputs. Gate A serves as a topgate or backgate, providing an invert of A input in the latter case. VDD is the supply voltage, providing +VDD (-VDD) voltage in the upper (lower) circuit.

Although the device of Fig. 2(a) has logic functionalities, it cannot be used for cascading. While the logic input is the voltage supplied by the source, the logic output is the device conductance, which is not suitable as an input of the successive gate. The similar problem has been encountered in the previously proposed devices<sup>3,4</sup>, where the logic input and output were encoded in different physical quantities.

To address this problem, we design XNOR and XOR logic gates, as schematically shown in Fig. 4. This design satisfies the concatenation requirement where the output voltage of the logic gate can be used as the logic input for the successive gate. As seen from Fig. 4, each gate represents two circuits, upper and lower, with VDD (-VDD) supply voltage on the upper (lower) circuit and a common output. Gate A serves as a topgate or backgate (i.e. connected to the top or bottom of the 2D channel), providing an invert of A input in the latter case. As seen from Fig. 4(a), when A = B, the top circuit is in ON state, while the bottom circuit is in OFF state, and the output voltage is positive, corresponding to logic state 1. When  $A \neq B$ , the top circuit is in OFF state, while the bottom circuit is in ON state, and the output voltage is negative, corresponding to logic state 0. The XNOR logic operation is thus realized. The XOR gate is obtained from the XNOR gate by changing gate A to be a backgate on the upper circuit and a topgate on the lower circuit (Fig. 4(b)). The NOT gate can be realized from the XNOR gate by setting A to 0 or from the XOR gate by setting A to 1.

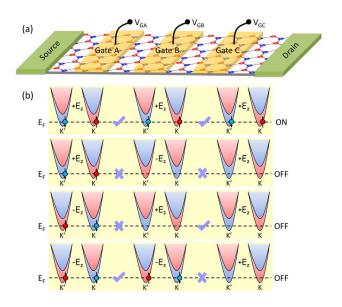

The design of AND and NAND gates requires a five-terminal building block shown in Fig. 5 (a), which involves three gates A, B, and C. Fig. 5(b) shows the relative band alignment between the three gated regions. As is evident from this figure, depending on the relative input polarities of the gates, electrons can be efficiently transmitted through the intravalley transport or blocked, which gives rise to the corresponding ON and OFF conductance states.

FIG. 5. (a) Schematic of the five-terminal device model with three gates A, B, and C. (b) Band alignments at the gate regions for different gate polarities determined by the electric field  $E_z$ . Dashed lines denote the Fermi energy  $E_F$ . Electrons (filled circles) can be transmitted (ON state) or blocked (OFF state) depending on  $E_z$  in the gated regions.

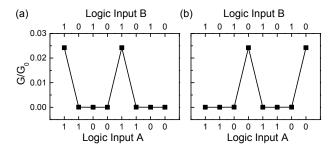

Figs. 6 (a) and (b) show the calculated conductance as a function of gate inputs. When gate C is set to positive (Fig. 6(a)), only the input A = B = 1 gives rise to the high conductance state, while all other inputs yield the low conductance state, in agreement with Figure 5(b). When gate C is set to negative (Fig. 6(b)), only the input A = B = 0 gives rise the high conductance state, while all other inputs yield the low conductance state.

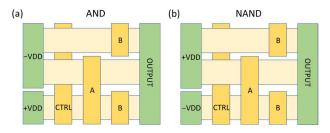

Based on this conductance behavior, we design AND and NAND logic gates that provide the concatenation requirement, as shown in Fig. 7. In Fig. 7(a), control gate CTRL is set to +VDD, and when A=B=1 (+VDD), the two upper devices are in OFF state while the lower is in ON state. Hence, the output voltage is going to be close to +VDD, resulting in logic state 1. In all other cases, the lower device is in OFF state, and the output voltage is -VDD, resulting in logic state 0. The AND logic operation is thus realized. The NAND gate is obtained by swapping the VDD and -VDD contacts (Fig. 7(b)). The OR and NOR gates can be realized from the NAND and AND gates, respectively, by setting CTRL to be -VDD.

FIG. 6. (a, b) Total conductance in units of  $G_0 = 2e^2/h$  as a function of logic inputs on gates A and B (bottom and top axes, respectively). Gate C is set to (a) positive and (b) negative.  $|E_z| = 1.25$  V/nm.

FIG. 7. Schematics of (a) AND and (b) NAND gates. The light yellow regions represent 2D channels. Gates A and B act as two logic inputs. Gate CTRL=+VDD serves as a topgate or backgate, providing an invert of CTRL input in the latter case. VDD is the supply voltage.

A common figure of merit to characterize the field-effect transistor performance is a subthreshold swing, which is how much change in the gate voltage is required to change the drain current by one decade. We estimate this quantity by calculating the conductance of the device of Fig. 2(a) in the OFF state as a function of applied electric field  $E_z$ . We find that conductance changes by an order in magnitude with  $E_z \sim 0.12$  V/nm. Assuming the channel thickness of 1 nm, this transforms to a subthreshold swing ~120 mV/dec, which is larger than that of the ultimate MOSFET performance of 60 mV/dec at room temperature. We note, however, that the estimated subthreshold swing is strongly reduced with increasing  $d_1$ . Thus, amending geometry of the device allows further improvement of the subthreshold swing. On the other hand, our calculation does not take into account disorder and phonon scattering, which are expected to reduce the ON/OFF ratio due to intervalley scattering. However, the two K and K' valleys are well separated by a wavevector comparable to the size of the Brillouin zone. Thus, intervalley scattering is equivalent to a large momentum transfer, which requires a very strong random potential. We expect therefore that the ON/OFF ratio is largely robust against this scattering<sup>25</sup>.

In addition to silicene, germanene, and stanene, a 1T'- $MX_2$  monolayer<sup>31</sup> (M = Mo, W; X = S, Se, Te) and a 2H- $MX_2$  bilayer<sup>32</sup> represent other promising candidates for valley spin logic gates, due to their electrically controllable valley spin polarization. The proposed design rules for the valley spin logic gates are universal for all these 2D materials.

## IV. CONCLUSIONS

In summary, we have proposed design of the valley spin logic gates based on the 2D materials, which support the VSV effect. The proposed devices utilize multiple gate contacts acting as logic inputs, while the output logic states are encoded in the output voltage. Through the analysis of the relative band alignment and the calculated conductance, we have demonstrated the realization of seven logic gates namely NOT, XNOR, XOR, AND, NAND, OR, and NOR. Our proposed valley-spin logic gates satisfy the concatenation requirement, where the output voltage of the logic gate can be used as the logic input of successive gate. Our results validate the practical use of the electrically controlled valley-spin locking in emerging 2D materials in novel logic devices.

#### **ACKNOWLEDGMENTS**

The authors thank Peter Dowben for helpful discussions. This research was supported by the National Science Foundation (NSF) through the E2CDA program (grant ECCS-1740136) and the Semiconductor Research Corporation (SRC) through the nCORE program.

- <sup>1</sup> S. A. Wolf, D. D. Awschalom, R. A. Buhrman, J. A. Daughton, S. von Molnár, M. L. Roukes, A. Y. Chtchelkanova, and D. M. Treger, Spintronics: A Spin-Based Electronics Vision for the Future, *Science* 294, 1488 (2001).

- <sup>2</sup> E. Y. Tsymbal and I. Žutić, Eds., *Spintronics Handbook: Spin Transport and Magnetism, 2-nd Edition*, 3 volumes (CRC Press, Taylor & Francis Group, 2019).

- <sup>3</sup> A. Ney, C. Pampuch, R. Koch, and K. H. Ploog, Programmable computing with a single magnetoresistive element, *Nature* **425**, 485 (2003).

- <sup>4</sup> H. Dery, P. Dalal, Ł. Cywiński, and L. J. Sham, Spin-based logic in semiconductors for reconfigurablelarge-scale circuits, *Nature* 447, 573 (2007).

- <sup>5</sup> B. Behin-Aein, D. Datta, S. Salahuddin, and S. Datta, Proposal for an all-spin logic device with built-in memory, *Nat. Nanotechnol.* 5, 266 (2010).

- <sup>6</sup> Y. Kunihashi, Makoto Kohda, H. Sanada, H. Gotoh, T. Sogawa, and J. Nitta, *Appl. Phys. Lett.* **100**, 113502 (2012).

- <sup>7</sup> A. A. Khajetoorians, J. Wiebe, B. Chilian, and R. Wiesendanger, *Science* **332**, 1062 (2011).

- <sup>8</sup> C. H. Wan, X. Zhang, Z. H. Yuan, C. Fang, W. J. Kong, Q. T. Zhang, H. Wu, U. Khan, X. F. Han, *Adv. Electron. Mater.* 3, 1600282 (2017).

- <sup>9</sup> S. Manipatruni, D. Nikonov, C. C. Lin, T. A. Gosavi, H. Liu, B. Prasad, Y. L. Huang, E. Bonturim, R. Ramesh, and I. A. Young. *Nature* 565, 35 (2019).

- <sup>10</sup> J. Lee, S. Hong, H. Kim, J. Chang, and H. C. Koo, Reconfigurable spin logic device using electrochemical potentials, *Appl. Phys. Lett.* 114, 152403 (2019).

- <sup>11</sup> M. Zeng, L. Shen, H. Su, C. Zhang, and Y. Feng, Graphene-based spin logic gates, *Appl. Phys. Lett.* **98**, 092110 (2011).

- <sup>12</sup> P. Zhao and G. Chen, Spin-polarized transport properties and spin molecular Boolean logic gates in planar four-coordinate Fe complex-based molecular devices with carbon nanotube bridges and electrodes, *J. Magn. Magn. Mater.* 493, 165712 (2020).

- <sup>13</sup> P. Gypens, J. Leliaert, and B. Van Waeyenberge, Balanced magnetic logic gates in a Kagome spin ice, *Phys. Rev. Applied* 9, 034004 (2018).

- <sup>14</sup> W. Yu, J. Lan, and J. Xiao, Magnetic logic gate based on polarized spin waves, *Phys. Rev. Applied* 13, 024055 (2020).

- <sup>15</sup> X. Xu, W. Yao, D. Xiao, and T. F. Heinz, Spin and pseudospins in layered transition metal dichalcogenides. *Nat. Phys.* **10**, 343 (2014).

- <sup>16</sup> J. R. Schaibley, H. Yu, G. Clark, P. Rivera, J. S. Ross, K. L. Seyler, W. Yao and X. Xu, Valleytronics in 2D materials, *Nat. Rev. Mater.* 1, 16055 (2016).

- <sup>17</sup> D. Xiao, G. B. Liu, W. Feng, X. Xu, and W. Yao, Coupled Spin and Valley Physics in Monolayers of MoS<sub>2</sub> and Other Group-VI Dichalcogenides, *Phys. Rev. Lett.* **108**, 196802 (2012).

- <sup>18</sup> T. Cao, G. Wang, W. Han, H. Ye, C. Zhu, J. Shi, Q. Niu, P. Tan, E. Wang, B. Liu, and J. Feng, Valley-selective circular dichroism of monolayer molybdenum disulphide, *Nat. Commun.* 3, 887 (2012).

- <sup>19</sup> E. Y. Tsymbal, O. N. Mryasov, and P. R. LeClair, Spin-dependent tunnelling in magnetic tunnel junctions, *J. Phys.: Condens. Matter* 15, R109 (2003).

- <sup>20</sup> L. L. Tao and J. Wang, Giant magnetoresistance and perfect spin filter effects in manganese phthalocyanine based molecular junctions, *Nanoscale* 9, 12684 (2017).

- <sup>21</sup> A. Rycerz, J. Tworzydło, and C. W. J. Beenakker, Valley filter and valley valve in graphene, *Nat. Phys.* 3, 172 (2007).

- <sup>22</sup> J. Nakabayashi, D. Yamamoto, and S. Kurihara, Band-Selective Filter in a Zigzag Graphene Nanoribbon, *Phys. Rev. Lett.* **102**, 066803 (2009).

- <sup>23</sup> Y. Kim and J. D. Lee, Proposed Valley Valve from Four-Channel Valley Manipulation, *Phys. Rev. Applied* 11, 034048 (2019).

- <sup>24</sup> Y. S. Ang, S. A. Yang, C. Zhang, Z. Ma, and L. K. Ang, Valleytronics in merging Dirac cones: All-electric-controlled valley filter, valve, and universal reversible logic gate, *Phys. Rev. B* 96, 245410 (2017).

- <sup>25</sup> L. L. Tao and E. Y. Tsymbal, Two-dimensional spin-valley locking spin valve, *Phys. Rev. B* **100**, 161110(R) (2019).

- <sup>26</sup> C. C. Liu, H. Jiang, and Y. Yao, Low-energy effective Hamiltonian involving spin-orbit coupling in silicene and two-dimensional germanium and tin, *Phys. Rev. B* 84, 195430 (2011).

- <sup>27</sup> M. Ezawa, Valley-Polarized Metals and Quantum Anomalous Hall Effect in Silicene, *Phys. Rev. Lett.* **109**, 055502 (2012).

- <sup>28</sup> L. L. Tao, K. T. Cheung, L. Zhang, and J. Wang, All-electrical generation of spin-polarized currents in quantum spin Hall insulators, *Phys. Rev. B* 95, 121407(R) (2017).

- <sup>29</sup> M. Ezawa, Monolayer Topological Insulators: Silicene, Germanene, and Stanene, *J. Phys. Soc. Jpn.* 84, 121003 (2015).

- <sup>30</sup> S. Datta, *Electronic Transport in Mesoscopic Systems* (Cambridge University Press, Cambridge, England, 1997).

- <sup>31</sup> X. Qian, J. Liu, L. Fu, and J. Li, Quantum spin Hall effect in two-dimensional transition metal dichalcogenides, *Science* **346**, 1344 (2014).

- <sup>32</sup> H. Yuan, M. S. Bahramy, K. Morimoto, S. Wu, K. Nomura, B. J. Yang, H. Shimotani, R. Suzuki, M. Toh, C. Kloc, X. Xu, R. Arita, N. Nagaosa, and Y. Iwasa, Zeeman-type spin splitting controlled by an electric field, *Nat. Phys.* 9, 563 (2013).