# An mm-Wave Synthesizer With Robust Locking Reference-Sampling PLL and Wide-Range Injection-Locked VCO

Dongyi Liao<sup>✉</sup>, Yucai Zhang, *Member, IEEE*, Fa Foster Dai<sup>✉</sup>, *Fellow, IEEE*, Zhenqi Chen, *Senior Member, IEEE*, and Yanjie Wang, *Senior Member, IEEE*

**Abstract**—In this article, a two-stage millimeter (mm)-wave frequency synthesizer with low in-band noise and robust locking reference-sampling techniques is presented. Using a two-stage scheme allows separately dealing with the low phase noise (PN) frequency synthesis in the first stage and the mm-wave frequency multiplication in the second stage, achieving the best overall power efficiency. In the first stage, a voltage domain reference-sampling phase detector (RSPD)-locked loop (RSPLL) is adopted to achieve both low PN and robust locking without additional frequency locking loop. A reference reshaping buffer is implemented to improve the phase detector gain and in-band PN. The reference rising/falling time is programmable to achieve optimal RSPLL performance even under external disturbances. The second stage employs an injection-locked voltage-controlled oscillator (ILVCO) for 4× frequency multiplication. A low-power digital frequency tracking loop (FTL) detecting actual frequency errors is implemented in order to achieve wide operation range for the ILVCO while using a high  $Q$  tank with low power. The prototype synthesizer was fabricated in a 45-nm partially depleted silicon on insulator (PDSOI) CMOS technology. The first stage 9-GHz RSPLL achieves 144-fs integrated jitter with 7.2-mW power consumption, achieving a figure of merit (FoM) of  $-248$  dB and the overall mm-wave synthesizer achieves 251-fs integrated jitter with 20.6-mW power consumption at 35.84 GHz, achieving an FoM of  $-238.9$  dB.

**Index Terms**—Frequency tracking loop (FTL), injection-locked frequency divider (ILFD), injection-locked oscillator, millimeter (mm)-wave frequency generation, reference-sampling phase detector (RSPD)-locked loop (RSPLL), sub-sampling PLL (SSPLL).

## I. INTRODUCTION

THE next-generation 5G network requires mobile transceivers to operate over millimeter (mm)-wave bands of around 28–40 GHz. Compared to its predecessor at the sub-6-GHz band, this giant leap in operating frequency presents new challenges to radio frequency integrated circuit (RFIC) designs. The wider channel bandwidth at the mm-wave frequency range is utilized to provide higher data rate. To

Manuscript received July 2, 2019; revised October 7, 2019 and November 25, 2019; accepted November 26, 2019. Date of publication January 10, 2020; date of current version February 25, 2020. This article was approved by Guest Editor Qun Jane Gu. (Dongyi Liao and Yucai Zhang contributed equally to this work.) (Corresponding author: Fa Foster Dai.)

D. Liao is with Qualcomm Technologies Inc., San Diego, CA 92121 USA.

Y. Zhang and F. F. Dai are with the Department of Electrical and Computer Engineering, Auburn University, Auburn, AL 36849 USA (e-mail: daifa01@auburn.edu).

Z. Chen and Y. Wang are with Digital Analog Integration Inc., Auburn, AL 36830 USA.

Color versions of one or more of the figures in this article are available online at <http://ieeexplore.ieee.org>.

Digital Object Identifier 10.1109/JSSC.2019.2959513

support a more complicated modulation scheme including 256-quadratic-amplitude modulation (QAM), the local oscillator (LO) in the RF transceiver chain is required to achieve an integrated phase noise (PN) of less than  $-30$  dBc at 5G mm-wave bands [1]. This puts more stringent restrictions on the amount of jitter produced by the integrated frequency synthesizer. Another major challenge is to minimize the increased power consumption of the mm-wave synthesizer. The fast deteriorating quality factor of the integrated  $LC$  tank at mm-wave frequency costs high power consumption in order to generate a low-noise carrier in mm-wave oscillator. In this regard, we have adopted a two-stage approach [1]–[3] where the second stage consists of a noisy but power efficient injection-locked voltage-controlled oscillator (ILVCO). The overall system PN will be dominated by the first stage where the PN of the mm-wave VCO is largely suppressed due to injection locking. Thus, a low-noise mm-wave synthesizer can be achieved with lower total power consumption. In addition, the adopted partially depleted silicon on insulator (PDSOI) CMOS process provides faster transistor with an  $f_t$  reaching 290 GHz and inductors with high quality factor due to high substrate resistivity. All these are very beneficial for our mm-wave synthesizer performance.

To reduce the PN of the first stage phase-locked loop (PLL), a type-I reference sampling PLL (RSPLL) structure has been adopted. Compared to sub-sampling PLL (SSPLL) [4], the RSPLL [5] can extend the phase detector (PD) capture range from half VCO cycle to half reference cycle, thus not requiring additional frequency loops where the integration of two loops can be nontrivial [6]. Although RSPLL has adopted a similar voltage domain PD as in SSPLL where the phase error is first transferred to the voltage error, directly using reference edge as the sampled slope causes a much lower PD gain in RSPLL. This requires a much larger sampling capacitor in RSPLL to suppress the sampling noise compared to SSPLL.

In our proposed RSPLL design, a reference clock buffer has been introduced to reshape the external reference clock into a square wave with programmable rising/falling time. This helps boost the PD gain and isolate it from the external reference waveform. Since the large gain of voltage domain PD is maintained only within the rising/falling edge of the sampled waveform, its linear range is proportional to the edge transition time. Large external disturbance coupled into the loop might cause the gated VCO edge to fall out of the sampled edge, which degrades the actual PD gain and the

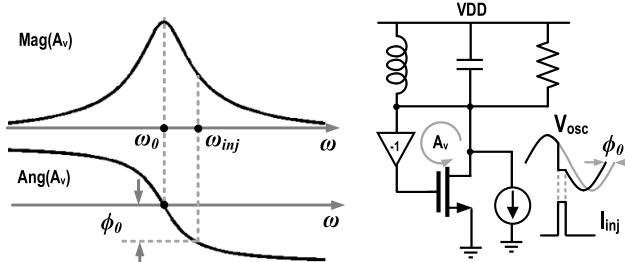

Fig. 1. Conceptual illustration of *LC* tank-based ILVCO.

in-band noise floor. Using the proposed reference reshaping buffer, the slope of the sampled edge becomes programmable: a faster slope leads to higher PD gain and lower PLL in-band noise floor, whereas a slower slope leads to wider linear range and thus improved robustness against external disturbances.

ILVCO gains attractions as the second stage for the mm-wave frequency synthesizer due to its low additional noise and power [7]–[9]. Depending on the ratio of input and output frequency, injection locking technique can be categorized into three cases. The working principle of the fundamental-frequency injection locking is illustrated in Fig. 1 [10]. Assuming the tank has a free-running frequency  $\omega_0$ , an external signal  $\omega_{\text{inj}}$  is injected into the tank, introducing a phase shift  $\phi_0$ ; ILVCO will sustain oscillation at  $\omega_{\text{inj}}$  if the total loop phase shift including  $\phi_0$  equals  $2\pi$  to meet the Barkhausen oscillation criteria. The frequency locking range increases with higher relative injection strength, higher  $\omega_0$ , and lower tank  $Q$ . For sub-harmonic injection locking cases such as ILVCO, the *LC* tank will be locked to an oscillation frequency of  $\omega' = n \cdot \omega_{\text{inj}}$ . On the other hand, in a super-harmonic injection locking case such as frequency dividers,  $\omega_0$  is close to the  $n$ th sub-harmonic of the injection signal, and thus the locked tank oscillation frequency will be  $\omega' = (1/n) \cdot \omega_{\text{inj}}$ .

For the ILVCO design, there are significant challenges to achieve a wide locking range with low power consumption, since a higher tank  $Q$  leads to better PN and lower power but narrower frequency locking range. In [7], it was proposed to improve the locking range through a higher order tank. However, this leads to substantial penalty in lowered tank  $Q$  and a much higher power consumption reaching 148 mW. Alternatively, methods to calibrate VCO free-running frequency were proposed to mitigate this problem: the envelope detection frequency tracking loop (FTL) proposed in [8] and [9] provides a power efficient method to detect frequency error. However, it is prone to miss the frequency drift after the initial lock. Another approach [9] based on the average phase detection FTL relies on a specific phase delay of quadrature VCOs (QVCO) and may limit the lock range since it only detects the phase deviation.

For our proposed ILVCO, a low-power auxiliary FTL which detects the actual frequency error to tune the VCO free-running frequency for robust injection locking is implemented. This method provides an effective approach that does not require any special VCO structure and can be applied in various mm-wave frequency multipliers. To minimize the power overhead of the FTL loop, an inductor-less injection-locked frequency divider (ILFD) is implemented as the first stage

Fig. 2. Illustration of a two-stage PLL architecture PN upscaling compared to a single-stage PLL design.

mm-wave prescaler. Through tuning the delay of each stage in the ILFD, multiple integer division ratios can be achieved to extend the output frequency range when used as output divider, or allow frequency multiplication with other ratios when used in FTL loop for ILVCO.

This article is an extension of [11], with a more detailed theoretical analysis and circuit design. It is organized as follows. Section II discusses the advantage of multistage mm-wave synthesizers, along with theoretical analysis and simulation results for our presented RSPLL; Section III presents the implementation details of the entire synthesizer system; the measurement results and conclusions are given in Sections IV and V, respectively.

## II. DESIGN OF A LOW-NOISE mm-WAVE PLL

### A. Multistage mm-Wave PLL Architecture

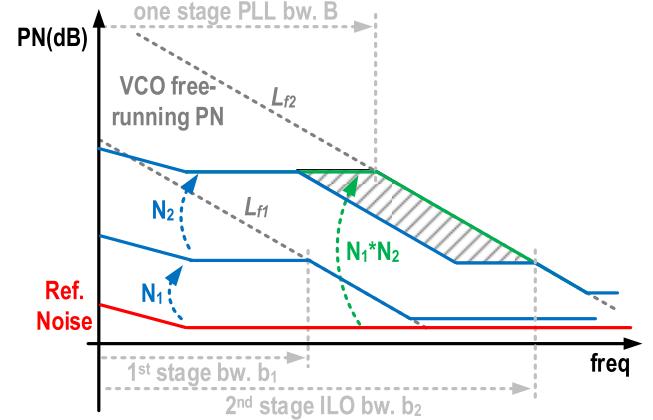

Since it is difficult to directly generate an mm-wave carrier and achieve overall good PLL figure of merit (FoM) with a single-stage frequency synthesizer, most recent publications rely on the two-stage architecture [2]. The FoM disadvantage from the single-stage architecture is mainly due to the dramatically degraded integrated VCO performance at the mm-wave frequency. As illustrated in Fig. 2,  $L_{f1}$  and  $L_{f2}$  represent the VCO free-running PN at an intermediate frequency  $f_1$  and the mm-wave frequency  $f_2$ . In a two-stage PLL structure, the reference clock is first upscaled with a factor of  $N_1$  to reach  $f_1$ . To achieve minimal integrated PN, the bandwidth of first-stage PLL is usually set at the intersection of  $L_{f1}$  ( $b_1$  as labeled in Fig. 2), and the elevated reference PN which is  $N_1$  times larger due to frequency upscaling. At the second stage, this intermediate frequency is further multiplied by  $N_2$  through a frequency multiplier such as ILVCO and reaches  $f_2$ . Due to the relatively high  $f_1$ , the close-in PN at mm-wave output is largely determined by the first-stage PLL. At far-out frequency  $b_2$ , which represents the bandwidth of the second-stage ILVCO, the output PN follows  $L_{f2}$ . Eventually the mm-wave VCO PN in the two-stage architecture can be suppressed with a narrow loop bandwidth  $b_1$ . Whereas for a single-stage design, the reference noise is directly multiplied by  $N_1 \cdot N_2$  times, achieving similar in-band noise floor but requiring a higher loop bandwidth  $B$  to suppress VCO PN. The shaded

part represents the additional noise from a single-stage structure for side-by-side comparison.

As a quantitative example, using a reference clock running at 80 MHz with a PN floor of  $-155$  dBc/Hz beyond 100-kHz offset frequency, its contribution to PLL in-band noise floor after frequency multiplication by  $100 \times (N_1)$  and another  $4 \times (N_2)$ , corresponding to first-stage PLL ( $f_1 = 8$  GHz) and second-stage ILVCO ( $f_2 = 32$  GHz), would be  $-115$  and  $-103$  dBc/Hz, respectively. This is under the assumption that second-stage ILVCO injects negligible in-band PN, which is verified in our measurement as shown later. In a two-stage configuration, using our measured first-stage VCO and second-stage mm-wave VCO data where  $L_{f1}$  is  $-110$  dBc/Hz (at 1-MHz offset) and  $L_{f2}$  is  $-86$  dBc/Hz (at 1-MHz offset) at 8.4 and 35.7 GHz, respectively, the loop bandwidth of first-stage PLL is set to 2 MHz ( $b_1$ ) where in-band noise floor intersects  $L_{f1}$  for optimal integrated PLL jitter. The second-stage ILVCO bandwidth is set wide enough where the mm-wave VCO reaches noise floor to avoid injecting additional noise, assuming 20 MHz ( $b_2$ ) in this case. On the other hand, using a one-stage PLL architecture for a direct frequency multiplication of  $400 \times$ , its loop bandwidth needs to reach about 5 MHz ( $B$ ). Integrating the PN profile of both configurations from 1-kHz to 100-MHz offset frequency gives an integrated jitter of 157 and 107 fs at 32 GHz, or about 46% additional jitter from a two-stage to a one-stage architecture.

Despite the PN advantage of the multistage PLL architecture, having an additional stage in the frequency generation chain unavoidably leads to more hardware and higher power consumption. Fortunately, such penalties can be partially alleviated in the following ways.

- 1) Since the mm-wave PN profile largely depends on the first-stage output, the noise requirement on the mm-wave VCO (which usually dominates the power consumption of the entire synthesizer) can be relaxed, resulting in less power consumption.

- 2) Through reducing the second-stage frequency upscaling ratio  $N_2$ , a simpler loop architecture can be utilized in the second-stage PLL, reducing or even eliminating power hungry loop components like mm-wave dividers. Furthermore, by operating at this intermediate frequency rather than directly at the mm-wave frequency range, it is more power efficient to implement jitter reduction techniques in the first-stage PLL.

### B. Reference Sampling With Programmable Sampled Slope

Ever since the introduction of SSPLL several years ago [4], voltage sampling technique has attracted increasing attention in state-of-the-art PLL designs [11]–[15]. As shown in Fig. 3, the sub-sampling phase detector (SSPD) in an SSPLL measures the phase errors by sampling the fast VCO edge using the reference clock, achieving a large PD gain:  $V_{PD} = A_{VCO}\phi_e$ , or the PD output voltage equals to VCO amplitude times phase error. This large gain consequently suppresses noise from the subsequent stages including charge pump (CP) and loop filter (LF). However, the detected voltage

Fig. 3. Conceptual diagram for different sampling schemes in the voltage-mode PLL.

from the SSPLL is valid only within the half-VCO cycle. On the other hand, RSPLL, proposed in [6], uses a gated VCO edge to sample the sinusoidal reference clock. The detected voltage remains roughly proportional to the phase error over half of the reference period. Thus, in terms of locking robustness, RSPLL is much more improved compared to SSPLL. However, the PD gain in this case is lower:  $V_{PD} = A_{ref}\phi_e/N$ , or roughly  $N$  times smaller than that of an SSPLL. Thus, it requires a large sampling capacitor to achieve similar in-band noise suppression. In sum, SSPLL and RSPLL represent two extreme phase lock topologies: SSPLL achieves large PD gain with small detection range, whereas RSPLL achieves large detection range with reduced PD gain.

In our proposed design, a programmable slope generator is added to the reference clock before it is sampled by the VCO edge for the tradeoff between the PD gain and the PD detection range. A similar slope buffer has been proposed for SSPLL [16], wherein a larger PD detection range can be achieved with RSPLL as it is not limited by the VCO period. As shown in Fig. 3, the transition time of the rising or falling edge after reshaping the reference waveform is largely determined by the  $RC$  time constant at reference buffer output. Define a loop feedback gain  $\beta$  as follows:

$$\beta = \frac{V_{PD}}{\phi_e} = T_{ref} / (2\pi \cdot \tau_{rising}) \cdot A_{ref} \cdot \frac{1}{N} \quad (1)$$

where  $T_{ref}$  and  $\tau_{rising}$  denote the reference period and the rising time of the reshaped reference waveform, respectively. Considering  $(T_{ref}/2\pi \cdot \tau_{rising}) \gg 1$ , the achieved PD gain is much greater than that in the original RSPLL without slope shaping. In addition, the locking range is kept as one reference cycle, leading to robust locking. Note that even though the polarity of the reference-sampling phase detector (RSPD) output is correct in one reference period (12.5 ns), the linear range is still limited to the sampled edge rising time ( $\sim$ hundreds of ps). Outside the sampled edge, the RSPD saturates and causes much smaller PD gain, elevating the PLL in-band noise floor level. In normal integer operation, the phase error after lock should be ideally close to zero.

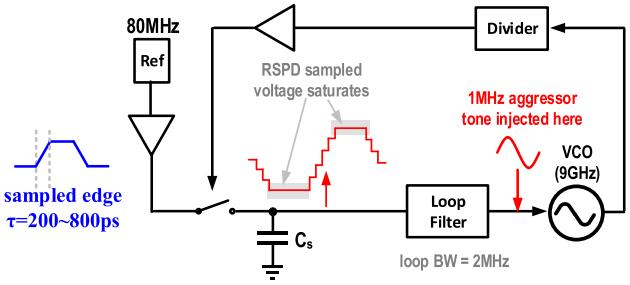

Fig. 4. Behavioral RSPLL model for external disturbance simulation. Large aggressor causes RSPD saturation, reduces PD gain, and degrades in-band PN in saturation regions.

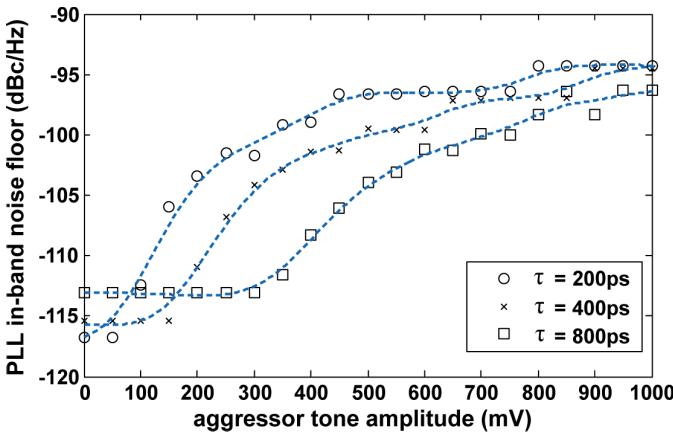

Fig. 5. Simulated in-band PN degradation with increasing aggressor tone amplitude. Simulation results are shown as symbols along with three interpolated curves for different rising times ( $\tau$ ) of the reshaped reference edge.

However, under scenarios with large external disturbances, large jitter might occur on the sampling edge, forcing RSPD into saturation.

To understand this phenomenon, a simplified model for our proposed RSPLL design has been built as shown in Fig. 4. The reference clock is reshaped into a square wave with a limited rising/falling time of  $\tau$ . After being sampled by the divided VCO clock, the charge is stored in the sampling capacitor  $C_s$ . The external aggressor can be coupled into the system through several mechanisms such as layout parasitics or power line coupling, etc. In this model, aggressor tones at 1 MHz with various amplitudes are injected at LF output due to large layout area of the integrated LF. Large aggressor amplitude causes RSPD to saturate and clip to the rail on the RSPD output. In these shaded regions, the PD gain is largely suppressed, degrading both loop gain and in-band noise level. In Fig. 5, three levels of sampled edge time  $\tau$  have been simulated over increasingly larger aggressor tone amplitudes. Larger  $\tau$  causes RSPLL in-band noise to rise at higher aggressor power level, implying that it is less sensitive to external disturbances. On the other hand, a smaller  $\tau$  results in better in-band noise floor in the absence of disturbances due to stronger suppression for RSPD and LF noise.

Since a type-I PLL structure is adopted for this design, the major in-band noise contributor is the slope generator and RSPD, which are implemented with a current mode logic

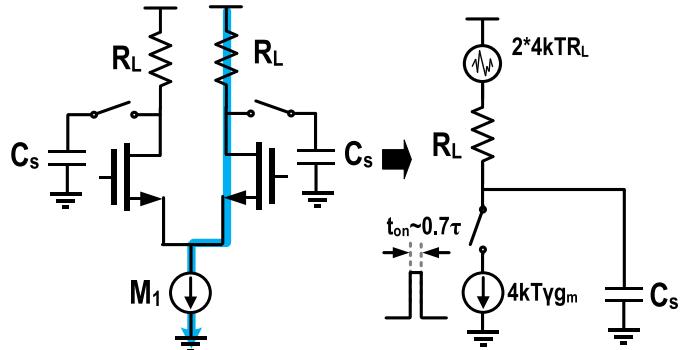

Fig. 6. Simplified noise model of the reference sampling PD.

(CML) buffer loaded by a sampling capacitor  $C_s$  as shown in the simplified diagram (Fig. 6). Assuming that the differential input reference clock is switching relatively fast, such that the differential pair mostly stays in switching mode in which all the current flows through one branch, this allows us to make a simplification of dividing the left and right branches for noise analysis. Assuming the turn on time of current source connected to sampling capacitor is  $t_{on} = 0.7\tau$  to reach 50% of output swing (here  $\tau$  represents the time constant  $R_L C_s$ ), the noise at RSPD output can be shown as follows [17]:

$$v_{n,RSPD}^2 = \frac{kT}{C_s} (2 + \gamma g_m R_L (1 - e^{-2t_{on}/\tau})) \quad (2)$$

where  $\gamma$  and  $g_m$  represent the channel thermal noise coefficient and transconductance of current source  $M_1$ . The two terms in (2) represent contribution from load resistor  $R_L$  and current source  $M_1$ , respectively. Dividing (2) over the loop feedback gain  $\beta^2$  as in (1) gives the in-band noise contribution from RSPD, which is approximately proportional to  $\tau_{\text{rising}}^2$ . Thus, RSPD noise rises with slower reshaped reference edge.

### III. IMPLEMENTATION OF A TWO-STAGE mm-WAVE FREQUENCY SYNTHESIZER

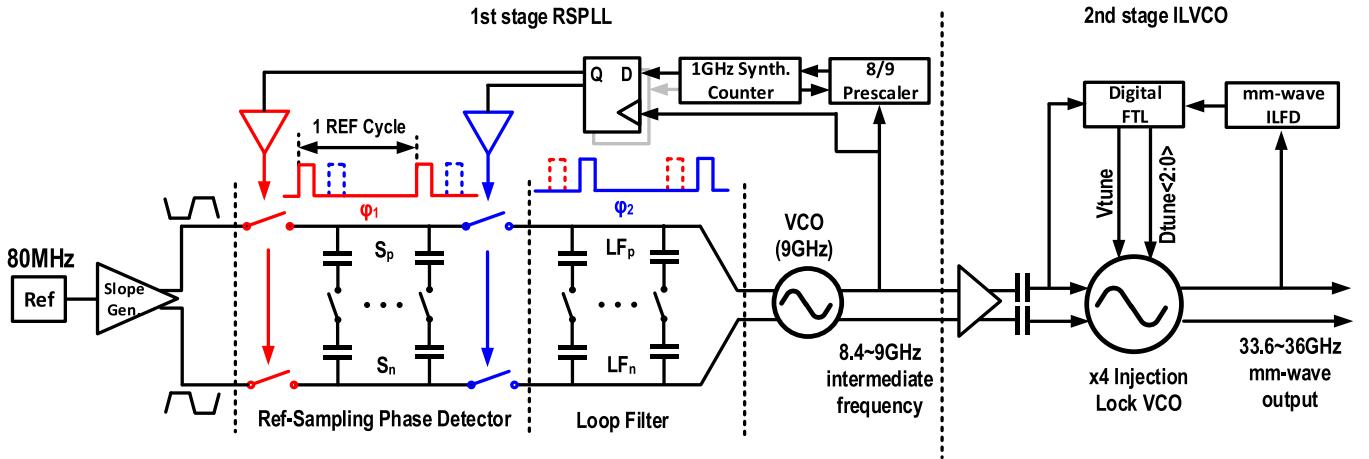

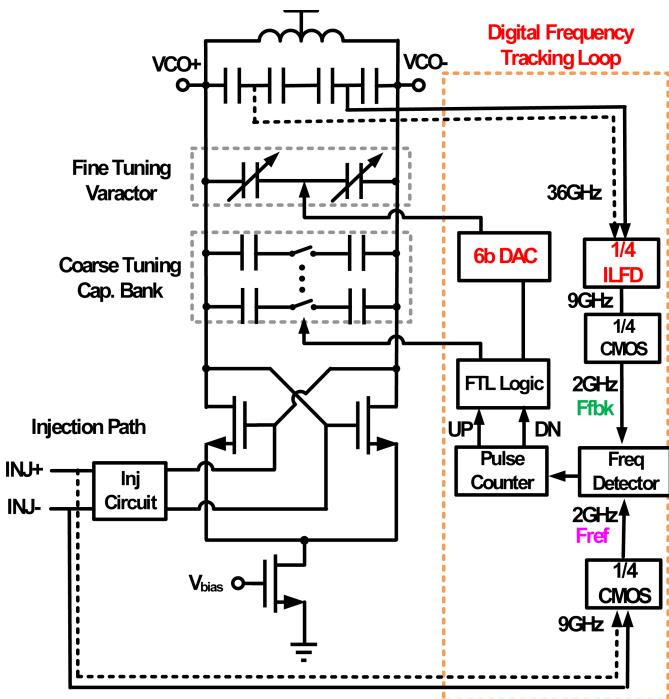

The block diagram of our proposed two-stage cascaded PLL architecture is shown in Fig. 7. The first stage is a type-I low-noise RSPLL with reference reshape buffer, while the second stage is an mm-wave ILVCO. The injection ratio between the first-stage RSPLL and the second-stage ILVCO is chosen to be  $4\times$ . Therefore, the first-stage target frequency is 8–9 GHz and the second-stage target frequency is 32–36 GHz. This frequency plan relaxes the operating frequency of the first-stage RSPLL to allow using inductor with a higher quality factor and lower power to achieve better FoM. The ILVCO injection lock range is simulated to be around  $\pm(40\text{--}60)$  MHz for a  $4\times$  injection ratio. As a comparison, a  $3\times$  injection ratio might obtain  $\pm(100\text{--}150)$ -MHz lock range, but it would require the first-stage RSPLL to be running at 12 GHz with higher power.

#### A. First-Stage Low Noise Type-I RSPLL

In the first-stage RSPLL, the external 80-MHz reference clock is multiplied to 9 GHz as an intermediate clock for the second stage. To avoid the noise and power due to CP, a type-I PLL structure was adopted. However, having one less pole

Fig. 7. Block diagram of the proposed two-stage mm-wave frequency synthesizer.

Fig. 8. Schematic of the reference sampling PD.

compared to a common type-II design leads to less in-band VCO PN suppression and a nonzero residual phase error. For PLL in-band noise, loop gain provides 20-dB/dec suppression which cancels the 20-dB/dec rising slope of VCO free-running PN, leading to a flat in-band VCO noise floor. However, for very small frequency offset, VCO PN enters the  $1/f^3$  region and flicker noise starts to arise at PLL output. Thus, a larger loop bandwidth is required in a type-I PLL to suppress the VCO PN.

The loop divider adopted a pulse-swallow structure, consisting of an 8/9 prescaler running at VCO frequency ( $\sim 9$  GHz) followed by a synthesized digital counter running at the divided VCO frequency ( $\sim 1$  GHz). Division ratio at prescaler is controlled by a digital counter dynamically to provide continuous division ratio programmability. Due to the large loop division ratio (100–112), the pulse-swallow divider can continuously support all the ratios over the required range [18]. The synthesized digital counter generates two output pulses,  $\varphi_1$  and  $\varphi_2$ , to control the RSPD and LF, each spanning over roughly 2 ns and separated by 1 ns to avoid charge kickback as shown in Fig. 7. The  $\varphi_1$  and  $\varphi_2$  are resampled by the VCO edge at divider output to clean up accumulated jitter going through digital logic.

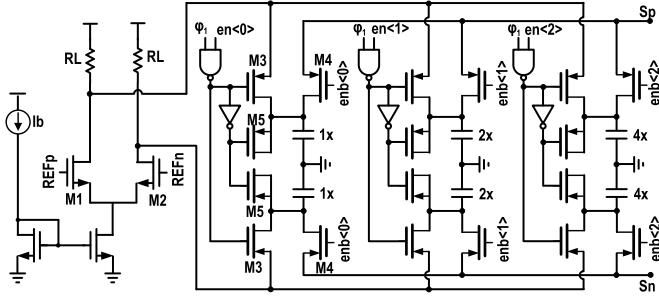

The external reference clock is reshaped with a differential pair and a programmable binary capacitor array as shown in Fig. 8. The reshaped slope is then determined by the time constant of load resistance  $R_L$  and total capacitance  $C_s$  from the capacitor array. The sampling switch  $M_3$  is driven

by  $\varphi_1$  gated with capacitor enable signal  $en<2:0>$ . Another half-sized switch  $M_5$  is driven by an inverted clock to neutralize the charge injected from turning off  $M_3$ . Switch  $M_4$  driven by inverted capacitor enable signal  $enb<2:0>$  connects the activated capacitors to the output  $S_p/S_n$ . To implement a type-I PLL, a switched cap circuit is utilized as the LF. A capacitor array is built for programmable loop bandwidth. When  $\varphi_2$  becomes high, charges stored in the sampling capacitor  $C_s$  are redistributed onto the capacitor array in LF. The equivalent filter  $RC$  time constant implemented with the switched capacitor circuit can be shown as follows:

$$R_{LF}C_{LF} = \left( R_{sw} + \frac{1}{f_{ref}C_s} \right) \cdot C_{LF} \sim \frac{1}{f_{ref}} \frac{C_{LF}}{C_s} \quad (3)$$

where  $R_{sw}$  is the switch ON resistance and  $C_s$  is the sampling capacitance in RSPD. Assuming  $R_{sw}$  is small, the LF pole frequency only depends on reference clock and capacitor ratio between the LF and the RSPD.

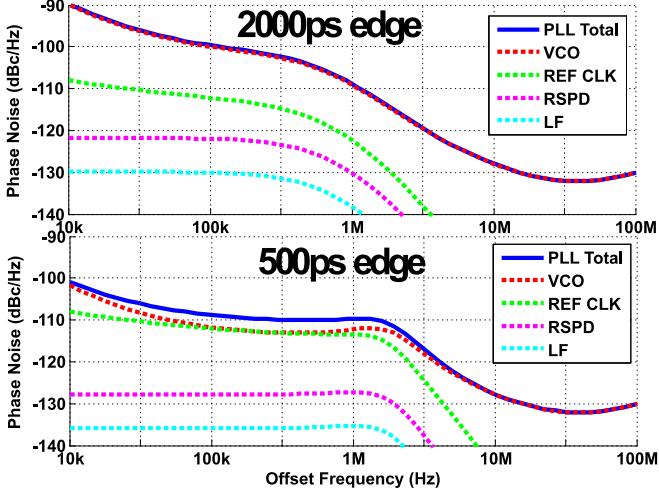

The RSPLL loop bandwidth for optimal total PN is around 2 MHz, where the in-band noise floor and VCO noise intersect. The RSPD load resistor is  $400 \Omega$  with a swing of 600 mV at CML buffer output. The sampling capacitor  $C_s$  can be programmed from 0.25 to 1.75 pF, leading to a reference edge rising time of about 500 ps–2 ns. The LF capacitor  $C_{LF}$  is fixed at eight times the sampling capacitance, creating the second pole at 10 MHz. The RSPLL output PN is simulated for the fastest and slowest sampled edge as shown in Fig. 9. For the slow edge case, the loop bandwidth is about 500 kHz. The small loop bandwidth makes the in-band noise floor dominated by VCO PN due to the weak out-band noise suppression in type-I PLL. For the fast edge case, the loop bandwidth has reached 2 MHz, making the reference clock and VCO contribute equally to the PLL in-band noise floor, reaching an improved in-band noise floor of about  $-110$  dBc/Hz at 8.4 GHz. Although the RSPD has contributed negligible PN, its noise contribution has increased by about 6 dB from the fast sampled edge to the slow sampled edge case, which agrees with our previous noise analysis for RSPD.

Fig. 9. Simulated RSPLL PN at 8.4 GHz with slow and fast reference sampled edges.

Fig. 10. Schematic of the second-stage injection-locked frequency multiplier with a digital FTL.

### B. Second-Stage mm-Wave Injection-Locked Frequency Multiplier

The proposed ILFM topology is shown in Fig. 10. It consists of an ILVCO and a low-power and low-area digital FTL with smooth lock transition. An inductor-less mm-wave ILFD has been adopted in FTL to save power and area. The FTL loop directly detects the actual frequency deviations rather than the envelope or the phase deviations as presented in [8] and [9], which relies on specific VCO or QVCO phase delay characteristics. The proposed digital FTL also resolves the dilemma between extending the injection locking for robust locking over larger frequency range, and increasing the tank  $Q$  to achieve lower PN and power.

Fig. 11. Injection circuit and timing diagram.

Fig. 12. Schematic of the simplified asynchronous sampling FD.

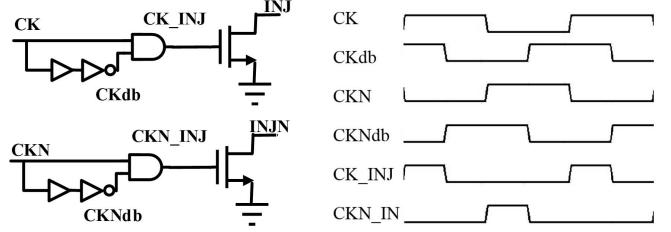

**1) ILFM Circuit Structure:** To meet the frequency tuning range requirement, the ILVCO is implemented with four binary weighted high- $Q$  metal-insulator-metal (MIM) capacitor banks for coarse frequency tuning (total 16 coarse frequency bands), and one varactor bank for fine frequency tuning. The tank inductor and the parasitic inductance on the interconnection between the inductor and the rest of the VCO have all been extracted in electromagnetic (EM) simulation to better predict the VCO frequency and  $Q$ -factor. A high  $Q$  inductor ( $Q \sim 19$  at 40 GHz) was achieved for the PDSOI process. The simulated PN was  $-83.7$  to  $-91.7$  dBc/Hz at 1-MHz offset for the highest VCO frequency around 36 GHz. The injection circuit (details shown in Fig. 11) is a pair of pulse generators with  $\sim 20\%$  duty cycle. It injects currents into the  $LC$  tank on both rising and falling input clock edges, reducing the effective internal frequency injection ratio to  $2\times$ .

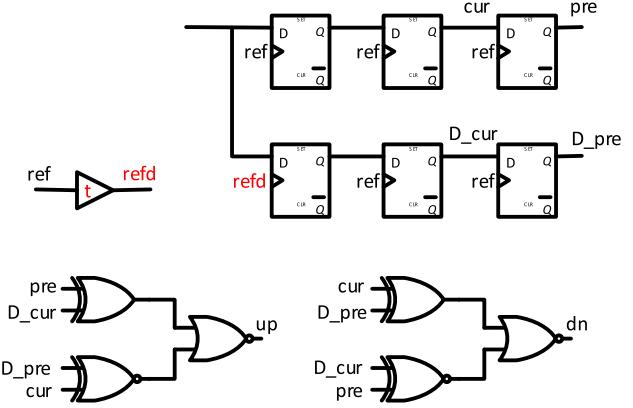

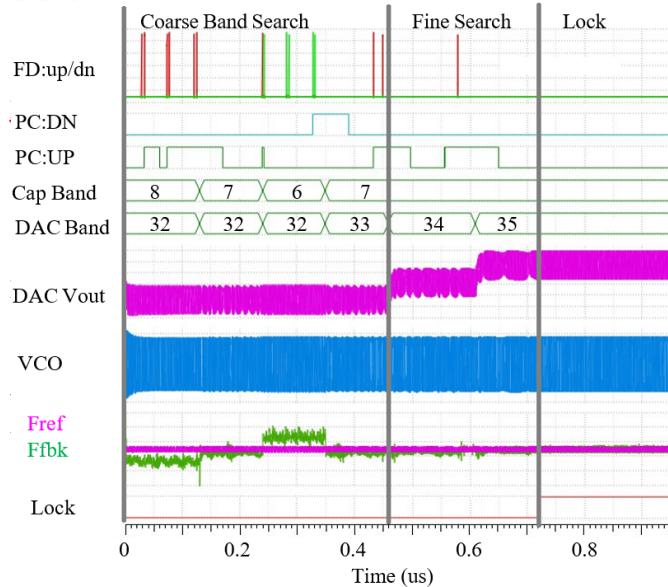

The circuit in the dashed box in Fig. 10 is our proposed digital FTL. It consists of a wideband power-efficient ILFD, two divide-by-4 CMOS dividers, a low-power CMOS asynchronous sampling frequency detector (FD) [19], a pulse counter, the FTL logic, and a 6-bit voltage DAC. As illustrated in Fig. 12, the FD uses 6 D-flip-flops (DFF) to asynchronously sample the clocks and uses six gates to generate the up- and down-indication signals. Other low-power-type FDs may also be used. The DAC step size was designed for 20 MHz (1/4 of minimum injection lock range) to ensure lock. The frequency locking flow will be illustrated in Section IV. The voltage DAC was employed to provide smooth transition between the frequency lock with FTL and the phase lock through ILVCO. After the VCO is injection-locked, the FTL output codes settle to a constant value where both the MIM capacitor bank (coarse

Fig. 13. Injection locking waveforms (from top to bottom): the FD outputs (the red line is “up” and the green line is “dn” pulses); the pulse counter output DN (down); pulse counter output UP (up); the coarse tuning capacitor bank code; the fine-tuning DAC code; the DAC output voltage; the VCO tank oscillation waveform; reference clock frequency (pink) and feedback clock frequency (green); and the lock signal.

tuning) and the varactor biasing voltage (fine-tuning) remain constant, avoiding additional PN due to the FTL. On the other hand, when the ILVCO loses lock, the FTL FD can instantly detect the frequency deviation and enable FTL logic, bringing ILVCO back to injection lock state.

2) *Frequency Locking Flow*: The FTL logic performs the VCO frequency search in a two-step process, which can be illustrated with the simulated locking transient waveforms as shown in Fig. 13. First, it searches for the optimum coarse tuning capacitor bank that provides the closest free-running frequency to the locked frequency. At the end of each time window, the FTL logic examines the pulse counter outputs which acts as a digital low pass filter and determines the search direction of the coarse tuning code. The search starts from the middle coarse bank 8 in order to save time, then changes one band at a time while the DAC band is fixed in the middle band 32. The coarse band ramping process stops at band 6, where the pulse counter asserts the DN signal indicating that the VCO frequency is above the target. It then goes back one step to band 7 to start the second search for the DAC codes. In a similar fashion, the optimum DAC code controlling fine-tuning varactor biasing is stabilized at code 35 where the VCO’s free-running frequency was in the injection locking range. Then the VCO will quickly injection lock to the  $N$ th harmonic of the reference frequency generated by the first-stage RSPLL (i.e., an injection ratio of  $1:N$ ). Later, the FTL can be turned off to save power, or stay alive to track any instantaneous disturbances or voltage and temperature variations in normal operation. Note that all initial settings and the time window are made programmable for test flexibility. In the presence of beat frequency, the instant

Fig. 14. Simplified schematic of a four-stage ILFD and CML latch in each stage.

Fig. 15. Simulated ILFD injection strength required when biased for self-oscillation frequency  $\sim 9$  GHz.

and average frequency will be higher than  $\omega_{\text{inj}}$  for low-side injection case (or lower than  $\omega_{\text{inj}}$  for high-side injection case) [10]. In Fig. 13, the last few fine band search steps actually illustrate this scenario, where the VCO frequency is not far away from the lock range (as indicated by  $F_{\text{ref}}$  and  $F_{\text{fbk}}$  lines). The phase-frequency detector (PFD) is able to detect the frequency difference, enable the FTL make correct up/down decision, and drive the VCO frequency to fall into final injection lock.

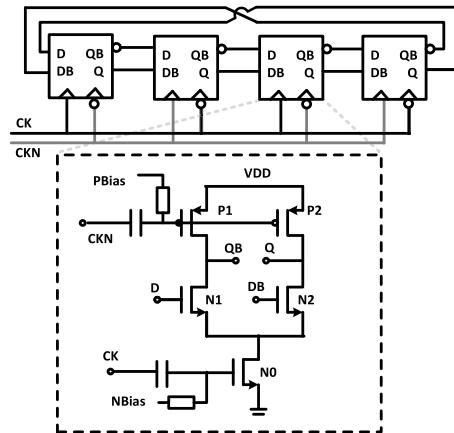

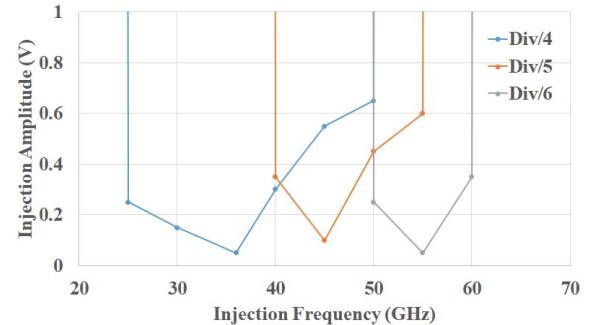

3) *mm-Wave ILFD*: To reduce the power consumption of our proposed digital FTL, an inductor-less mm-wave ILFD comprising of four-stage cascaded CML latches [20] has been utilized as the first stage mm-wave prescaler, as shown in Fig. 14. When a sufficiently strong external clock is injected, the ILFD would be pulled away from its self-oscillation frequency and lock to one of the sub-harmonics of the injected clock. For steady-state injection-locked operation, both loop magnitude and phase need to satisfy Barkhausen criteria (loop gain  $\geq 1$  and loop phase =  $2\pi$ ). For the divide-by- $N$  operation, the total loop delay equals to  $N$  times the injected clock period. Simulation showed our ILFD’s self-oscillation frequency without external excitations to be 7.3–15.4 GHz for the optimized bias condition range, which is mainly determined by the delay in each stage. Fig. 15 shows the simulated injection strength required when biased for self-oscillation frequency  $\sim 9$  GHz as an example.

Fig. 16. Die photograph and the power breakdown of the proposed synthesizer.

Each latch stage comprises of a differential input pair  $N_1/N_2$ , a tail current source  $N_0$  and a pair of PMOS loads  $P_1/P_2$ . The injected differential clock signal  $CK$  is ac-coupled to the gate of  $N_0$  and  $CKN$  is ac-coupled to the gates of  $P_1/P_2$ . The gate dc biasing level can be externally tuned: the gain of each stage can be adjusted through gate biasing on  $N_0$  which tunes the biasing current of the differential pair, whereas the phase delay can be adjusted by the load PMOS ( $P_1/P_2$ ) gate biasing voltage for tuning the load time constant. The two-point injection scheme (at  $N_0$  and  $P_1/P_2$ ) helps extend the locking range. Through tuning these two biasing points, the ILFD in our design is able to provide a division ratio of 4/5/6 as long as the phase and magnitude conditions are satisfied at the divided frequencies. The dynamic latch may be viewed as a conventional static CML latch without the regenerative cross-pair to minimize output capacitance and thus achieves high-speed operation. Note that since  $CK/CKN$  of the ILFD drive odd/even latch stage's  $CK/CKN$  alternatively, the total loading of  $CK/CKN$  is actually symmetric so as not to degrade the preceding VCO's PN performance.

#### IV. MEASUREMENT RESULTS

##### A. mm-Wave Synthesizer Measurement Results

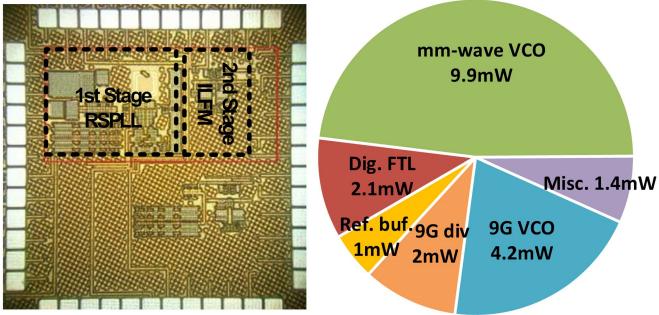

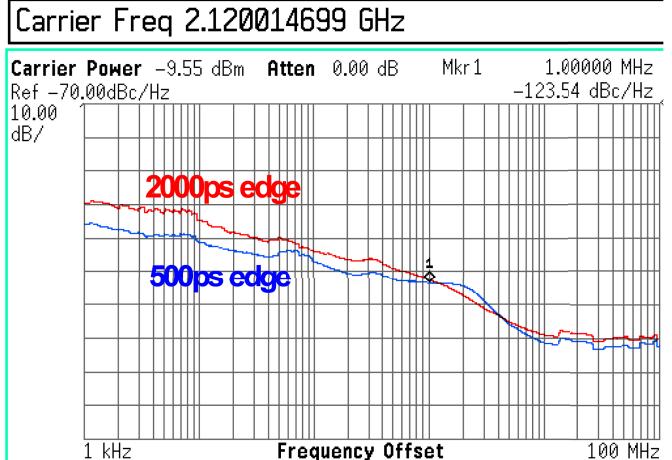

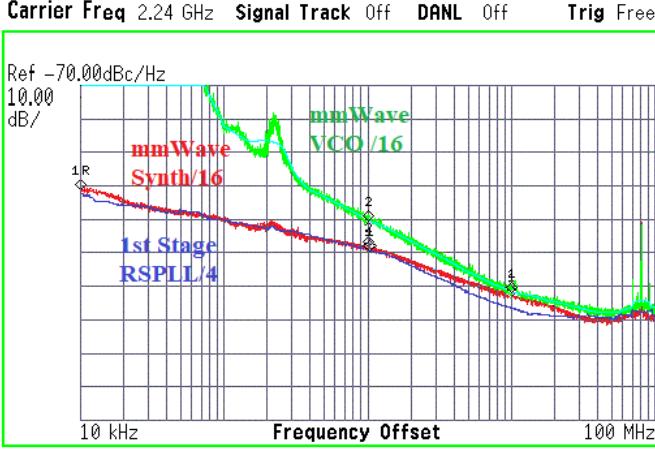

The proposed mm-wave synthesizer MMIC was implemented in a 45-nm PDSOI CMOS process with the die photograph and power breakdown chart shown in Fig. 16. The core active area is only 0.41 mm<sup>2</sup>. The entire two-stage mm-wave synthesizer system consumes 20.6 mW from 1.1/0.9-V power supply. The first and second stages consume 7.2 and 13.4 mW, respectively. The measured PN of the first-stage RSPLL with slow and fast reference sampled edge is shown in Fig. 17. The PLL output frequency was divided by 4 before output for the measurement. Due to the type-I architecture, VCO flicker noise rises along with the loop flicker noise at close-in offset frequency. Using faster sampled edge of 500 ps, a higher loop bandwidth can be achieved, improving VCO noise suppression and in-band noise floor compared to the 2000-ps sampled edge case. The PN was measured as  $-123$  dBc/Hz at 1-MHz offset frequency, achieving an integrated jitter of 144 fs (10 kHz–10 MHz) at 2.24-GHz test frequency, which corresponds to the PLL output at 8.96 GHz. The first-stage RSPLL achieves an FoM of  $-248$  dB as shown in the performance Table I.

Fig. 17. Measured RSPLL PN with slow/fast sampled edge rising time; faster edge helps suppressing VCO in-band noise contribution, leading to lower in-band noise floor. VCO output frequency has been divided by 4 for measurement.

TABLE I

MEASURED RSPLL PERFORMANCES AND COMPARISONS

|                         | Gao [4]<br>JSSC-10 | Dongyi[6]<br>JSSC-17 | Jahnavi[5]<br>ISSCC-18 | This work        |

|-------------------------|--------------------|----------------------|------------------------|------------------|

| Architecture            | SSPLL<br>type-II   | SSPLL<br>type-II     | RSPLL<br>type-I        | RSPLL<br>type-I  |

| Tech                    | 180nm              | 130nm                | 65nm                   | 45nm             |

| Ref. (MHz)              | 55.25              | 50                   | 50                     | 80               |

| Output Freq.<br>(GHz)   | 2.21               | 2.3-2.4              | 2.05-2.55              | 8.4-9            |

| Int. RMS<br>Jitter (fs) | 150<br>(10k-40M)   | 158<br>(10k-10M)     | 110<br>(10k-10M)       | 144<br>(10k-10M) |

| Ref. Spur<br>(dBc)      | -46                | -72                  | -63                    | -48              |

| Power (mW)              | 7.6                | 21                   | 3.7                    | 7.2              |

| FoMp* (dB)              | -247               | -243                 | -253                   | -248             |

$$FOMp = 20\log_{10}(jitter) + 10\log_{10}(Pdc[mW])$$

Similarly, the second-stage mm-wave output was divided 16 times to around 2.24 GHz for the measurement. The first-stage RSPLL output showed about 2-dB in-band PN degradation due to loading and parasitic coupling from the second-stage ILVCO. As shown in Fig. 18, the close-in PN profile closely follows that of the first-stage RSPLL (for frequency offset  $< 1$  MHz), and becomes gradually worse than the RSPLL but still better than the mm-wave VCO between 1 and 30 MHz, then reaches flat noise floor beyond 30 MHz. The injection lock range of the second-stage ILFM is about 10–30 MHz. A higher injection lock bandwidth could further lower the mm-wave synthesizer PN closer to the RSPLL PN in the 1–30-MHz offset range. Note that the measured PN of the ILVCO includes the inductor-less divider noise. Thus, the PN of the implemented ILVCO should be better than what was measured using the divider. The second-stage ILFM achieved an integrated jitter (10 kHz–10 MHz) of 251 fs at 35.84 GHz, reaching a jitter FoM<sub>j</sub> of  $-238.9$  dB as shown in the performance Table II. The back-calculated PN at 35.84 GHz is  $-94.9$  dBc/Hz at 1-MHz offset. Through adopting the proposed FTL structure for mm-wave ILVCO, our design has achieved good PN, low power, and good overall PLL FoM performance.

TABLE II

MEASURED mm-WAVE SYNTHESIZER PERFORMANCES

|                      | Alvin JSSC-14 [7] | Tee. JSSC-16 [21]  | Ying RFIC-17 [22] | Waleed TMTT-17 [2] | Nagarajan TMTT-17 [23] | Zunsong ISSCC-19 [24]  | Ahmed ISSCC-17 [25] | This work          |

|----------------------|-------------------|--------------------|-------------------|--------------------|------------------------|------------------------|---------------------|--------------------|

| Topology             | PLL + 3step ILFM  | SSPLL + 1step ILFM | Single stage PLL  | PLL + SSPLL        | Single stage PLL       | Single stage iSSPD PLL | Single stage ADPLL  | RSPLL + 1step ILFM |

| Tech.                | 65nm              | 65nm               | 250nm             | 65nm               | 0.18um SiGe            | 65nm                   | 65nm                | 45nm               |

| Ref. (MHz)           | 100               | 36/40              | 50                | 230                | 120                    | 103                    | 100                 | 80                 |

| Output Freq. (GHz)   | 20.6-48.2         | 55.6-65.2          | 37.2-40           | 26-32              | 29.5-33.4              | 25.4-29.5              | 50.2-64.8           | 33.6-36            |

| PN @ 1MHz (dBc/Hz)   | -108.1            | -91                | -100.7            | -116.2             | -97                    | -112.8                 | -92.7               | -94.9              |

| Int. RMS Jitter (fs) | -                 | 290 [10k-40M]      | 104 [100k-1M]     | 63.6 [1k-10M]      | 189 [10k-10M]          | 71 [1k-100M]           | 223 [1k-40M]        | 251 [10k-10M]      |

| Ref. Spur (dBc)      | -                 | -73                | <-73              | -63.2              | -40                    | -63                    | <-59.1              | -60                |

| Power (mW)           | 148.3             | 32                 | 323-380           | 26.9               | 63                     | 10.2                   | 46                  | 20.6               |

| FoMp (dB)            | -179              | -171.6             | -170.5            | -191.3             | -168.5                 | -191.1                 | -170                | -172.8             |

| FoMj (dB)            | -                 | -236               | -234              | -249.6             | -237                   | -252.9                 | -236.5              | -238.9             |

FOMp=PN-20log10(f/f0)+10log10(Pdc[mw])

FOMj=20log(Jitter[s])+10log10(Pdc[mw])

Fig. 18. Measured PN of the divided mm-wave output overlaid with the first-stage output and the second-stage mm-wave VCO free-running PN.

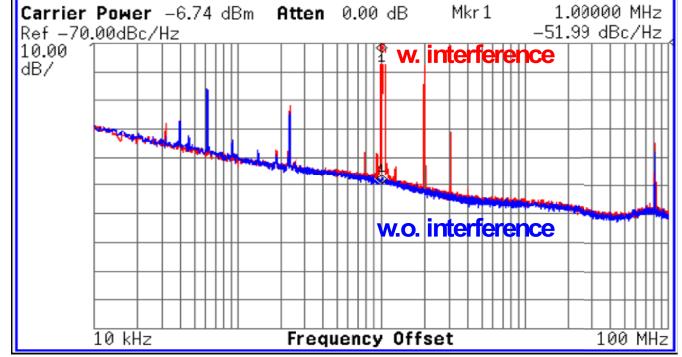

To test the locking robustness of the RSPLL, a 1-MHz 50-mV peak-to-peak sinusoidal disturbance was injected onto the power supply of the first-stage VCO. The mm-wave synthesizer output spectrum in the presence of this disturbance is shown in Fig. 19. Due to its large programmable capture range, the RSPLL remains locked without using an auxiliary frequency lock loop, which is usually required for conventional SSPLLs. The in-band noise floor remains the same as in the case without disturbance. Only a spur corresponding to the injected signal was present in the measured spectrum as an evidence of the disturbance.

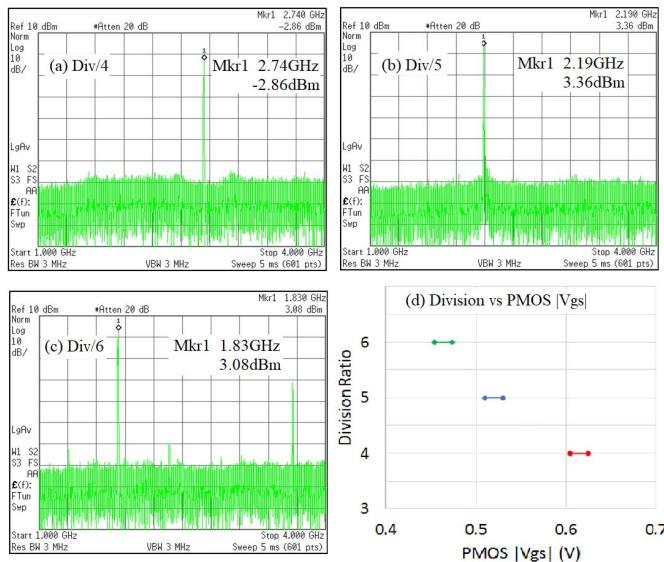

### B. ILFD Measurement Results

In Section IV-A, the ILFD is embedded in the FTL loop to lower the input frequency of the PFD and thus lower power consumption. It may also be used outside the loop in the output path to divide down the clock frequency to provide multiple frequency bands by utilizing its multiple

Fig. 19. Measured spectrum of the mm-wave output in the presence of external disturbances; the large spur at 1 MHz corresponds to the injected disturbance (output frequency was divided by 16 for the measurement).

TABLE III

MEASURED PN AT THE INJECTION-LOCKED DIVIDER OUTPUTS

| Input Frequency (GHz) | Division ratio | Output Frequency (GHz) | Phase noise @1MHz offset (dBc/Hz) |

|-----------------------|----------------|------------------------|-----------------------------------|

| 43.81                 | 4              | 10.95                  | -101.2                            |

|                       | 5              | 8.76                   | -103.3                            |

|                       | 6              | 7.30                   | -104.7                            |

division ratios. To test the programmable division ratio of our implemented ILFD, the divider is configured in an open-loop testing setup in which the mm-wave VCO free-running output clock is directly divided by the ILFD in a separate prototype chip. The ILFD was followed by a CMOS divide-by-4 circuit and a differential CML output buffer for testing purposes. This second mm-wave VCO was measured to operate at 41.2–43.9 GHz. Fig. 20(a)–(c) shows the measured output spectra at the buffered output with division ratios of 4/5/6 when the VCO was tuned to 43.8 GHz. Fig. 20(d) shows the division ratio versus PMOS gate voltage  $|V_{GS}|$ . It was noticed that the range of the bias voltage of the load PMOS was about 20 mV. Table III summarizes the

Fig. 20. Measured ILFD (with additional Div/4 buffer) output spectra with different divide ratios at input frequency 43.8 GHz. (a) Divided-by-4. (b) Divided-by-5. (c) Divided-by-6. (d) Division ratios versus PMOS  $|V_{gs}|$ .

TABLE IV

MEASURED RESULTS AND COMPARISON TO OTHER mm-WAVE DIVIDERS

| Ref                      | Ghiloni [26]<br>JSSC-13 | Mostajeran [27]<br>MTTS-17 | Hara [28]<br>ASSCC-09 | This work        |

|--------------------------|-------------------------|----------------------------|-----------------------|------------------|

| Fin Max                  | 70GHz                   | 61GHz                      | 11.4GHz               | 43.8GHz          |

| Division ratios          | 4                       | 2                          | 2/3/4/6               | 4/5/6            |

| Supply Voltage           | 1.0V                    | 1.6V                       | 1.2V                  | 0.94V            |

| Power                    | 4.8mW                   | 10.4mW                     | 1.3mW                 | 2.4mW            |

| Area [ $\mu\text{m}^2$ ] | 3000                    | 1600                       | -                     | 1368             |

| Technology               | 32nm CMOS               | 0.13um<br>CMOS             | 90nm<br>CMOS          | 45nm SOI<br>CMOS |

measured PN for different division ratios. Table IV compares this ILFD with other published mm-wave frequency dividers. Note that this power is slightly higher than reported in the mm-wave synthesizer power breakdown (Fig. 16), due to the higher operating frequency quoted in Table IV. It achieved the highest input frequency and the lowest power consumption among these programmable frequency dividers.

## V. CONCLUSION

An mm-wave two stage frequency synthesizer has been presented in this article. To reduce the PN of the first-stage PLL, a type-I RSPLL has been implemented. Compared to an SSPLL, the RSPLL can achieve similar in-band PN performance, yet with greatly improved locking robustness without using additional frequency locking loop. Unlike prior RSPLLs, a reshaping reference clock buffer has been proposed to adjust the reference slope. This scheme balances the detectable range and the gain of the sampling PD, leading to optimum PLL PN performance and robust loop dynamics under external disturbances. Using a type-I PLL, the LF size can be greatly reduced, leading to a compact fully integrated mm-wave PLL design. The second-stage ILFM uses an ILVCO to provide a four times higher frequency for mm-wave frequency generation. A low-power FTL-detecting

frequency deviation was proposed in order to calibrate the VCO free-running frequency and improve the locking robustness of the ILVCO with a high  $Q$  tank against process-voltage-temperature (PVT) variations. The FTL was assisted with an mm-wave injection-locked divider capable of multi-modulus integer divisions. The first-stage RSPLL achieved a high FoM of  $-248$  dB at 8.96-GHz output and the overall mm-wave synthesizer achieved an FoM of  $-238.9$  dB at 35.84 GHz.

## ACKNOWLEDGMENT

The authors thank Global Foundries, Santa Clara, CA, USA, for chip fabrication support.

## REFERENCES

- [1] S. Ek *et al.*, “A 28-nm FD-SOI 115-fs jitter PLL-based LO system for 24–30-GHz sliding-IF 5G transceivers,” *IEEE J. Solid-State Circuits*, vol. 53, no. 7, pp. 1988–2000, Jul. 2018.

- [2] W. El-Halwagy, A. Nag, P. Hisayasu, F. Aryanfar, P. Mousavi, and M. Hossain, “A 28-GHz quadrature fractional-N frequency synthesizer for 5G transceivers with less than 100-fs jitter based on cascaded PLL architecture,” *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 2, pp. 396–413, Feb. 2017.

- [3] H. Yoon *et al.*, “A  $-31$  dBc integrated-phase-noise 29 GHz fractional-N frequency synthesizer supporting multiple frequency bands for backward-compatible 5G using a frequency doubler and injection-locked frequency multipliers,” in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2018, pp. 366–368.

- [4] X. Gao, E. A. M. Klumperink, M. Bohsali, and B. Nauta, “A low noise sub-sampling PLL in which divider noise is eliminated and PD/CP noise is not multiplied by  $N^2$ ,” *IEEE J. Solid-State Circuits*, vol. 44, no. 12, pp. 3253–3263, Dec. 2009.

- [5] J. Sharma and H. Krishnaswamy, “A 2.4-GHz reference-sampling phase-locked loop that simultaneously achieves low-noise and low-spur performance,” *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1407–1424, May 2019.

- [6] D. Liao, F. F. Dai, B. Nauta, and E. A. M. Klumperink, “A 2.4-GHz 16-phase sub-sampling fractional-N PLL with robust soft loop switching,” *IEEE J. Solid-State Circuits*, vol. 53, no. 3, pp. 715–727, Mar. 2018.

- [7] A. Li, S. Zheng, J. Yin, X. Luo, and H. C. Luong, “A 21–48 GHz subharmonic injection-locked fractional-N frequency synthesizer for multiband point-to-point backhaul communications,” *IEEE J. Solid-State Circuits*, vol. 49, no. 8, pp. 1785–1799, Aug. 2014.

- [8] D. Shin *et al.*, “A mixed-mode injection frequency-locked loop for self-calibration of injection locking range and phase noise in  $0.13\text{ }\mu\text{m}$  CMOS,” in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2016, pp. 50–51.

- [9] S. Yoo *et al.*, “A PVT-robust  $-39$  dBc 1kHz-to-100 MHz integrated-phase-noise 29 GHz injection-locked frequency multiplier with a 600 W frequency-tracking loop using the averages of phase deviations for mm-band 5G transceivers,” in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 324–325.

- [10] B. Razavi, “A study of injection locking and pulling in oscillators,” *IEEE J. Solid-State Circuits*, vol. 39, no. 9, pp. 1415–1424, Sep. 2004.

- [11] D. Liao, Y. Zhang, Z. Chen, Y. Wang, and F. F. Dai, “An mm-wave synthesizer with low in-band noise and robust locking reference-sampling PLL,” in *Proc. IEEE CICC*, Austin, TX, USA, Apr. 2019, pp. 1–4.

- [12] L. Grimaldi *et al.*, “A 30 GHz digital sub-sampling fractional-N PLL with  $198\text{fs}_{\text{rms}}$  Jitter in 65 nm LP CMOS,” in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2019, pp. 268–270.

- [13] A. T. Narayanan *et al.*, “A fractional-N sub-sampling PLL using a pipelined phase-interpolator with an FoM of  $-250$  dB,” *IEEE J. Solid-State Circuits*, vol. 51, no. 7, pp. 1630–1640, Jul. 2016.

- [14] D. Liao, R. Wang, and F. F. Dai, “A low-noise inductor-less fractional-N sub-sampling PLL with multi-ring oscillator,” in *Proc. IEEE RFIC*, Honolulu, HI, USA, Jun. 2017, pp. 108–111.

- [15] A. Sharkia, S. Mirabbasi, and S. Shekhar, “A type-I sub-sampling PLL with a  $100 \times 100\text{ }\mu\text{m}^2$  footprint and  $-255$ -dB FOM,” *IEEE J. Solid-State Circuits*, vol. 53, no. 12, pp. 3553–3564, Dec. 2018.

- [16] S. S. Nagam and P. R. Kinget, "A 0.008 mm<sup>2</sup> 2.4 GHz type-I sub-sampling ring-oscillator-based phase-locked loop with a  $-239.7$  dB FoM and  $-64$  dBc reference spurs," in *Proc. IEEE CICC*, San Diego, CA, USA, Apr. 2018, pp. 1–4.

- [17] T. Sepke, P. Holloway, C. G. Sodini, and H.-S. Lee, "Noise analysis for comparator-based circuits," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, no. 3, pp. 541–553, Mar. 2009.

- [18] J. W. M. Rogers, C. Plett, and F. F. Dai, *Integrated Circuit Design for High-Speed Frequency Synthesis*. Norwood, MA, USA: Artech House, 2006.

- [19] W. Bae, "Frequency acquisition technique for injection-locked clock generator using asynchronous-sampling frequency detection," *Electron. Lett.*, vol. 53, no. 18, pp. 1240–1242, Aug. 2017.

- [20] A. Mazzanti, P. Uggetti, and F. Svelto, "Analysis and design of injection-locked LC dividers for quadrature generation," *IEEE J. Solid-State Circuits*, vol. 39, no. 9, pp. 1425–1433, Sep. 2004.

- [21] T. Siriburanon *et al.*, "A low-power low-noise mm-wave subsampling PLL using dual-step-mixing ILFD and tail-coupling quadrature injection-locked oscillator for IEEE 802.11ad," *IEEE J. Solid-State Circuits*, vol. 51, no. 5, pp. 1246–1260, May 2016.

- [22] Y. Chen *et al.*, "A 40 GHz PLL with  $-92.5$  dBc/Hz in-band phase noise and 104fs-RMS-jitter," in *Proc. IEEE RFIC*, Jun. 2017, pp. 31–32.

- [23] N. Mahalingam *et al.*, "A 30-GHz power-efficient PLL frequency synthesizer for 60-GHz applications," *IEEE Trans. Microw. Theory Techn.*, vol. 65, no. 11, pp. 4165–4175, Nov. 2017.

- [24] Z. Yang, Y. Chen, S. Yang, P.-I. Mak, and R. P. Martins, "A 25.4-to-29.5 GHz 10.2 mW isolated sub-sampling PLL achieving  $-252.9$  dB jitter-power FoM and  $-63$  dBc reference spur," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2019, pp. 270–272.

- [25] A. Hussein *et al.*, "A 50-to-66 GHz 65 nm CMOS all-digital fractional-N PLL with 220fs<sub>rms</sub> jitter," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2017, pp. 326–327.

- [26] A. Ghilioni, A. Mazzanti, and F. Svelto, "Analysis and design of mm-Wave frequency dividers based on dynamic latches with load modulation," *IEEE J. Solid-State Circuits*, vol. 48, no. 8, pp. 1842–1850, Aug. 2013.

- [27] A. Mostajeran, M. Emadi, A. Cathelin, and E. Afshari, "A compact ultra-wide-band frequency divider with a locking range of 12–61 GHz with 0 dBm of input power," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2017, pp. 4–9.

- [28] S. Hara, K. Okada, and A. Matsuzawa, "A 9.3 MHz to 5.7 GHz tunable LC-based VCO using a divide-by-N injection-locked frequency divider," in *Proc. IEEE Asian Solid-State Circuits Conf.*, Nov. 2009, pp. 81–84.

**Dongyi Liao** received the B.S. degree in electrical engineering from the University of Electrical Science and Technology of China, Chengdu, China, in 2012, and the M.S. and Ph.D. degrees in electrical engineering from Auburn University, Auburn, AL, USA, in 2013 and 2018, respectively.

He is currently with Qualcomm Technologies Inc., San Diego, CA, USA. His current research interest is mainly focused on RF/analog/mixed-signal integrated circuit design including RF transceiver front end, phase-locked loops, and analog-to-digital converter.

**Yucai Zhang** (M'05) received the B.Sc. and M.Sc. degrees from the University of Electrical Science and Technology of China, Chengdu, China, in 1993 and 1996, respectively, and the M.A.Sc. degree from the University of Toronto, Toronto, ON, Canada, in 2001. He is currently pursuing the Ph.D. degree in electrical and computer engineering with Auburn University, Auburn, AL, USA.

He has worked for multiple companies, including Maxim Integrated Products, Hillsboro, OR, USA, and Intel Cooperation, Hillsboro, in radio frequency integrated circuits and high-speed SerDes. His current research interest is 5G and millimeter (mm)-wave wireless communication circuits.

**Fa Foster Dai** (M'92–SM'00–F'09) received the Ph.D. degree in electrical engineering from Pennsylvania State University, State College, PA, USA, in 1998.

From 1997 to 2000, he was a Technical Staff Member of very large scale integration (VLSI) with Hughes Network Systems, Germantown, MD, USA. From 2000 to 2001, he was a Technical Manager/a Principal Engineer of radio frequency integrated circuits (RFIC) with YAFO Networks, Hanover, MD. From 2001 to 2002, he was a Senior RFIC Engineer with Cognio Inc., Gaithersburg, MD. In August 2002, he joined Auburn University, Auburn, AL, USA, where he is currently a Reynolds Family Endowed Professor of electrical and computer engineering. His research interests include analog and mixed-signal circuit designs, RFIC and monolithic microwave integrated circuit (MMIC) designs, and high-performance frequency synthesis. He has coauthored six books and book chapters including *Integrated Circuit Design for High-Speed Frequency Synthesis* (Artech House Publishers, February 2006) and *Low-Noise Low-Power Design for Phase-Locked Loops-Multi-Phase High-Performance Oscillators* (Springer International Publishing AG, November 2014).

Dr. Dai served as a Guest Editor for the IEEE JOURNAL ON SOLID STATE CIRCUITS in 2012 and 2013 and the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS in 2001, 2009, and 2010. He served on the technical program committees (TPC) for the IEEE Symposium on VLSI Circuits from 2005 to 2008. He currently serves on the Steering Committee of the IEEE Custom Integrated Circuits Conference (CICC) and TPC of the IEEE RFIC Symposium. He was a TPC Chair of the 2016 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM) and the General Chair of the 2017 BCTM. He currently serves as a TPC Chair for the 2019 IEEE CICC and the Conference Chair of the 2020 IEEE CICC.

Inc., Auburn.

**Zhenqi Chen** (S'02–M'09–SM'17) received the B.S. and M.S. degrees in electronic engineering from Tsinghua University, Beijing, China, in 2000 and 2003, respectively, and the Ph.D. degree in electrical and computer engineering from Auburn University, Auburn, AL, USA, in 2016.

From 2009 to 2018, he was with Qualcomm, Boxborough, MA, USA, where he was a Staff Engineer, designing advanced RFIC and modules for 4G and 5G smartphones. Since 2018, he has been a Technical Consultant of Digital Analog Integration

**Yanjie Wang** (S'97–M'08–SM'16) received the M.A.Sc. degree from Carleton University, Ottawa, ON, Canada, in 2002, and the Ph.D. degree from the University of Alberta, Edmonton, AB, Canada, in 2009.

He was an ASIC Design Engineer with NorTEL Networks, Ottawa, and AMCC, Montreal, QC, Canada, from 1999 to 2003. In 2007, he was a Ph.D. Graduate Student Researcher with Berkeley Wireless Research Center, University of California at Berkeley, Berkeley, CA, USA. Since 2008, he has been a Senior Staff Research Scientist with Intel Corporation, Hillsboro, OR, USA, focusing on the next-generation 5G millimeter (mm)-wave and energy-efficient broadband RF transceiver circuits and systems. Since 2018, he has been a Technical Consultant of Digital Analog Integration Inc., Auburn, AL, USA.

Dr. Wang was a recipient of the Best Invited Paper Award of the IEEE Custom Integrated Circuits Conference (CICC) 2015 and the Best Paper Award (2nd place) of the IEEE CICC2015. He has been serving as a Technical Program Committee Member of the IEEE Radio Frequency Integrated Circuits Symposium and an Organizational Committee Member of the IEEE CICC since 2012.