# A Model for R(t) Elements and R(t)-Based Spike Timing-Dependent Plasticity with Basic Circuit Examples

Robert C. Ivans, *Student Member, IEEE*, Sumedha G. Dahl, *Student Member, IEEE*, and Kurtis D. Cantley, *Member, IEEE*

Abstract-Spike timing-dependent plasticity (STDP) is a fundamental synaptic learning rule observed in biology that leads to numerous behavioral and cognitive outcomes. Emulating STDP in electronic spiking neural networks with high-density memristive synapses is therefore of significant interest. While one popular method involves pulse-shaping the spiking neuron output voltages, an alternative approach is outlined in this paper. The proposed STDP implementation uses time-varying dynamic resistance (R(t)) elements to achieve local synaptic learning from spike-pair STDP, spike triplet STDP, and firing rates. The R(t) elements are connected to each neuron circuit thereby maintaining synaptic density and leverage voltage-division as a means of altering synaptic weight (memristor voltage). Example R(t) elements with their corresponding behaviors are demonstrated through simulation. A three-input-two-output network using single-memristor synaptic connections and R(t) elements is also simulated. Network-level effects such as non-specific synaptic plasticity are discussed. Finally, spatiotemporal pattern recognition (STPR) using R(t) elements is demonstrated in simulation.

*Index Terms*—Memristor, spike-timing-dependent plasticity, spiking neural network, synapse.

#### I. INTRODUCTION

Human brains are made up of billions of neurons which generate voltage spikes called action potentials in response to stimulus [1]. Those billions of neurons are interconnected through trillions of synapses which effectively serve to scale the magnitude of action potentials that pass through them [2]. The amount of scaling that a synapse performs is referred to as its synaptic efficacy, strength, or weight. The weight of a synapse is not static, and changes over time based on learning rules that depend on pre- and post-synaptic neuron activity. Timing differences between two action potentials occurring in the neurons that the synapse connects is one mechanism that can alter the weight [3]–[5]. This is known as Spike-Timing-Dependent Plasticity (STDP).

Many forms of STDP have been observed in different brain regions across various species. It is known to be responsible for abilities including rapid response to threats and sound source localization [4], [6]–[11]. However, it is also known that biological synapses implement much more complex and diverse learning rules than pair-based STDP [12]. In reality, synapses integrate multiple action potentials asymmetrically and can alter their weight over longer timescales containing multiple pre- and post-synaptic spikes [12]–[17]. Broader consequences of this observation are not well understood, but may enable many advanced cognitive functions.

Electronic spiking neural networks comprised of STDP synapses have been shown to perform complicated learning tasks such as pattern recognition, classification, and feature extraction [18]–[24]. Due to these demonstrated abilities, many researchers have implemented STDP synapses using CMOS circuits [25]–[31]. The circuits generally contain at least a dozen devices and have relatively large footprints [28], [30]–[32]. Both these traits are highly undesirable when the objective is to maximize synaptic density and the overall number of synapses. In other words, although local Hebbian learning rules such as STDP are essential for constructing networks with an extremely large number of elements, the synapse implementations must also be compact.

Memristors are an ideal candidate for electronic synapses because they have only two terminals and can change their resistance based on previously applied bias. They can also be non-volatile with very small cross-sectional area, and densely fabricated in crossbar array structures [33]–[42]. Using single memristors as synapses requires that the neurons somehow control synaptic weight change. A dominant approach for obtaining STDP with memristive synapses is to engineer the shape of the neuron output voltage pulses to achieve the desired weight update function [21], [37], [41], [43]–[50]. In the pulse-shaping method, signals are directed toward both the axonic and dendritic synapses whenever a neuron fires. The potential across the memristor itself is given by the difference between the post- and pre-synaptic voltages. The main drawback of this approach is that it allows only nearestneighbor pairs of action potentials to contribute to synaptic weight changes, and has no dependence on firing rate [51]— [53]. This paper presents an approach that is similar and complementary to pulse shaping and is compatible with

The authors are with the Department of Electrical and Computer Engineering, Boise State University, Boise ID 83725 (e-mail: robertivans@boisestate.edu and kurtiscantley@boisestate.edu).

This paper was submitted for review August 3<sup>rd</sup>, 2018. The work was supported in part by the U.S. Air Force Office of Scientific Research under grant FA-14-1-0188, Defense Threat Reduction Agency grant HDTRA-17-1-0036, and the National Science Foundation award 1751230.

single-memristor synapses contained in crossbar arrays. The approach enables the realization of traditional pair-based STDP as well as rules that depend on multiple spikes and long-term firing rates. The key to facilitating these effects is the addition of dynamic resistance, or R(t), elements to the input and output of each hidden layer neuron circuit. In this work, we define R(t) elements as circuits or devices which possess time-varying resistance. This technique is similar to pulse shaping in that a time-varying quantity is driving STDP. However, the distinguishing characteristic of R(t)-based STDP is that the path resistance between neurons changes as a function of the pre- and post-synaptic neuron outputs. Table I compares and contrasts the R(t) and shaped pulse methods of facilitating STDP.

A simple digital pulse is used in the examples presented in this work to activate the R(t) elements which creates the timevarying resistance. This creates a network of time-dynamic voltage dividers, and maximizes the simplicity of the synapses while only slightly increasing the complexity of the neurons. Simple digital pulses are used for mathematical convenience; however, shaped pulses can also be used with R(t) elements for even more complicated learning rules, but this is beyond the scope of this introductory work.

The remainder of this paper is organized as follows: Section II describes perfect STDP using R(t) elements and single memristor synapses and explains the process involved in component value selection. Section III presents examples and simulations of R(t) implementations that result in pair-based and triplet STDP behavior. Section IV contains simulations demonstrating STDP in networks using R(t) elements and single-memristor synapses, and discusses other characteristics of the network. Conclusions are presented in Section V.

#### II. STDP WITH R(T) ELEMENTS

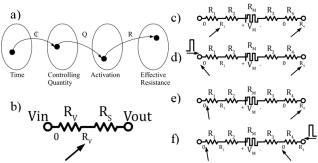

An R(t) element is a circuit or device which possess a time-varying resistance. To design an R(t) element, one must design a circuit or device such that a controlling quantity varies in time to produce the desired R(t) response. One way to do this is to design a circuit or device which implements an activation function, Q, to bridge the gap between R(t) and the controlling quantity function, C. The relationship between the activation function, the time-varying controlling quantity, and the resulting effective resistance is depicted in Fig. 1a. To facilitate

TABLE I

COMPARING AND CONTRASTING THE R(T) AND SHAPED PULSE METHODS OF

| FACILITATING STDP                                          |                  |               |

|------------------------------------------------------------|------------------|---------------|

|                                                            | R(t)             | Shaped Pulses |

| Frequency influenced learning rules                        | Yes              | No            |

| Sensitive to component values                              | Yes <sup>a</sup> | No            |

| Only needs one potential                                   | Yes              | No            |

| Sneak paths                                                | $Yes^b$          | $Yes^b$       |

| Frequency influenced<br>nonspecific synaptic<br>plasticity | Yes              | No            |

"This depends on the desired behavior. The equations presented in this work represent a rigid case where synaptic weight change is guaranteed not to occur outside of the influence of related spikes. However, if merely facilitating STDP is desired, then component value selection can be relaxed. <sup>b</sup>If the network doesn't use neurons which control the potential at their inputs, then the network will have sneak paths.

Fig. 1. An R(t) Element model and the four stages of R(t)-based STDP. a) Illustration showing that R(t) is a composition of three functions. b) An R(t) element model represented as a static resistance,  $R_S$ , and a variable resistance,  $R_V$ , capable of sweeping between 0 and  $R_V$  in time. c) An STDP circuit, consisting of two R(t) elements on either side of a memristor, is in its initial state with pre- and post-synaptic R(t) elements at their maximum resistances. d) A digital pre-synaptic pulse arrives, driving its associated R(t) element to its minimum value. e) Some time passes, over which the resistance of the pre-synaptic R(t) element rises. f) A post-synaptic pulse arrives, driving the post-synaptic R(t) element to its minimum value, and placing a potential across the memristor,  $V_M$ , greater than its negative threshold  $V_{TH}$ , causing memristance to decrease.

excitatory STDP behavior, the activation functions should be implemented such that the R(t) element's resistance decreases sharply when exposed to stimulus and increases slowly once the stimulus is removed. In this work we use the term activated to describe a condition where the controlling quantity abruptly and temporarily increases resulting in a temporary state of reduced resistance for the R(t) element. R(t) elements have been modeled using

$$R(t) = R_V Q(\mathfrak{C}(t)) + R_S, \tag{1}$$

where  $R_V$  is the variable portion of the R(t) element,  $R_S$ , is the static portion of the R(t) element which represents its minimum series resistance, Q is an activation function which converts a controlling quantity into a real number in the range [0,1], and  $\mathbb{C}$  is the controlling quantity function which represents a controlling quantity, such as potential or charge, at a particular time

From the model one can see that the R(t) element has a minimum resistance of  $R_S$  and a maximum resistance of  $R_S + R_V$ . Using two resistors instead of a single resistor is a mathematical convenience to describe the R(t) element's resistance with a single activation factor between zero and one. Fig. 1b depicts a two-resistor model of an R(t) element. The angle of the arrow going from left to right in the figure is a graphical approximation of the effective resistance of  $R_V$  in the range from zero to  $R_V$  at a particular moment in time.

#### A. Synaptic Weight Change

Two R(t) elements combined with a memristor form a circuit which can implement STDP through voltage division. In very general terms, when only one R(t) element is activated, neural spiking is insufficient to cause the voltage across the memristor,  $V_M$ , to exceed the memristor's threshold,  $V_{TH}$ . However, when both R(t) elements are sufficiently activated, the resistance of the memristor, relative to the rest of the branch, is large enough to cause neural spike voltage to exceed its threshold voltage. More specifically, an increase in synaptic strength through an STDP circuit using digital spiking neurons and R(t) elements with single-memristor synapses can be explained in four stages, as depicted graphically in Fig. 1 c-f. In the first stage, it is

assumed that no spikes have occurred for a long enough time period that both pre- and post-synaptic R(t) elements are in their most resistive states. It is also assumed that the value of the memristor is somewhere between its most resistive  $(R_{OFF})$  and least resistive  $(R_{ON})$  states. The second stage begins when a presynaptic spike occurs. The resistance of the pre-synaptic R(t) element is suddenly reduced, and the voltage across the memristor is less than the memristor positive threshold voltage,  $V_{TH}^+$ , meaning that its value will remain unchanged. In the third stage the pre-synaptic R(t) element's resistance has increased with the passage of time, but is still not at its maximum value. The fourth stage begins with the arrival of a post-synaptic spike. The reduced resistances of the R(t) elements results in a negative voltage, greater in magnitude than the absolute value of the negative memristor threshold voltage,  $|V_{TH}^-|$ , across the memristor. This causes its memristance to decrease. As the memristance is decreased, the total path resistance is reduced. This results in a higher current for a given potential. So, more charge is transferred to the post-synaptic neuron through the synapse for a given spike—the synaptic connection has strengthened. A decrease in synaptic resistance due to a postpre spike pair is achieved similarly. One final thing to note is that if the memristors used in the simulation are additive in nature, meaning that a change in their memristance is not dependent on their instantaneous memristance value, R(t) element-based STDP causes non-additive behavior to manifest due to the state of the memristor affecting the voltage that it drops in the resistive voltage divider.

#### B. Component Value Selection for Perfect STDP

In this work we define perfect STDP as a synaptic connection where synaptic change is guaranteed not to occur outside of related spikes. The rest of this section describes how to choose component values that will result in perfect STDP. Before choosing to design STDP circuits which implement perfect STDP, circuit designers should bear in mind that perfect STDP has very strict requirements, results in very small synaptic changes, and as will be demonstrated in Section IV, is not necessary to facilitate spatiotemporal pattern recognition (STPR) with R(t) elements. This section is included to demonstrate that perfect STDP is mathematically possible rather than to be a design guide that one should rigidly follow.

To design a perfect STDP circuit with R(t) elements and a memristor, one must determine the values of  $R_S$  and  $R_V$  for each R(t) element, decide on an activation function Q, and implement the design. Instead of defining a specific implementation of Q, we will use particular values of Q, denoted as X and Y, to determine values of R which will enable STDP to occur, as implementing a particular activation function is beyond the scope of this work. Our strategy is to focus on selecting particular values of  $R_V$  and  $R_S$  which will facilitate STDP for all possible values that a particular memristor could have. The shape of a particular STDP curve is due to the composition of  $R \circ Q \circ \mathcal{C} = R(Q(\mathcal{C}(t)))$ , and so to attain a specific desired STDP curve one must carefully design their circuits; however, the point of this work is not to design any particular STDP curve, but rather to show how STDP is possible in the first place and to provide a model which, when properly

implemented, guarantees perfect STDP behavior.

With this in mind, to facilitate STDP the memristor voltage,  $V_M$ , must be considered with respect to its threshold voltage for two cases: where change is desired  $(|V_M| \ge V_{TH})$  and where change is undesired ( $|V_M| < V_{TH}$ ). We assert that the activation of an R(t) element occurs when a bias is applied to its input terminal. In other words, when a voltage spike is applied to Terminal 1 (Terminal 2) in Fig. 1,  $R_1(R_4)$  is activated. Its resistance suddenly decreases toward  $R_S$  and then slowly rises over time toward  $R_V + R_S$ .

#### 1) Choosing the $R_V$ values: $R_I$ and $R_4$

Resistances  $R_1$  and  $R_4$  are the variable portions of the R(t)elements. They control whether, or not, and by what amount the memristor will be changed in response to spiking stimulus. Consider the STDP circuit model depicted in Fig. 1b. If a potential of  $V_{PRE}$  were applied to Terminal 1, and ground were applied to Terminal 2, then the memristor voltage would be

$$V_{M} = V_{PRE} \frac{R_{M}}{XR_{1} + R_{2} + R_{M} + R_{3} + YR_{4}}$$

where X and Y are real values between zero and one which

represent how resistive, at the moment when  $V_{PRE}$  is applied,  $R_1$  and  $R_4$  are, respectively. Assume that the R(t) element connected to Terminal 1 is fully activated, and therefore minimally resistive (X=0). Depending on the type of R(t)element it may not be true that a single neural spike would fully activate it. However, this is a safe assumption to make because, for the purpose of determining component values, we are assuming some activation of  $R_4$  and applying a DC bias, and not neural spikes, to Terminal 1. For the case when change is desired, the component values must result in a situation where

$$V_M \ge V_{TH}$$

. Substituting into (7) and rearranging gives us

$$R_M \left( \frac{V_{PRE}}{V_{TH}^+} - 1 \right) \ge R_2 + R_3 + YR_4. \tag{3}$$

This inequality describes all of the factors which determine whether, or not, memristance will change: the current value of  $R_M$ , the values chosen for  $V_{PRE}$ ,  $R_2$ ,  $R_3$ , and  $R_4$ , and the resistance of  $R_4$ , at the time  $V_{PRE}$  is applied.

A similar inequality can be derived for the case when change is undesired ( $V_M < V_{TH}$ ):

$$R_M \left( \frac{V_{PRE}}{V_{TH}^*} - 1 \right) < R_2 + R_3 + YR_4.$$

(4)

Let A denote the resistance of  $R_4$ , above which  $V_M < V_{TH}$ , regardless of  $R_M$ , and let B denote the resistance of  $R_4$ , below which  $V_M > V_{TH}$ , regardless of  $R_M$ . Choosing A and B is accomplished by examining the fringe cases where change is undesired with the memristor at its highest resistance value  $(R_M = R_{OFF})$  and where change is desired with the memristor at its lowest resistance value  $(R_M = R_{ON})$ , and then selecting from the allowed values. The fringe cases can be expressed as

From the allowed values. The fringe cases can be expressed as

$$V_{TH}^{+} \leq V_{PRE} \frac{R_{ON}}{R_2 + R_{ON} + R_3 + BR_4} \text{ and}$$

$$V_{TH}^{+} > V_{PRE} \frac{R_{OFF}}{R_2 + R_{OFF} + R_3 + AR_4}$$

which can be combined and rearranged to yield

$$(R_2 + R_2)(R_{OFF} - R_{OFF})$$

(7)

$$(R_2 + R_3)(R_{OFF} - R_{ON})$$

(7)

$< R_4[R_{ON}A - R_{OFF}B].$

Since  $R_2$ ,  $R_3$ , and  $R_4$  are greater than zero, and  $R_{OFF} > R_{ON}$ ,

$$R_{ON}A > R_{OFF}B \tag{8}$$

which can be rearranged into

$$\frac{A}{B} > \frac{R_{OFF}}{R_{ON}}. (9)$$

This inequality is a good rule of thumb for choosing A and B. but insufficient to ensure that the circuit wil produce perfect STDP. Thus, start by choosing A and B which satisfy (9). Next,  $R_4$  is chosen. Re-examining the fringe cases, they can be expressed as

$$R_{OFF} \left( \frac{V_{PRE}}{V_{TH}^+} - 1 \right) < R_2 + R_3 + AR_4 \text{ and}$$

(10)

$$R_{ON}\left(\frac{V_{PRE}}{V_{TH}^{+}} - 1\right) \ge R_2 + R_3 + BR_4.$$

(11)

It is clear that if

$$R_4 = \frac{R_{OFF} \left( \frac{V_{PRE}}{V_{TH}^+} - 1 \right)}{4} \dagger \tag{12}$$

and the value of B is updated such that

$$B \le \frac{R_{ON} \left( \frac{V_{PRE}}{V_{TH}^{+}} - 1 \right) - (R_2 + R_3)}{R_4}$$

(13)

then (9), (10), and (11) can all be satisfied. The next step depends on whether symmetrical STDP is desired. If symmetrical STDP is desired, then let  $R_2=R_3$ ,  $R_1=R_4$ , and choose  $R_2$ . If asymmetrical STDP is desired, then connect ground to Terminal 1 and  $V_{POST}$  to Terminal 2. Assume that the R(t) element connected to Terminal 2 is fully activated, and

therefore minimally resistive

$$(Y=0)$$

. Thus (2) becomes

$$V_{M} = V_{POST} \frac{R_{M}}{XR_{1} + R_{2} + R_{M} + R_{3}}.$$

Let  $C$  denote the resistance of  $R_{1}$ , above which  $V_{M} < V_{TH}$ ,

regardless of  $R_M$ , and let D denote the resistance of  $R_1$ , below which  $V_M > V_{TH}$ , regardless of  $R_M$ .

Choosing C and D is accomplished by examining the fringe cases where change is undesired with the memristor at its highest resistance value  $(R_M = R_{OFF})$  and where change is desired with the memristor at its lowest resistance value ( $R_M$  =  $R_{ON}$ ), and then selecting from the allowed values. The fringe

$$V^{-} < V \qquad R_{ON} \tag{15}$$

$$V_{TH}^{-} \le V_{POST} \frac{R_{ON}}{DR_1 + R_2 + R_{ON} + R_3}$$

$$V_{--}^{-} > V_{--} = \frac{R_{OFF}}{R_{OFF}}$$

(15)

$V_{TH}^{-} > V_{POST} \frac{R_{OFF}}{CR_1 + R_2 + R_{OFF} + R_3}$  which can be combined and rearranged to yield

$$(R_2 + R_3)(R_{OFF} - R_{ON})$$

(17)

$< R_1[R_{ON}C - R_{OFF}D].$

Since  $R_1$ ,  $R_2$ , and  $R_3$  are greater than zero, and  $R_{OFF} > R_{ON}$ , then

$$R_{ON}C > R_{OFF}D, \tag{18}$$

which can be rearranged into

$$\frac{C}{D} > \frac{R_{OFF}}{R_{ON}}. (19)$$

This inequality is a good rule of thumb for choosing C and D, but insufficient to ensure that the circuit will produce perfect STDP. Thus, start by choosing C and D which satisfy (19).

Next,  $R_1$  is chosen. Re-examining the fringe cases, they can be expressed as

$$R_{OFF} \left( \frac{V_{POST}}{V_{TH}} - 1 \right) < CR_1 + R_2 + R_3 \text{ and}$$

(20)

$$R_{ON}\left(\frac{V_{POST}}{V_{TH}} - 1\right) \ge DR_1 + R_2 + R_3.$$

(21)

It is clear that if

$$R_1 = \frac{R_{OFF} \left( \frac{V_{POST}}{V_{TH}^-} - 1 \right)}{C} \ddagger \tag{22}$$

$$D \le \frac{R_{ON} \left( \frac{V_{POST}}{V_{TH}^{-}} - 1 \right) - (R_2 + R_3)}{R_1}$$

(23)

and  $R_3$ .

## 2) Choosing the $R_S$ values: $R_2$ and $R_3$

The combination of  $R_2$  and  $R_3$  limit the maximum theoretical voltage that can be applied to the memristor and therefore limit the magnitude of change that the memristor can undergo due to the application of a spike. The individual values of  $R_2$  and  $R_3$ will not affect the shape of the STDP curve, only their combined value. To ensure that the memristor will change as desired, choose  $R_2$  and  $R_3$  such that the quantity  $R_2 + R_3$  obeys all of the following inequalities:

$$R_2 + R_3 \le \frac{V_{PRE}}{V_{TH}^+} R_{ON} - R_{ON} - BR_4 \tag{24}$$

$$R_2 + R_3 > \frac{V_{PRE}}{V_{TH}^+} R_{OFF} - R_{OFF} - AR_4 \tag{25}$$

$$R_{2} + R_{3} > \frac{V_{PRE}}{V_{TH}^{+}} R_{OFF} - R_{OFF} - AR_{4}$$

$$R_{2} + R_{3} \leq \frac{V_{POST}}{V_{TH}^{-}} R_{ON} - R_{ON} - DR_{1}$$

(25)

$$R_2 + R_3 > \frac{V_{POST}}{V_{TH}^-} R_{OFF} - R_{OFF} - CR_1$$

(27)

## III. R(T) ELEMENT IMPLEMENTATION EXAMPLES

Previous work has demonstrated that synapses composed of single memristors driven by short-term memory transistors are capable of STDP. Specifically, thin-film transistors (TFTs) with layers of nanoparticles in the gate dielectric were used to drive memristive synapses. Close correspondence to biological measurements for spike pairs, triplets, and overall frequency measurements [54]-[56]. Simulations also indicated these networks are capable of performing STPR [24]. The nanoparticle TFTs effectively perform the function of an R(t) element, as will be discussed in Section III D.

$$^{\dagger}$$

Any  $R_4$  such that  $R_4 > \frac{R_{OFF}\left(\frac{V_{PBE}-1}{V_{TH}^+}\right)}{A} - (R_2 + R_3)$  will satisfy (10)

<sup>‡</sup> Any

$$R_1$$

such that  $R_1 > \frac{R_{OFF}\left(\frac{V_{POST}}{V_{TH}^2} - 1\right)}{C} - (R_2 + R_3)$  will satisfy (20).

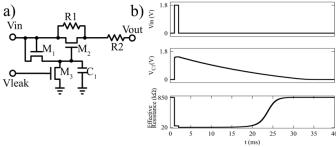

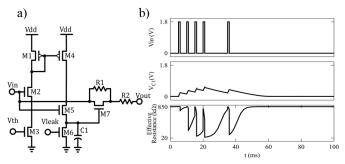

Fig. 2. a) A schematic of a simple R(t) element circuit. b) The simple R(t) element circuit's response to a 1 ms long 1.8 V digital (square) pulse with Vleak = 50 mv, R1=842 k $\Omega$ , R2=19 k $\Omega$ , C<sub>1</sub> =1 pF, and W/L=10/2 for all MOSFETs. Effective resistance is calculated as the voltage difference between Vin and Vout over the current through R2. A small measuring bias voltage is applied to Vin, but not C1, in the absence of spiking stimulus.

This section provides two additional examples of R(t) elements in the form of CMOS circuits (as opposed to devices). These basic circuits, are designed using the R(t) element model described in Section II, and are meant to emphasize the characteristics of simple and compound R(t) elements rather than perfectly encapsulate simple and compound R(t) element functionality. We demonstrate how to create STDP circuits with these circuits, and provide simulation results conducted using the industry-standard circuit design software Cadence Virtuoso, TSMC 0.18 micron technology MOSFET models, and the NCSU Cadence design kit [57].

The first example is a simple R(t) element circuit, defined to be an R(t) element that achieves its maximum resistance change from a single digital pulse. The second example is a compound R(t) element circuit, defined as an R(t) element that requires multiple digital pulses to achieve their maximum resistance change. Both examples were used in conjunction with an ideal memristor with the following characteristics:  $\alpha$ =0.001,  $R_{ON}$ =10 k $\Omega$ ,  $V_{TH}^+$ =200 mV,  $V_{TH}^-$ =-200 mV,  $\Delta M$  described by:

$$f(M, V_M, V_{TH}^+, V_{TH}^-)$$

$$= \begin{cases} \alpha \exp(V_M - V_{TH}^+) - 1, V_M > V_{TH}^+ \text{ and } M < R_{OFF} \\ -\alpha \exp(|V_M - V_{TH}^-|) - 1, V_M < V_{TH}^- \text{ and } M > R_{ON} \\ 0, \text{ otherwise,} \end{cases}$$

(28)

and memristance, M, described by

$$M = R_{ON} \frac{w}{D} + R_{OFF} \left( 1 - \frac{w}{D} \right), \tag{29}$$

where w/D represents physical characteristics of the memristor which for the purposes of a memristor-based synapse can be thought of as the weight with values between zero and one [36], [58]–[60].

## A. Simple R(t) Element Circuits

The first implementation of an R(t) element circuit that will be demonstrated is a simple R(t) element circuit. We define a

Fig. 3. A schematic of a simple R(t) element-based STDP circuit. It is important to note that the R(t) elements are not part of the synapse, many memristive synapses can be fed by a neuron through a single R(t) element, rather they are an accessory to be added to a neuron. In this figure, the neurons have been substituted with piece-wise linear voltage sources to create simple digital pulses.

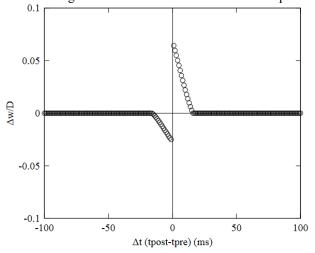

Fig. 4. a) The pair-based STDP plot created by an STDP circuit composed of two simple R(t) element circuits and a memristor. The memristor is initialized to 55 k $\Omega$  (w/D=0.5). Applied pre- and post-synaptic pulses are 1.8 V digital pulses with pulse widths of 1 ms and Vleak=40 mV. b) A simulation demonstrating the multiplicative behavior of the additive memristor due to the voltage dividing nature of the R(t) element-based STDP circuit. The same pre- and post-synaptic potentials are applied to two identical simple STDP circuits (Vleak=40 mV) except for the initial condition of the two memristors (0.100 in one and 0.500 in the other). The memristor with the lower initial w/D, and thus a higher initial memristance, experiences a larger  $\Delta w/D$  because it drops a larger fraction of the applied potential.

simple R(t) element as an R(t) element that achieves its maximum resistive change from a single digital pulse. The values of  $R_1$  and  $R_2$  were chosen in accordance with the guidance described in the previous section. A and B were chosen to be 0.95 and 0.05 respectively, which resulted in  $R_1$  and  $R_2 + R_3$  being 842 k $\Omega$  and 38 k $\Omega$  respectively. Since symmetrical STDP was desired, and the memristor used had symmetrical characteristics,  $R_4$ = $R_1$ . Fig. 2 depicts a schematic of a simple R(t) element circuit and a plot of the response of the simple R(t) element to a 1.8 V digital pulse applied to Vin when w/D=0.5.

When a digital pulse arrives at Vin, capacitor  $C_1$ . Is charged through diode connected MOSFET M1. For the duration of the pulse,  $V_{GM2}$  rises towards Vin- $V_{DS}$ , increasing the conduction of M2 and lowering the overall effective resistance of the R(t) element. When the simple digital pulse ends, charge leaks to ground out of  $C_1$  through M3, at a rate determined by Vleak. This causes  $V_{GM2}$  to lower over time and the effective resistance of the R(t) element to rise over time. This particular implementation of an R(t) element circuit used in an STDP

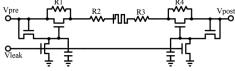

Fig. 5. a) A schematic of a compound R(t) element circuit. b) The compound R(t) element circuit's response to simple 1 ms duration 5 V digital pulses with Vleak= 40mV, Vth=68 mV, R1=842 k $\Omega$ , R2=19 k $\Omega$ , C1=1 pF, and W/L=10/2 and 20/2 for all NMOS and PMOS respectively. Effective resistance is calculated as the voltage difference between Vin and Vout over the current through R2 with a small measuring bias applied to Vin, but not C1, in the absence of spiking stimulus.

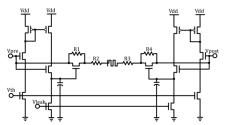

Fig. 6. A schematic of the compound R(t) element-based STDP circuit. It is important to note that the R(t) elements are not part of the synapse, many memristive synapses can be fed by a neuron through a single R(t) element, rather they are an accessory to be added to a neuron. In this figure, the neurons have been substituted with piece-wise linear voltage sources to create simple digital pulses.

circuit as shown in Fig. 3, produces the STDP curve of Fig. 4a. Although the memristor described in (28) is additive, the memristor will change in a non-additive fashion due to the voltage dividing action of the STDP circuit. This property is portrayed in Fig. 4b. It is important to note that the R(t) elements in this single STDP circuit do not belong to the synapse memristor, but instead to the input and output neurons connected through it. In a network configuration, many single-memristor synapses may be connected to a particular neuron's R(t) element. This is explained in more detail in Section IV.

### B. Compound R(t) Element Circuits

The second implementation of an R(t) element circuit that will be demonstrated is a compound R(t) element circuit. We define a compound R(t) element as an R(t) element that requires multiple digital pulses to achieve its maximum resistance change. The values of  $R_1$  and  $R_2$  from the previous example circuit are used. Fig. 5 shows a schematic of a compound R(t)

Fig. 7. Three separate spike trains are applied to the same compound R(t) element-based STDP circuit with the same settings (Vleak=40 mV, Vth=125 mV, memristor initialized to w/D=0.500). The pre- and post-synaptic R(t) element's effective resistances are depicted with thin solid and dotted lines respectively. The memristor's w/D is depicted with a thick line. The times of pre- and post-synaptic spikes are represented with  $\circ$  and + respectively. Notice how the magnitude of change varies as the inter-spike-interval and time between triplets varies. a) Three spike triplets are applied to the compound STDP circuit with an inter-spike-interval of 6 ms and 15 ms between triplets. b) Three spike triplets are applied to the compound STDP circuit with an inter-spike-interval of 3 ms and 15 ms between triplets. c) Three spike triplets are applied to the compound STDP circuit with an inter-spike-interval of 6 ms and 10 ms between triplets. Applied pre- and post-synaptic pulses are 1.8 V digital pulses with pulse widths of 1 ms.

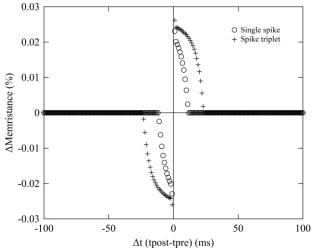

Fig. 8. The STDP plot created by an STDP circuit composed of two compound R(t) element circuits and a memristor under the influence of two different kinds of stimulus—pairs of single spikes and spike triplets. The pairs of single spikes are typical pre-post pairs, whereas the spike triplets are pre-pre-post and post-post-pre triplets where the first two spikes are separated by 5 ms. The memristor is initialized to 55 k $\Omega$  (w/D=0.5). Applied pre- and post-synaptic pulses are 1.8 V digital pulses with widths of 1 ms. Vleak=40 mV and Vth=125 mV.

element circuit and a plot of the response of the compound R(t) element to five 1.8 V digital pulses applied to Vin.

When a simple digital pulse is applied at Vin to the compound R(t) element, current flows through the current-mirror-like arrangement composed of M1, M2, and M3. This induces another current (Vth $\neq$ Vleak) in the structure composed of M4, M5, and M6. The induced current is divided between flowing to ground through M6 and charging C1. The charge in C1 raises  $V_{GM7}$  which increases the conductivity of M7 and lowers the effective resistance of the R(t) element. When the simple digital pulse at Vin ends the charge stored in C1 leaks to ground through M6 at a rate determined by Vleak. This particular implementation of a compound R(t) element used in an STDP circuit is shown in Fig. 6.

Since compound R(t) elements, by definition, cannot achieve their least resistive state by a single spike, the STDP curve changes for different combinations of spikes. The

Fig. 9. The STDP plot created by using two simple R(t) elements and a memristor based on the Yakopcic model.

memristance changes resulting from pre-post pairs and pre-pre-post triplets produce different STDP curves because the effective resistance of compound R(t) elements is dependent on the cumulative effect of spike combinations. Thus, combinations of spikes will produce different effects than pairs of single spikes. These higher-order effects, which lead to STDP asymmetry, are examined in Fig. 7. Here, evenly spaced spike-triplets, which would otherwise leave the memristor unchanged, cause a net change in w/D. Two things to note are how the second pair of spikes in the triplet are dominant. A prepost-pre triplet acts more like a post-pre pair than a pre-post pair. In addition, the repetition frequency clearly affects the change in w/D, as each successive repetition of the triplet causes the magnitude of the change in w/D to increase.

Further, the circuit produces the STDP curves depicted in Fig. 8 when exposed to spike-pair stimulus and spike-triplet stimulus. The triplets are composed of sequences of 1.8 V prepre-post ( $\Delta t < 0$ ) and post-post-pre ( $\Delta t > 0$ ) synaptic spikes of 1 ms in duration with 6 ms between the leading edges of the first two spikes in the sequence, and  $\Delta t$  is taken to be the time between the leading edges of the second and third spikes in the sequence. It is important to note that the R(t) elements in this single STDP circuit do not belong to the synapse memristor, but instead to the input and output neurons connected through it. In a network configuration, many single-memristor synapses may be connected to a particular neuron's R(t) element. This is explained in more detail in Section IV.

#### C. Demonstration with a More Realistic Memristor Model

To demonstrate how R(t) elements can facilitate STDP with a less ideal, and more realistic memristor, an STDP circuit was constructed using two simple R(t) elements and a memristor based on the Yakopcic model [61], [62]. The memristor parameters are as follows:  $a_1=a_2=0.135$ , b=0.025,  $V_p=V_n=0.2$ ,  $A_p=A_n=4000$ ,  $x_p=x_n=0.3$ ,  $\alpha_p=\alpha_n=1$ ,  $x_0=0.5$ , and  $\eta=1$ . The R(t) element parameters are  $R_1=R_2=R_3=R_4=1.5$  k $\Omega$ . The resulting STDP plot is depicted in Fig. 9.

## D. Discussion and Comparison to Other Methods

The use of charge-trapping TFTs mentioned previously is functionally similar to an R(t) approach in that the characteristics of the synaptic path are modified by an accessory element, independent of the neurons, to induce specific synaptic changes. Simulation, fabrication, and experimental validation of these devices have been demonstrated previously and has been shown to enable complex synaptic learning [56], [59], [63]. At first, the simplicity of using a single device as an R(t) element seems elegant and extremely advantageous. However, a great deal of design effort is required to realize device functionality in accordance with the requirements presented in Section II. Threshold voltage must be set to the proper value, and the subthreshold swing must offer the appropriate amount of conductance modulation for the operating voltages. Most importantly, thicknesses of the gate tunneling dielectrics and the charge trapping mechanism (nanoparticles or otherwise) must be precise to achieve the desired time constants. Once the circuit is fabricated, these response parameters cannot be

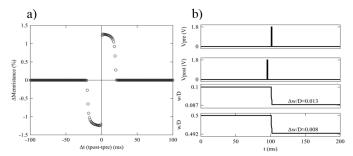

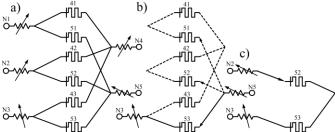

Fig. 10. a) The connections of an R(t) element-based STDP neural network consisting of three input neurons, two output neurons, six single-memristor synapses, and five R(t) elements. The connections to the pre-synaptic neurons are labeled N1-N3 and the connections to the post-synaptic neurons are labeled as N4 and N5. The synapses are labeled according to the neurons they connect using a post-pre naming convention. For example, Synapse 52 connects Neurons 5 and 2. These connections between the R(t) elements give rise to two types of non-specific synaptic plasticity. The first is heterogeneous non-specific plasticity, where the change in weight is due to a low resistance path which begins and ends on different layers. The second is homogeneous non-specific synaptic plasticity, where the change in weight is due to a low resistance path which starts and ends on the same layer. b) This figure depicts an example of the specific and non-specific synaptic paths that arise due to a pre-post pair. The specific path that results from N3 firing followed by N5 firing is illustrated with solid black lines. The non-specific paths, which could result in heterogeneous non-specific synapse weight increase of Synapses 51 and 52 and weight decreases of 41, 42, and 43, are illustrated with dashed black lines. c) This figure depicts an example of the non-specific path that arises due to a prepre pair. The non-specific path that results from N3 firing followed by N2 could result in the homogeneous non-specific synaptic weight decrease of Synapse 52 and increase of Synapse 53.

tuned as in the CMOS implementations, dramatically reducing the flexibility of the design.

Comparison of power consumption between these two approaches is also important. In the simple and compound R(t) elements presented, the minimum effective resistance of the current path (when the element is activated) is on the order of R2 plus the channel resistance of M2 or M7, resulting in approximately  $20\ k\Omega$ . This value is on the same order as the lowest possible on-state channel resistance achievable in TFT devices with high-k dielectrics such as  $HfO_2$ . Assuming that both the TFT and CMOS implementations would need to exhibit similar changes in resistance between the input and output terminal across similar voltage ranges, the power consumption should be similar in both cases.

One of the biggest drawbacks is that TFTs degrade significantly over time, resulting in an undesirable loss of the expected R(t) properties. It is also far more difficult to integrate these special devices into a typical CMOS fabrication process. Future R(t) element designs could be much more power- and area-efficient than either of the approaches discussed here. However, they would still need to follow similar behavioral rules to achieve the same learning characteristics for any given memristor technology.

## IV. NETWORK EXAMPLES

Neural networks are typically composed of multiple neurons, each of which connects to other neurons via synapses. The maximum number of R(t) elements, A, required in a layered neural network with R(t) element-based STDP can be determined using

$$A = I + O + 2\sum_{i=1}^{h} H_i,$$

(30)

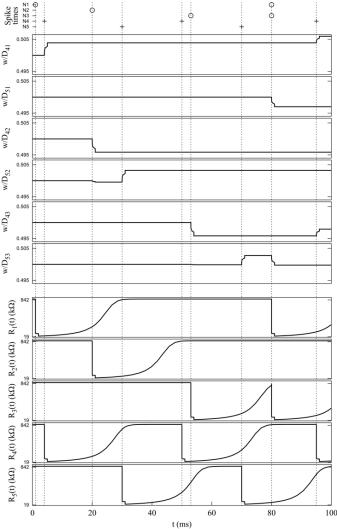

Fig. 11. The results of the small network simulation. The times of pre- and post-synaptic spikes are represented at the top with  $\circ$  and + respectively. The weights of the memristive synapses are shown in the middle and change via specific and non-specific plasticity over the course of the simulation. The effective resistances of the R(t) elements are shown at the bottom.

where I is the number of input neurons, O is the number of output neurons,  $H_i$  is the number of neurons in the  $i_{th}$  hidden layer, and h is the number of hidden layers. In most useful cases  $(I > O \ge 2)$  this is fewer than the maximum number of synapses, S, in a layered neural network given by

$$S = \sum_{i=1}^{n-1} N_i N_{i+1}, \tag{31}$$

where  $N_i$  is the number of neurons in the  $i_{th}$  layer and n is the number of layers.

#### A. Small Network Example

Fig. 10 depicts the connections of a network consisting of three input neurons, two output neurons, six synapses, and five R(t) elements. In Fig. 10, the R(t) elements are symbolically represented as variable resistors and the neurons have been abstracted as voltage signals applied to the connectome.

To demonstrate R(t) element-based STDP in this network, 1.8 V digital spikes of 1 ms duration were applied to the network inputs and outputs in a 100 ms transient simulation. Results of the applied stimulus are shown in Fig. 11. Note the

rise in w/D that occurs at 4ms in synapse 41. This corresponds with the pre- and post-synaptic spikes at 1 and 4 ms, respectively. Also, the w/D increase at 30 ms in Synapse 52 is not as large. This is due to the increased amount of time between the pre- and post-synaptic spikes, at 20 and 30 ms, resulting in a larger post-synaptic R(t) element resistance at the time of the post-synaptic spike, and thus a smaller voltage across the memristor resulting in a smaller memristance change. The decreases in w/D that occur at 53 and 80 ms in synapses 43 and 51 respectively can be explained similarly.

At 20 ms into the simulation Synapse 52 decreases in strength, despite the fact that Neuron 5 had not fired yet. This non-specific synaptic plasticity is due to alternative paths through the multiple memristors between the pre- and postsynaptic firing neurons as depicted in Fig. 10. Unlike other methods that induce non-specific synaptic plasticity, which depend on the availability of alternative paths, often referred to as sneak paths, the induced synaptic change was facilitated by activated R(t) elements—meaning that the time between the non-specific spikes altered the resistances of the available paths making some paths temporarily more susceptible to the influence of non-specific synaptic plasticity than others. In simulation non-specific synaptic plasticity has been shown to improve the recognition of sparse patterns under certain conditions [64]. A final set of spikes was added at 80 and 95 ms to demonstrate that, although the memristor is behaving nonadditively, the expression of the modified behavior may be very subtle.

Fig 12. The results of the STPR network simulation. The network consists of 25 afferent spiking neurons (N1 through N25), 26 R(t) elements, 25 memristors, and 1 output neuron (Nout). The network was trained using an unsupervised method consisting of the afferent neurons producing random spiking signals with a spike pattern embedded in them at random times. Notice that the spikes produced by the output neuron, Nout, occur after the presentation of the patterns (highlighted with grey bars)—this is STPR. A false positive occurs at 33.624 s and is highlighted with a grey circle.

#### B. STPR Example

A network consisting of 25 afferent neurons, 25 memristors, 26 R(t) element circuits, and one output neuron was also simulated to demonstrate STPR using R(t) elements. To demonstrate R(t) element-based STPR, 1.8 V digital spikes of 1 ms duration were simulated from the afferent neurons. Training was performed using an unsupervised method wherein the afferent neurons produced random spiking signals mixed with 1666 instances of a 10 ms spatiotemporal pattern over 30 seconds. Fig. 12 depicts a sample of the simulation after training. The STPR performed by this network are the spikes from the output neuron, Nout, which occur after the network is exposed to spatiotemporal patterns in the afferent neurons. The spatiotemporal patterns in Fig. 12 are highlighted with grey bars. A false positive occurs at 33.624 s in the simulation and is highlighted with a grey circle.

#### V. CONCLUSIONS

A model was described for designing dynamic resistance, or R(t) elements that achieve various forms of STDP in memristor-based neural networks. Two examples of R(t) element circuits, a simple R(t) element and a compound R(t) element, were presented. Behavior of these circuits was simulated in a commercially available software package using models provided by the foundry. Simulation results of a three-input, two-output, fully-connected spiking neural network using R(t) element-based STDP, and of STPR in a twenty-five-input, one-output SNN using R(t) circuit elements, were presented. Future work includes examining non-specific synaptic plasticity more closely, and confirming simulation results through circuit implementation and extensive electrical testing.

#### REFERENCES

- [1] B. Pakkenberg and H. J. G. Gundersen, "Neocortical Neuron Number in Humans: Effect of Sex and Age," *Journal of Comparative Neurology*, vol. 384, no. 2, pp. 312–320, 1997.

- [2] Y. Tang, J. R. Nyengaard, D. M. G. De Groot, and H. J. G. Gundersen, "Total Regional and Global Number of Synapses in the Human Brain Neocortex," *Synapse*, vol. 41, no. 3, pp. 258–273, 2001.

- [3] T. V. P. Bliss and T. Lømo, "Long-Lasting Potentiation of Synaptic Transmission in the Dentate Area of the Anaesthetized Rabbit Following Stimulation of the Perforant Path," *The Journal of Physiology*, vol. 232, no. 2, pp. 331–356, 1973.

- [4] H. Markram, J. Lübke, M. Frotscher, and B. Sakmann, "Regulation of Synaptic Efficacy by Coincidence of Postsynaptic APs and EPSPs," *Science*, vol. 275, no. 5297, pp. 213–215, Jan. 1997.

- [5] G. Bi and M. Poo, "Synaptic Modifications in Cultured Hippocampal Neurons: Dependence on Spike Timing, Synaptic Strength, and Postsynaptic Cell Type," *J. Neurosci.*, vol. 18, no. 24, p. 10464, Dec. 1998.

- [6] G. Bi and M. Poo, "Synaptic Modification by Correlated Activity: Hebb's Postulate Revisited," *Annual Review of Neuroscience*, vol. 24, no. 1, pp. 139– 166, 2001.

- [7] W. Bialek, F. Rieke, R. R. de Ruyter van Stevininck, and D. Warland, "Reading a Neural Code," *Science*, vol. 252, no. 5014, pp. 1854–1857, Jun. 1991.

- [8] B. Glackin, J. Wall, T. McGinnity, L. Maguire, and L. McDaid, "A Spiking Neural Network Model of the Medial Superior Olive Using Spike Timing Dependent Plasticity for Sound Localization," Frontiers in Computational Neuroscience, vol. 4, p. 18, 2010.

- [9] C. Carr and M. Konishi, "A Circuit for Detection of Interaural Time Differences in the Brain Stem of the Barn Owl," *Journal of Neuroscience*, vol. 10, no. 10, pp. 3227–3246, 1990.

- [10] M. H. Holmqvist and M. V. Srinivasan, "A Visually Evoked Escape Response of the Housefly," *Journal of Comparative Physiology A*, vol. 169, no. 4, pp. 451–459, Oct. 1991.

- [11] P. X. Joris, P. H. Smith, and T. C. Yin, "Coincidence Detection in the Auditory System: 50 Years After Jeffress," *Neuron*, vol. 21, no. 6, pp. 1235–1238, 1998.

- [12] J. Lisman and N. Spruston, "Questions about STDP as a General Model of Synaptic Plasticity," *Front Synaptic Neurosci*, vol. 2, pp. 140–140, Oct. 2010.

- [13] H. Z. Shouval, S. S.-H. Wang, and G. M. Wittenberg, "Spike Timing Dependent Plasticity: A Consequence of More Fundamental Learning Rules," *Frontiers in computational neuroscience*, vol. 4, no. 19, pp. 1–13, Jul. 2010.

- [14] H.-X. Wang, R. C. Gerkin, D. W. Nauen, and G.-Q. Bi, "Coactivation and Timing-Dependent Integration of Synaptic Potentiation and Depression," *Nature Neuroscience*, vol. 8, no. 2, pp. 187–193, Feb. 2005.

- [15] J.-P. Pfister and W. Gerstner, "Triplets of Spikes in a Model of Spike Timing-Dependent Plasticity," *J. Neurosci.*, vol. 26, no. 38, p. 9673, Sep. 2006.

- [16] W. Senn, "Beyond Spike Timing: The Role of Nonlinear Plasticity and Unreliable Synapses," *Biological Cybernetics*, vol. 87, no. 5–6, pp. 344–355, Dec. 2002.

- [17] P. Sjöström, G. Turrigiano, and S. Nelson, "Rate, Timing, and Cooperativity Jointly Determine Cortical Synaptic Plasticity," *Neuron*, vol. 32, pp. 1149–1164, Jan. 2002.

- [18] F. Rosenblatt, "Perceptron Simulation Experiments," *Proceedings of the IRE*, vol. 48, no. 3, pp. 301–309, Mar. 1960.

- [19] W. Maass, "Networks of Spiking Neurons: The Third Generation of Neural Network Models," *Neural Networks*, vol. 10, no. 9, pp. 1659–1671, 1997.

- [20] R. ul Rojas, *Neural Networks a Systematic Introduction*. Berlin: Springer-Verlag, 1996.

- [21] B. Linares-Barranco, T. Serrano-Gotarredona, L. Camuñas-Mesa, J. Perez-Carrasco, C. Zamarreño-Ramos, and T. Masquelier, "On Spike-Timing-Dependent-Plasticity, Memristive Devices, and Building a Self-Learning Visual Cortex," Frontiers in Neuroscience, vol. 5, p. 26, 2011.

- [22] T. Masquelier, R. Guyonneau, and S. J. Thorpe, "Spike Timing Dependent Plasticity Finds the Start of Repeating Patterns in Continuous Spike Trains," *PLOS ONE*, vol. 3, no. 1, pp. 1–9, Jan. 2008.

- [23] S. Mitra, S. Fusi, and G. Indiveri, "Real-Time Classification of Complex Patterns Using Spike-Based Learning in Neuromorphic VLSI," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 3, no. 1, pp. 32–42, Feb. 2009.

- [24] K. D. Cantley, R. C. Ivans, A. Subramaniam, and E. M. Vogel, "Spatio-Temporal Pattern Recognition in Neural Circuits with Memory-Transistor-Driven Memristive Synapses," in 2017 International Joint Conference on Neural Networks (IJCNN), 2017, pp. 4633–4640.

- [25] P. A. Merolla *et al.*, "A Million Spiking-Neuron Integrated Circuit with a Scalable Communication Network and Interface," *Science*, vol. 345, no. 6197, pp. 668–673, Aug. 2014.

- [26] J. Fieres, J. Schemmel, and K. Meier, "Realizing Biological Spiking Network Models in a Configurable Wafer-Scale Hardware System," in 2008 IEEE International Joint Conference on Neural Networks (IEEE World Congress on Computational Intelligence), 2008, pp. 969–976.

- [27] M. M. Khan et al., "SpiNNaker: Mapping Neural Networks onto a Massively-Parallel Chip Multiprocessor," in Proceedings of the International Joint Conference on Neural Networks Proc Int Jt Conf Neural Networks, United States, 2008, pp. 2849–2856.

- [28] R. C. Ivans, K. D. Cantley, and J. L. Shumaker, "A CMOS Synapse Design Implementing Tunable Asymmetric Spike Timing-Dependent Plasticity," in 2017 IEEE 60th International Midwest Symposium on Circuits and Systems (MWSCAS), 2017, pp. 1125–1128.

- [29] S. G. Pradyumna and S. S. Rathod, "Analysis of CMOS Synapse Generating Excitatory Postsynaptic Potential using DC Control Voltages," in 2015 Global Conference on Communication Technologies (GCCT), 2015, pp. 433–436.

- [30] G. Indiveri, E. Chicca, and R. Douglas, "A VLSI Array of Low-Power Spiking Neurons and Bistable Synapses With Spike-Timing Dependent Plasticity," *IEEE Trans. Neural Netw.*, vol. 17, no. 1, pp. 211–221, Jan. 2006.

- [31] S. Mitra, S. Fusi, and G. Indiveri, "A VLSI Spike-Driven Dynamic Synapse Which Learns Only When Necessary," in 2006 IEEE International Symposium on Circuits and Systems (ISCAS), 2006, pp. 4 pp.-.

- [32] E. Chicca, F. Stefanini, C. Bartolozzi, and G. Indiveri, "Neuromorphic Electronic Circuits for Building Autonomous Cognitive Systems," *Proc. IEEE*, vol. 102, no. 9, pp. 1367–1388, Sep. 2014.

- [33] C. Diorio, P. Hasler, A. Minch, and C. A. Mead, "A Single-Transistor Silicon Synapse," *IEEE Transactions* on Electron Devices, vol. 43, no. 11, pp. 1972–1980, Nov. 1996.

- [34] M. Hu, Y. Chen, J. J. Yang, Y. Wang, and H. H. Li, "A Compact Memristor-Based Dynamic Synapse for Spiking Neural Networks," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 36, no. 8, pp. 1353–1366, Aug. 2017.

- [35] M. Wuttig and N. Yamada, "Phase-Change Materials for Rewriteable Data Storage," *Nature materials*, vol. 6, pp. 824–832, Dec. 2007.

- [36] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The Missing Memristor Found," *Nature*, vol. 453, no. 7191, pp. 80–83, May 2008.

- [37] S. H. Jo, T. Chang, I. Ebong, B. B. Bhadviya, P. Mazumder, and W. Lu, "Nanoscale Memristor Device as Synapse in Neuromorphic Systems," *Nano Letters*, vol. 10, no. 4, pp. 1297–1301, 2010.

- [38] B. Govoreanu *et al.*, "10×10 nm2 Hf/HfOx Crossbar Resistive RAM with Excellent Performance, Reliability and Low-Energy Operation," in *2011 International Electron Devices Meeting*, Washington, DC, USA, 2011, pp. 31.6.1-31.6.4.

- [39] M.-J. Lee *et al.*, "A Fast, High-Endurance and Scalable Non-Volatile Memory Device Made from Asymmetric Ta2O5-x/TaO2-x Bilayer Structures," *Nature Materials*, vol. 10, p. 625, Jul. 2011.

- [40] A. Chanthbouala *et al.*, "A Ferroelectric Memristor," *Nature Materials*, vol. 11, p. 860, Sep. 2012.

- [41] D. Kuzum, R. G. D. Jeyasingh, B. Lee, and H.-S. P. Wong, "Nanoelectronic Programmable Synapses Based on Phase Change Materials for Brain-Inspired Computing," *Nano Letters*, vol. 12, no. 5, pp. 2179– 2186, 2012.

- [42] T. Prodromakis, I. Salaoru, A. Khiat, and C. Toumazou, "Concurrent Resistive and Capacitive Switching of Nanoscale TiO2 Memristors," in *Nature Conference on Frontiers in Electronic Materials: Correlation Effects and Memristive Phenomena*, 2012.

- [43] X. Wu, V. Saxena, and K. A. Campbell, "Energy-Efficient STDP-Based Learning Circuits with Memristor Synapses," in *Machine Intelligence and Bioinspired Computation: Theory and Applications VIII*, Baltimore, Maryland, USA, 2014, vol. 9119, p. 977906.

- [44] H. Mostafa, C. Mayr, and G. Indiveri, "Beyond Spike-Timing Dependent Plasticity in Memristor Crossbar Arrays," in 2016 IEEE International Symposium on Circuits and Systems (ISCAS), 2016, pp. 926–929.

- [45] B. Linares-Barranco and T. Serrano-Gotarredona, "Memristance Can Explain Spike-Time-Dependent-Plasticity in Neural Synapses," *Nature Precedings*, pp. 1–4, Mar. 2009.

- [46] G. S. Snider, "Self-Organized Computation with Unreliable, Memristive Nanodevices," *Nanotechnology*, vol. 18, no. 36, pp. 1–13, Aug. 2007.

- [47] G. Indiveri *et al.*, "Neuromorphic Silicon Neuron Circuits," *Frontiers in Neuroscience*, vol. 5, no. 73, pp. 1–23, 2011.

- [48] J. A. Pérez-Carrasco, C. Zamarreño-Ramos, T. Serrano-Gotarredona, and B. Linares-Barranco, "On Neuromorphic Spiking Architectures for Asynchronous STDP Memristive Systems," in *Proceedings of 2010 IEEE International Symposium on Circuits and Systems*, 2010, pp. 1659–1662.

- [49] T. Serrano-Gotarredona, T. Prodromakis, and B. Linares-Barranco, "A Proposal for Hybrid Memristor-CMOS Spiking Neuromorphic Learning Systems," *IEEE Circuits and Systems Magazine*, vol. 13, no. 2, pp. 74–88, May 2013.

- [50] B. Linares-Barranco and T. Serrano-Gotarredona, "Exploiting Memristance in Adaptive Asynchronous

- Spiking Neuromorphic Nanotechnology Systems," in 2009 9th IEEE Conference on Nanotechnology (IEEE-NANO), Genoa, Italy, 2009, pp. 601–604.

- [51] C. Mayr and J. Partzsch, "Rate and Pulse Based Plasticity Governed by Local Synaptic State Variables," *Frontiers in Synaptic Neuroscience*, vol. 2, no. 33, pp. 1–28, Sep. 2010.

- [52] C. Clopath and W. Gerstner, "Voltage and Spike Timing Interact in STDP A Unified Model," *Frontiers in Synaptic Neuroscience*, vol. 2, no. 25, pp. 1–11, Jul. 2010.

- [53] W. Cai, F. Ellinger, and R. Tetzlaff, "Neuronal Synapse as a Memristor: Modeling Pair- and Triplet-Based STDP Rule," *IEEE Transactions on Biomedical Circuits and Systems*, vol. 9, no. 1, pp. 87–95, Feb. 2015

- [54] K. D. Cantley, A. Subramaniam, H. J. Stiegler, R. A. Chapman, and E. M. Vogel, "Spike Timing-Dependent Synaptic Plasticity Using Memristors and Nano-Crystalline Silicon TFT Memories," in 2011 11th IEEE International Conference on Nanotechnology, Portland, OR, 2011, pp. 421–425.

- [55] K. D. Cantley, A. Subramaniam, and E. M. Vogel, "Spike Timing-Dependent Plasticity Using Memristors and Nano-Crystalline Silicon TFT Memories," in *Nanoelectronic Device Applications Handbook*, 1st ed., J. E. Morris and K. Iniewski, Eds. CRC Press, 2013.

- [56] A. Subramaniam, K. Cantley, G. Bersuker, D. Gilmer, and E. Vogel, "Spike-Timing-Dependent Plasticity Using Biologically Realistic Action Potentials and Low-Temperature Materials," *Nanotechnology, IEEE Transactions on*, vol. 12, no. 3, pp. 450–459, May 2013.

- [57] T. Schaffer, A. Stanaski, A. Glaser, and P. Franzon, "The NCSU Design Kit for IC Fabrication Through MOSIS," in *International Cadence User Group*, Austin, TX, 1998.

- [58] Z. Biolek, D. Biolek, and V. Biolkova, "SPICE Model of Memristor with Nonlinear Dopant Drift.," *Radioengineering*, vol. 18, no. 2, pp. 210–214, Jun. 2009

- [59] K. D. Cantley, A. Subramaniam, H. J. Stiegler, R. A. Chapman, and E. M. Vogel, "Hebbian Learning in Spiking Neural Networks With Nanocrystalline Silicon TFTs and Memristive Synapses," *IEEE Transactions on Nanotechnology*, vol. 10, no. 5, pp. 1066–1073, Sep. 2011.

- [60] K. D. Cantley, A. Subramaniam, H. J. Stiegler, R. A. Chapman, and E. M. Vogel, "Neural Learning Circuits Utilizing Nano-Crystalline Silicon Transistors and Memristors," *IEEE Transactions on Neural Networks* and Learning Systems, vol. 23, no. 4, pp. 565–573, Apr. 2012.

- [61] C. Yakopcic, T. M. Taha, G. Subramanyam, R. E. Pino, and S. Rogers, "A Memristor Device Model," *IEEE Electron Device Letters*, vol. 32, no. 10, pp. 1436–1438, Oct. 2011.

- [62] C. Yakopcic, T. M. Taha, G. Subramanyam, and R. E. Pino, "Generalized Memristive Device SPICE Model and its Application in Circuit Design," *IEEE Transactions on Computer-Aided Design of Integrated*

- Circuits and Systems, vol. 32, no. 8, pp. 1201–1214, Aug. 2013.

- [63] S. Aghnout and G. Karimi, "Modeling triplet spike timing dependent plasticity using a hybrid TFTmemristor neuromorphic synapse," *Integration*, vol. 64, pp. 184–191, 2019.

- [64] K. Safaryan, R. Maex, N. Davey, R. Adams, and V. Steuber, "Nonspecific Synaptic Plasticity Improves the Recognition of Sparse Patterns Degraded by Local Noise," *Scientific Reports*, vol. 7, no. 46550, pp. 1–14, Apr. 2017.