www.acsnano.org

# Controlling Polarity of MoTe<sub>2</sub> Transistors for Monolithic Complementary Logic *via* Schottky Contact Engineering

Xia Liu, Arnob Islam, Jing Guo, and Philip X.-L. Feng\*

ABSTRACT: Two-dimensional (2D) layered molybdenum ditelluride (MoTe<sub>2</sub>) crystals, featuring a low energy barrier in the crystalline phase transition and a sizable band gap close to that of silicon, are rapidly emerging with substantial potential and promise for future nanoelectronics. It has been challenging, however, to realize n-type MoTe<sub>2</sub> field-effect transistors (FETs), thus complementary logic, because MoTe<sub>2</sub> FETs mainly exhibit p-type behavior. Here, we report a dopant-free method for controlling polarity of MoTe<sub>2</sub> FETs by modifying Schottky barriers at their MoTe<sub>2</sub>—metal contacts via thermal annealing. Upon annealing, MoTe<sub>2</sub> FETs encapsulated by hexagonal boron nitride (h-BN) are consistently changed from hole to electron conduction, displaying an on/off current ratio of 10<sup>5</sup> or higher. When the MoTe<sub>2</sub> channel is sandwiched between top and bottom h-BN thin layers (h-BN/MoTe<sub>2</sub>/h-BN FETs), higher field-effect mobility is attained, up to 48.1 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (hole) and 52.4 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> (electron) before and after thermal annealing, respectively. The thermally controlled FET polarity change further enables high-performance MoTe<sub>2</sub> monolithic complementary inverters with gain as high as 36, suggesting this simple and effectual approach may lead to compelling possibilities of rationally controlling transport polarity, on demand, in atomically thin transistors with metal contacts and their 2D integrated circuits.

**KEYWORDS:** 2D materials, molybdenum ditelluride (MoTe<sub>2</sub>), transistor polarity, Schottky barrier, semiconductor—metal contact, monolithic inverter, thermal annealing

wo-dimensional (2D) atomic or molecule sheets of layered semiconductors are natively endowed with ultimate thinness, broad spectra of outstanding electronic and optoelectronic properties, as well as their compelling dependency on discrete, integer numbers of layers, thus having strong potential for enabling devices with unconventional features and performance. The Group VI transition metal dichalcogenides (TMDCs) have tunable band gaps (from 0.88 to 2 eV) and are especially suitable for atomically thin transistors by virtue of their band gaps being comparable with those of conventional semiconductors (e.g., Ge, Si, GaAs). Moreover, these semiconducting TMDCs show reliable transition from indirect to direct band gap when scaled down to the single-layer limit. They also offer different

crystal structures and phases so that they can be accessed and configured to achieve programmable functions. For example, the electrodes (*i.e.*, source and drain) and the channel of a field-effect transistor (FET) can be built in a single material with configurable metallic and semiconducting phases. 6-9 TMDCs may also possess dangling-bond-free surfaces and can be assembled together through van der Waals interactions to

Received: July 13, 2019 Accepted: January 7, 2020 Published: January 7, 2020

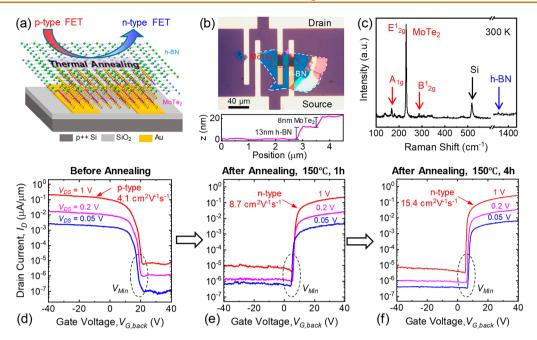

Figure 1. Device structure and electronic characteristics of back-gate h-BN/MoTe<sub>2</sub> FET measured before and after thermal annealing. (a) 3D atomic-view schematic of the device and its heterostructure. (b) Optical microscopy image of the representative device and thickness profile of stacking nanosheets. (c) Raman spectroscopy measurement and verification of signatory Raman peaks of the constituting crystals in the device stack. (d) Drain current,  $I_{\rm D}$ , as a function of the back-gate voltage,  $V_{\rm G,back}$ , of the as-fabricated FET at varying drain-to-source bias voltages,  $V_{\rm DS}$ . (e) Transfer characteristics of the same device after thermal annealing in N<sub>2</sub> flow for 1 h. (f) Transfer characteristics of the device after the second thermal annealing in N<sub>2</sub> flow for 4 h.

create novel heterostructures with great versatility. To date, 2D TMDCs have been adopted in many electronic and optoelectronic devices, ranging from FETs, tunneling FETs, memories, to logic circuits and photodetectors. 10-12 Carrier transport in the channels and across the metal-semiconductor contacts is at the heart of electronics and optoelectronics. One basic and essential characteristic of a 2D FET is its dominant polarity of carrier transport, that is, electron (n-type) or hole (p-type) conduction in the channel. However, often due to strong Fermi level pinning at the metal-2D semiconductor interface, the Schottky barrier (SB) height does not change considerably irrespective of the choice of metal contact, which results in 2D molybdenum disulfide (MoS<sub>2</sub>) FETs mainly exhibiting n-type conduction<sup>13</sup> and 2D tungsten diselenide (WSe<sub>2</sub>) FETs being accessible to both electron and hole conduction.14

Recently, molybdenum ditelluride (MoTe<sub>2</sub>), a newer member of the TMDC family, is receiving increasing attention due to its rich crystalline phases and its unusual semiconducting, metallic, and superconducting properties. 15-18 The hexagonally structured MoTe<sub>2</sub> has a band gap comparably narrower than those of other semiconducting TMDCs.<sup>5,1</sup> Single-layer (1L) MoTe<sub>2</sub> is theoretically predicted and experimentally verified to have a band gap of  $E_g = 1.1$  eV, which very well matches the band gap of silicon (Si). The acoustic phonon-limited mobility of MoTe2 is greater than 2500 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> theoretically.<sup>20</sup> In contrast to MoS<sub>2</sub>, MoTe<sub>2</sub> mainly shows p-type (or p-dominated ambipolar) when prepared by using a flux of tellurium (Te). Nevertheless, traditional doping methods, including ion implantation and dopant diffusion, are not yet practically applicable to 2D materials.<sup>21,22</sup> The technological challenge of chemical doping is manipulating doping concentration in atomically thin semiconductors. Recently, unconventional doping strategies,

such as molecular doping, 23,24 electron doping, 25,26 and optoelectronic activation, 27 have been explored. Such methods mainly involve surface dopant species, including H-doping from parasitic H<sub>2</sub>O accompanying Al<sub>2</sub>O<sub>3</sub> atomic layer deposition (ALD),<sup>24</sup> MgO film deposited by electron-beam evaporation, <sup>26</sup> or O<sub>2</sub>/H<sub>2</sub>O ad/desorption-induced doping mediated by electrothermal self-heating.<sup>28</sup> These approaches are invasive to the host 2D materials and often require special gases or complex fabrication processes. Meanwhile, another issue in most TMDCs is that surface stability and susceptibility can often be affected by the presence of ionic impurities when exposed to an ambient environment or at the interface with the substrate.<sup>29–31</sup> MoTe<sub>2</sub> thin FETs are also sensitive to oxygen and water vapor due to intrinsic Te defects, thereby altering the device performance.<sup>32</sup> Therefore, reliable and controllable creation of n-type transport of MoTe<sub>2</sub> FETs remains an open challenge and demands careful investigation toward realizing MoTe<sub>2</sub> monolithic logic functions and fulfilling the promises and potential of this excellent 2D material.

In this study, we introduce a dopant-free method for rationally controlling the polarity of MoTe<sub>2</sub> transistors from pto n-type. To prevent environmental susceptibility and ensure stability of the transistor performance, we employ a thin hexagonal boron nitride (h-BN) layer on top of MoTe<sub>2</sub> to encapsulate the devices, thus evading direct exposure of the chemically active Te atoms on the device surface. The pristine h-BN-encapsulated MoTe<sub>2</sub> (h-BN/MoTe<sub>2</sub>) FETs are p-type. Interestingly, after simple thermal annealing at ~100 to 350 °C in inert gases, the polarity of the h-BN/MoTe<sub>2</sub> transistors is switched from p-type to n-type with excellent performance enhancement. The efficacy and simplicity of this approach to controlling transistor polarity manifests in several aspects. First, the method does not involve any chemical dopants, electrical field, or any complex process. Second, very moderate annealing

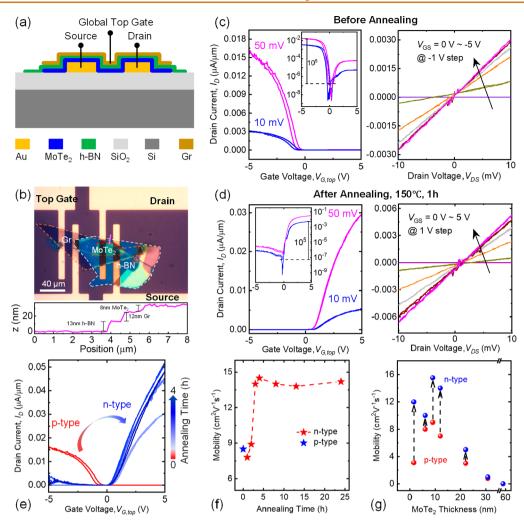

Figure 2. Transfer characteristics of the Gr top-gate h-BN/MoTe<sub>2</sub> FET measured before and after thermal annealing. (a) Cross-sectional illustration of the top-gate MoTe<sub>2</sub> FET. (b) Optical microscopy image of the device and thickness profile of stacking nanosheets. (c) Left: Drain current,  $I_{\rm D}$ , as a function of the top-gate voltage,  $V_{\rm G,top}$ , with drain-to-source excitation voltage  $V_{\rm DS}$  of 50 and 10 mV in linear and logarithmic scale, respectively. Right:  $I_{\rm D}$  as a function of  $V_{\rm DS}$  for the device before thermal annealing as  $V_{\rm G,top}$  decreases from 0 to -5 V with a step of -1 V. (d) Left:  $I_{\rm D}$  as a function of  $V_{\rm G,top}$  for the same device after 1 h thermal annealing at 150 °C in linear and logarithmic scale, respectively, which shows unipolar n-type. Right:  $I_{\rm D}$  as a function of  $V_{\rm DS}$  for the annealed device with  $V_{\rm G,top}$  increasing from 0 to 5 V with a step of 1 V. (e) Annealing time dependence of  $I_{\rm D}$ – $V_{\rm G,top}$  curves at the same  $V_{\rm DS}$  = 50 mV. (f) Measured mobility with varying annealing time. (g) Summary of the switch from hole to electron conduction, measured from multiple top-gate h-BN/MoTe<sub>2</sub> FETs with varying MoTe<sub>2</sub> thickness, all through 4 h annealing.

temperature (~100 °C) can trigger p- to n-transport in MoTe<sub>2</sub> FETs with Au contact electrodes. Third, h-BN encapsulation renders excellent passivation and highly stable transistors. Importantly, this simple technique has enabled MoTe<sub>2</sub> transistors with very high electron mobility of  $\mu_{\rm n} = 52.4~{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1}$  and on/off current ratio of  $I_{\rm on}/I_{\rm off} \sim 10^5$ . This controllable realization of n-type MoTe<sub>2</sub> transistors is conscientiously elucidated by MoTe<sub>2</sub>—metal Schottky contact modulation due to thermal annealing, along with an extensive set of clear and deterministic control experiments. This method is further utilized to build all-MoTe<sub>2</sub> monolithic complementary logic functions, thus validating a viable and agile approach to controlling transport polarity and enhancing performance of 2D Schottky contact FET-enabled electronic and optoelectronic devices.

# **RESULTS AND DISCUSSION**

p- to n-Type Polarity Change in Back-Gate MoTe<sub>2</sub> FETs by Thermal Annealing. We first describe the device

structure and measure the transfer characteristics of a global back-gate MoTe<sub>2</sub> FET with top h-BN encapsulation. Figure 1a presents a three-dimensional (3D) illustration of the h-BNencapsulated MoTe<sub>2</sub> (h-BN/MoTe<sub>2</sub>) FET on 290 nm thick silicon oxide (SiO<sub>2</sub>) with doped Si as the global back gate. Specifically, the MoTe<sub>2</sub> crystal is fully encapsulated by a thin h-BN layer. A top-view optical micrograph of the as-fabricated h-BN/MoTe<sub>2</sub> FET (Figure 1b) displays the distinctive colors of different stacking layers of the heterostructure. Gold (Au) is selected as the electrode material due to its moderate work function  $(\phi_{\rm m}=4.7-4.9~{\rm eV})^{33,34}$  compared to that of other metals (such as Pt, Ni, and Ti), so that the Fermi level is around the midgap of the MoTe<sub>2</sub> semiconductor.<sup>35</sup> The line profile measured by atomic force microscopy (AFM) shows that the thicknesses of h-BN and MoTe<sub>2</sub> layers are 13 and 8 nm, respectively. The device fabrication process is described in detail in the Experimental Section. Raman spectroscopy probing ( $\lambda = 532$  nm) on the h-BN/MoTe<sub>2</sub> stack of the back-gate FET (Figure 1c) exhibits the overall information on

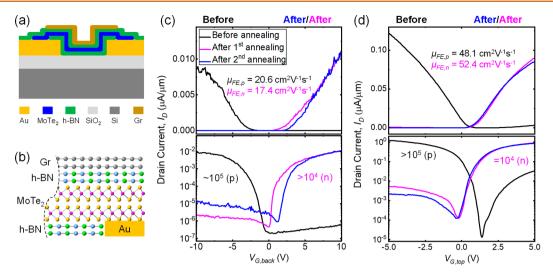

Figure 3. Transfer characteristics of double-encapsulated, dual-gate h-BN/MoTe<sub>2</sub>/h-BN FET measured before and after thermal annealing. (a) Cross-sectional illustration of the h-BN/MoTe<sub>2</sub>/h-BN FET. (b) 3D atomic-view schematic of the S-M contact region. (c)  $I_{\rm D}-V_{\rm G,back}$  curves measured in the back-gate configuration, before thermal annealing, after the first and the second thermal annealing, in linear (top plot) and logarithmic (bottom plot) scales, all at  $V_{\rm DS}=50$  mV. (d)  $I_{\rm D}-V_{\rm G,top}$  curves measured in the top-gate configuration, before thermal annealing, after the first and second thermal annealing, all at  $V_{\rm DS}=50$  mV.

the identities of the constitutive crystals in this heterostructure.  $^{36}$

Transfer characteristics of the back-gate FET is investigated under simple thermal annealing. Figure 1d shows the drain current  $(I_D)$  as a function of the back-gate voltage  $(V_{G,back})$  and at various drain voltages  $(V_{DS})$  before thermal annealing. As shown, the as-fabricated pristine back-gate h-BN/MoTe<sub>2</sub> FET exhibits hole conduction behavior (p-type transport), although the ambipolar MoTe<sub>2</sub> transistor has been previously reported due to Fermi level pinning at contacts.<sup>37</sup> The hole field-effect mobility is  $\mu_{\text{FE,p}} = \frac{L}{W} \frac{d}{\epsilon_0 \epsilon_r} \frac{1}{V_{\text{DS}}} \frac{dI_{\text{DS}}}{dV_{\text{G}}} \approx 4.1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , where Land W are the length and width of the channel, respectively, and d and  $\varepsilon_r$  are the thickness and dielectric constant of the corresponding dielectric layer, respectively. The dielectric constants of SiO<sub>2</sub> and h-BN are 3.2 and 3.5, respectively. The subthreshold swing (SS) is calculated to be SS =  $\left(\frac{d \log_{10} I_{\rm DS}}{dV_{\rm G}}\right)^{-1}$  = 250 mV/dec. As seen in Figure 1d, the gate voltage sweeping remains stable, and thus the environment has little effect on the measured data.

It is worth mentioning that the gate voltage  $(V_{Min})$  at which the current becomes minimal is positive, indicating that the Fermi level of the as-exfoliated MoTe<sub>2</sub> is closer to the valence band. Specifically, in terms of crystal structure, the initial atom ratio of Te and Mo is 2.3, higher than the stoichiometric number of 2.0 (Supplementary Figure S1), verified by energydispersive X-ray spectroscopy (EDS). The excess Te is suggested to be atomic Te dopants that have been consistently observed in CVD-grown MoTe<sub>2</sub>. 38,39 It was recently reported that the intrinsic defects of natural MoTe2 are in the forms of interstitial/intercalated Te atoms and Mo vacancies observed through scanning transmission electron microscopy (STEM) and scanning tunneling microscopy (STM).40 Therefore, presumably, the freshly exfoliated MoTe<sub>2</sub> flakes are p-type doped by excess Te. Interestingly, after thermal annealing at 150 °C in N<sub>2</sub> flow for 1 h, the polarity of the same device immediately turns into unipolar n-type (Figure 1e). In addition, the electron field-effect mobility increases to  $\mu_{\rm FE,n}$  =

8.7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. Moreover, the hysteresis (quantified in voltage swing) decreases by ~4 times after thermal annealing (Supplementary Figure S2). The intrinsic origin of hysteresis in MoTe<sub>2</sub> transistors could probably be attributed to charge trap states at the interface between MoTe2 and the dielectric due to adsorption/desorption of water molecules or other contaminants. Thermal annealing essentially removes such contaminants and reduces the hysteresis. The positive value of  $V_{\text{Min}}$  in Figure 1e indicates that the MoTe<sub>2</sub> channel with n-type conduction is still p-type doped, which indicates that the transport behavior in the annealed MoTe2 FET is not due to the electron doping effect. Subsequently, after a second thermal annealing for 4 h, the FET maintains n-type conduction and its performance is further boosted, with electron mobility boosted up to  $\mu_{FE,n} = 15.4 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  and an improved subthreshold swing of SS = 208 mV/dec (Figure 1f). It shall be emphasized that the positive values of  $V_{\rm Min}$  in Figure 1e,f are approximately unchanged, which suggests that thermal annealing has a negligible effect on shifting the Fermi level of the p-type MoTe<sub>2</sub> channel material. It is worth mentioning that in Figure 1d,f, Ioff increases with the increase of drain voltage  $(V_{DS})$  due to the increase of thermionic emission contributed carrier transport at higher  $V_{\rm DS}$ .

p- to n-Type Polarity Change in Top-Gate MoTe<sub>2</sub> FETs by Thermal Annealing. The transistor polarity change from p- to n-type has also been observed in top-gate h-BN/MoTe<sub>2</sub> FETs, as shown in Figure 2. A thin graphite (Gr) layer is additively transferred on top of an h-BN-encapsulated MoTe<sub>2</sub> FET to serve as the global top gate, as shown in Figure 2a,b. Figure 2c shows measured  $I_{\rm D}$  as a function of  $V_{\rm G,top}$  for the top-gate FET before thermal annealing. The transistor behaves as a unipolar p-type with hole mobility of  $\mu_{\rm FE,p}=7.8~{\rm cm^2~V^{-1}~s^{-1}}$  and an on/off current ratio of  $I_{\rm on}/I_{\rm off}\sim10^5$ .  $I_{\rm D}$  as a function of  $V_{\rm DS}$  ( $I_{\rm D}-V_{\rm DS}$ ) increases with increasing top-gate negative voltage  $V_{\rm G,top}$ , indicating p-type conduction in the transistor. The linear  $I_{\rm D}-V_{\rm DS}$  characteristic indicates low SB at the source/drain (S/D) contacts, and holes can tunnel through. After thermal annealing under the same condition, 150 °C for 1 h (Figure 2d), the transistor polarity is also changed from p-

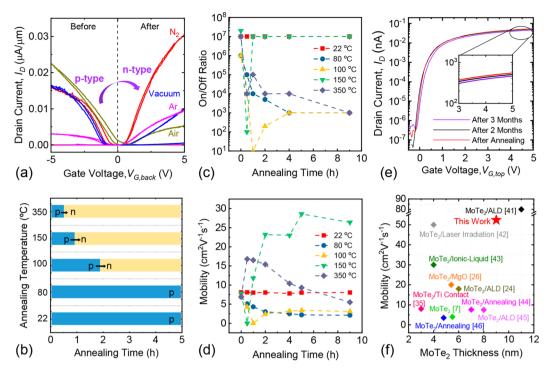

Figure 4. Summary on polarity change, annealing conditions, and performance of h-BN-encapsulated MoTe<sub>2</sub> FETs. (a) Transfer characteristics of top-gate h-BN/MoTe<sub>2</sub> FETs before and after thermal annealing in different carrying gases or vacuum. (b) Transistor polarity switch occurs at >100 °C and needs shorter time at higher annealing temperature. (c) Evolution of mobility with varying annealing temperature. (d) On/off ratio varies with annealing temperature and time. (e) Transfer characteristics of the same device after thermal annealing and after several months. (f) Comparison with other best n-type MoTe<sub>2</sub> FETs reported in the literature.

to n-type, and the hysteresis voltage swing decreases dramatically. The  $I_{\rm D}{-}V_{\rm DS}$  characteristic is also linear, and the drain current increases with increasing positive  $V_{\rm G,top}$ . Figure 2e summarizes that the transistor polarity has been changed from p- to n-type and subsequently maintains n-type during continued thermal annealing. The mobility of the top-gate device increases with continued thermal annealing and reaches a high value after 4 h, stabilizes, and persists for >24 h of annealing (Figure 2f). In addition, the transistors show reliable current levels and high stability of threshold voltage  $(V_{\rm T})$  during thermal annealing, confirming the h-BN-encapsulated MoTe<sub>2</sub> structures are robust and electrically stable.

We have measured tens of top-gate h-BN/MoTe<sub>2</sub> transistors with various MoTe<sub>2</sub> thicknesses, and all of them (as summarized in Figure 2g) exhibit polarity change from ptype (of the as-fabricated pristine devices) to n-type after 4 h thermal annealing at 150 °C in a N2 flow. In addition, the gate leakage currents in all of the measured transistors are negligible at several picoamperes (pA) (Supplementary Figure S2). The freshly exfoliated MoTe2 flakes used in this study cover a wide range of thicknesses, from 1.5 nm (bilayer, 2L) to 57.6 nm (82L). A thicker channel enhances the carrier mobility through reduced Coulomb scattering due to physical separation from the SiO<sub>2</sub> dielectric. Meanwhile, the transistor performance declines when the MoTe<sub>2</sub> thickness is greater than 10 nm. Given the highly consistent observations in both back-gate and top-gate devices described above, the data have shown that the type of dominant injected carriers in the h-BN-encapsulated MoTe<sub>2</sub> FETs have been switched from p- to n-type through the 150 °C thermal annealing.

p- to n-Type Polarity Change in Dual-Gate MoTe<sub>2</sub> FETs by Thermal Annealing. Considering SiO<sub>2</sub> used in the above devices might interact with MoTe<sub>2</sub> at the interface, we

conduct a careful control experiment using h-BN as the bottom dielectric of the transistor. h-BN makes outstanding ultrathin dielectric layers for 2D electronics due to atomically smooth surface and high immunity to surface states. Figure 3a illustrates the h-BN double-encapsulated device with both top gate (Gr) and back gate (Si), with thicknesses of the top h-BN, MoTe<sub>2</sub>, and bottom h-BN being 25, 9, and 30 nm, respectively. Figure 3c shows that the polarity of the back-gate branch is p-type with a hole mobility of  $\mu_{\text{FE},p} = 20.6 \text{ cm}^2 \text{ V}^{-1}$ s<sup>-1</sup>. After thermal annealing under the same condition, the transistor polarity is changed from p- to n-type. Similarly, the top-gate h-BN/MoTe<sub>2</sub>/h-BN transistor shows the same phenomenon (Figure 3d). Before thermal annealing, the hole mobility is  $\mu_{\text{FE,p}} = 48.1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , which is the highest value ever attained by back-gate MoTe2 transistors at room temperature. After thermal annealing, the transistor exhibits electron conduction (n-type) with an even higher mobility of  $\mu_{\text{FE,n}} = 52.4 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ .

Control Experiments, Persistence of Polarity Change, and Its Temperature Dependency. We systematically investigate the p- to n-type polarity change phenomena and further conduct more control experiments to meticulously explore effects possibly contributing to the transistor polarity change. One first set of control experiments is on direct comparison between devices with and without h-BN encapsulation, cofabricated on the same MoTe<sub>2</sub> flake (Supplementary Figure S3). Upon the same thermal annealing (at 150 °C in N<sub>2</sub> flow for 1 h or longer), the h-BN-encapsulated FET shows a p- to n-type polarity switch, whereas the uncovered one does not transform to n-type but exhibits considerable degradation of its p-type behavior. As detailed in Supporting Information, spectroscopic studies (EDS, Raman) indicate that the annealing has no noticeable

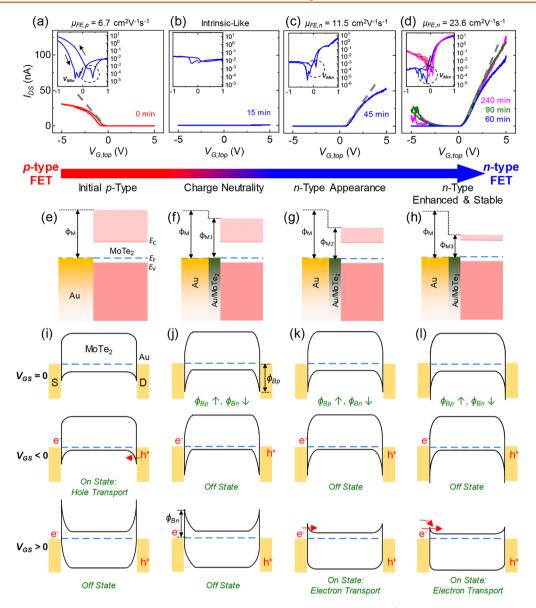

Figure 5. Visualizing the polarity change process and elucidating its underlying mechanism. (a–d) Polarity change process of top-gate h-BN/MoTe<sub>2</sub> FET during 150 °C thermal annealing, measured in ambient environment.  $V_{\rm DS} = 50$  mV. The plots in (b–d) share the same y-axis label with the plot in (a). (e–h) Corresponding band diagrams of the vertical MoTe<sub>2</sub>–Au contact from the initial state and during the annealing process. (i–l) Corresponding electrostatically gated band diagrams of the transistor with horizontal source—gate—drain structure in the four stages and for  $V_{\rm GS} = 0$ ,  $V_{\rm GS} < 0$ , and  $V_{\rm GS} > 0$  (assuming  $V_{\rm DS} = 0$  for simplicity in depicting the diagrams).

effect on the h-BN-encapsulated MoTe<sub>2</sub> crystal in the channel region, whereas it probably has caused oxidation and degradation in the uncovered MoTe<sub>2</sub> (Supplementary Figure S4). It is also indicated that the h-BN encapsulation is sufficiently impermeable to prevent Te loss from the covered MoTe<sub>2</sub> channels through 150 °C annealing (Supplementary Figure S1b). Upon varying the top h-BN thickness, we have also found the annealing-induced polarity change is independent of the encapsulating h-BN thickness (Supplementary Figure S5).

Persistency of p- to n-type polarity change has been consistently observed in all h-BN top- and double-encapsulated FETs (as detailed in previous sections), upon annealing at 150 °C, regardless of the carrying gases. The h-BN/MoTe<sub>2</sub> transistors are thermally annealed in vacuum or in the carrying gas of N<sub>2</sub>, Ar, or air. Figure 4a shows that all pristine p-type conduction switches to n-type conduction after annealing,

independent of carrying gas. It is noted that as the thickness and area of the devices are different, the on-state currents of the devices vary.

Meanwhile, annealing temperature can determine if the transistor polarity change occurs, and there appears to be a threshold temperature. The temperature dependence of the transfer characteristics is investigated in the temperature range from 22 °C (room temperature) to 350 °C. The polarity switch from p- to n-type exclusively occurs at annealing temperatures greater than 100 °C (Figure 4b). Figure 4c,d exhibits the time evolutions (during annealing) of mobility and on/off ratio varying with annealing temperature, respectively.

Polarity-Switched Transistor Performance and Benchmarking. A long-term stable carrier transport in ultrathin channels is important for realizing practical high-performance devices. We compare the measured transfer characteristics of the same device after thermal annealing and

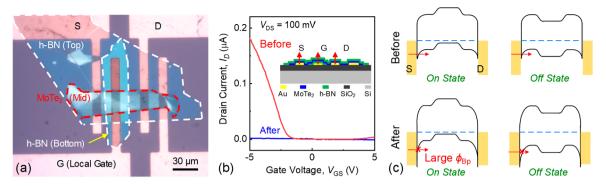

Figure 6. Further verification with deterministic control experiment on local gate FET to elucidate the mechanism of modifying the MoTe<sub>2</sub>—Au Schottky contact on changing device transport polarity. (a) Optical microscopy image of the local gate MoTe<sub>2</sub> transistor encapsulated by h-BN. (b)  $I_{\rm D}$ – $V_{\rm GS}$  characteristics of local gate MoTe<sub>2</sub> transistor before and after thermal annealing at 150 °C for 1 h. The inset shows the cross-sectional illustration of the device. (c) Corresponding electrostatically gated band diagrams of the local gate transistor with horizontal S–G–D structure at on state and off state before and after thermal annealing.

after preserving it in ambient environment for a long time. As shown in Figure 4e, the  $I_{\rm D}{-}V_{\rm G,top}$  curves exhibit excellent repeatability and stability after 2 and 3 months. Continuous measurement over 36 h also showed very stable performance (Supplementary Figure S6). Figure 4f summarizes and benchmarks the specifications and performance of devices measured in this work against the other best n-type MoTe<sub>2</sub> FETs reported in the field,  $^{41-46}$  illustrating that post-annealing polarity-switched devices are outstanding and among the very best in terms of measured mobility. Specifically, the highest mobility ( $\mu_{\rm FE,n}=52.4~{\rm cm}^2~{\rm V}^{-1}~{\rm s}^{-1}$ ) is attained in a h-BN/MoTe<sub>2</sub>/h-BN device with a 9 nm thick MoTe<sub>2</sub> channel, and this is, to date, the highest mobility measured among thermally annealed MoTe<sub>2</sub> FETs.

Elucidating the Mechanism: MoTe2-Au Schottky Contact Change via Thermal Annealing. With the MoTe<sub>2</sub> channel region well encapsulated by h-BN and showing no measurable material variation, it is clear by now that the observed polarity switch from p- to n-type has been very consistent and robust, regardless of back gate or top gate, SiO<sub>2</sub>, or h-BN/SiO $_2$  substrate. We also find that the  $V_{\rm Min}$  values remain stable, indicating the Fermi level of the annealed MoTe<sub>2</sub> channel is still closer to the valence band than to the conduction band (thus still p-type channel material). Therefore, this consistent polarity switch in all types of encapsulated devices examined above collectively suggests that, instead of the insulators and substrates, it is the MoTe2-metal contact regions at S/D electrodes and their interplay with thermal annealing that are responsible for switching the polarity of device transport (p to n), as we systematically illustrate in

To visualize the p- to n-type polarity change process, we continuously measure the  $I_{\rm D}-V_{\rm G,top}$  characteristics at different annealing stages. Figure 5a shows the p-type characteristics of the as-fabricated pristine transistor. After 15 min thermal annealing, the p-type  $I_{\rm D}$  decreases by several orders of magnitude (Figure 5b). As thermal annealing continues, the transistor starts to exhibit n-type behavior. The data in Figure 5c (after 45 min thermal annealing) appear to be almost a "mirrored" n-type copy of that in Figure 5a (before annealing). With longer annealing, the n-type performance enhances moderately until the carrier concentration level reaches saturation.

All of the data and control experiments above suggest that the thermal annealing effects on the MoTe<sub>2</sub>-Au Schottky

contacts account for the observed polarity change. In fact, our earlier studies on Schottky contact MoS<sub>2</sub> FETs have also suggested that thermal annealing can modify TMDC—metal contacts by alloying or hybridization, thus changing the effective work function and Schottky barrier at the contacts. Here, we perform X-ray photoelectron spectroscopy (XPS) and Raman spectroscopy of MoTe<sub>2</sub> on Au before and after thermal annealing, as well as of MoTe<sub>2</sub> on SiO<sub>2</sub> as a reference. The MoTe<sub>2</sub> samples are fully encapsulated by thin h-BN flakes in both cases. Upon annealing, the XPS results (Supplementary Figure S7) exhibit distinct shifts of the Te 3d<sub>5/2</sub> peak for few-layer MoTe<sub>2</sub> on Au, whereas, in contrast, no shift of the Te 3d<sub>5/2</sub> peak is seen for MoTe<sub>2</sub> on SiO<sub>2</sub>. Raman spectroscopy results also show a clear shift of the MoTe<sub>2</sub> peak when 1L MoTe<sub>2</sub> is annealed on top of Au (Supplementary Figure S8).

As illustrated in Figure 5, upon thermal annealing, owing to the MoTe<sub>2</sub>-Au interaction, the Au-MoTe<sub>2</sub> composite exhibits lower work function compared to that of bare Au (Figure 5eh). From the carrier transport perspective, electronic characteristics of the MoTe<sub>2</sub> transistor during thermal annealing are explained using band diagrams in Figure 5i-l. We consider MoTe<sub>2</sub> as an intrinsically p-type material due to built-in Te excess, which dictates that the Fermi level  $(E_F)$  should be closer to the valence band. Before annealing, the Schottky barrier height for holes  $(\phi_{Bp})$  is lower than that for electrons  $(\phi_{Bn})$ . As a result, the Au–MoTe<sub>2</sub> contact has a lower contact resistance for hole transport, resulting in p-type transport behavior (Figure 5a,i). Figure 5j-l shows the band diagrams at  $V_{\rm GS} = 0$ ,  $V_{\rm GS} < 0$ , and  $V_{\rm GS} > 0$ , corresponding to the annealed conditions shown in Figure 5b-d. These indicate that work function reduction of the Au-MoTe2 composite corresponds to a  $\phi_{\mathrm{Bp}}$  increase with the annealing time. On the other hand, the Schottky barrier height for electrons,  $\phi_{\rm Bn} = E_{\rm g} - \phi_{\rm Bp}$ , decreases. When  $\phi_{\rm Bn} pprox \phi_{\rm Bp}$ , the device shows intrinsic-like I-Vcharacteristics (Figure 5b,j). When  $\phi_{\rm Bn}$  further decreases and becomes smaller, the contact resistance for electrons is much lower than that for holes. Therefore, the observed p- to n-type polarity change during thermal annealing is attributed to the work function reduction due to the Au-MoTe<sub>2</sub> composite, which lowers the contact resistance for electrons but increases the contact resistance for holes. Meanwhile,  $V_{\rm Min}$  values in Figure 5a,c,d do not shift noticeably after thermal annealing, which clearly indicates that intrinsic doping in the MoTe<sub>2</sub> channel material is not changed. Given this, we note that, for future technology considerations, when threshold voltage  $(V_T)$

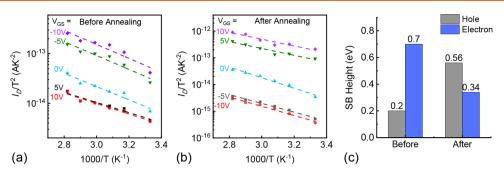

Figure 7. Extraction of Schottky barrier (SB) height for the h-BN/MoTe<sub>2</sub> FETs before and after thermal annealing.  $I_{\rm D}/T^2$  is plotted against 1000/T at different values of  $V_{\rm GS}$  in the device with Au contacts (a) before and (b) after thermal annealing. The dashed lines are fitting curves. (c) Comparison of the SB heights for electrons and holes before and after thermal annealing. SB height of electrons (holes) is extracted at the off state (thermionic emission limited transport) with  $V_{\rm GS}$  of 10 V (-10 V) from the slope of  $I_{\rm D}/T^2$  (in logarithm) versus 1/T plot.

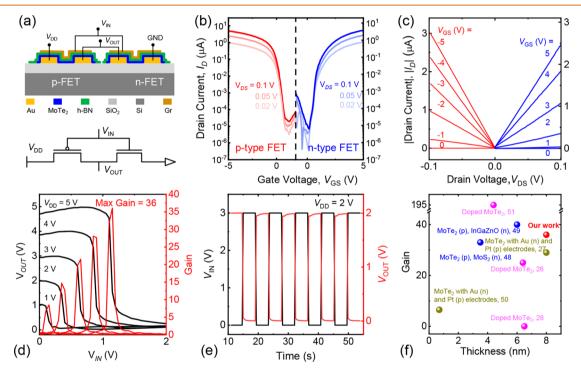

Figure 8. Monolithic MoTe<sub>2</sub> inverter utilizing the thermally controlled polarity change of the constitutive FETs. (a) Cross-sectional view of the MoTe<sub>2</sub> inverter and its circuit diagram. (b) Transfer characteristics  $(I_{\rm D}-V_{\rm GS})$  of the p-FET (curves on left) and n-FET (curves on right). (c) Output characteristics  $(I_{\rm D}-V_{\rm DS})$  of the p-FET (left) and n-FET (right). (d) Voltage transfer characteristics of the MoTe<sub>2</sub> inverter at varying supply voltage  $V_{\rm DD}=1$ , 2, 3, 4, and 5 V, showing almost ideal transition voltages. The right axis values indicate the voltage gain  $(g=-dV_{\rm OUT}/dV_{\rm IN})$ , which is as high as g=36 at  $V_{\rm DD}=5$  V. (e) Dynamic switching of the MoTe<sub>2</sub> inverter. (f) Benchmarking of this monolithic MoTe<sub>2</sub> inverter against reported heterogeneous inverters involving MoTe<sub>2</sub>.

tuning is desired, the present polarity control method should be combined with techniques or processes that can efficiently modify  $V_T$ .

Further Experimental Verification: Local Gate Device, Schottky Barrier Height Extraction. The modification of MoTe<sub>2</sub>—Au contacts by thermal annealing and its deterministic role on transport polarity change are further verified by control experiments on local gate devices that we have delicately made with meticulously prepared MoTe<sub>2</sub> and h-BN flakes, as shown in Figure 6a. The local gate (G) resides in the middle of the channel, and there is no overlap region, but there is distance (extension region) between the G and S/D electrodes. Its length is  $\sim 1/4$  of the channel length, as displayed in Figure 6a. The first and third electrodes from the left are used as S and D, and the second electrode is used as

bottom local gate G, on top of which is an h-BN layer as gate dielectric, and MoTe<sub>2</sub> is transferred on top of h-BN as channel material and then fully encapsulated by a top h-BN layer. The FET shows high-performance p-type characteristics before thermal annealing (Figure 6b). After thermal annealing, the device shows much degraded p-type behavior but not n-type characteristics. The lack of p- to n-type change here clearly indicates that it is not some mysterious doping mechanism in the channel region that is accounting for the p- to n-type polarity change. Instead, this control experiment again strongly confirms that the MoTe<sub>2</sub>—Au contacts play a key role in the polarity change. In fact, the mechanism illustrated in Figure 5 and Figure 6c very well explains the results from the local gate device, where after annealing Schottky barriers become high for holes, which blocks injection of holes into the channel from

S/D, hence the observed degradation in p-type behavior. Note here the extension regions in the local gate device remain p-type.

Furthermore, Figure 7 presents the  $I_{\rm D}-V_{\rm DS}$  characteristics of few-layer MoTe<sub>2</sub> FETs at different temperatures in range of ~293–355 K (~20–82 °C), which are lower than the annealing temperature for polarity change. SB heights for electrons/holes are extracted at the off state (thermionic emission limited transport) for p-FET (before annealing, Figure 7a) and n-FET (after annealing, Figure 7b) from the slope of  $I_{\rm D}/T^2$  (in logarithm) versus 1/T plot. Upon thermal annealing, the SB height for holes increases from 0.2 to 0.56 eV, and the SB height for electrons decreases from 0.7 to 0.34 eV (Figure 7c). These results clearly provide direct and deterministic evidence of modifying relative SB heights for electrons/holes by thermal annealing.

It is worth noting that the transistor polarity change from pto n-type is explained by simply modifying the Schottky barrier (SB) height through thermal annealing; it is fundamentally different from previously reported chemical doping. The mechanism of transistor polarity change also preserves the excellent electron and hole mobilities of h-BN/MoTe<sub>2</sub>/h-BN heterostructures. The benefit from the h-BN encapsulation is to maintain MoTe<sub>2</sub> crystal intact. With comparison to MoTe<sub>2</sub> FETs on SiO<sub>2</sub> substrates, the annealed h-BN-encapsulated MoTe<sub>2</sub> devices are free of hysteresis effects. It not only leads to an enhanced electron mobility but also features superior stability and robustness.

Monolithic Inverter Demonstration by Utilizing the Polarity Control via Annealing. Finally, we design and demonstrate high-performance monolithic complementary inverters by directly exploiting the polarity control elucidated above to enable both p-FET and n-FET in MoTe<sub>2</sub> (unlike other inverters that employ two different 2D materials for pand n-FET). Figure 8a shows the cross section of the Gr topgate MoTe2 inverter with h-BN encapsulation. The n-FET is realized by polarity change from an as-fabricated p-FET through thermal annealing; then another p-FET is added nearby on the same chip via the agile, deterministic all-dry stamp-transfer process for making 2D devices. Figure 8b depicts measured transfer characteristics of both FETs, featuring a high on/off current ratio of  $\sim 10^6$ . Figure 8c illustrates the linear  $I_D$ – $V_{DS}$  curves with varying gate voltage of 0 to -5 V for p-FET and 0 to 5 V for n-FET.

An inverter is a "NOT" logic gate that outputs the opposite logic level of its input. Clean inverter operation is observed in Figure 8d for switching between logic "1" ( $\sim V_{\rm DD}$ ) and logic "0" (0 V). When  $V_{\rm IN}$  is  $V_{\rm DD}$  (logic "1"), the n-FET is turned on, and  $V_{\rm OUT}$  decreases to near 0 (logic state "0"). When  $V_{\rm IN}$  is pulled down to zero (logic "0"),  $V_{\rm OUT}$  assumes  $V_{\rm DD}$  (logic "1"), indicative of the complete input/output signal inversion. The slope of transfer function in the middle transition region provides a measure of the small signal voltage gain (g = $-dV_{OUT}/dV_{IN}$ ), which presents the responsivity of  $V_{OUT}$ variation to the change in  $V_{\rm IN}$ . A high gain of g=36 is achieved under supply voltage  $V_{\rm DD}=5$  V (Figure 8d), validating this inverter can serve for 2D logic circuits. Another important figure-of-merit for an inverter is on its dynamic operations and cycling performance. This inverter is switched by a square voltage waveform  $(V_{\rm IN})$  applied to the gate, which causes the output voltage  $(V_{OUT})$  to oscillate synchronously with a phase difference of  $\pi$ , as shown in Figure 8e. Figure 8f illustrates the comparison and benchmarking of all known

inverters using MoTe<sub>2</sub>, where previously reported inverters have been realized by using different materials for p- and n-FETs, including MoTe<sub>2</sub>/MoS<sub>2</sub><sup>48</sup> or MoTe<sub>2</sub>/InGaZnO heterostructures, employing electrodes with different work functions, or aluminum modification. This demonstration of *monolithic* high-performance inverters solely using MoTe<sub>2</sub> as the channel material with p- and n-type controlled by simple thermal annealing modification of Schottky contacts provides possibilities toward rationally controlling polarity of arrays of devices to enable more complex logic functions and circuits, all in MoTe<sub>2</sub> with metal electrodes.

### **CONCLUSIONS**

In summary, we have developed a dopant-free transistor polarity control method by modifying Schottky barrier height via thermal annealing. We realize MoTe<sub>2</sub> FETs from p- to ntype conduction with measured electron mobility up to 52.4 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and on/off current ratio of  $I_{on}/I_{off} \sim 10^5$  or higher. The h-BN-encapsulated MoTe<sub>2</sub> FETs exhibit excellent stability and robustness, with versatile device configurations, manifesting the potential extension to other 2D semiconductors and contacting materials. The modification of Schottky barrier height for holes and electrons is derived from thermally induced work function variation. More generally, the contact engineering approach provides an alternative pathway to intentionally configure the transport polarity of Schottky contact FETs. Such nondestructive and dopant-free contact engineering techniques have enabled us to build highperformance all-MoTe<sub>2</sub> monolithic complementary logic circuits.

# **EXPERIMENTAL SECTION**

Device Fabrication. All MoTe, FETs are fabricated by exfoliating MoTe<sub>2</sub> flakes from 2H-MoTe<sub>2</sub> bulk crystal and then stamp-transferred onto a SiO<sub>2</sub>-on-Si substrate with prepattered source/drain (S/D) electrodes by employing an all-dry transfer method. 52 First, the electrodes are patterned and fabricated onto a Si wafer covered by 290 nm thick thermal oxide (SiO<sub>2</sub>) using photolithography and Au deposition. The substrates with S/D electrodes are cleaned in acetone and isopropyl alcohol using a sonicator and dried using a N2 gun. In the next step, a MoTe<sub>2</sub> flake with uniform thickness is transferred onto the SiO<sub>2</sub>-on-Si substrate or on earlier transferred h-BN layer. During transfer, it is necessary to keep a  $\sim 2-4^{\circ}$  anchor between the flake and the substrate in order not to trap bubbles in the interface between MoTe2 and the substrate. For the h-BN-encapsulated transistors, the second transfer step is conducted by exfoliating h-BN flakes from h-BN bulk crystal. The shape of the h-BN flake is carefully chosen in order to fully encapsulate the MoTe<sub>2</sub> flake. The thin graphite flakes are exfoliated from graphite bulk crystal. After all of the transfer processes, the devices are annealed at the temperature of 80–350  $^{\circ}$ C in N<sub>2</sub> gas (78 Torr) with a constant flow rate of 102.4 sccm. All 2D materials (MoTe<sub>2</sub>, h-BN, and graphene) are prepared by Scotch-tape exfoliation from high-quality single-crystal flakes onto PDMS stamps.

**Material Characterization.** Atomic force microscopy imaging is performed using an Agilent N9610A AFM in the tapping mode. Raman spectroscopy is performed using a customized micro-Raman system. Raman spectra of MoTe<sub>2</sub> flakes are measured in vacuum ( $\sim$ 10 mTorr) at room temperature using a 532 nm green laser. The laser power is  $\sim$ 100–200  $\mu$ W. EDS is measured using an XEDS and EBSD Oxford system (XMax 50 mm EDS, Nordlys high-resolution EBSD) that is integrated into the SEM system (Nova NanoLab 200).

**Electrical Measurement.** All measurements of the electronic characteristics are performed in the dark at room temperature using a semiconductor characterization system (Keithley 4200) and a customized probe station.

### ASSOCIATED CONTENT

# Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsnano.9b05502.

Figures of structure characterization (EDS, Raman, and XPS), performance of FETs (calibration of hysteresis, gate leakage, and cyclic testing), and control experiments (h-BN encapsulation and different contact metal) (PDF)

### **AUTHOR INFORMATION**

# **Corresponding Author**

Philip X.-L. Feng — Department of Electrical Engineering & Computer Science, Case School of Engineering, Case Western Reserve University, Cleveland, Ohio 44106, United States; Electrical & Computer Engineering, University of Florida, Gainesville, Florida 32611, United States; orcid.org/0000-0002-1083-2391; Email: philip.feng@ufl.edu

### **Authors**

Xia Liu — Department of Electrical Engineering & Computer Science, Case School of Engineering, Case Western Reserve University, Cleveland, Ohio 44106, United States; orcid.org/0000-0003-1886-6825

Arnob Islam — Department of Electrical Engineering & Computer Science, Case School of Engineering, Case Western Reserve University, Cleveland, Ohio 44106, United States; orcid.org/0000-0002-3931-1506

Jing Guo – Electrical & Computer Engineering, University of Florida, Gainesville, Florida 32611, United States

Complete contact information is available at: https://pubs.acs.org/10.1021/acsnano.9b05502

# Notes

The authors declare no competing financial interest.

## **ACKNOWLEDGMENTS**

We thank the National Science Foundation (NSF) through EPMD Awards (Grant Nos. ECCS-1810154, ECCS-2015670, and ECCS-1809770), CAREER Award (Grant No. ECCS-1454570 and ECCS-2015708), and the Wen H. Ko Fellowship for financial support. We also thank X.-Q. Zheng, J. Lee, H. Jia, and Y. Wang for technical support and helpful discussions.

# **REFERENCES**

- (1) Novoselov, K. S.; Mishchenko, A.; Carvalho, A.; Castro Neto, A. H. 2D Materials and van der Waals Heterostructures. *Science* **2016**, 353, aac9439.

- (2) Wang, F.; Wang, Z.; Jiang, C.; Yin, L.; Cheng, R.; Zhan, X.; Xu, K.; Wang, F.; Zhang, Y.; He, J. Progress on Electronic and Optoelectronic Devices of 2D Layered Semiconducting Materials. *Small* **2017**, *13*, 1604298.

- (3) Bhimanapati, G. R.; Lin, Z.; Meunier, V.; Jung, Y.; Cha, J.; Das, S.; Xiao, D.; Son, Y.; Strano, M. S.; Cooper, V. R.; Liang, L. B.; Louie, S. G.; Ringe, E.; Zhou, W.; Kim, S. S.; Naik, R. R.; Sumpter, B. G.; Terrones, H.; Xia, F. N.; Wang, Y. L.; et al. Recent Advances in Two-Dimensional Materials beyond Graphene. *ACS Nano* **2015**, *9*, 11509–11539.

- (4) Duerloo, K. N.; Li, Y.; Reed, E. J. Structural Phase Transitions in Two-Dimensional Mo- and W-Dichalcogenide Monolayers. *Nat. Commun.* **2014**, *5*, 4214.

- (5) Keum, D. H.; Cho, S.; Kim, J. H.; Choe, D.-H.; Sung, H.-J.; Kan, M.; Kang, H.; Hwang, J.-Y.; Kim, S. W.; Yang, H.; Chang, K. J.; Lee,

- Y. H. Bandgap Opening in Few-Layered Monoclinic MoTe<sub>2</sub>. Nat. Phys. **2015**, 11, 482–486.

- (6) Li, Y.; Duerloo, K. N.; Wauson, K.; Reed, E. J. Structural Semiconductor-to-Semimetal Phase Transition in Two-Dimensional Materials Induced by Electrostatic Gating. *Nat. Commun.* **2016**, *7*, 10671

- (7) Sung, J. H.; Heo, H.; Si, S.; Kim, Y. H.; Noh, H. R.; Song, K.; Kim, J.; Lee, C. S.; Seo, S. Y.; Kim, D. H.; Kim, H. K.; Yeom, H. W.; Kim, T. H.; Choi, S. Y.; Kim, J. S.; Jo, M. H. Coplanar Semiconductor-Metal Circuitry Defined on Few-Layer MoTe<sub>2</sub> via Polymorphic Heteroepitaxy. Nat. Nanotechnol. 2017, 12, 1064.

- (8) Ma, R.; Zhang, H.; Yoo, Y.; Degregorio, Z. P.; Jin, L.; Golani, P.; Ghasemi Azadani, J.; Low, T.; Johns, J. E.; Bendersky, L. A.; Davydov, A. V.; Koester, S. J. MoTe<sub>2</sub> Lateral Homojunction Field-Effect Transistors Fabricated Using Flux-Controlled Phase Engineering. *ACS Nano* **2019**, *13*, 8035–8046.

- (9) Zhang, X.; Jin, Z.; Wang, L.; Hachtel, J. A.; Villarreal, E.; Wang, Z.; Ha, T.; Nakanishi, Y.; Tiwary, C. S.; Lai, J.; Dong, L.; Yang, J.; Vajtai, R.; Ringe, E.; Idrobo, J. C.; Yakobson, B. I.; Lou, J.; Gambin, V.; Koltun, R.; Ajayan, P. M. Low Contact Barrier in 2H/1T′ MoTe<sub>2</sub> In-Plane Heterostructure Synthesized by Chemical Vapor Deposition. ACS Appl. Mater. Interfaces 2019, 11, 12777–12785.

- (10) Si, M. W.; Su, C. J.; Jiang, C. S.; Conrad, N. J.; Zhou, H.; Maize, K. D.; Qiu, G.; Wu, C. T.; Shakouri, A.; Alam, M. A.; Ye, P. D. Steep-Slope Hysteresis-Free Negative Capacitance MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* **2018**, *13*, 24–28.

- (11) Wuttig, M.; Yamada, N. Phase-Change Materials for Rewriteable Data Storage. *Nat. Mater.* **2007**, *6*, 824–832.

- (12) Roy, T.; Tosun, M.; Cao, X.; Fang, H.; Lien, D. H.; Zhao, P. D.; Chen, Y. Z.; Chueh, Y. L.; Guo, J.; Javey, A. Dual-Gated MoS<sub>2</sub>/WSe<sub>2</sub> van der Waals Tunnel Diodes and Transistors. *ACS Nano* **2015**, *9*, 2071–9.

- (13) Liu, X.; Qu, D.; Ryu, J.; Ahmed, F.; Yang, Z.; Lee, D.; Yoo, W. J. P-Type Polar Transition of Chemically Doped Multilayer MoS<sub>2</sub> Transistor. *Adv. Mater.* **2016**, *28*, 2345–2351.

- (14) Das, S.; Appenzeller, J. WSe<sub>2</sub> Field Effect Transistors with Enhanced Ambipolar Characteristics. *Appl. Phys. Lett.* **2013**, *103*, 103501.

- (15) Roy, A.; Movva, H. C. P.; Satpati, B.; Kim, K.; Dey, R.; Rai, A.; Pramanik, T.; Guchhait, S.; Tutuc, E.; Banerjee, S. K. Structural and Electrical Properties of MoTe<sub>2</sub> and MoSe<sub>2</sub> Grown by Molecular Beam Epitaxy. *ACS Appl. Mater. Interfaces* **2016**, *8*, 7396–7402.

- (16) Qi, Y.; Naumov, P. G.; Ali, M. N.; Rajamathi, C. R.; Schnelle, W.; Barkalov, O.; Hanfland, M.; Wu, S.-C.; Shekhar, C.; Sun, Y.; Suß, V.; Schmidt, M.; Schwarz, U.; Pippel, E.; Werner, P.; Hillebrand, R.; Forster, T.; Kampert, E.; Parkin, S.; Cava, R. J.; Felser, C.; Yan, B.; Medvedev, S. A.; et al. Superconductivity in Weyl Semimetal Candidate MoTe<sub>2</sub>. Nat. Commun. 2016, 7, 11038.

- (17) Deng, K.; Wan, G. L.; Deng, P.; Zhang, K. N.; Ding, S. J.; Wang, E. Y.; Yan, M. Z.; Huang, H. Q.; Zhang, H. Y.; Xu, Z. L.; Denlinger, J.; Fedorov, A.; Yang, H. T.; Duan, W. H.; Yao, H.; Wu, Y.; Fan, S. S.; Zhang, H. J.; Chen, X.; Zhou, S. Y. Experimental Observation of Topological Fermi Arcs in Type-II Weyl Semimetal MoTe<sub>2</sub>. Nat. Phys. **2016**, *12*, 1105–1110.

- (18) Yang, J.; Lu, T. Y.; Myint, Y. W.; Pei, J. J.; Macdonald, D.; Zheng, J. C.; Lu, Y. R. Robust Excitons and Trions in Monolayer MoTe<sub>2</sub>. ACS Nano 2015, 9, 6603-6609.

- (19) Huang, J. H.; Deng, K. Y.; Liu, P. S.; Wu, C. T.; Chou, C. T.; Chang, W. H.; Lee, Y. J.; Hou, T. H. Large-Area 2D Layered MoTe<sub>2</sub> by Physical Vapor Deposition and Solid-Phase Crystallization in a Tellurium-Free Atmosphere. *Adv. Mater. Interfaces* **2017**, *4*, 1700157.

- (20) Zhang, W.; Huang, Z.; Zhang, W.; Li, Y. Two Dimensional Semiconductors with Possible High Room Temperature Mobility. *Nano Res.* **2014**, *7*, 1731–1737.

- (21) Eftekhari, A. Tungsten Dichalcogenides (WS<sub>2</sub>, WSe<sub>2</sub>, and WTe<sub>2</sub>): Materials Chemistry and Applications. *J. Mater. Chem. A* **2017**, *5*, 18299–18325.

- (22) Hu, Z.; Wu, Z.; Han, C.; He, J.; Ni, Z.; Chen, W. Two-Dimensional Transition Metal Dichalcogenides: Interface and Defect Engineering. *Chem. Soc. Rev.* **2018**, *47*, 3100–3128.

- (23) Gong, Y. J.; Yuan, H. T.; Wu, C. L.; Tang, P. Z.; Yang, S. Z.; Yang, A. K.; Li, G. D.; Liu, B. F.; van de Groep, J.; Brongersma, M. L.; Chisholm, M. F.; Zhang, S. C.; Zhou, W.; Cui, Y. Spatially Controlled Doping of Two-Dimensional SnS<sub>2</sub> through Intercalation for Electronics. *Nat. Nanotechnol.* **2018**, *13*, 294–299.

- (24) Lim, J. Y.; Pezeshki, A.; Oh, S.; Kim, J. S.; Lee, Y. T.; Yu, S.; Hwang, D. K.; Lee, G. H.; Choi, H. J.; Im, S. Homogeneous 2D MoTe<sub>2</sub> *p-n* Junctions and CMOS Inverters Formed by Atomic-Layer-Deposition-Induced Doping. *Adv. Mater.* **2017**, *29*, 1701798.

- (25) Zhang, X.; Shao, Z.; Zhang, X.; He, Y.; Jie, J. Surface Charge Transfer Doping of Low-Dimensional Nanostructures toward High-Performance Nanodevices. *Adv. Mater.* **2016**, *28*, 10409–10442.

- (26) Luo, W.; Zhu, M.; Peng, G.; Zheng, X.; Miao, F.; Bai, S.; Zhang, X.-A.; Qin, S. Carrier Modulation of Ambipolar Few-Layer MoTe<sub>2</sub> Transistors by MgO Surface Charge Transfer Doping. *Adv. Funct. Mater.* **2018**, 28, 1704539.

- (27) Wu, E.; Xie, Y.; Zhang, J.; Zhang, H.; Hu, X.; Liu, J.; Zhou, C.; Zhang, D. Dynamically Controllable Polarity Modulation of MoTe<sub>2</sub> Field-Effect Transistors through Ultraviolet Light and Electrostatic Activation. *Sci. Adv.* **2019**, *5*, No. eaav3430.

- (28) Chang, Y. M.; Yang, S. H.; Lin, C. Y.; Chen, C. H.; Lien, C. H.; Jian, W. B.; Ueno, K.; Suen, Y. W.; Tsukagoshi, K.; Lin, Y. F. Reversible and Precisely Controllable *p/n*-Type Doping of MoTe<sub>2</sub> Transistors through Electrothermal Doping. *Adv. Mater.* **2018**, *30*, 1706995.

- (29) Stier, A. V.; Wilson, N. P.; Clark, G.; Xu, X.; Crooker, S. A. Probing the Influence of Dielectric Environment on Excitons in Monolayer WSe<sub>2</sub>: Insight from High Magnetic Fields. *Nano Lett.* **2016**, *16*, 7054–7060.

- (30) Ye, F.; Lee, J.; Hu, J.; Mao, Z.; Wei, J.; Feng, P. X.-L. Environmental Instability and Degradation of Single- and Few-Layer WTe<sub>2</sub> Nanosheets in Ambient Conditions. *Small* **2016**, *12*, 5802–5808

- (31) Dolui, K.; Rungger, I.; Sanvito, S. Origin of the *n*-Type and *p*-Type Conductivity of MoS<sub>2</sub> Monolayers on a SiO<sub>2</sub> Substrate. *Phys. Rev. B: Condens. Matter Mater. Phys.* **2013**, 87, 165402.

- (32) Chen, B.; Sahin, H.; Suslu, A.; Ding, L.; Bertoni, M. I.; Peeters, F. M.; Tongay, S. Environmental Changes in MoTe<sub>2</sub> Excitonic Dynamics by Defects-Activated Molecular Interaction. *ACS Nano* **2015**, *9*, 5326–5332.

- (33) Hansen, W. N.; Johnson, K. B. Work Function Measurements in Gas Ambient. Surf. Sci. 1994, 316, 373–382.

- (34) Helander, M. G.; Greiner, M. T.; Wang, Z. B.; Lu, Z. H. Pitfalls in Measuring Work Function Using Photoelectron Spectroscopy. *Appl. Surf. Sci.* **2010**, 256, 2602–2605.

- (35) Nakaharai, S.; Yamamoto, M.; Ueno, K.; Tsukagoshi, K. Carrier Polarity Control in  $\alpha$ -MoTe<sub>2</sub> Schottky Junctions Based on Weak Fermi-Level Pinning. *ACS Appl. Mater. Interfaces* **2016**, *8*, 14732–14739

- (36) Ruppert, C.; Aslan, O. B.; Heinz, T. F. Optical Properties and Band Gap of Single- and Few-Layer MoTe<sub>2</sub> Crystals. *Nano Lett.* **2014**, *14*, *6231–6*.

- (37) Lin, Y. F.; Xu, Y.; Wang, S. T.; Li, S. L.; Yamamoto, M.; Aparecido-Ferreira, A.; Li, W. W.; Sun, H. B.; Nakaharai, S.; Jian, W. B.; Ueno, K.; Tsukagoshi, K. Ambipolar MoTe<sub>2</sub> Transistors and Their Applications in Logic Circuits. *Adv. Mater.* **2014**, *26*, 3263.

- (38) Zhou, L.; Xu, K.; Zubair, A.; Liao, A. D.; Fang, W. J.; Ouyang, F. P.; Lee, Y. H.; Ueno, K.; Saito, R.; Palacios, T.; Kong, J.; Dresselhaus, M. S. Large-Area Synthesis of High-Quality Uniform Few-Layer MoTe<sub>2</sub>. J. Am. Chem. Soc. **2015**, 137, 11892–5.

- (39) Yang, L.; Zhang, W.; Li, J.; Cheng, S.; Xie, Z.; Chang, H. Tellurization Velocity-Dependent Metallic–Semiconducting–Metallic Phase Evolution in Chemical Vapor Deposition Growth of Large-Area, Few-Layer MoTe<sub>2</sub>. ACS Nano **2017**, 11, 1964–1972.

- (40) Zhu, H.; Wang, Q.; Cheng, L.; Addou, R.; Kim, J.; Kim, M. J.; Wallace, R. M. Defects and Surface Structural Stability of MoTe<sub>2</sub> under Vacuum Annealing. *ACS Nano* **2017**, *11*, 11005–11014.

- (41) Qu, D. S.; Liu, X. C.; Huang, M.; Lee, C.; Ahmed, F.; Kim, H.; Ruoff, R. S.; Hone, J.; Yoo, W. J. Carrier-Type Modulation and Mobility Improvement of Thin MoTe<sub>2</sub>. *Adv. Mater.* **2017**, 29, 1606433.

- (42) Cho, S.; Kim, S.; Kim, J. H.; Zhao, J.; Seok, J.; Keum, D. H.; Baik, J.; Choe, D. H.; Chang, K. J.; Suenaga, K.; Kim, S. W.; Lee, Y. H.; Yang, H. Phase Patterning for Ohmic Homojunction Contact in MoTe<sub>2</sub>. Science **2015**, 349, 625–628.

- (43) Lezama, I. G.; Ubaldini, A.; Longobardi, M.; Giannini, E.; Renner, C.; Kuzmenko, A. B.; Morpurgo, A. F. Surface Transport and Band Gap Structure of Exfoliated 2H-MoTe<sub>2</sub> Crystals. 2D Mater. **2014**, *1*, 021002.

- (44) Wang, Z.; Wang, F.; Yin, L.; Huang, Y.; Xu, K.; Wang, F.; Zhan, X.; He, J. Electrostatically Tunable Lateral MoTe<sub>2</sub> p—n Junction for Use in High-Performance Optoelectronics. *Nanoscale* **2016**, *8*, 13245–13250.

- (45) Ji, H.; Joo, M.-K.; Yi, H.; Choi, H.; Gul, H. Z.; Ghimire, M. K.; Lim, S. C. Tunable Mobility in Double-Gated MoTe<sub>2</sub> Field-Effect Transistor: Effect of Coulomb Screening and Trap Sites. *ACS Appl. Mater. Interfaces* **2017**, *9*, 29185–29192.

- (46) Chen, J. C.; Feng, Z. H.; Fan, S. Q.; Shi, S.; Yue, Y. C.; Shen, W. F.; Xie, Y.; Wu, E. X.; Sun, C. L.; Liu, J.; Zhang, H.; Pang, W.; Sun, D.; Feng, W.; Feng, Y. Y.; Wu, S.; Zhang, D. H. Contact Engineering of Molybdenum Ditelluride Field Effect Transistors through Rapid Thermal Annealing. ACS Appl. Mater. Interfaces 2017, 9, 30107—30114.

- (47) Islam, A.; Lee, J.; Feng, P. X.-L. All-Dry Transferred Single- and Few-Layer MoS<sub>2</sub> Field Effect Transistors with Enhanced Performance by Thermal Annealing. *J. Appl. Phys.* **2018**, *123*, 025701.

- (48) Pezeshki, A.; Hosseini Shokouh, S. H.; Jeon, P. J.; Shackery, I.; Kim, J. S.; Oh, I.-K.; Jun, S. C.; Kim, H.; Im, S. Static and Dynamic Performance of Complementary Inverters Based on Nanosheet  $\alpha$ -MoTe<sub>2</sub> p-Channel and MoS<sub>2</sub> n-Channel Transistors. *ACS Nano* **2016**, 10, 1118–1125.

- (49) Lee, H. S.; Choi, K.; Kim, J. S.; Yu, S.; Ko, K. R.; Im, S. Coupling Two-Dimensional MoTe<sub>2</sub> and InGaZnO Thin-Film Materials for Hybrid pn Junction and CMOS Inverters. ACS Appl. Mater. Interfaces 2017, 9, 15592–15598.

- (50) Larentis, S.; Fallahazad, B.; Movva, H. C. P.; Kim, K.; Rai, A.; Taniguchi, T.; Watanabe, K.; Banerjee, S. K.; Tutuc, E. Reconfigurable Complementary Monolayer MoTe<sub>2</sub> Field-Effect Transistors for Integrated Circuits. *ACS Nano* **2017**, *11*, 4832–4839.

- (51) Qi, D.; Han, C.; Rong, X.; Zhang, X.-W.; Chhowalla, M.; Wee, A. T. S.; Zhang, W. Continuously Tuning Electronic Properties of Few-Layer Molybdenum Ditelluride with *In Situ* Aluminum Modification toward Ultrahigh Gain Complementary Inverters. *ACS Nano* **2019**, *13*, 9464–9472.

- (52) Yang, R.; Zheng, X. Q.; Wang, Z.; Miller, C. J.; Feng, P. X.-L. Multilayer MoS<sub>2</sub> Transistors Enabled by a Facile Dry-Transfer Technique and Thermal Annealing. J. Vac. Sci. Technol., B: Nanotechnol. Microelectron.: Mater., Process., Meas., Phenom. 2014, 32, 061203.