# A 30-GHz CMOS SOI Outphasing Power Amplifier With Current Mode Combining for High Backoff Efficiency and Constant Envelope Operation

Kang Ning<sup>✉</sup>, Student Member, IEEE, Yihao Fang, Navid Hosseinzadeh, Student Member, IEEE, and James F. Buckwalter<sup>✉</sup>, Senior Member, IEEE

**Abstract**—High peak and average efficiency is an important feature of power amplifiers (PAs) for 5G millimeter-wave communication. This article reviews the challenges of conventional outphasing approaches in CMOS technologies and demonstrates a low-loss outphasing combiner for low loadline impedance. Undesirable characteristics of CMOS devices for outphasing are compensated with neutralization, unilaterization, and stabilization networks for the outphasing PA (OPA). The OPA is realized in 45-nm CMOS silicon on insulator (SOI) and demonstrates 40% 6-dB backoff drain efficiency (DE) while providing 17-dBm peak output power with a peak 50.5% DE. For 64-QAM, a 31.3% average DE and 10.1-dBm average output power are measured. The OPA demonstrates less than 1.5% error vector magnitude (EVM) with 64-QAM waveform using a phase-based lookup table (LUT). With 16-QAM, the bit rate reaches 20 Gb/s with 12% EVM. To the best of our knowledge, this is the highest bit rate for a high-efficiency PA. The adjacent channel leakage ratio (ACLR) is under  $-25$  dBc.

**Index Terms**—5G, Chireix power combiner, millimeter wave (mm-wave), outphasing power amplifier (OPA), power amplifier (PA), silicon on insulator (SOI) CMOS.

## I. INTRODUCTION

THE emerging focus on fifth-generation (5G) wireless communication is developing millimeter-wave (mm-wave) technology compatible with silicon-based CMOS process technologies. Transmitters designed for the 28-GHz band will support cyclic-prefix orthogonal frequency-division multiple access (CP-OFDMA) and QAM waveforms, potentially with multiple beams, pushing requirements on high peak-to-average power ratio (PAPR) above 10 dB. Additionally, high rates up to 20 Gb/s are proposed over 2-GHz channel bands, but ACLR is relaxed to  $-17$  dBc compared to earlier 4G LTE [1]. A key research challenge is to demonstrate CMOS power amplifiers (PAs) at 28 GHz with higher average efficiency at 6- or 10-dB output backoff (OBO) power levels. [2]–[8].

Manuscript received April 5, 2019; revised July 17, 2019 and September 13, 2019; accepted October 13, 2019. Date of publication November 8, 2019; date of current version April 23, 2020. This article was approved by Associate Editor Waleed Khalil. This work was supported in part by the National Science Foundation (NSF) through the GigaNets Program under Award 1518812 and in part by the NSF SPECEES Program under Award 1824495. (Corresponding author: Kang Ning.)

The authors are with the Department of Electrical and Computer Engineering, University of California at Santa Barbara, Santa Barbara, CA 93106 USA (e-mail: kangning@ucsb.edu).

Color versions of one or more of the figures in this article are available online at <http://ieeexplore.ieee.org>.

Digital Object Identifier 10.1109/JSSC.2019.2949255

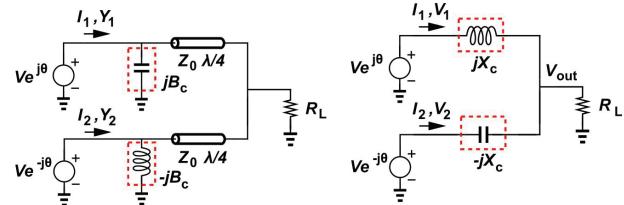

Fig. 1. Conventional OPA with voltage-mode PAs and voltage-mode power combiner (left) and proposed OPA with voltage-mode PAs and current-mode power combiner (right).

To address high PAPR, conventional approaches for mm-wave PAs include envelope tracking, Doherty, and OPAs [9], while popular for RF bands, the efficiency of supply modulators drops rapidly at gigahertz envelope bandwidths, resulting in low average efficiency and difficulty in operating with arrays [10]–[12]. Load modulation techniques, including Doherty and outphasing, are promising but are also confronted by significant challenges when realized with silicon CMOS processes. Several Doherty PAs have been proposed recently to provide OBO drain efficiency (DE) ( $\eta$ ) improvement but require significant analog or digital predistortion (DPD) and lossy power combiners [13]–[19]. DPD becomes difficult to realize in beamformers when per-element observation is required to correct for gain variation. Recent work [20] has shown that calibrating the outphasing signals is energy efficient and practical since it requires timing precision at baseband.

Outphasing power amplifiers (OPAs), on the other hand, tend to suffer from lossy power combiners but have the advantage of using constant envelope signaling. The outphasing PA operates in class-B at mm-wave bands to realize the highest gain, and a conventional Chireix power combiner requires two quarter-wavelength transmission lines in the power combiner, as shown in Fig. 1. In [21], a triaxial balun is proposed as the outphasing combiner using a sub-quarter-wavelength balun [22] to reduce the combiner loss to around 0.5 dB. However, this low-loss triaxial balun design is not easily realized in the CMOS processes due to the proximity of the metal layers to the ground and the lower loadline impedance of the CMOS device. Series combiners have been proposed at RF bands [23]–[25]. Here, we demonstrate an mm-wave series combiner as shown in Fig. 1 to improve the class-B waveform behavior over OBO conditions with lower loss. While earlier work on

OPAs required non-constant amplitude and outphasing angle variation for high efficiency [26]–[28], we demonstrate that the current-mode combiner allows true constant envelope signals to realize high average efficiency.

This article proposes a low-loss current-mode power combiner for the OPA appropriate for the characteristics of a silicon CMOS process. Section II reviews the conventional Chireix OPA and details of the limitations in mm-wave bands. In Section III, a current-mode combiner is presented and the impact of parasitics that strongly degrade CMOS PAs at mm-wave bands, particularly  $C_{gd}$  and  $C_{ds}$ , on  $\eta$  at OBO levels are detailed. Section IV describes the mm-wave PA circuit-level simulations, including neutralization, unilateralization, and stabilization techniques to improve the average efficiency. Finally, we demonstrate true constant envelope waveform generation and linearization to realize low error vector magnitude (EVM) with high-order QAM at 30 GHz and compare to the state of the art in Section V.

## II. OUTPHASING POWER COMBINERS

Chireix introduced the OPA in 1935 and recent work has shown that this approach can be adapted to mm-wave bands [29]. In the conventional OPA, a complex RF signal is decomposed into two constant envelope signals that are separated by an outphasing angle  $\theta$ , while the common-mode phase of the two signals is the phase modulation  $\phi$ .

As shown in Fig. 1, two voltage-mode outphasing signals  $Ve^{j\theta}$  and  $Ve^{-j\theta}$  are combined through two  $\lambda/4$  transmission lines with characteristic impedance  $Z_0$ . The output power varies with the outphasing angle  $\theta$ , and the admittances seen at the output of the amplifiers ( $k = 1$  and 2) are

$$Y_k = \frac{I_k}{V_k} = \frac{2 \cos^2 \theta}{R'_L} \mp j \frac{\sin 2\theta}{R'_L} = G_0 \mp j B_0 \quad (1)$$

where  $R'_L = (Z_0^2/R_L)$ . The RF output power and DC power consumed at the drain of each PA are

$$P_{RF,k} = \frac{1}{2} \operatorname{Re}(V_k^* Y_k^* V_k) = \frac{1}{2} |V_k|^2 G_0 \quad (2a)$$

$$P_{DC,k} = I_{DC,k} V_{DC} = \frac{2}{\pi} |V_k^* Y_k^* V_k| = \frac{2}{\pi} |V_k|^2 |Y| \quad (2b)$$

where the maximum amplitude  $|V_k|$  is  $V_{DC}$  based on class-B PA output voltage waveform assumption and ignoring the knee voltage. We note that  $P_{RF}$  is proportional to  $G_0$  and  $P_{DC}$  is proportional to  $(G_0^2 + B_0^2)^{1/2}$ . Therefore, the DE of the PA is

$$\eta_{VM} = \frac{P_{RF}}{P_{DC}} = \frac{\pi}{4} \frac{G_0}{\sqrt{G_0^2 + B_0^2}}. \quad (3)$$

The OPA  $\eta$  reaches a maximum class-B peak efficiency (78%) when the susceptance is zero.

To control the range over which the OPA  $\eta$  is high under backoff conditions, the compensating susceptance  $\pm B_C$  is introduced in the conventional Chireix power combiner as shown in Fig. 1 to drop  $P_{DC}$  more quickly than the output power  $P_{RF}$ . The admittance seen looking into the two paths becomes

$$Y_k = G_0 \mp j(B_0 - B_C). \quad (4)$$

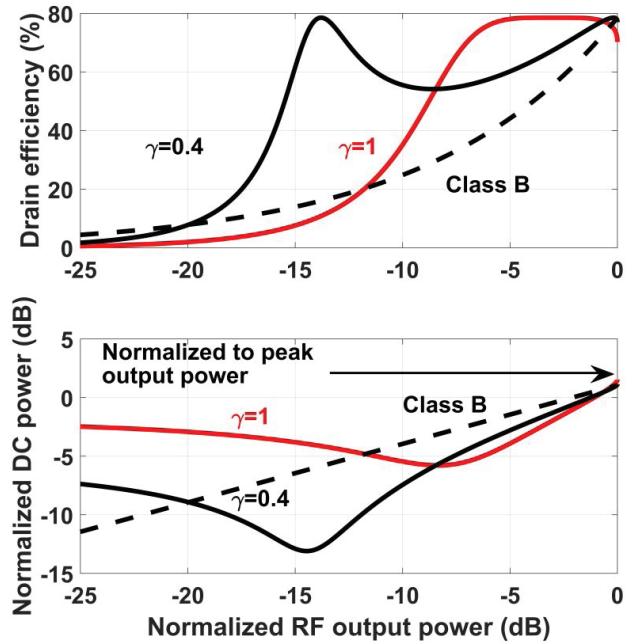

Fig. 2. Conventional DE and DC power consumption for OBO power levels.

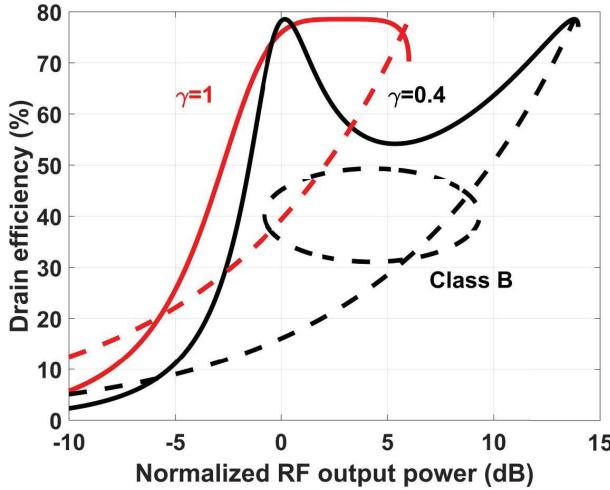

In the presence of  $\pm B_C$ ,  $P_{DC}$  drops as shown in Fig. 2 as  $\eta$  under OBO is improved. Based on the choice of  $B_C$ ,  $\eta$  peaks at different backoff power levels. If  $B_C = \gamma B_0$ ,  $\eta$  for voltage-mode sources is expressed as

$$\eta_{VM} = \frac{P_{RF}}{P_{DC}} = \frac{\pi}{4} \frac{G_0}{\sqrt{G_0^2 + B_0^2(1 - \gamma)^2}}. \quad (5)$$

A key insight into the operation of the Chireix combiner is that the DC power is controlled to improve efficiency under OBO conditions, while in Doherty amplifiers, the delivered output power is controlled by the auxiliary amplifier. As shown in Fig. 2, the minimum  $P_{DC}$  occurs at lower  $P_{RF}$  and the smaller coefficient ( $\gamma = 0.4$ ) provides more DC power reduction.

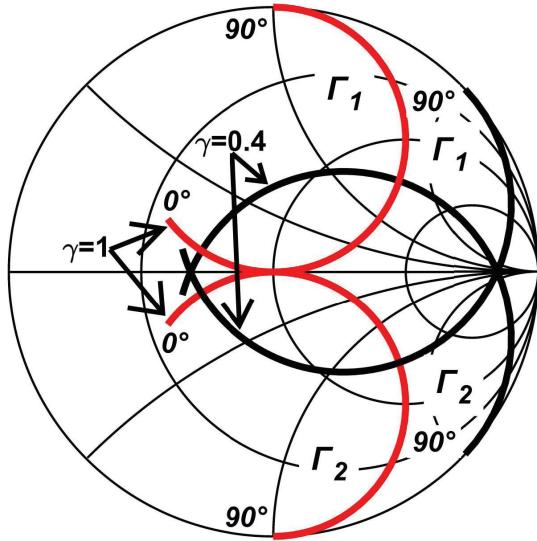

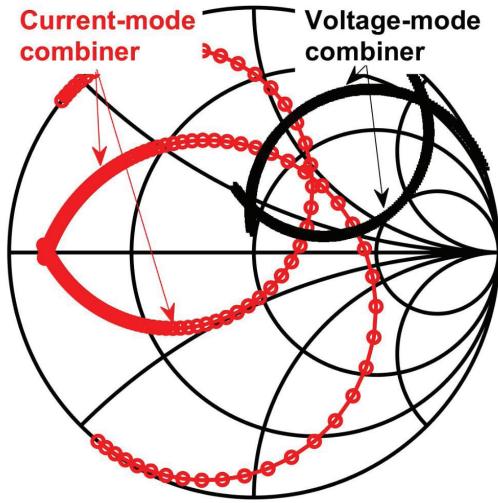

The reflection coefficients seen at the output of the PAs in the presence of  $B_C$  are shown in Fig. 3 as a function of outphasing angle. The real part of the impedance changes from 25 to 500  $\Omega$  limiting the output power and efficiency that are achievable in CMOS technology.

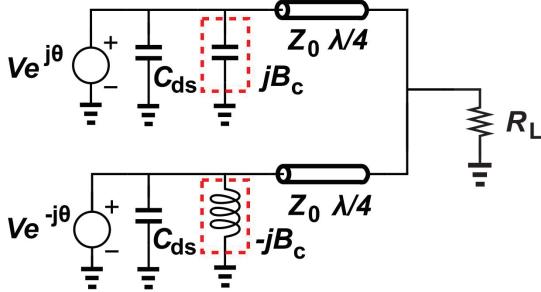

Unfortunately, other factors also limit the conventional Chireix combiner in mm-wave frequency bands. The intrinsic transistor parasitics, such as  $C_{ds}$  and  $C_{gd}$  shown in Fig. 4, impact the PA efficiency in mm-wave bands by shifting the desired loadline impedance.

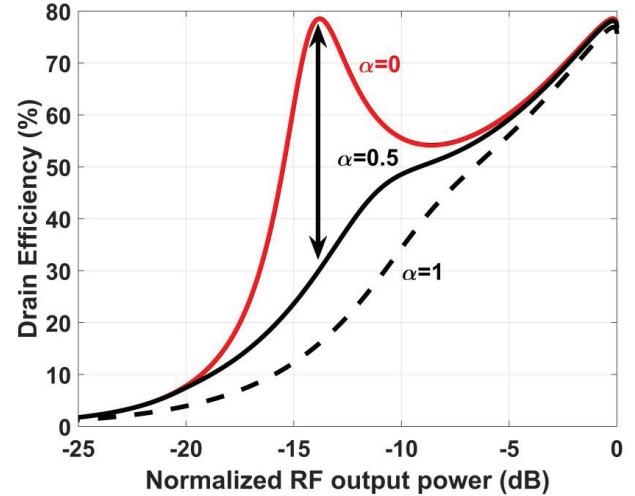

If the PA includes a significant output capacitance comprising  $C_{ds}$  and  $C_{gd}$ , the contribution of the output capacitance is defined by  $\alpha B_0 = \omega C_{out}$ , and the efficiency becomes

$$\eta_{VM} = \frac{\pi}{2} \frac{1}{\sqrt{1 + \frac{B_0^2}{G_0^2}(1 - \gamma - \alpha)^2} + \sqrt{1 + \frac{B_0^2}{G_0^2}(1 - \gamma + \alpha)^2}}. \quad (6)$$

Fig. 3. Smith chart illustrating the reflection for Chireix combiner for different values of  $\gamma$  with sweeping the outphasing angle from  $0^\circ$  to  $90^\circ$ .

Fig. 4. Role of transistor output capacitance in Chireix combiner.

If we choose  $Z_0 = 50 \Omega$  and  $\gamma = 0.4$  at 30 GHz for the Chireix combiner, the combiner is compensated with a capacitor of 42 fF. In a 45-nm CMOS process, a transistor that is capable of delivering a peak power of 16 dBm has a  $C_{ds}$  of around 50 fF. While some of the output capacitance can be incorporated into the Chireix compensation capacitance, Fig. 5 shows that 20 fF causes  $\eta$  to drop to 56% from 78% peak at the 6-dB OBO power. At this point, the advantage over a class-B PA is greatly diminished.

Since  $C_{gd}$  changes the phase between the output voltage and current waveforms, it also tends to contribute to a degradation in gain and efficiency under OBO conditions. The voltage difference between the gate and drain changes with outphasing angle, and the current between the gate and drain,  $I_{gd}$ , also changes, causing the output drain voltage to overlap the drain current and the efficiency drops [30], [31].

Additionally,  $C_{gd}$  varies the transistor output capacitance making it difficult to absorb the output capacitance into the Chireix combiner. Small-signal intuition suggests that the feedback capacitance generates a gain-dependent output capacitance,  $C_{out} = C_{ds} + (1 + (1/A_v))C_{gd}$ . This is close to  $C_{gd}$  if the voltage gain  $A_v$  is high, but the gain is limited in mm-wave bands and changes with  $\theta$ . Therefore, the impact of  $C_{gd}$  is to produce a contribution to  $\alpha$  from (6) that changes with  $\theta$ .

Fig. 5. Efficiency drops under backoff conditions for  $\alpha = 0$  ( $C_{out} = 0$ ),  $\alpha = 0.5$  ( $C_{out} = 21$  fF), and  $\alpha = 1$  ( $C_{out} = 42$  fF) when  $\gamma = 0.4$ .

For this reason, unilaterization techniques, such as cross-coupled capacitors, offer limited efficiency improvement under OBO conditions for mm-wave OPAs [32].

### III. HYBRID-MODE OUTPHASING POWER COMBINING

The previous discussion presented the limitations of a Chireix outphasing power combining in mm-wave bands. Fundamentally, the Chireix combiner is presented as a voltage-mode combiner, driven with two voltage sources. Earlier work at RF bands explores the approach shown in Fig. 1 and combines the features of a voltage-mode PA with a current-mode power combiner [23]–[25]. Here, we investigate the hybrid-mode operation by considering a series (current mode) combining with a voltage-mode PA. To maintain constant envelope signaling, the condition for the hybrid-mode outphasing operation satisfies

$$V_{out} - V e^{\pm j\theta} = \mp j X_C I_{1,2}. \quad (7)$$

Solving for  $I_1$ ,  $I_2$ , and  $V_{out}$ , the output voltage is

$$V_{out} = 2V \frac{R_L}{X_C} \sin \theta. \quad (8)$$

Now, the output voltage depends on the compensation reactance  $X_C$  and is suitable for CMOS PAs where low loadline impedance is typical for high output power. The output currents are

$$I_k = V \frac{\sin \theta}{X_C} \mp j V \left( \frac{\cos \theta}{X_C} - \frac{2R_L \sin \theta}{X_C^2} \right). \quad (9)$$

The admittance seen looking into the combiner is

$$Y_k = \frac{I_k}{V_k} = 2 \sin^2 \theta \frac{X_C^2}{R_L} \mp j \left( \frac{1}{X_C} - \sin 2\theta \frac{X_C^2}{R_L} \right). \quad (10)$$

Therefore, the RF output power and DC power consumption are

$$P_{RF} = \frac{1}{2} |V|^2 \operatorname{Re}\{Y_1^*\} = |V|^2 \sin^2 \theta \frac{R_L}{X_C^2} \quad (11a)$$

Fig. 6. DE for the current-mode combiner for different compensation coefficients. The plot is normalized for the minimum  $P_{DC}$ .

and

$$P_{DC} = \frac{2}{\pi} |V|^2 \frac{R_L}{X_C^2} \sqrt{(2 \sin^2 \theta)^2 + \left( \frac{X_C}{R_L} - \sin 2\theta \right)^2}. \quad (11b)$$

Consequently, the current-mode OPA output power exhibits different backoff characteristics when compared with the voltage-mode Chireix OPA. Comparing (2a) with (11b) demonstrates that the RF power is now modulated by the outphasing angle and the output power from current-mode OPA is related to the compensation component  $X_C$ .  $\eta_H$  is given by

$$\eta_H = \frac{\pi}{2} \frac{\sin^2 \theta}{\sqrt{4 \sin^4 \theta + \left( \sin 2\theta - \frac{X_C}{R_L} \right)^2}}. \quad (12)$$

The peak efficiency is controlled by the ratio  $(X_C/R_L)$ , and when this ratio equals to  $\sin 2\theta$ , it provides the same efficiency curve as (5); however, the output power is also related to  $X_C$ . Smaller  $X_C$  reaches higher peak output power, as shown in Fig. 6. For instance, the peak efficiency at 14-dB OBO occurs when  $\theta = 80$  for  $\gamma = 0.4$ . As in voltage-mode power combiner topology,  $\gamma = 1$  presents resistance between the two paths.  $\gamma = 0.4$  suggests that the reactances are partially compensated by the series inductor and capacitor.

Most notably, the benefit of the current-mode combiner is shown in Fig. 7. The impedances that are required for high average efficiency are shifted to much lower loadlines that are compatible with CMOS devices.

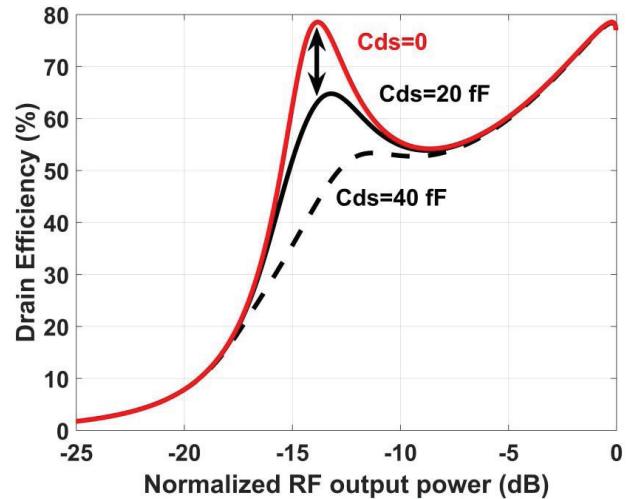

When we review the role of  $C_{out}$  in the current-mode combiner, the DE illustrates less sensitivity to the role of parasitic shunt capacitance as we observed for the Chireix combiner. For  $C_{ds}$  of 20 fF, the OBO efficiency peak drops only 10% and still offers significant advantages compared with a Chireix combiner shown in Fig. 5. Since it obviates the need for quarter-wave transmission lines as shown in Fig. 1, a lower loss combiner may also be possible and will be investigated in Section IV.

Fig. 7. Smith chart illustrating the impedance variation seen at the output of the two PAs for the current-mode combiner.

Fig. 8. Efficiency degradation across backoff conditions for  $C_{ds} = 0$ ,  $C_{ds} = 20$  fF, and  $C_{ds} = 40$  fF for hybrid power combiner for  $\gamma$  of 0.4.

To compare the voltage- and current-mode Chireix combiners, we plot the change in the load impedance presented to the outphasing PAs in the presence of a 40-fF output capacitance, e.g.,  $C_{ds}$ , in Figs. 8 and 9. This variation is anticipated to be the result of process and modeling variation. Notably, the current-mode combiner impedance is shifted only slightly with respect to the ideal curves shown in Fig. 7. On the other hand, the voltage-mode combiner impedance is rotated substantially compared to Fig. 3 and results in much lower efficiency relative to the optimal loadline matching. The impedance shift causes the efficiency to drop at back off, as illustrated in Figs. 5 and 8. From this simulation, we find that the current-mode combiner is more robust to output capacitance changes.

#### IV. 28-GHz SILICON ON INSULATOR (SOI) CMOS OUTPHASING PA DESIGN

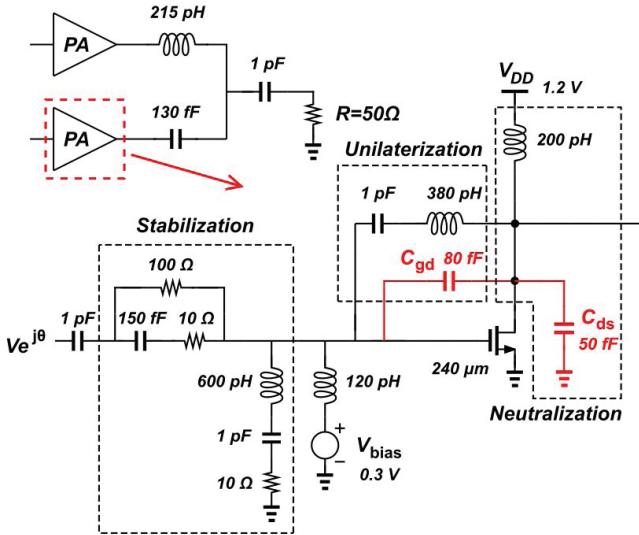

The schematic of the proposed hybrid-mode OPA is shown in Fig. 10, where each PA consists of a single common-source

Fig. 9. Impedance variation with 40-fF  $C_{ds}$  in voltage-and current-mode power combiner.

Fig. 10. Schematic of the proposed OPA with the neutralization, unilateralization, and stabilization networks.

NMOS FET (NFET) biased in class B. The OPA is designed in GlobalFoundries 45RF SOI CMOS process and includes a pair of identical PA stages combined with the described current-mode power combiner. A 240- $\mu\text{m}$ -wide NFET produces a load-line impedance close to 25  $\Omega$  when delivering 15 dBm of output power. Because the PA loadline is small relative to 50  $\Omega$ , the real part of the load impedance seen in the two paths ranges from 25 to 50  $\Omega$ .

#### A. PA Design

The PA circuit design consists of three key design components to realize high average efficiency: a neutralization network to compensate the reactance of  $C_{ds}$  that degrades backoff efficiency, a unilateralization network to minimize the current feedback through  $C_{gd}$  to improve load modulation, and a stabilization network to compensate the impact of

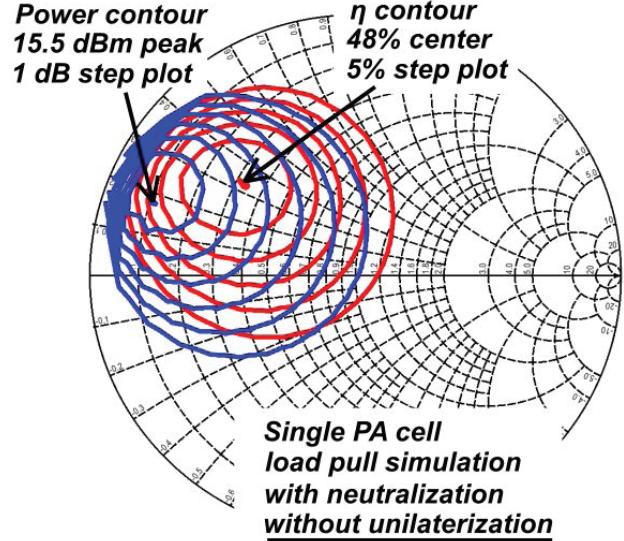

Fig. 11. Load-pull simulation of PA cell without unilaterization.

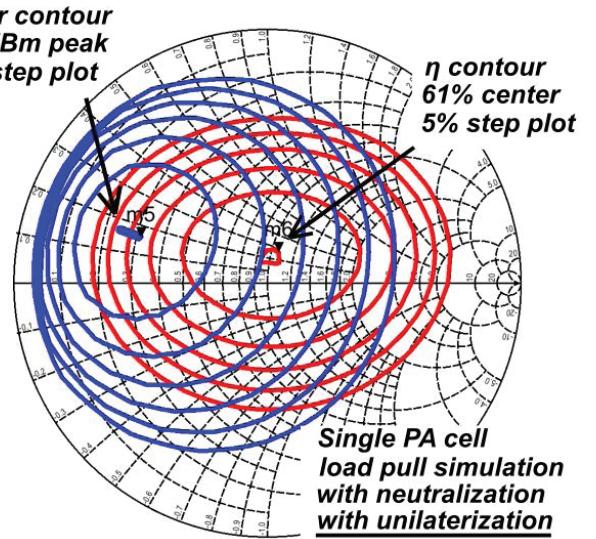

Fig. 12. Load-pull simulation of PA cell with unilaterization.

the unilateralization and neutralization networks on the PA stability.

The load inductor is chosen to neutralize all the parasitic capacitance on drain node, including  $C_{ds}$ , parasitic capacitance from power combiner, and inductor load. A 200-pH inductor is used to resonate with the output capacitance of the 240- $\mu\text{m}$  transistor. The NFET is unilateralized with a 380-pH inductor in series with a 1-pF DC blocking capacitor connected between the gate and drain to resonate out  $C_{gd}$  near 28 GHz. It should be noted that this network provides a feedback path at low frequency, near 6 GHz and impacts the circuit stability at lower frequencies.

Figs. 11 and 12 show the benefit of the neutralization and unilateralization networks for compensating  $C_{ds}$  and  $C_{gd}$ . Without unilateralization, the peak DE is 48% and the peak power is 15.5 dBm. Furthermore,  $\eta$  drops to 24% at the 6-dB OBO, half of its the peak value eliminating any advantage to outphasing relative to a class-B PA.

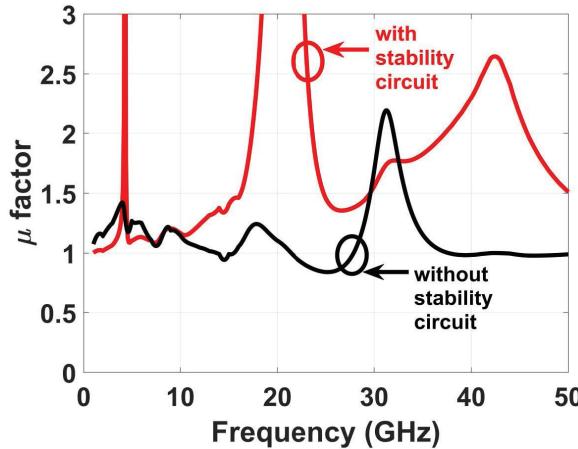

Fig. 13. Simulated  $\mu$  factor of a single PA cell with and without the input high-pass network.

With the  $C_{gd}$  unilateralization, the peak  $\eta$  increases to 61%, while the output power drops to 14.5 dBm. Now,  $\eta$  drops to 51% at 6-dB OBO, significantly higher than half of its peak value (30%).

The introduction of the unilateralization network introduces conditional stability at other frequencies. A shunt low-frequency trap is designed at the gate using a 600-pH inductor in series with a 1-pF capacitor and a 10- $\Omega$  resistor to provide low impedance near 6 GHz and marked as stabilization in Fig. 10 [33]. Fig. 13 shows the source stability factor over a broadband with the low-frequency trap. Notably, the PA is not unconditionally stable below 28 GHz. To further improve the stability of the PA cell, a high-pass circuit input network reduces the reflection at the gate to ensure that a single PA cell is unconditionally stable. The  $\mu$  factor of each PA is shown to be unconditionally stable in Fig. 13.

### B. Combiner Design

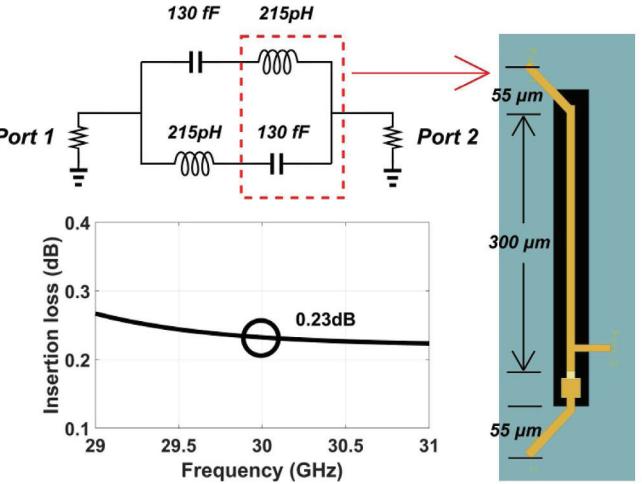

The choice of the series reactance,  $X_C$ , in the current combiner provides different OBO power ranges. The compensation coefficient,  $\gamma = 0.4$ , is chosen based on producing a real part of the impedance seen into the two paths that are in the range of 25–50  $\Omega$ . Based on  $X_C = \gamma X_0$ , a 215-pH series inductor and a 130-fF series capacitor are added on the two paths.

The inductor uses a 4- $\mu$ m-thick, 10- $\mu$ m-wide metal to improve the quality factor ( $Q$ ). The process offers a high- $Q$  ( $>100$ ) MIM capacitor for the combiner. The capacitor has been simulated with EM software EMX to verify the quality factor. The current combiner is simulated with a back-to-back configuration as shown in Fig. 14 and indicates that the total loss of the power combiner is 0.23 dB at 30 GHz. The layout of the current combiner is shown aside in the plot and illustrates the compact implementation of the outphasing combiner.

### C. Dependence on VSWR

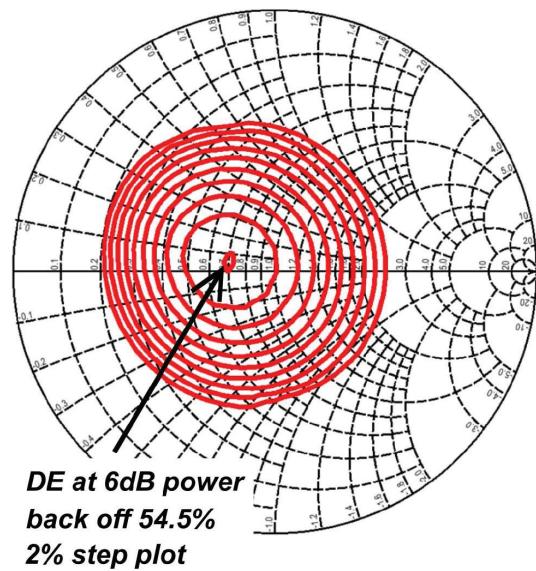

To investigate the sensitivity of the hybrid-mode OPA to load variations at the antenna, the output of the OPA was subjected to load pull at the output to assess the DE degradation at 6-dB OBO. As plotted in Fig. 15, the simulated  $\eta$  plots 2%

Fig. 14. Simulated insertion loss of the outphasing power combiner.

Fig. 15. Simulated  $\eta$  contour at 6-dB OBO from the peak output power ( $\theta = 20^\circ$ ).

contour drops in the efficiency for different load impedances. While  $\eta$  peaks at 54.5% around 35  $\Omega$ ,  $\eta$  reduces to 52.5% for load resistances between 25 and 50  $\Omega$ .

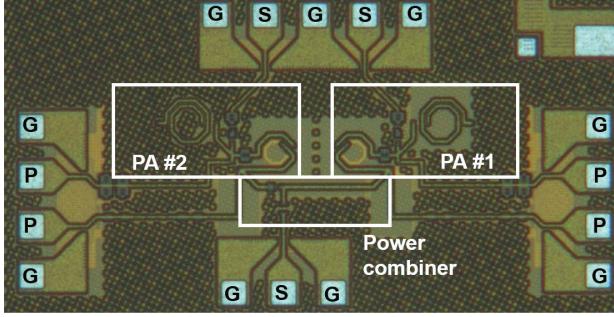

## V. OUTPHASING PA MEASUREMENT

Fig. 16 shows the chip microphotograph of the proposed OPA implemented in the GlobalFoundries 45-nm CMOS SOI process. The chip size is 920  $\mu$ m  $\times$  1790  $\mu$ m, including bondpads. The PAs are supplied with a 1.2-V voltage supply, and the gates are biased at 0.3 V for class-B operation.

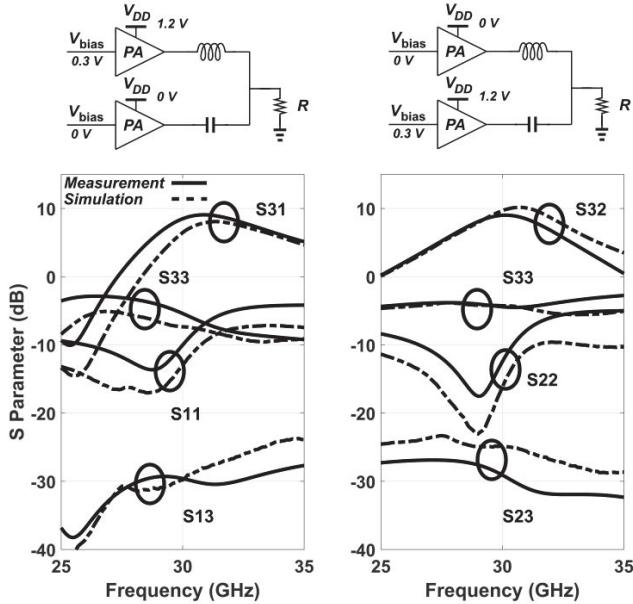

### A. Small-Signal Characterization

Since the outphasing PA is a three-port network with two input ports and a single output port, the measured S-parameters are compared to simulated S-parameters by sequentially measuring each PA. The measured results in Fig. 17 match the

Fig. 16. Micrograph of the hybrid-mode OPA chip.

Fig. 17. Measured S-parameters for a single PA cell compared to simulations.

simulation results accurately. Under these conditions, the PAs are unconditionally stable and simulated single PA  $\mu$  factor is plotted in Fig. 13.

### B. CW Power Measurement

The phase to each of the OPA inputs is calibrated and de-skewed to ensure that the input signals have the correct outphasing angle. Two signals generated by the AWG are shorted from input to output probe separately and compared to an 8-GHz reference generated from the AWG to calibrate the phase mismatch. After calibration, the phase mismatch from the AWG to the input probe is calculated and compensated in the output waveform of the AWG. In continuous-wave (CW) measurements for  $\eta$  and power added efficiency (PAE), the output probe connects to the power meter.

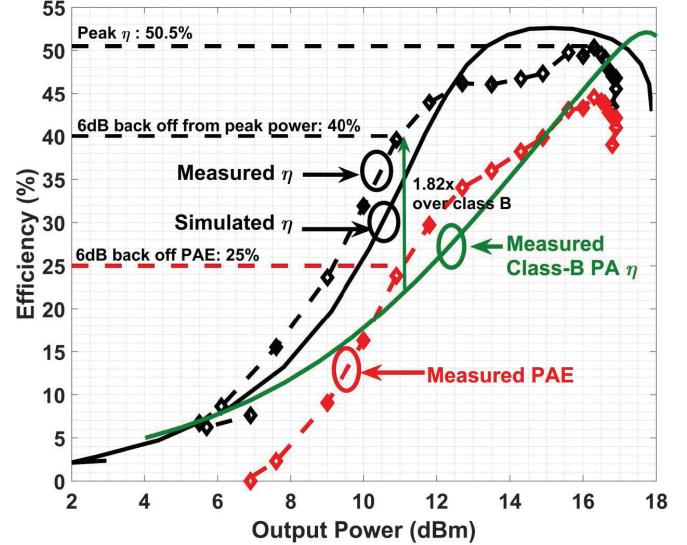

The outphasing angle  $\theta$  is swept and the output power is recorded. As shown in Fig. 18, the measured peak output power of outphasing PA is 17 dBm at 30 GHz with 50.5% peak  $\eta$ . The peak PAE is 45% at 16.2-dBm output power. At 6-dB OBO,  $\eta$  is 40%, while PAE is 25%. The simulated voltage-mode PA with voltage-mode power combiner has a similar peak  $\eta$  but at 6-dB OBO, the  $\eta$  drops

Fig. 18. Measured efficiency result comparing with simulation.

Fig. 19. Measurement setup.

to 32%, much lower than  $\eta$  presented in current-mode power combiner. However, to the best of our knowledge, this is the highest efficiency at 6-dB OBO for a CMOS PA in this band. We attribute some  $\eta$  degradation to the VSWR of the power meter (1.4), which presents a 50- $\Omega$  measurement plane at the output of the OPA.

We compare the DE of the OPA to a neutralized class-B PA from our previous work [31] where the PA has 18-dBm peak output power with  $-28$ -dBc adjacent channel power ratio (ACPR), which is close to the OPA in terms of output power and linearity. The 6-dB OBO DE is less than 25% and is around 15% lower than the DE for the measured OPA.

### C. Memoryless Outphasing AM-AM/AM-PM Compensation

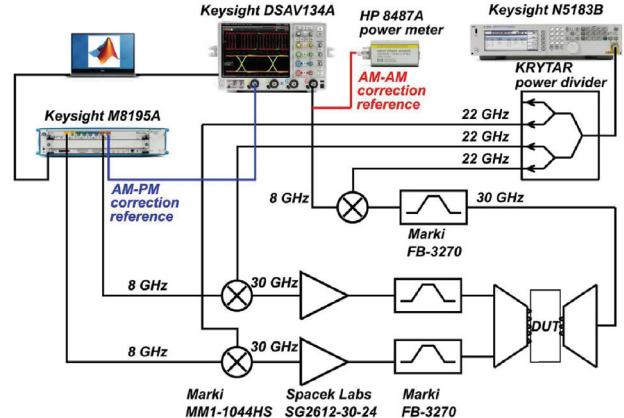

The chip is measured on wafer using the test setup shown in Fig. 19 to characterize the outphasing performance. The signal generation and phase calibration are performed offline in MATLAB, and a waveform is downloaded to a Keysight M8195A AWG as a pair of constant envelope IF outphasing signals at 8 GHz. The IF signals are upconverted to

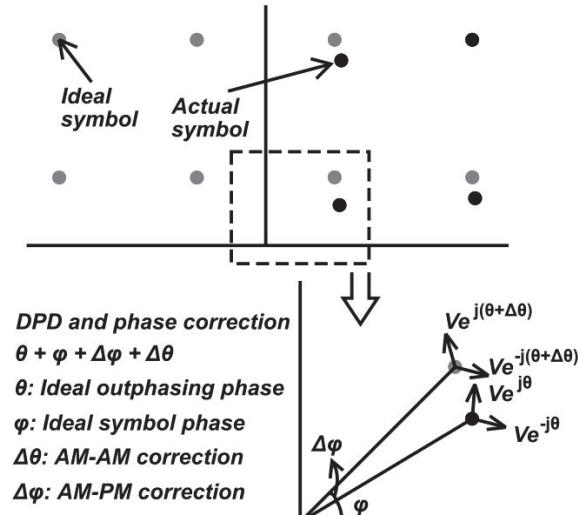

Fig. 20. Theory of phase-only DPD.

Fig. 21. PM-AM and PM-PM measured error for calibration and predistortion.

30 GHz with a Marki MM1-1044HS mixer. Two Spacek Labs SG2612-30-24 predrivers are used to amplify 30-GHz RF band signals for large-signal compression measurements, and a Marki FB-3270 bandpass filter is used to filter out the 14-GHz image tone. For modulated signal measurements, the output of the OPA is down-converted back to 8 GHz and demodulated by Keysight Oscilloscope DSAV134A.

One of the significant results in this mm-wave OPA is linearization of the PA with a memoryless lookup table (LUT). This greatly reduces the need for intensive digital signal processing power consumption to implement DPD. While prior outphasing work [34] used a combination of amplitude and phase predistortion to linearize the OPA,

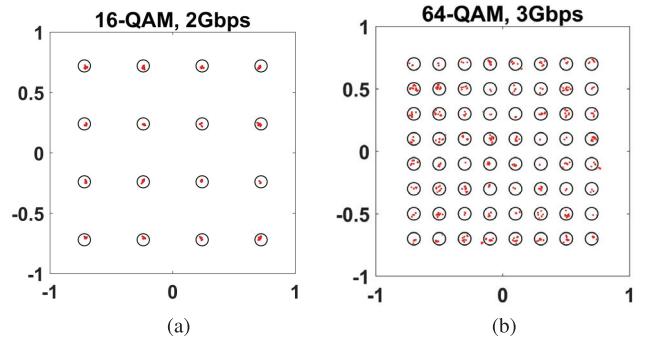

Fig. 22. Constellation plot for different QAMs. (a) Constellation plot for 16-QAM. (b) Constellation plot for 64-QAM.

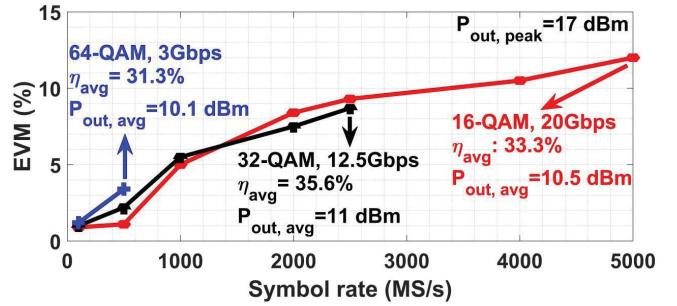

Fig. 23. EVM measurement for different QAM signals at different data rates.

this is an undesirable feature for outphasing, which should be predistorted solely through phase compensation.

As shown in Fig. 20, each QAM symbol is resolved into two outphasing signals where the two signals have common phase  $\phi$  and outphasing phase  $\theta$ .

Unequal amplitude from two paths of the PA and power combiner causes the actual symbols to have some mismatch with respect to the ideal symbols. In OPAs, the output power is controlled by  $\theta$  such that both amplitude modulation (AM-AM) is adjusted through the outphasing angle, while the phase modulation (AM-PM) is adjusted through a common-mode phase signal. Therefore, both amplitude and phase calibration are performed solely by phase. Fig. 20 shows that the AM mismatch could be compensated by AM-PM outphasing phase correction  $\Delta\theta$  and the PM mismatch could be compensated by PM-PM common phase correction  $\Delta\phi$ .

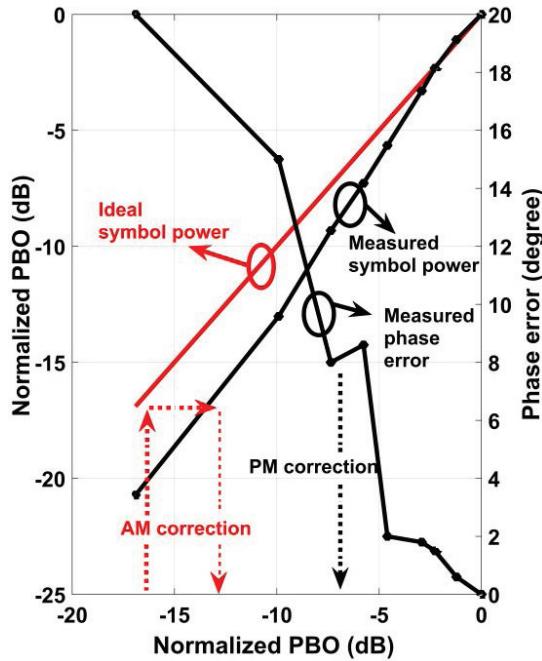

The measured AM-AM and AM-PM behavior is shown in Fig. 21. The calibration is normalized to the maximum output power of the outphasing PA to calibrate amplitude and phase, and each deviation is stored in an LUT.

#### D. QAM Measurements

Fig. 22 plots the 16-QAM and 64-QAM constellations at 500 MS/s. In both cases, the constellation exhibits low EVM. At 100 MS/s, the rms EVM is measured to be under 1.5% for 16/32/64-QAM waveforms. Fig. 23 shows a comparison of the EVM for different QAM waveforms at different symbol rates using only the memoryless LUT described previously. In all EVM measurements, the peak power symbol is set to the peak output power (17 dBm) to demonstrate the linearity

TABLE I

COMPARISON OF THIS WORK WITH STATE OF THE ART

|                        | [32]       | [21]       | [26]       | [13]       | This Work  |       |       |                             |

|------------------------|------------|------------|------------|------------|------------|-------|-------|-----------------------------|

| Technology             | 40nm CMOS  | 130nm SiGe | 45nm SOI   | 130nm SiGe | 45nm SOI   |       |       |                             |

| Architecture           | Outphasing | Outphasing | Outphasing | Doherty    | Outphasing |       |       |                             |

| Supply (V)             | 1          | 4          | 1          | 1.5        |            | 1.2   |       |                             |

| Frequency (GHz)        | 59.5-67    | 28         | 25.5-30    | 23.3-39.7  |            | 30    |       |                             |

| Gain (dB)              | 26         | 14         | -          | 18.2       |            | 7     |       |                             |

| $P_{sat}$ (dBm)        | 15.6       | 23         | 17.1       | 16.8       |            | 17    |       |                             |

| Peak $\eta$ (%)        | 25*        | 43         | 56         | 29.4       |            | 50.5  |       |                             |

| $\eta$ @6dB PBO        | 9*         | 35         | 38         | 25.4       |            | 40    |       |                             |

| Modulation             | QPSK       | 8PSK       | 64QAM OFDM | 64QAM      | 64QAM      | 16QAM | 32QAM | 64QAM                       |

| Data Rate (Gb/s)       | 3.52       | -          | 0.48       | 6          | 15         | 3     | 0.4 2 | 0.6 3                       |

| EVM (dB)               | -34        | -35        | -30.5      | -29.7      | -27.5      | -27   | -26.6 | -41 -36 -38 -28.4 -36.4 -28 |

| $P_{avg}$ (dBm)        | 10.8       | 11         | 14.3       | 10.7       | 10.4       | 9.2   | 7.2   | 10.5                        |

| $\eta$ @ $P_{avg}$ (%) | -          | -          | 25.3       | 36         | 34         | 18.5  | 14.4  | 33.3 35.6 31.2              |

| Area ( $mm^2$ )        | 0.96       | 0.56       | -          |            | 1.76       |       | 1.65  |                             |

\* for PAE instead of  $\eta$

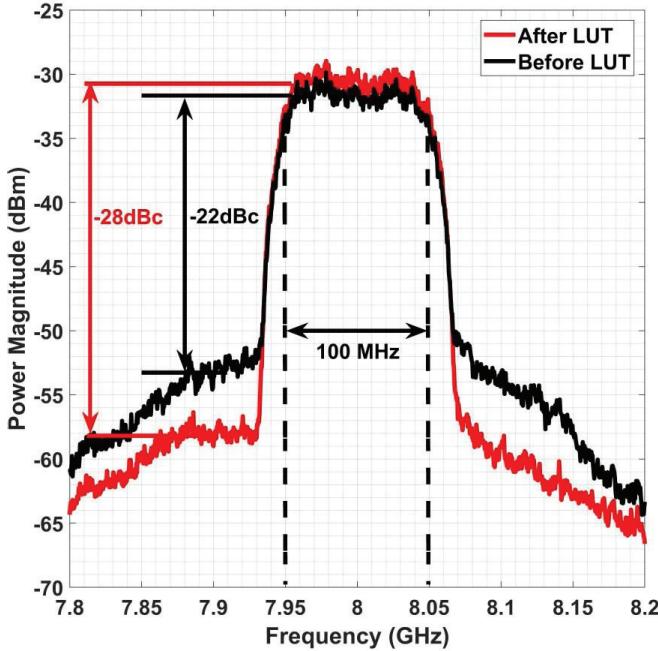

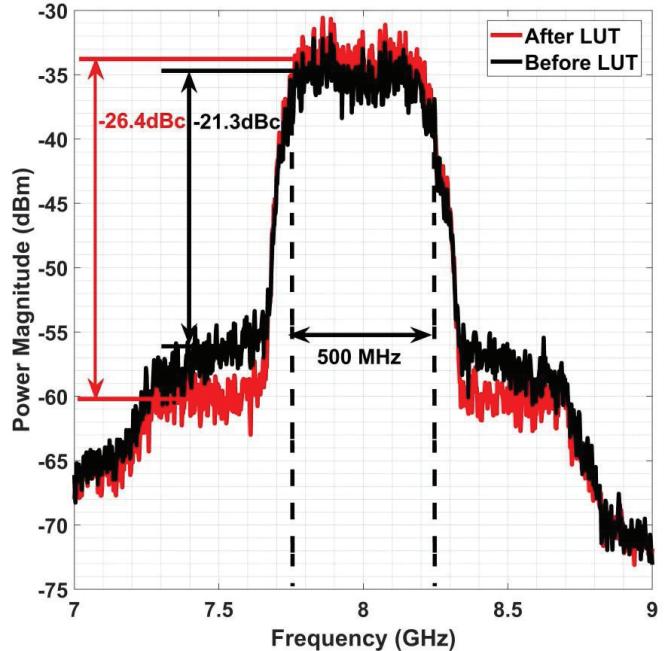

Fig. 24. ACPR of QAM-64 with 100-MHz signal.

Fig. 25. ACPR of QAM-64 with 500-MHz signal.

under the highest efficiency. The average efficiency  $\eta_{avg}$  for 64-QAM signal at 3-Gb/s data speed is 31.3% with 10.1-dBm average output power. At 16-QAM modulation, the EVM is 12% with a record data speed of 20 Gb/s with 10.5-dBm output power. To the best of our knowledge, this is the first CMOS PA at *Ka*-band to achieve 20-Gb/s modulated data speed, which is expected by 5G peak data rate.

Figs. 24 and 25 show the ACPR for 64-QAM signal at 100- and 500-MS/s sample rates with and without the phase-only memoryless LUT. The ACPR has 6- and 5-dB improvement after compensation at 100- and 500-MS/s sample speed, respectively, without introducing substantial increased demands in the DAC bandwidth. In this measurement, outphasing angle is controlled by AWG at baseband and the resolution of the outphasing angle directly contributes to the nonlinearity in the outphasing transmitter. In [35] and [36], the DAC resolution directly impacts the ACPR and,

in particular, a -40-dB ACLR demands slightly more than 40-dB AM dynamic range. This dynamic range relates to the phase resolution requirement larger than 8 bits.

Table I compares the measured performance of the presented OPA comparing to the state of the art. The presented hybrid-mode OPA achieves the highest OBO efficiency compared to earlier work as well as the lowest EVM and highest peak data rate.

## VI. CONCLUSION

This article presents a hybrid-mode OPA that is designed to achieve the highest efficiency in a CMOS process. The hybrid mode realizes a compact, low-loss current-mode power combiner to avoid high losses under backoff power conditions. The CMOS PA design considers the importance of transistor parasitics on load modulation and demonstrates a combination of unilaterization, neutralization, and stabilization to realize a

high-efficiency OPA. The demonstrated OPA achieves a peak  $\eta$  of 50.5% and a 6-dB OBO  $\eta$  of 40% all while operating with true constant envelope input signals. Finally, we demonstrate a memoryless LUT to compensate AM-AM and AM-PM variation of each symbol and demonstrate less than 1.5% EVM at 100-MS/s sample speed. For a 16-QAM signal, the PA achieves highest 20-Gb/s data rate as expected for 5G peak data rate.

#### ACKNOWLEDGMENT

The authors would like to thank the continued support of GlobalFoundries for providing access to 45RFSOI and Integrand providing for access to EMX software.

#### REFERENCES

- [1] *IMT Vision—Framework and Overall Objectives of the Future Development of IMT for 2020 and Beyond*, Standard ITU-R M.2083-0, Sep. 2015.

- [2] T. Li, M. Huang, and H. Wang, “A continuous-mode harmonically tuned 19-to-29.5 GHz ultra-linear PA supporting 18 Gb/s at 18.4% modulation PAE and 43.5% peak PAE,” in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 410–412.

- [3] J. S. Park, Y. Wang, S. Pellerano, C. Hull, and H. Wang, “A CMOS wideband current-mode digital polar power amplifier with built-in AM-PM distortion self-compensation,” *IEEE J. Solid-State Circuits*, vol. 53, no. 2, pp. 340–356, Feb. 2018.

- [4] T.-W. Li and H. Wang, “A continuous-mode 23.5-41 GHz hybrid class-F/F-1 power amplifier with 46% peak PAE for 5G massive MIMO applications,” in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2018, pp. 220–230.

- [5] J. A. Jayamon, J. F. Buckwalter, and P. M. Asbeck, “Multigate-cell stacked FET design for millimeter-wave CMOS power amplifiers,” *IEEE J. Solid-State Circuits*, vol. 51, no. 9, pp. 2027–2039, Sep. 2016.

- [6] J. F. Buckwalter, S. Daneshgar, J. Jayamon, and P. Asbeck, “Series power combining: Enabling techniques for Si/SiGe millimeter-wave power amplifiers,” in *Proc. IEEE 16th Top. Meeting Silicon Monolithic Integr. Circuits RF Syst. (SiRF)*, Jan. 2016, pp. 116–119.

- [7] B. Hanafi, O. Gürbüz, H. Dabag, J. F. Buckwalter, G. Rebeiz, and P. Asbeck, “Q-band spatially combined power amplifier arrays in 45-nm CMOS SOI,” *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 6, pp. 1937–1950, Jun. 2015.

- [8] J. A. Jayamon, J. F. Buckwalter, and P. M. Asbeck, “28 GHz>250 mW CMOS power amplifier using multigate-cell design,” in *Proc. IEEE Compound Semiconductor Integr. Circuit Symp. (CSICS)*, Oct. 2015, pp. 1–4.

- [9] H. Wang, S. Kousai, K. Onizuka, and S. Hu, “The wireless workhorse: Mixed-signal power amplifiers leverage digital and analog techniques to enhance large-signal RF operations,” *IEEE Microw. Mag.*, vol. 16, no. 9, pp. 36–63, Oct. 2015.

- [10] S. Hu, S. Kousai, and H. Wang, “A broadband CMOS digital power amplifier with hybrid class-G Doherty efficiency enhancement,” in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2015, pp. 1–3.

- [11] V. Vorapipat, C. S. Levy, and P. M. Asbeck, “A class-G voltage-mode Doherty power amplifier,” *IEEE J. Solid-State Circuits*, vol. 52, no. 12, pp. 3348–3360, Dec. 2017.

- [12] P. Asbeck and Z. Popovic, “ET comes of age: Envelope tracking for higher-efficiency power amplifiers,” *IEEE Microw. Mag.*, vol. 17, no. 3, pp. 16–25, Mar. 2016.

- [13] S. Hu, F. Wang, and H. Wang, “A 28 GHz/37 GHz/39 GHz multiband linear Doherty power amplifier for 5G massive MIMO applications,” in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 32–33.

- [14] H. Wang *et al.*, “Towards energy-efficient 5G mm-Wave links: Exploiting broadband mm-Wave Doherty power amplifier and multi-feed antenna with direct on-antenna power combining,” in *Proc. IEEE Bipolar/BiCMOS Circuits Technol. Meeting*, Oct. 2017, pp. 30–37.

- [15] S. Hu, S. Kousai, J. S. Park, O. L. Chlieh, and H. Wang, “Design of a transformer-based reconfigurable digital polar Doherty power amplifier fully integrated in bulk CMOS,” *IEEE J. Solid-State Circuits*, vol. 50, no. 5, pp. 1094–1106, May 2015.

- [16] N. Rostomyan, M. Özen, and P. Asbeck, “28 GHz Doherty power amplifier in CMOS SOI with 28% back-Off PAE,” *IEEE Microw. Compon. Lett.*, vol. 28, no. 5, pp. 446–448, May 2018.

- [17] N. Rostomyan, J. A. Jayamon, and P. M. Asbeck, “15 GHz Doherty power amplifier with RF predistortion linearizer in CMOS SOI,” *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 3, pp. 1339–1348, Mar. 2018.

- [18] V. Vorapipat, C. S. Levy, and P. M. Asbeck, “Voltage mode Doherty power amplifier,” *IEEE J. Solid-State Circuits*, vol. 52, no. 5, pp. 1295–1304, May 2017.

- [19] H. T. Nguyen, T. Chi, S. Li, and H. Wang, “A 62-to-68 GHz linear 6 Gb/s 64 QAM CMOS doherty radiator with 27.5%/20.1% PAE at peak/6 dB-back-off output power leveraging high-efficiency multi-feed antenna-based active load modulation,” in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 402–404.

- [20] M. Kosunen *et al.*, “A 0.35-to-2.6 GHz multilevel outphasing transmitter with a digital interpolating phase modulator enabling up to 400 MHz instantaneous bandwidth,” in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 224–225.

- [21] B. Rabet and J. Buckwalter, “A high-efficiency 28 GHz outphasing PA with 23 dBm output power using a triaxial balun combiner,” in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 174–176.

- [22] H.-C. Park, S. Daneshgar, Z. Griffith, M. Urteaga, B.-S. Kim, and M. Rodwell, “Millimeter-wave series power combining using sub-quarter-wavelength baluns,” *IEEE J. Solid-State Circuits*, vol. 49, no. 10, pp. 2089–2102, Oct. 2014.

- [23] T. W. Barton and D. J. Perreault, “Four-way microstrip-based power combining for microwave outphasing power amplifiers,” *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 61, no. 10, pp. 2987–2998, Oct. 2014.

- [24] T. W. Barton and D. J. Perreault, “Theory and implementation of RF-input outphasing power amplification,” *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 12, pp. 4273–4283, Dec. 2015.

- [25] T. W. Barton, A. S. Jurkov, P. H. Pednekar, and D. J. Perreault, “Multi-way lossless outphasing system based on an all-transmission-line combiner,” *IEEE Trans. Microw. Theory Techn.*, vol. 64, no. 4, pp. 1313–1326, Apr. 2016.

- [26] S. Li, T. Chi, H. T. Nguyen, T. Huang, and H. Wang, “A 28 GHz packaged chireix transmitter with direct on-antenna outphasing load modulation achieving 56%/38% PA efficiency at peak/6 dB back-off output power,” in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2018, pp. 68–71.

- [27] S. Li, T. Chi, J. Park, H. T. Nguyen, and H. Wang, “A 28-GHz flip-chip packaged chireix transmitter with on-antenna outphasing active load modulation,” *IEEE J. Solid-State Circuits*, vol. 54, no. 5, pp. 1243–1253, May 2019.

- [28] W. Tai *et al.*, “A transformer-combined 31.5 dBm outphasing power amplifier in 45 nm LP CMOS with dynamic power control for back-off power efficiency enhancement,” *IEEE J. Solid-State Circuits*, vol. 47, no. 7, pp. 1646–1658, Jul. 2012.

- [29] H. Chireix, “High power outphasing modulation,” *Proc. Inst. Radio Eng.*, vol. 23, no. 11, pp. 1370–1392, Nov. 1935.

- [30] K. Ning and J. F. Buckwalter, “An 18-dBm, 57 to 85-GHz, 4-stack FET power amplifier in 45-nm SOI CMOS,” in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2018, pp. 1453–1456.

- [31] K. Ning and J. F. Buckwalter, “A 28-GHz, 18-dBm, 48% PAE stacked-FET power amplifier with coupled-inductor neutralization in 45-nm SOI CMOS,” in *Proc. IEEE BiCMOS Compound Semiconductor Integr. Circuits Technol. Symp. (BCICTS)*, Oct. 2018, pp. 85–88.

- [32] D. Zhao, S. Kulkarni, and P. Reynaert, “A 60-GHz outphasing transmitter in 40-nm CMOS,” *IEEE J. Solid-State Circuits*, vol. 47, no. 12, pp. 3172–3183, Dec. 2012.

- [33] N. Hosseiniadeh and A. Medi, “Wideband 5 W Ka-band GaAs power amplifier,” *IEEE Microw. Wireless Compon. Lett.*, vol. 26, no. 8, pp. 622–624, Aug. 2016.

- [34] T. Hwang, K. Azadet, R. S. Wilson, and J. Lin, “Linearization and imbalance correction techniques for broadband outphasing power amplifiers,” *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 7, pp. 2185–2198, Jul. 2015.

- [35] J. Fritzin, A. Alvandpour, P. N. Landin, and C. Fager, “Linearity, intermodulation distortion and ACLR in outphasing amplifiers,” in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2013, pp. 1–4.

- [36] Y. Wang, J. Guan, M. Wei, and R. Negra, “Impact of modulation order and DAC resolution on high data rate wireless transmitters,” in *Proc. IEEE Radio Wireless Symp. (RWS)*, Jan. 2016, pp. 126–128.

**Kang Ning** (S'14) received the B.S. degree from the School of Physics Science and Technology, Lanzhou University, Lanzhou, China, in 2012, and the M.S. degree in electrical and computer engineering from the University of Minnesota at Twin Cities, Minneapolis, MN, USA, in 2015. He is currently pursuing the Ph.D. degree with the University of California at Santa Barbara, Santa Barbara, CA, USA.

In 2019, he was an mm-Wave IC Designer Intern at Mixcomm Inc., Chatham, NJ, USA. His current research interests include RF/millimeter-wave (mm-wave) integrated circuit (IC) design in silicon and compound semiconductor technologies.

Mr. Ning serves as a reviewer for the IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS, the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR ARTICLES, and the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES.

**Yihao Fang** was born in Shanghai, China, in 1992. He received the B.Sc. degree in materials science and engineering with a concentration in electronic materials from the University of California at Los Angeles (UCLA), Los Angeles, CA, USA, in 2016. He is currently pursuing the Ph.D. degree with Prof. M. Rodwell's group, University of California at Santa Barbara (UCSB), Santa Barbara, CA, USA.

From 2013 to 2016, he was an undergraduate Research Assistant at Prof. Yang Yang's Lab, UCLA, where he worked on organic semiconductors and organic-halide perovskites. In 2016, he joined the Electrical Engineering Department, University of California at Santa Barbara (UCSB). His research interests include III/V semiconductors, heterojunction bipolar transistors (HBTs), tunneling field-effect transistors (TFETs), and terahertz III/V metal-oxide-semiconductor field-effect transistors (MOSFETs).

**Navid Hosseinzadeh** (S'13) received the M.Sc. degree in electrical engineering from the Sharif University of Technology, Tehran, Iran, in 2014. He is currently pursuing the Ph.D. degree in electrical and computer engineering with the Department of Electrical and Computer Engineering, University of California at Santa Barbara, Santa Barbara, CA, USA.

In 2019, he was a Research and Development Intern with the PsiQuantum Corporation, Palo Alto, CA, USA. His current research interests include RF/millimeter-wave integrated circuit (IC) design in silicon and compound semiconductor technologies, silicon photonics integrated circuits, and quantum computers.

Mr. Hosseinzadeh serves as a reviewer for the IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS, the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR ARTICLES, and the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES.

**James F. Buckwalter** (S'01–M'06–SM'13) received the Ph.D. degree in electrical engineering from the California Institute of Technology, Pasadena, CA, USA, in 2006.

From 1999 to 2000, he was a Research Scientist with Telcordia Technologies Inc., Piscataway, NJ, USA. In 2004, he joined the IBM Thomas J. Watson Research Center, Yorktown Heights, NY, USA. In 2006, he joined the Faculty of the University of California at San Diego, La Jolla, CA, USA, as an Assistant Professor, where he became an Associate Professor in 2012. He is currently a Professor of electrical and computer engineering with the University of California at Santa Barbara, Santa Barbara, CA, USA.

Dr. Buckwalter was a recipient of the 2004 IBM Ph.D. Fellowship, the 2007 Defense Advanced Research Projects Agency Young Faculty Award, the 2011 NSF CAREER Award, and the 2015 IEEE MTT-S Young Engineer Award.