#### **PAPER**

## Ultra-wide bandgap AlGaN metal oxide semiconductor heterostructure field effect transistors with high-*k* ALD ZrO<sub>2</sub> dielectric

To cite this article: Shahab Mollah et al 2019 Semicond. Sci. Technol. 34 125001

View the article online for updates and enhancements.

#### Recent citations

- Improved operation stability of in situ AISiO dielectric grown on (000–1) N-polar GaN by MOCVD Islam Sayed *et al*

- Characterization of AlSiO dielectrics with varying silicon composition for N-polar GaN-based devices Islam Sayed *et al*

- Trap characterization in ultra-wide bandgap Al0.65Ga0.4N/Al0.4Ga0.6N MOSHFET's with ZrO2 gate dielectric using optical response and cathodoluminescence Mohi Uddin Jewel et al

### IOP ebooks™

Bringing together innovative digital publishing with leading authors from the global scientific community.

Start exploring the collection-download the first chapter of every title for free.

Semicond. Sci. Technol. 34 (2019) 125001 (7pp)

https://doi.org/10.1088/1361-6641/ab4781

# Ultra-wide bandgap AlGaN metal oxide semiconductor heterostructure field effect transistors with high-k ALD ZrO<sub>2</sub> dielectric

Shahab Mollah<sup>1</sup>, Mikhail Gaevski<sup>1</sup>, MVS Chandrashekhar<sup>1</sup>, Xuhong Hu<sup>1</sup>, Virginia Wheeler<sup>2</sup>, Kamal Hussain<sup>1</sup>, Abdullah Mamun<sup>1</sup>, Richard Floyd<sup>1</sup>, Iftikhar Ahmad<sup>1</sup>, Grigory Simin<sup>1</sup>, Charles Eddy<sup>2</sup> and Asif Khan<sup>1</sup>

E-mail: mmollah@email.sc.edu

Received 11 July 2019, revised 31 August 2019 Accepted for publication 24 September 2019 Published 25 October 2019

#### **Abstract**

We report on  $Al_{0.65}Ga_{0.35}N/Al_{0.4}Ga_{0.6}N$  metal oxide semiconductor heterojunction field-effect transistor (MOSHFET) with high-k ZrO<sub>2</sub> gate-dielectric deposited using atomic layer deposition process. As extracted from frequency dependent capacitance-voltage (CV) characteristics, the oxide gates resulted in an interfacial state trap density of  $\sim 2 \times 10^{12}$  cm<sup>-2</sup>. A comparative study, on the same material, shows the gate-leakage current of the ZrO<sub>2</sub> MOSHFETs to be lower by five orders; their ON/OFF current ratio ( $\sim 10^7$ ) to be higher by about four orders and their threshold voltage to decrease (less negative) by 3.5 V with respect to the Schottky gate devices.

Keywords: AlGaN HFET, AlGaN MOSHFET, high Al composition, insulating gate, atomic layer deposition, threshold voltage, fixed interface charges

1

(Some figures may appear in colour only in the online journal)

#### 1. Introduction

Due to the higher thermal conductivity and breakdown field, the Baliga figure of merit of ultra-wide bandgap (UWBG)  $Al_xGa_{1-x}N$  (x > 0.5) channel devices is higher than those with GaN and SiC channels [1–3]. They have been shown to have excellent radiation hardness [4] with the cutoff wavelengths in the solar-blind spectral region. UWBG III-Nitride semiconductors are thus promising materials for compact next-generation power electronics [5–10], solar-blind photodetection [11, 12] and nuclear reactor controls requiring radiation hardness [13].

The research on UWBG transistors is currently focused on several different type of devices, such as high electron mobility transistors (HEMTs), insulating gate HEMTs (also known as MOS-HEMTs or metal oxide semiconductor heterojunction field-effect transistor (MOSHFETs)), vertical MOSHFETs, CAVET devices etc [5]. Among those, HEMTs and MOSHFETs are of particular interest due to simple

epilayer structure, excellent defect screening by high-density 2DEG and broad range of potential applications.

We have recently reported on  $Al_{0.65}Ga_{0.35}N/Al_{0.4}Ga_{0.6}N$ MOSHFETs with SiO<sub>2</sub> gate-oxide that was deposited using a plasma enhanced chemical vapor deposition (PECVD) process [14]. These devices had record high drain currents of 0.6 A mm<sup>-1</sup>. However, an oxide thickness greater than 100 Å was required for a factor of  $10^3$  reduction in the gate-current. This in turn increased (more negative) the threshold voltage by about 2 V. Our past work with GaN channel MOSHFETs established that use of high-k gate-oxides mitigates this problem giving a very low gate-leakage current without a substantial increase in the threshold voltage [15]. However, highk dielectrics have never been used in UWBG MOSHFETs with high-Al content barrier. The motivation behind the current work is to study the reduction of the gate-leakage current and change in the threshold voltage in UWBG MOSHFET with atomic layer deposition (ALD) high-k dielectrics.

<sup>&</sup>lt;sup>1</sup> Department of Electrical Engineering, University of South Carolina, Columbia, SC 29208, United States of America

<sup>&</sup>lt;sup>2</sup> Naval Research Laboratory, Washington DC, United States of America

#### 2. Experimental

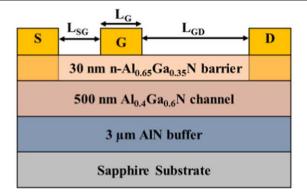

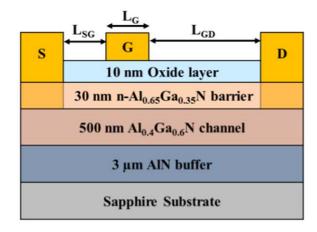

The device epilayer structure shown in figures 1(a), (b) was deposited on a 3  $\mu$ m thick AlN/sapphire templates using metalorganic-chemical-vapor deposition process. Details of the growth procedure are reported elsewhere [16]. The off axis (102) x-ray peak line width for the AlN buffer layers of our templates was measured to be 330 arcsecs, which based on our past calibrations, translates to an overall defect-density  $\sim$ (1 – 3)  $\times$  10<sup>8</sup> cm<sup>-2</sup>. The channel Al<sub>0.40</sub>Ga<sub>0.60</sub>N and the barrier n-Al<sub>0.65</sub>Ga<sub>0.35</sub>N layers for our structures were respectively 0.5  $\mu$ m and 300 Å thick and only the barrier layer was silicon doped. As measured from the 1/ $C^2$  versus V plot, the barrier layer carrier concentration due to Si-doping was approximately 4  $\times$  10<sup>18</sup> cm<sup>-3</sup>. As measured by the Eddy current method, the sheet resistance ( $R_{\rm sh}$ ) value for our epilayer structure was  $\sim$ 1900  $\Omega/\Box$ .

The device source/drain ohmic contact metal stack Zr/Al/Mo/Au (150/1000/400/300 Å) [14] were evaporated and annealed for 30 s at 950 °C under N<sub>2</sub> using rapid thermal annealing. The devices were mesa-isolated with Cl<sub>2</sub>-based inductively coupled plasma reactive ion-etching (ICP-RIE). We achieved linear source–drain ohmic-contacts with a contact resistance as low as 1.64  $\Omega$  mm which gives an equivalent ohmic specific contact resistivity of ~1.4  $\times$  10<sup>-5</sup>  $\Omega$  cm<sup>2</sup>. The gate-metal consisted of Ni/Au (1000 Å/2000Å). In addition to devices with gate-length 1.8  $\mu$ m, gated transmission lined model test structures with gate-lengths ranging from 10 to 100  $\mu$ m were also fabricated.

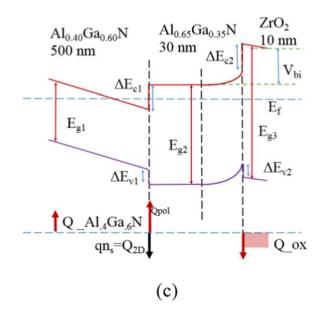

For this study, two sets of devices with identical geometry were fabricated on the same wafer. These consisted of devices with Schottky gates and with ZrO2 oxide under the gate metals. The thickness of the ALD gate-oxide was 10 nm. The ZrO<sub>2</sub> film was deposited using thermal ALD process at 200 °C, with trimethylaluminum (TMA), tetrakis (dimethylamido) zirconium (IV) (TDMAZ) and deionized water as the precursors. The TDMAZ precursor was also heated to 75 °C in order to achieve a linear growth rate of 0.7 Å/cycle. The deposition was initiated with 15 water pulses prior to the typical AB pulsing sequence to deposit the gate dielectric to ensure saturation of hydroxyl groups at the AlGaN surface required for conformal ALD nucleation [17–19]. The thickness of the ZrO2 films was obtained using witness samples grown on Si substrates in the same run, giving thickness 10 nm, with an index of refraction 2.13 from ellipsometry, very close to the ideal value of 2.15 expected for ZrO<sub>2</sub> [20, 21]. In previous studies by the coauthors' group (e.g. Shahin et al [19], the thickness of ZrO2 on Si witness samples as measured by ellipsometry has identical thickness to the electrical thickness of ZrO<sub>2</sub> deposited on GaN in the same run using identical deposition conditions. The stoichiometry of the films was confirmed by XPS (figures 2(a), (b)). Neither carbon, nor nitrogen were observed, indicating complete ligand exchange during ALD, underscoring the high purity of the films. This is consistent with the close to ideal index of 2.13 measured by ellipsometry. The relative intensities of the Zr3d and O1s core levels (figures 2(a), (b)) are also consistent with

(a)

(b)

**Figure 1.** The device structure of the HFET (a) and MOSHFET (b). (c) Band diagram of ZrO<sub>2</sub> MOS-HFET,  $E_{\rm g1}=4.52~{\rm eV},$   $E_{\rm g2}=5.22~{\rm eV},$   $E_{\rm g3}=6~{\rm eV},$   $\Delta E_{\rm v1}=0.21~{\rm eV},$   $\Delta E_{\rm c1}=0.49~{\rm eV},$   $\Delta E_{\rm v2}=0.234~{\rm eV},$   $\Delta E_{\rm c2}=0.546~{\rm eV},$   $V_{\rm bi}=2.7~{\rm V}$  and  $Q_{\rm ox}=-3.1~\times~10^{13}~{\rm q~C~cm}^{-2}.$

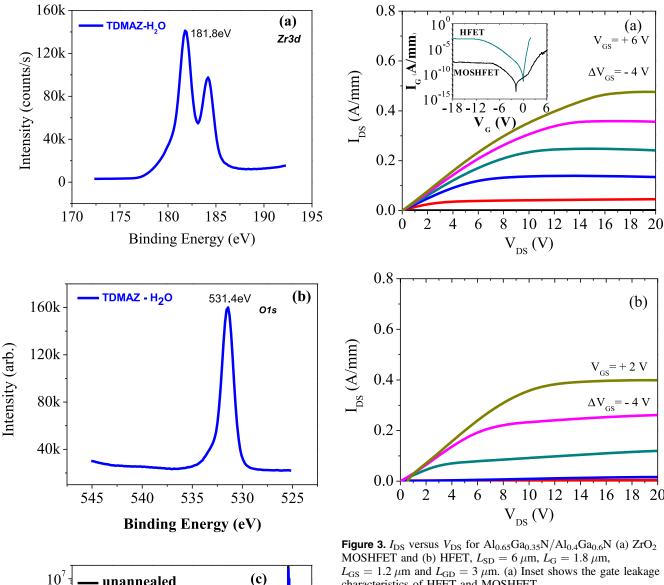

$L_{\rm GS}=1.2~\mu{\rm m}$  and  $L_{\rm GD}=3~\mu{\rm m}$ . (a) Inset shows the gate leakage characteristics of HFET and MOSHFET.

The transfer  $(I_{DS} \text{ versus } V_G)$  and the output I-V characteristics were measured using a parameter analyzer and the capacitance voltage (C-V) measurements were performed using a HP 4284A Precision LCR Meter.

## Intensity (arb.) $10^{4}$ $10^{3}$

40

50

2Theta (deg)

60

70

unannealed

$10^6$

10<sup>5</sup>

20

30

annealed 400°C

(c)

Figure 2. (a) The 3d core level XPS spectra (b) O 1 s photoelectron spectra of ZrO<sub>2</sub> dielectric (c) XRD of ZrO<sub>2</sub> dielectric film.

stoichiometric ZrO2 [22]. XRD showed no sharp peaks, indicative of highly amorphous films. This amorphous nature persisted until 400 °C, at which point no sharp peaks were seen.

#### 3. Results and discussion

Figure 3(a) shows the output characteristics of the ZrO<sub>2</sub> MOSHFET, with the gate length  $L_{\rm G}=1.8~\mu{\rm m}$ , gate-source and gate-drain spacing  $L_{\rm SG}=1.2~\mu{\rm m}$  and  $L_{\rm GD}=3~\mu{\rm m}$ respectively. Clear saturation is observed, with peak currents  $\sim 0.5 \,\mathrm{A}\,\mathrm{mm}^{-1}$  at  $V_{\mathrm{G}} = 6\,\mathrm{V},\ V_{\mathrm{D}} = 20\,\mathrm{V}.$  For the HFET (no oxide under gate i.e. Schottky gate) the saturation current was  $\sim 0.4 \text{ A mm}^{-1}$  ( $V_G = 2 \text{ V}$ ) which is shown in figure 3(b), and a channel electron mobility  $>400 \,\mathrm{cm}^2 \,\mathrm{V}^{-1} \,\mathrm{s}^{-1}$  was estimated by accounting for access region and contact resistances. This procedure is outlined in a previous report [14]. The  $I_{\rm G}$ - $V_{\rm G}$ curves in the inset of figure 2 show that the use of insulating

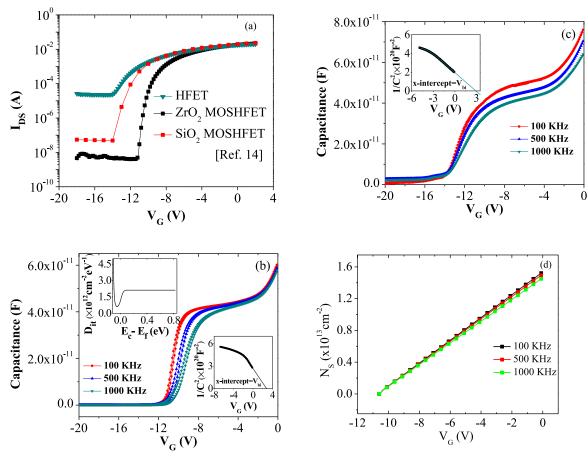

Figure 4. (a): Transfer characteristics HFET and MOSHFET;  $L_{\rm SG}=L_{\rm GD}=10~\mu{\rm m}$  and  $L_{\rm G}=10~\mu{\rm m}$ . (b) MOSHFET CV characteristics. Upper inset shows the extracted distribution of traps with  $E_{\rm c}-E_{\rm f}$  from the CV measurements, lower inset shows the  $1/C^2$  versus V plot. (c) HFET C-V characteristics. Inset shows the  $1/C^2$  versus V plot. (d) 2DEG charge density  $(N_{\rm s}~(V_{\rm G}))$  of  $ZrO_2$  MOSHFET.

gate with ALD oxide reduces the gate-leakage current by 5 orders of magnitude.

The transfer characteristics of figure 4(a) were measured using  $10~\mu m$  long gate MOSHFET. This was done to ensure that in the subthreshold regime the gate leakage current is dominated by bulk rather than the surface leakage. The transfer curves show an ON/OFF ratio of  $\sim 10^3$  for the HFET which increases to  $\sim 6 \times 10^6$  for the MOSHFET, while in our previously reported PECVD SiO<sub>2</sub> MOSHFET [14] it was  $\sim 10^6$ . This improvement is primarily from the reduction in the gate leakage current by  $\sim 5$  orders of magnitude compared to HFET, where the gate leakage reduction was  $\sim 4$  orders of magnitude in SiO<sub>2</sub> MOSHFET. Using data of figure 4(a), the values of threshold voltage  $V_{th}$  were obtained as  $V_{G}$  voltages at which the drain current decreases to  $30~\mu A$  or  $0.1~mA~mm^{-1}$ .

The slope in transfer curves shown in figure 4(a) represents the rate of transition from on- into off-state (in a logarithmic scale). The peak drain currents (on-state currents) are similar for HFET and MOSHFET, however, the off-state current in MOSHFET is much lower because in HFET the gate leakage masks the actual subthreshold swing of the device. Besides, MOSHFET with ZrO<sub>2</sub> gate dielectric has more positive threshold voltage compared to HFET. These two factors determine much steeper slope of the MOSHFET transfer curves in figure 4(a).

The transfer characteristics of figure 4(a) show a positive  $V_{\rm th}$  shift by  $\sim 3.5 \, {\rm V}$  in  ${\rm ZrO}_2$  MOSHFET as compared to the HFET. This is contrary to what was observed for the PECVD SiO<sub>2</sub> MOSHFETs [14, 23], where a reduction of gate-leakage current is accompanied by a more negative  $V_{\rm th}$  [15]. Positive threshold voltage shift is an important effect that may help creating normally-off (enhancement mode) MOSHFETs which are critically important for use in power electronics applications. The  $V_{\rm th}$  shift can be caused by a negative charge in the oxide or the oxide/barrier interface or both. Oxide and interfacial charges also play an important role in switching and high-frequency performance of wide bandgap MOSH-FETs [24]. To determine these charges in the fabricated ALD ZrO<sub>2</sub> MOSHFETs, a comprehensive study of their frequencydependent C-V measurements was conducted as described below.

For the study, we used devices with gate-length  $L_{\rm G}=100~\mu{\rm m}$ , and gate-width  $W=200~\mu{\rm m}$  to test the C-V characteristics. Figure 4(b) shows frequency dependent C-V characteristics for the  ${\rm ZrO_2}$  MOSHFET. The  $V_{\rm th}$  value here is consistent with that measured from the transfer characteristics of figure 4(a). At  $V_{\rm G}=0$ , the depletion only extends partially into the barrier layer, and does not reach the 2DEG, simplifying the analysis. Because of the high doping in the barrier

layer, it is possible to clearly distinguish three regimes seen in all devices:

- (i) Depletion through barrier layer  $-2 \text{ V} < V_{\text{G}} < 0 \text{ V}$  with  $1/C^2$  dependence showing constant doping

- (ii) 2D electron gas at barrier/channel interface  $\approx\!\!-8$  V <  $V_{\rm G}<-2$  V

- (iii) Pinch-off, with depletion extending into channel epitaxial layer  $V_{\rm G} \ll -8~{

m V}$

The boundary between regime (i) and (ii) represents the voltage at which the 2DEG is being depleted, from which the capacitance of the gate at the 2DEG is measured,  $C_{\rm 2D}$ , which is true regardless of whether an oxide is present. Given this value of  $C_{\rm 2D}$ , the  $V_{\rm th}$  measured in figure 4(a) can be expressed as:

$$V_{\text{th}} = -\frac{Q_{\text{2D}}}{C_{\text{2D}}} - \frac{qN_{\text{d}}}{2\varepsilon_{\text{s}}}(t_{\text{b}}^2 - x_{\text{d}}^2),$$

(1)

where  $t_b$  is the barrier layer thickness,  $x_d$  is the depletion region width in the Al<sub>0.65</sub>Ga<sub>0.35</sub>N barrier layer (figure 1).  $Q_{2D}$ is the 2DEG sheet charge density. The first term in the right hand side of equation (1) represents the voltage required to deplete the 2DEG. The sheet charge density  $Q_{2D}$  is obtained by integrating the area under the C-V curve in figure 4(b), giving a  $V_G$  dependent sheet carrier concentration  $(N_S)$  in figure 4(d). Since all voltages are referenced to 0 V, the  $N_S$ value at  $V_G = 0 \text{ V}$  gives the  $Q_{2D} = qN_S$ . The capacitance of the 2DEG was measured from C-V at the point where the C-V characteristic begins to flatten out ( $\sim$ 47 pF for an area of  $2 \times 10^{-4}$  cm<sup>2</sup>). Thus, the first term is -8 V. The second part represents the voltage required to deplete the doped barrier. This term is based on standard expression for Schottky junction depletion widths. The calculated value for the second part is -2.5 V based on the 0-bias capacitance value for the MOSHFET, and the measured barrier thickness by C-V(figure 4(c)) from the HFET without the ZrO<sub>2</sub>. So the calculated threshold voltage is  $-10.5 \,\mathrm{V}$  which is very close to the value  $-10.7 \,\mathrm{V}$  determined from the  $I_{\mathrm{d}}$ – $V_{\mathrm{g}}$  curve (figure 4(a)). From the linear  $1/C^2$  characteristic in regime (i), the donor concentration in the barrier layer,  $N_{\rm d}$  is obtained. The value of  $N_{\rm d}$  for MOSHFET was  $\sim 4.2 \times 10^{18}~{\rm cm}^{-3}$ , whereas for the HFET, this was significantly higher at  $6.8 \times 10^{18}$  cm<sup>-3</sup>. We attribute this change to the *in situ* pre-ALD surface preparation. From the boundary between regimes (i) and (ii) for the HFET, where the 2DEG is located at the barrier/channel interface, the barrier thickness  $t_{\rm b} = \varepsilon_{\rm S}/C_{\rm 2D} = 30 \, \rm nm$  is obtained.

The gate capacitance in  $ZrO_2$  MOSHFET is a series combination of the oxide capacitance and the barrier capacitance at the 2DEG, where the C-V characteristic begins to flatten out:

$$\frac{1}{C_{\rm G}} = \frac{1}{C_{\rm ox}} + \frac{1}{C_{\rm b}}$$

$C_{\rm G}$  is total gate capacitance of MOSHFET 47 pF at 100 KHz from figure 4(b).  $C_{\rm b}$  is barrier capacitance which is obtained from the HFET C-V characteristics without the  ${\rm ZrO_2}$  (53 pF at 100 KHz figure 4(c)) Thus, the oxide capacitance

normalized to the area  $2 \times 10^{-4}\,\mathrm{cm}^2$  is obtained. Given the 10 nm thickness, as measured by ellipsometry in the experimental section, the dielectric constant is extracted from  $C_{\mathrm{ox}} = \varepsilon_r \varepsilon_0/t_{\mathrm{ox}}$  to be  $\varepsilon_r = 23$ , which is within the experimental range of 18–25 [15, 25, 26]. This relatively high value is consistent with the close to ideal index of 2.13 measured by ellipsometry. This is expected due to the lack of C and N contaminants by XPS, an advantage of the TDMAZ precursor [19].

Figure 4(d) shows the 2DEG charge density as a function of gate voltage. In the on- state the device has a sheet charge density of  $\sim 1.53 \times 10^{13} \, \mathrm{cm}^{-2}$ .

The built-in voltage  $V_{\rm bi}$  (defined in figure 1(c) band diagram), measured from the  $1/C^2$  x-intercept in figure 3(a) can be expressed in terms of  $x_{\rm d}$  as follows [27]:

$$V_{\rm bi} = \frac{qN_{\rm d}x_{\rm d}^2}{2\epsilon_{\rm s}} + E_{\rm ox}t_{\rm ox}.$$

(2)

The barrier height for MOSHFET and HFET are 2.7 eV and 3 eV respectively (see figures 4(b) and (c) inset). For the HFET,  $t_{\rm ox}=0$ , so that from the measured  $N_{\rm d}$  and  $V_{\rm bi}$ ,  $x_{\rm d}$  is extracted to be 20 nm, in agreement with that extracted from the gate capacitance at  $V_{\rm G}=0$  V i.e. C(0), which is  $x_{\rm d}=\varepsilon_{\rm s}/C(0)=24$  nm, showing that our formalism here is self-consistent. For the MOSHFET,  $E_{\rm ox}$  is determined from Gauss's law at the oxide/barrier interface, where  $Q_{\rm ox}$  is the fixed sheet charge density at this interface:

$$\epsilon_{\rm ox} E_{\rm ox} - \epsilon_{\rm s} E_{\rm s} = Q_{\rm ox} = \epsilon_{\rm ox} E_{\rm ox} - \epsilon_{\rm s} \left(\frac{q N_{\rm d} x_{\rm d}}{\epsilon_{\rm s}}\right).$$

(3)

Solving for  $E_{\rm ox}$  in terms of  $Q_{\rm ox}$ , we can rewrite  $V_{\rm bi}$  as:

$$V_{\text{bi}} = \frac{qN_{\text{d}}x_{\text{d}}^2}{2\epsilon_{\text{s}}} + \frac{qN_{\text{d}}x_{\text{d}}}{\epsilon_{\text{ox}}}t_{\text{ox}} + \frac{Q_{\text{ox}}}{\epsilon_{\text{ox}}}t_{\text{ox}},\tag{4}$$

where the HFET can be described by setting  $t_{\rm ox}=0$ .  $x_{\rm d}$  is deduced from the fact that the oxide capacitance,  $C_{\rm ox}=\epsilon_{\rm ox}/t_{\rm ox}$  and the depletion capacitance in the barrier,  $\epsilon_s/x_{\rm d}$  are in series. From the measured 0 bias capacitance C(0),  $x_{\rm d}=(C_{\rm ox}\,\epsilon_{\rm s}-C(0)\,\epsilon_{\rm s})/C(0)\,C_{\rm ox}$ . Inserting this  $x_{\rm d}$  into the previous equation, we have an equation with a single unknown remaining, namely  $Q_{\rm ox}$ , in terms of the measured  $V_{\rm bi}$ ,  $N_{\rm d}$ , and the known oxide parameters. The extracted value of  $Q_{\rm ox}$  is  $-3.1\times10^{13}\,{\rm q}\,{\rm C}\,{\rm cm}^{-2}$ . Negative value of  $Q_{\rm ox}$  helps depleting the 2DEG thus making  $V_{\rm th}$  more positive. Further optimization of barrier thickness and doping as well as of oxide film may enable realization of enhancement mode UWBG AlGaN devices as was the case for GaN channel HEMTs [28–33].

From the difference in the high  $(C_{\rm HF})$  and the low frequency  $(C_{\rm LF})$  capacitance versus voltage (C-V) characteristics, the density of interface states,  $D_{\rm it}$  can be obtained. Since the barrier is doped and relatively thick  $\sim \! 30$  nm, the surface oxide charges,  $Q_{\rm ox}$  do not significantly impact trapping at the barrier/channel interface. At low frequencies, slow traps have sufficient time to recharge and hence contribute to the measured capacitance, whereas at high frequencies they do not, resulting in lower measured capacitance. Figure 4(b) shows this dispersion for the MOSHFET. From this

difference, at a given,  $V_G$  [34]

$$D_{\rm it}(V_{\rm G}) = \frac{C_{\rm ox}}{q} \left( \frac{C_{\rm LF}}{C_{\rm ox} - C_{\rm LF}} - \frac{C_{\rm HF}}{C_{\rm ox} - C_{\rm HF}} \right). \tag{5}$$

To relate the gate voltage  $V_{\rm G}$  to the Fermi level position with respect to the conduction band in the channel,  $E_{\rm c}$ , we note that the 2D density of states is constant [35], leading to the following expression for a degenerate 2DEG density:

$$n_{s} = \int_{E_{C}}^{\infty} \frac{m^{*}}{\pi \hbar^{2}} f(E - E_{f}) d$$

$$= \frac{m^{*}kT}{\pi \hbar^{2}} \ln \left[ \frac{1}{1 + \exp\left(-\frac{E_{C} - E_{f}}{kT}\right)} \right], \tag{6}$$

where we have assumed single sub-band occupation. Rearranging, and with  $n_s(V_G)$  measured from integrating the C-V profile in figure 4(b), the distribution of interface traps with energy level below the conduction band  $E_c$  is obtained for the channel region in the vicinity of the barrier channel interface [36]

$$E_{\rm C} - E_f = -kT \ln \left[ \exp \left( \frac{n_{\rm s} \pi \hbar^2}{m^* kT} \right) - 1 \right]. \tag{7}$$

The distribution of interfacial traps is plotted in inset of figure 4(b), showing a uniform distribution below the conduction band. This distribution is atypical for III-N devices, which normally show an exponential dependence of  $D_{\rm it}$  near the conduction band [36]. The total trap density is  $\sim 2 \times 10^{12}$  cm<sup>-2</sup>.

#### 4. Conclusions

In summary, we have demonstrated  $V_{\rm th}$  control in Al<sub>0.6</sub>Ga<sub>0.4</sub>N/Al<sub>0.4</sub>Ga<sub>0.6</sub>N MOS-HFET using ALD deposited high-k ZrO<sub>2</sub> gate dielectric. By using a doped barrier design, high drain-currents of 0.5 A mm<sup>-1</sup> were achieved, whereas the ZrO<sub>2</sub> gate dielectric reduces the gate leakage currents by a factor of more than  $10^4$  when compared to Schottky-gate devices. We have found that fixed oxide charges result in a significant,  $\sim$ 3.5 V positive threshold voltage shift compared to Schottky-gate devices. Further improvements in growth process and the device geometry may enable enhancement mode UWBG AlGaN channel devices.

#### **Acknowledgments**

This research was supported by DARPA DREAM contract (ONR N00014-18-1-2033), Program Manager Dr Young-Kai Chen, monitored by ONR, Dr Paul Maki. It was also partially supported by ARO contract W911NF-18-1-0029 monitored by Dr M Gerhold and National Science Foundation (NSF), ECCS Award nos. 1711322 and 1810116, program director Dr Dimitris Pavlidis. Part of the AlN template work was

supported by MURI program monitored by Dr Lynn Petersen. The authors also acknowledge the support from the University of South Carolina through the ASPIRE program. Work at the US Naval Research Laboratory is supported by the Office of Naval Research.

#### **ORCID iDs**

Shahab Mollah https://orcid.org/0000-0002-2848-2959

#### References

- [1] Lien W C, Damrongplasit N, Paredes J H, Senesky D G, Liu T J K and Pisano A P 2014 4H-SiC N-channel JFET for operation in high-temperature environments *IEEE J*. *Electron Devices Soc.* 2 164–7

- [2] Menozzi R, Member S, Umana-membreno G A, Nener B D, Parish G, Sozzi G, Faraone L and Mishra U K 2008 Temperature-dependent characterization of AlGaN/GaN HEMTs: thermal and source/drain resistances *IEEE Trans. Device Mater. Reliab.* 8 255–64

- [3] Muhtadi S, Hwang S M, Coleman A, Asif F, Simin G, Chandrashekhar M V S and Khan A 2017 High electron mobility transistors with Al<sub>0.65</sub>Ga<sub>0.35</sub>N channel layers on thick AlN/sapphire templates *IEEE Electron Device Lett.* 38 914–7

- [4] Sun K-X 2011 Applications of robust, radiation hard AlGaN optoelectronic devices in space exploration and high energy density physics CLEO2011- Laser Sci. to Photonic Appl. Balt. MD pp 1–2

- [5] Tsao J Y et al 2018 Ultrawide-bandgap semiconductors: research opportunities and challenges Adv. Electron. Mater. 4 1600501

- [6] Muhtadi S, Hwang S, Coleman A, Asif F, Lunev A, Chandrashekhar M V S and Khan A 2017 High temperature operation of n-AlGaN channel metal semiconductor field effect transistors on low-defect AlN templates *Appl. Phys. Lett.* 110 193501

- [7] Kaplar R J, Allerman A A, Armstrong A M, Crawford M H, Dickerson J R, Fischer A J, Baca A G and Douglas E A 2017 Review—ultra-wide-bandgap AlGaN power electronic devices ECS J. Solid State Sci. Technol. 6 Q3061–6

- [8] Baca A G, Armstrong A M, Allerman A A, Douglas E A, Sanchez C A, King M P, Coltrin M E, Fortune T R and Kaplar R J 2016 An AlN/Alo. 85Gao. 15N high electron mobility transistor Appl. Phys. Lett. 109 33509

- [9] Mollah S, Gaevski M, Hussain K, Mamun A, Floyd R, Hu X, Chandrashekhar M V S, Simin G and Khan A 2019 Current collapse in high-Al channel AlGaN HFETs Appl. Phys. Express 12 074001

- [10] Bajaj S, Akyol F, Krishnamoorthy S, Zhang Y and Rajan S 2016 AlGaN channel field effect transistors with graded heterostructure ohmic contacts Appl. Phys. Lett. 109 0-4

- [11] Muhtadi S, Hwang S M, Coleman A L, Lunev A, Asif F, Chava V S N, Chandrashekhar M V S and Khan A 2017 High-speed solar-blind UV photodetectors using high-Al content Al 0.64 Ga 0.36 N/Al 0.34 Ga 0.66 N multiple quantum wells Appl. Phys. Express 10 011004

- [12] Muhtadi S, Hwang S, Coleman A, Asif F, Lunev A, Chandrashekhar M V S and Khan A 2017 Selective area deposited n-Al0. 5Ga0. 5N channel field effect transistors with high solar-blind ultraviolet photo-responsivity Appl. Phys. Lett. 110 171104

- [13] Owens A and Peacock A 2004 Compound semiconductor radiation detectors *Nucl. Instrum. Methods Phys. Res.* A 531 18–37

- [14] Hu X, Hwang S, Hussain K, Floyd R, Mollah S, Asif F, Simin G and Khan A 2018 Doped barrier Al<sub>0.65</sub> Ga<sub>0.35</sub> N/Al<sub>0.40</sub> Ga<sub>0.60</sub> N MOSHFET with SiO<sub>2</sub> gate-insulator and Zr-based ohmic contacts *IEEE Electron Device Lett.* 39 1568–71

- [15] Rai S, Adivarahan V, Tipirneni N, Koudymov A, Yang J, Simin G and Khan M A 2006 Low threshold-14 W/mm ZrO<sub>2</sub>/AlGaN/GaN metal-oxide-semiconductor heterostructure field effect transistors *Japan. J. Appl. Phys.* 1 45 4985–7

- [16] Fareed Q, Adivarahan V, Gaevski M, Katona T, Mei J, Ponce F A and Khan A 2007 Metal-organic hydride vapor phase epitaxy of Al<sub>x</sub>Ga<sub>1-x</sub>N films over sapphire *Japan. J. Appl. Phys.* 2 46 1–4

- [17] Anderson T J, Wheeler V D, Shahin D I, Tadjer M J, Koehler A D, Hobart K D, Christou A, Kub F J and Eddy C R 2016 Enhancement mode AlGaN/GaN MOS high-electron-mobility transistors with ZrO<sub>2</sub> gate dielectric deposited by atomic layer deposition Appl. Phys. Express 9 7–10

- [18] Anderson T J, Wheeler V D, Shahin D I, Tadjer M J, Luna L E, Koehler A D, Hobart K D, Kub F J and Eddy C R 2017 Normally-off AlGaN/GaN Mos-hemts using ZrO<sub>2</sub> gate dielectric with tuneable charge 231st ECS Meeting MA2017-01 1285

- [19] Shahin D I, Anderson T J and Christou A 2017 Achieving vertical trench-gate GaN MOSFETs via process optimization ECS Trans. 80 139–45

- [20] Gottmann J and Kreutz E W 1999 Pulsed laser deposition of alumina and zirconia thin films on polymers and glass as optical and protective coatings Surf. Coat. Technol. 116–119 1189–94

- [21] Sangermano M, Voit B, Sordo F, Eichhorn K J and Rizza G 2008 High refractive index transparent coatings obtained via UV/thermal dual-cure process *Polym. Elsevier* 49 2018–22

- [22] Liu J, Liao M, Imura M, Tanaka A, Iwai H and Koide Y 2014 Low on-resistance diamond field effect transistor with highk ZrO<sub>2</sub> as dielectric *Nat. Sci. Rep.* 4 6395

- [23] Adivarahan V, Rai S, Tipirneni N, Koudymov A, Yang J, Simin G and Khan M A 2006 Digital oxide deposition of SiO<sub>2</sub> layers for III-nitride metal-oxide-semiconductor heterostructure field-effect transistors Appl. Phys. Lett. 88 2-4

- [24] Khan M A, Simin G, Yang J, Zhang J, Koudymov A, Shur M S, Gaska R, Hu X and Tarakji A 2003 Insulating

- gate III-N heterostructure field-effect transistors for highpower microwave and switching applications *IEEE Trans. Microw. Theory Tech.* **51** 624–33

- [25] Chen C, Chiu H, Chien F, Chuang H, Chang K and Gau Y 2012 Microelectronics reliability high thermal stability and low hysteresis dispersion AlGaN/GaN MOS-HEMTs with zirconia film design *Microelectron. Reliab.* 52 2551–5

- [26] Botzakaki M A, Xanthopoulos N, Makarona E, Tsamis C, Kennou S, Ladas S, Georga S N and Krontiras C A 2013 Microelectronic engineering ALD deposited ZrO<sub>2</sub> ultrathin layers on Si and Ge substrates: a multiple technique characterization *Microelectron. Eng.* 112 208–12

- [27] Sze S M K K N 2001 Physics of Semiconductor Devices 3rd edn (New York: Wiley)

- [28] Khan M A, Chen Q, Sun C J, Yang J W, Blasingame M, Shur M S and Park H 1995 Enhancement and depletion mode GaN/AlGaN heterostructure field effect transistors Appl. Phys. Lett. 68 514–6

- [29] Zhang Y, Sun M, Joglekar S J, Fujishima T and Palacios T 2013 Threshold voltage control by gate oxide thickness in fluorinated GaN metal-oxide-semiconductor high-electronmobility transistors Appl. Phys. Lett. 103 033524

- [30] Palacios T, Suh C S, Chakraborty A, Keller S, DenBaars S P and Mishra U K 2006 High-performance e-mode AlGaN/GaN HEMTs IEEE Electron Device Lett. 27 428–30

- [31] Saito W, Takada Y, Kuraguchi M, Tsuda K and Omura I 2006 Recessed-gate structure approach toward normally off high-voltage AlGaN/GaN HEMT for power electronics applications *IEEE Trans. Electron Devices* 53 356–62

- [32] Maeda N, Hiroki M, Sasaki S and Harada Y 2012 Hightemperature characteristics in normally off AlGaN/GaN heterostructure field-effect transistors with recessed-gate enhanced-barrier structures Appl. Phys. Express 5 84201

- [33] Oka T and Nozawa T 2008 AlGaN/GaN recessed MIS-Gate HFET with high-threshold-voltage normally-off operation for power electronics applications *IEEE Electron Device* Lett. 29 668–70

- [34] Penumatcha A V, Swandono S and Cooper J A 2013

Limitations of the high-low C-V technique for MOS interfaces with large time constant dispersion *IEEE Trans. Electron Devices* 60 923–6

- [35] Charles K 2003 Introduction To Solid State Physics 8th edn (New York: Wiley)

- [36] Wang R et al 2010 Gate-recessed enhancement-mode InAIN/ AIN/GaN HEMTs with 1.9-A/mm drain current density and 800-mS/mm transconductance IEEE Electron Device Lett. 31 1383-5