#### ACCEPTED MANUSCRIPT

# Ultrawide bandgap $AI_xGa_{1-x}N$ channel heterostructure field transistors with drain currents exceeding 1.3 A/mm

To cite this article before publication: Mikhail Gaevski et al 2020 Appl. Phys. Express in press https://doi.org/10.35848/1882-0786/abb1c8

### Manuscript version: Accepted Manuscript

Accepted Manuscript is "the version of the article accepted for publication including all changes made as a result of the peer review process, and which may also include the addition to the article by IOP Publishing of a header, an article ID, a cover sheet and/or an 'Accepted Manuscript' watermark, but excluding any other editing, typesetting or other changes made by IOP Publishing and/or its licensors"

This Accepted Manuscript is © 2020 The Japan Society of Applied Physics.

During the embargo period (the 12 month period from the publication of the Version of Record of this article), the Accepted Manuscript is fully protected by copyright and cannot be reused or reposted elsewhere.

As the Version of Record of this article is going to be / has been published on a subscription basis, this Accepted Manuscript is available for reuse under a CC BY-NC-ND 3.0 licence after the 12 month embargo period.

After the embargo period, everyone is permitted to use copy and redistribute this article for non-commercial purposes only, provided that they adhere to all the terms of the licence <a href="https://creativecommons.org/licences/by-nc-nd/3.0">https://creativecommons.org/licences/by-nc-nd/3.0</a>

Although reasonable endeavours have been taken to obtain all necessary permissions from third parties to include their copyrighted content within this article, their full citation and copyright line may not be present in this Accepted Manuscript version. Before using any content from this article, please refer to the Version of Record on IOPscience once published for full citation and copyright details, as permissions will likely be required. All third party content is fully copyright protected, unless specifically stated otherwise in the figure caption in the Version of Record.

View the article online for updates and enhancements.

## Ultrawide Bandgap Al<sub>x</sub>Ga<sub>1-x</sub>N Channel Heterostructure Field Transistors with drain currents exceeding 1.3 A/mm

Mikhail Gaevski, Shahab Mollah, Kamal Hussain, Joshua Letton, Abdullah Mamun, Mohi Uddin Jewel, MVS Chandrashekhar, Grigory Simin and Asif Khan.

Department of Electrical Engineering, University of South Carolina, Columbia, SC 29208

We report an Ultrawide Bandgap Al<sub>0.4</sub>Ga<sub>0.6</sub>N channel Metal-Oxide-Semiconductor Heterostructure field effect transistor with drain currents exceeding 1.33 A/mm (pulse) and 1.17A/mm (DC), around a 2-fold increase over past reports. This increase was achieved by incorporating a hybrid barrier layer consisting of an AlN spacer, n-doped Al<sub>0.6</sub>Ga<sub>0.4</sub>N barrier and a thin reverse graded Al<sub>x</sub>Ga<sub>1-x</sub>N (x from 0.60 to 0.30) cap layer. To enhance current spreading, a "perforated" channel layout comprising of narrow channel sections separated by current blocking islands was used. A composite ALD deposited ZrO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> film was used as gate dielectric. A breakdown field above 2MV/cm was measured.

*Index Terms*— UWBG AlGaN MOSHFET, Perforated channel, RC-constant, Self-heating, Thermal resistance.

To take advantage of their high breakdown field, several research groups at present are developing ultrawide bandgap (UWBG) Al<sub>x</sub>Ga<sub>1-x</sub>N (x>0.4) channel heterostructure field effect transistors (HFETs) for high-temperature, high-voltage, and high-power applications. The higher breakdown field leads to a much higher Baliga Figure of Merit (BFOM).<sup>1,2)</sup> Devices with channel alloy compositions of 40% or higher have been reported by several groups including ours.<sup>3,4,5)</sup> To date, all these reported AlGaN channel devices have their drain currents well below 1 A/mm which is a typical value for GaN channel HFETs with micron size gate lengths.<sup>6-9)</sup> This is also the case even for the insulating gate devices where a positive gate-bias can be used for increasing the draincurrents. The fundamental reason for this is the alloy scattering which leads to the 2-dimensional electron gas (2DEG) mobility in UWBG AlGaN channel layers approximately a factor of 3-5 lower than that of GaN.<sup>10-12)</sup> Thus, the sheet resistance values for UWBG AlGaN channel HFETs are typically 2000  $\Omega/\Box$  as compared to around 300  $\Omega/\Box$  for GaN channel devices.<sup>13-15)</sup> Another current limiting factor is the difficulty in forming formation of low resistivity ohmic contacts to UWBG AlGaN layers. For these layers, the barrier heights are very high, and contacts typically show a Schottky type behavior.<sup>16)</sup> For direct contacts to the AlGaN barrier layers, even with high doping and Al-compositions around 0.60, contact resistance is typically over 4 ohm-mm.<sup>17)</sup> This again is approximately a factor of 6 higher than that for the GaN channel HFETs.<sup>18)</sup>

To decrease the contact resistivity and increase the peak drain currents in UWBG AlGaN channel HFETs and MOSHFETs, several approaches have been explored. Xue et. al. used highly *n*-doped Al<sub>x</sub>Ga<sub>1-x</sub>N selectively grown contact layers on top of the UWBG AlGaN barrier layers.<sup>19)</sup> However, the lowest achieved contact resistivity was still around 3.9  $\Omega$ -mm and, even with 0.16  $\mu$ m long gates in a 1.2  $\mu$ m access opening, the peak currents were limited to only 0.42 A/mm (at a gate voltage of +0V). We reported on a new device design for MOSHFETs with *n*-doped barrier layers and achieved a contact resistivity as low as 1.6  $\Omega$ -mm and peak drain currents as high as 0.6 A/mm at a gate-voltage of +6V for 2  $\mu$ m gate-length devices (access region 6  $\mu$ m).<sup>20)</sup> Higher gate-voltages led to excessive leakage currents from the breakdown of the PECVD deposited gate oxide (SiO<sub>2</sub>). More recently, we have also reported on a microchannel approach for reducing the effective contact resistance. For a 1:6 (fill factor), a 100 nm long gate in a 1.6  $\mu$ m long access region, a peak drain-current of 900 mA/mm was measured at a gate voltage of +2V (Schottky gate).<sup>21)</sup> The processing sequence for fabricating these micro-channel devices was complicated

with several steps needing precise e-beam lithography. Moreover, high gate leakage in these HFET devices limits usage of positive gate bias and it also reduces the breakdown voltage.

In this paper by incorporating several innovations in the epi-material and device design, we report  $Al_2O_3/ZrO_2-Al_{0.6}Ga_{0.3}N-Al_{0.4}Ga_{0.6}N$  depletion mode (D-mode) MOSHFETs with peak drain current  $I_{Dmax}$  more than 1.3 A/mm, a high transconductance 90 mS/mm and a breakdown field of 2 MV/cm. The devices exhibited very large  $I_{ON}/I_{OFF}$  values that were higher than  $10^8$ .

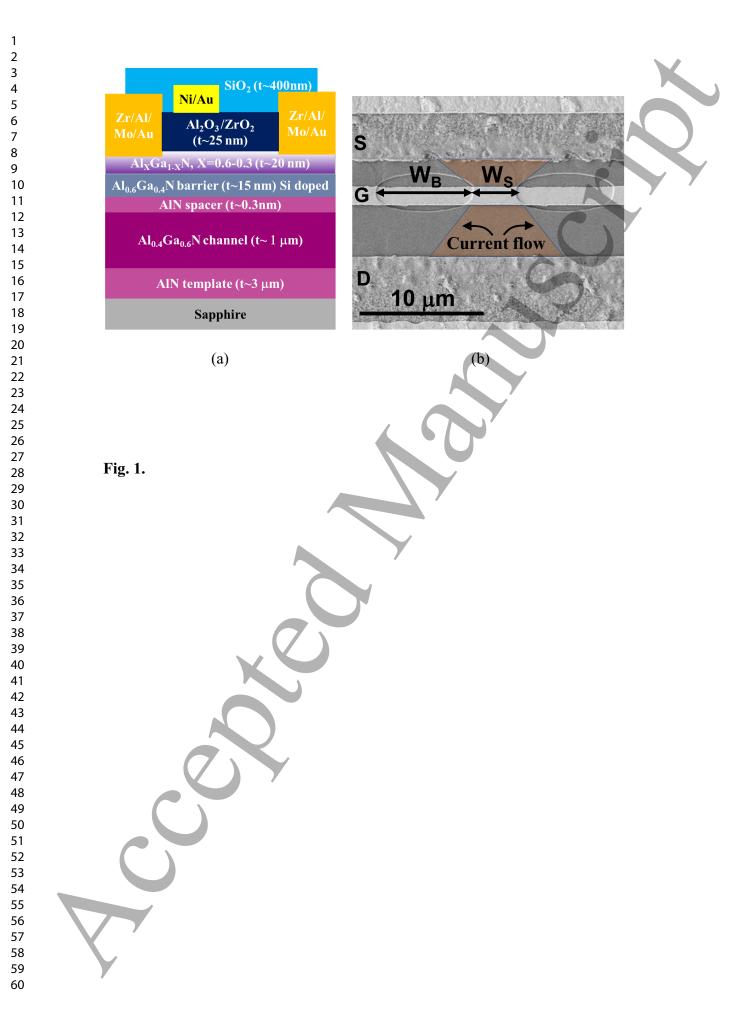

The device schematic cross-section is shown in Fig. 1(a). It consisted of a 3  $\mu$ m thick, high-quality AlN/sapphire template on which an Al<sub>0.4</sub>Ga<sub>0.6</sub>N channel layer was grown using low pressure metalorganic chemical vapor deposition (LP-MOCVD). Hybrid barrier design reported here includes 0.3 nm thick AlN spacer layer followed by a 15 nm thick Si-doped *n*-Al<sub>0.6</sub>Ga<sub>0.4</sub>N barrier layer followed by a 20 nm thick reverse composition graded Si-doped Al<sub>x</sub>Ga<sub>1-x</sub>N (x from 0.6 to 0.3 layer. This top layer was incorporated to assist ohmic contact formation. The use of reverse-graded layer allows achieving low contact resistance. The high barrier doping compensates the mobile positive charges resulting from the reverse composition grading.<sup>22)</sup>

In addition to the new epilayer design, we also incorporated a perforated channel (PC) layout [Fig. 1 (b)] which was shown to significantly reduce source and drain access resistances<sup>21,23</sup>. In this design, the device channel consists of relatively narrow 2DEG sections ("straits") separated by current blocking islands. Very high 2DEG concentration enables strong current spreading from the channel straits into the S-G and G-D regions. Current flow profiles are schematically shown by shaded areas in Fig. 1(b). 2D simulations show that 4µm away from the gate edge the current density in between the channel straits is only two times lower than that along the strait center. As a result, the equivalent width of the S-G and G-D access regions, including the contact regions is larger than that of the gate strait hence leading to substantially lower access resistances. Importantly, the HFET capacitance coming mainly from the strait regions does not increase in PC design (see more on this below). For the current study, both the continuous channel (CC) and PC geometry devices were fabricated on the same wafer to allow for a direct comparison of their electrical and thermal performance. For the fabricated devices, the gate-length, gate-source and gate-drain spacing were  $L_G \approx 2.0 \ \mu m$ ,  $L_{SG} \approx 2 \ \mu m$  and  $L_{GD} \approx 2.8 \ \mu m$ . For the PC layout, the width of channel sections were  $W_S \approx 3.75 \ \mu m$ , with blocking gaps between them  $W_B \approx 8.25 \ \mu m$ . This geometry corresponds to gap/strait ratio of 2-2.5 which is close to an optimal value as shown in

ref. <sup>23)</sup>. The device processing started with mesa-isolation using chlorine-based inductively coupled plasma reactive ion etching. (ICPRIE) The device source/drain electrodes of 15 nm Zr/100 nm Al/40 nm Mo/30 nm Au were deposited using electron-beam evaporation, followed by rapid thermal annealing (RTA) at 950 °C for 30 s in N<sub>2</sub> environment. After the ohmic fabrication, the conducting channels and the blocking islands were formed using standard photolithography and ICPRIE processes. The etch depth to form the current blocking islands was 200 nm to ensure complete isolation of the 2DEG channel straits. Hot tetramethylammonium hydroxide treatment was used to remove post plasma etch residue <sup>24)</sup>. Atomic Layer Deposition (ALD) was then used to deposit Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub> bilayer for the gate insulator followed by e-beam gate metallization consisting of 100 nm Ni/200 nm Au. Details of ALD process are described in <sup>26)</sup>. Identical geometry HFET and MOSHFET devices both with the (CC) and the (PC) layout were fabricated on the same epi-wafer for a comparative study. The transistor surface was also protected with PECVD deposited 400 nm SiO<sub>2</sub> film for high voltage measurements.

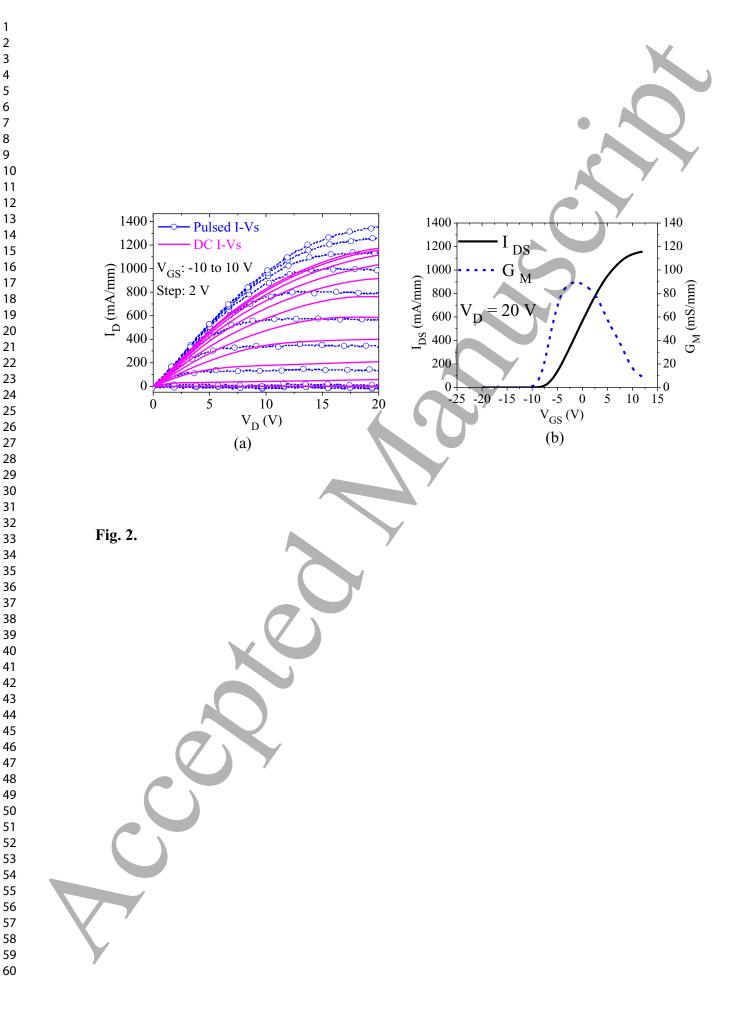

The sheet and contact resistances were measured using TLM patterns. The ohmic contact resistance was found to be 1.7  $\Omega$  mm which is one of the lowest reported to date for UWBG Al<sub>x</sub>Ga<sub>1-x</sub>N channel HEMTs.<sup>25)</sup> In addition, the fabricated MOSHFETs were characterized in both the DC and the pulse regimes to reduce heating effects at high drain currents. Short-pulse I-Vs were measured using DIVA D260 dynamic IV analyzer with pulse duration of 500 ns and low duty cycle of 0.1%. Current-voltage characteristics of the MOSHFET with  $L_{SD} \approx 8 \ \mu m \ (L_{GD} = 4$ um) are shown in Fig. 2 (a). The drain currents are normalized to the channel width. For the PCdevice the channel width is taken as the total width of all straits. This way of accounting for the total channel width is very similar to that used in large periphery multi-finger FETs. In those devices, substantial  $(50 - 150 \,\mu m \log)$  portions of the gate metal are used to connect elementary sections of multi-finger device; the length of these connections is not included in the total width when calculating the normalized current. In PC design the gate lines connecting straits perform the same function as section-to-section connections in multi-finger design. The combination of the hybrid barrier design and bi-layer gate dielectric allows operation at a positive gate bias as high as 12 V without any excessive gate-leakage. As seen, pulse drain saturation current is as high as 1.33 A/mm (at  $V_{GS}$ =+12V). Even in DC mode the peak drain current exceeds 1.17 A/mm. In Fig. 2(b) we include device transfer characteristics and the transconductance curve in DC mode. The measured transconductance value of 90 mS/mm for DC mode (as high as 110 mS/mm for pulse mode) is also more than twice that of the reported value on identical geometry devices in the past.<sup>20)</sup> The total on-resistances for the PC devices, extracted from the I-V slopes at low drain voltage are  $R_{ON}(PC) \approx 10 \ \Omega$ -mm which is about of factor of two less than  $R_{ON}$  of the (CC) device with the same  $L_{SD}$ . The threshold voltage Vth = -11 V was the same for both the CC and the PC layouts and was not affected by introduction of additional epi-layers compared to previously reported results <sup>20,23,26)</sup>.

Relative contributions of the three key features employed in current design, namely – (1) reverse graded barrier layer, (2) perforated channel layout and (3) MOS- gate design – towards maximum drain current are shown in Fig. 3 (a). It was found that hybrid barrier just slightly increases saturation current; however, it significantly improves the contact resistance and reduces the leakage current which leads to a higher breakdown voltage as discussed below. Channel perforation doubles the maximum drain saturation current of previously reported HFET <sup>20)</sup>. Figure 3 (b) shows reduction of the gate-leakage current that results from the introduction of the hybrid barrier and the composite high-*k* gate insulator. For the Al<sub>2</sub>O<sub>3</sub>/ZrO<sub>2</sub> MOSHFET, the gate leakage current remains in  $\mu$ A/mm range even at a gate voltage as high as +12V. The dramatic decrease of the gate leakage current allows device to be operated in positive gate bias regime thus pushing saturation current well above 1.3 A/mm.

As seen from Fig. 2(a) the difference between pulse and DC drain currents which we attribute to self-heating is relatively small. To evaluate the self-heating effects, we extracted the active region temperature in the CC and the PC-MOSHFETs by comparing short-pulse drain saturation currents (no self-heating) at different ambient temperatures with DC drain saturation current at the same drain voltage. The details of the temperature extraction procedure are outlined in  $^{27,28}$ . The probe station stage temperature was varied from room to 250 °C in 50 °C increments. We found that the channel temperatures for the CC- and the PC-MOSHFET were 329 °C (at dissipated power 0.497 W) and 179.6 °C (at 0.560 W) respectively. The thermal resistance was then found as  $R_{TH} = \Delta T /P$ , where  $\Delta T$  is the temperature increase due to self-heating. The obtained thermal resistance for the PC-MOSHFET was  $R_{TH-PC} = 13$  K.mm/W; that of the CC-MOSHFET  $R_{TH-CNV} = 29$  K.mm/W; therefore,  $R_{TH}$ -PC  $\approx 0.40 \times R_{TH-CNV}$ . The obtained  $R_{TH-PC}$  value is also smaller than 25K.mm/W reported for III-N HFETs on sapphire in ref.  $^{27}$  Because the total channel width and hence the power density are about the same for CC- and PC-MOSHFETs, we conclude

that the PC design also offers significant improvement in the heat removal. We attribute this improvement to a better heat spreading in the buffer and the AlN template under the straits of PC-MOSHFET.

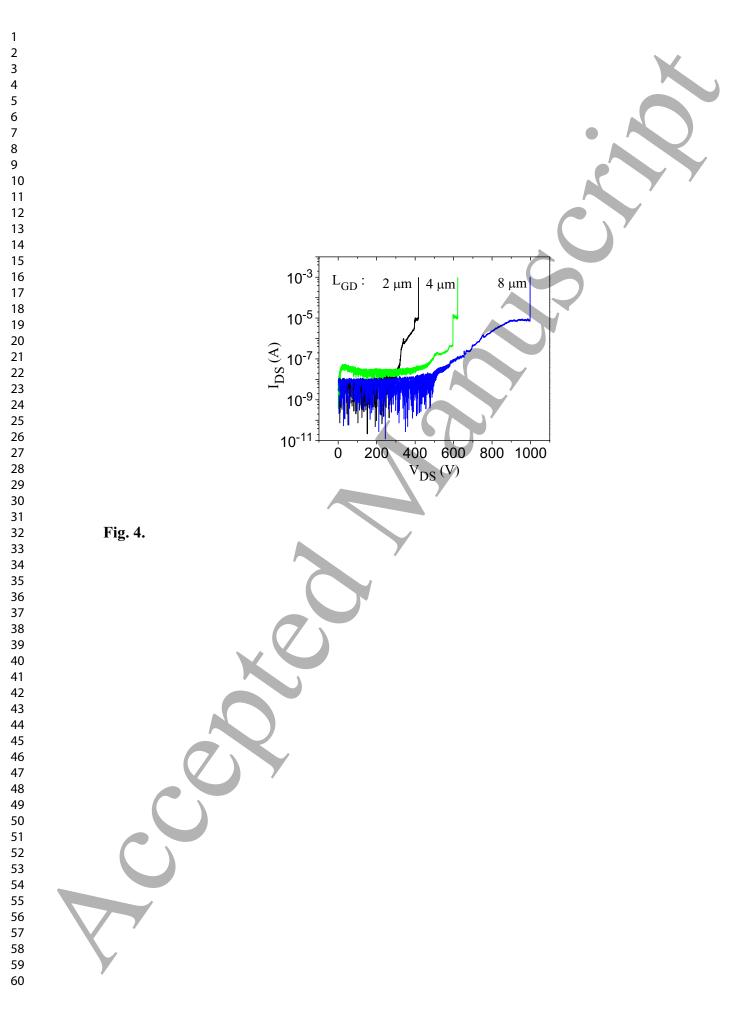

Figure 4 shows the breakdown voltage dependence for devices with different gate to drain spacings of 2, 4 and 8  $\mu$ m. As seen from the data, breakdown voltage increases to nearly 1000V for the largest spacing. The maximum breakdown field of 2.08 MV/cm achieved for the 2  $\mu$ m gate–drain spacing exceeds most reported for AlGaN-channel devices.<sup>29,30)</sup> Note, these devices had no field-plates and they did not undergo any special surface treatment other than the SiO<sub>2</sub> coating. We therefore expect that the breakdown field and the device operating voltages to further go up with better surface treatment and field-plating.

An important characteristic of transistor switches is Baliga High-Frequency Figure of Merit BHFFOM.<sup>31)</sup> BHFFOM =  $f_{BHF} = 1/(R_{ON} \times Cin)$ , where  $R_{ON}$  is the device on-resistance and  $C_{in}$  is the input capacitance. For FETs,  $C_{in} \approx C_G$  where  $C_G$  is the gate capacitance. At zero gate voltage,  $V_G = 0$ , the capacitances of the CC- and PC- devices were 8.7 pF/mm and 2.7 pF/mm respectively. Hence, the gate capacitance  $C_G$  of the PC-MOSHFET is around 3 times smaller than that of the CC-MOSHFET. Experimentally obtained values of  $R_{ON}$  and  $C_G$  allow to compare the BHFFOM for conventional and PC-MOSHFETs:  $f_{BHF-CC} = 4.6$  GHz and  $f_{BHF-PC} = 8$  GHz. As evidenced by these results, the maximum switching frequency for PC-MOSHFET is significantly higher than that of a conventional continuous channel geometry device.

In summary, for the first time we have demonstrated perforated channel UWBG AlGaN MOSHFET, with the saturation drain current exceeding 1.3 A/mm. The devices with a new composite barrier and gate-insulator design exhibit a three terminal breakdown field higher than 2 MV/cm and an extremely low gate-leakage current. The PC-MOSHFET device design leads to a factor of two lower access resistance due to the current spreading that occurs between the conducting channel sections and the larger area source and drain contacts. As a result, the PC-device design has nearly a two times higher unit-width channel current and Baliga high-frequency figure of merit. In addition, due to enhanced heat spreading, their thermal resistance is also more than two times lower than a continuous channel device on the same epilayer structure.

Acknowledgments

This research work is partially supported by DARPA DREAM contract (ONR N00014-18-1-2033), Program Manager Dr. Young-Kai Chen, monitored by ONR, Dr. Paul Maki and ARO contract W911NF-18-1-0029 monitored by Dr. M. Gerhold. Part of the AlN template was supported by MURI program monitored by Dr. Lynn Petersen. The authors would like to acknowledge partial support by National Science Foundation (NSF), ECCS Award nos. 1711322 and 1810116 under the supervision of program director Dr. Dimitris Pavlidis. The authors would also like to acknowledge the support from the University of South Carolina through the ASPIRE program.

## References

- 1) J. Y. Tsao, S. Chowdhury, M. A. Hollis, D. Jena, et al, Advance Elec. Mat. 4, 1600501 (2018).

- T. Nanjo, Akifumi Imai, Y. Suzuki, Y. Abe, T. Oishi, M. Suita, E. Yagyu, and Y. Tokuda, IEEE Trans. on Electron Devices 60, 1046 (2013).

- 3) S. Muhtadi, S. Hwang, A. L. Coleman, F. Asif, A. Khan, Proc. Device Research Conference 2017, p.143,

- 4) A.G. Baca, A.M. Armstrong, A.A. Allerman, E.A. Douglas, C.A. Sanchez, M.P. King, M.E. Coltrin, T.R. Fortune, and R.J. Kaplar, Appl. Phys. Lett. 109, 03409 (2016).

- N. Yafune, S. Hashimoto, K. Akita, Y. Yamamoto, H. Tokuda and M. Kuzuhara, Electronics Lett. 50, 211 (2014).

- 6) L. Shen, R. Coffie, D. Buttari, S. Heikman, A. Chakarborty, A. Chini, S. Keller, S.P. Denbaars, and U.K. Mishra, J. of Electronic Materials 33, 422 (2004).

- 7) S. Rai, V. Adivarahan, P. Huang, N. Tipirneni, F. Husna, G. Simin, J. W. Yang, M. A. Khan, Jap. J. of Appl. Phys. 45, 4985 (2006).

- 8) Y. -F. Wu, A. Saxler, M. Moore, R. P. Smith, S. Sheppard, P. M. Chavarker, T. Wisleded, U. K. Mishra, P. Parikh, IEEE Electron Dev. Lett. 25, 117 (2004).

- 9) E. Ahmadi, F. Wu, H. Li, S.W. Kaun, M. Tahhan, K. Hestroffer, S. Keller, J.S. Speck, and U.K. Mishra, Semicond. Sci. Technol. **30** 055012 (2015).

- 10) S. Bajaj, T. H. Hung, F. Akyol, D. Nath, S. Rajan, Appl. Phys. Lett. 105, 26403 (2014).

- 11) S. Muhtadi, S. M. Hwang, A. Coleman, F. Asif, G. Simin, MVS. Chandrashekhar, A. Khan, IEEE Electron Device Lett. 38, 914 (2017).

- 12) P. H. Carey, F. Ren, A. G. Baca, B. Klein, A. A. Allerman, A. M. Armstrong, E. A. Douglas, R. J. Kaplar, P. G. Kotula, S. J. Pearton, J. of Electron Device Society 7, 444 (2019).

- 13) S. Hashimoto, K. Akita, Y. Yamamoto, M. Ueno, T. Nakamura, K. Takeda, M. Iwaya, Y. Honda, H. Amano, Phys. Status Solidi A 209, 501 (2012).

- 14) S. Mollah, M. Gaevski, K. Hussain, A. Mamun, R. Floyd, X. Hu, MVS. Chandrashekhar, G. Simin, A. Khan, Appl. Phys. Express 12, 074001 (2019).

- 15) V. Kumar, W. Lu, R. Schwindt, A. Kuliev, G. Simin, J. Yang, M. A. Khan, I. Adesida, IEEE Electron Device Lett. 23, 46 (2002).

| 2        |

|----------|

| 3        |

| 4        |

| 5        |

| 6        |

| 7        |

| 8        |

| 9        |

| 9<br>10  |

|          |

| 11       |

| 12       |

| 13       |

| 14       |

| 15       |

| 16       |

| 17       |

| 18       |

| 19       |

| 20       |

| 21       |

| 22       |

| 22       |

|          |

| 24       |

| 25       |

| 26       |

| 27       |

| 28       |

| 29       |

| 30       |

| 31       |

| 32       |

| 33       |

| 34       |

| 34<br>35 |

|          |

| 36       |

| 37       |

| 38       |

| 39       |

| 40       |

| 41       |

| 42       |

| 43       |

| 44       |

| 45       |

| 46       |

| 40<br>47 |

|          |

| 48       |

| 49       |

| 50       |

| 51       |

| 52       |

| 53       |

| 54       |

| 55       |

| 56       |

| 57       |

| 58       |

| 58<br>59 |

| 59<br>60 |

| nU       |

16) A. G. Baca, B. A. Klein, A. A. Allerman, A. M. Armstrong, E. A. Douglas, C. A. Stephenson, T. R. Fortune, R. J. Kaplar, ECS Journal of Solid State Science and Technology 6, Q161 (2017).

- 17) S. Muhtadi, S. Hwang, A. Coleman, F. Asif, A. Lunev, M. V. S. Chandrashekhar, A. Khan, Appl. Phys. Lett. 110, 19401 (2017).

- 18) F. M. Mohammed, L. Wang, and I. Adesida, Appl. Phys. Lett. 88, 212107 (2006).

- H.Xue, S. Hwang, T. Razzak, C.H. Lee, G. C. Ortiz, , Z. Xia, S. H. Sohel, J. HWANG, S. Rajan, A. Khan, W. Lu, Solid State Electronics 164, 107696 (2020).

- 20) X. Hu, S. Hwang, K. Hussain, R. Floyd, S. Mollah, F. Asif, G. Simin and A. Khan, IEEE Electron Dev. Lett.,39, 1568 (2018).

- 21) H. Xue, K. Hussain, T. Razzak, M. Gaevski, S. H. Sohel, S. Mollah, V. Talesara, A. Khan, S. Rajan, W. Lu IEEE Electron Dev. Lett. 4, 667 (2020).

- 22) S. Bajaj, F. Akyol, S. Krishnamoorthy, Y. Zhang, and S. Rajan, Appl. Phys. Lett. 109, 133508 (2016).

- 23) G.S. Simin, M. Islam, M. Gaevski, J. Deng, R. Gaska, and M.S. Shur, IEEE Electron Device Lett. 4, 449 (2014).

- 24) J.W. Do, H-W. Jung, M.J. Shin, H-K. Ahn, H. Kim, R-H. Kim, K.J. Cho, S-J. Chang, B-G. Min, H.S. Yoon, J-H. Kim, J-M. Yang, J-H. Lee, J-W. Lim, Thin Solid Film 628, 31 (2017)

- 25) A.G. Baca, A.M. Armstrong, B.A. Klein, A.A. Allerman, E.A. Douglas, and R.J. Kaplar, J. Vac. Sci. Technol. A 38, 020803 (2020).

- 26) S. Mollah, K. Hussain, R. Floyd, A. Mamun, M. Gaevski, MVS Chandrashekhar, I. Ahmad, G. Simin, V. Wheeler, C. Eddy, A. Khan, Phys. Status Solidi A 217, 1900802 (2020).

- 27) R. Gaska, A. Osinsky, J. W. Yang, and M. S. Shur, IEEE Electron Dev. Lett. 19, 89 (1998).

- 28) J. Sun, H. Fatima, A. Koudymov, A. Chitnis, X. Hu, H.-M. Wang, J. Zhang, G. Simin, J. Yang and M. Asif Khan, IEEE Electron Device Lett. 24, 375 (2003).

- 29) M. Xiao, X. Duan, W. Zhang, H. Shan, J. Ning, and Y. Hao, IEEE Electron Dev. Lett. 39, 1149 (2018).

- T. Nanjo, M. Takeuchi, M. Suita, T. Oishi, Y. Abe, Y. Tokuda, and Y. Aoyagi, Appl. Phys. Lett. 92, 263502 (2008).

- 31) B. J. Baliga, IEEE Electron Dev. Lett. 10, 455 (1989).

## **Figure Captions**

Fig. 1. (a)Schematic structure, and (b) layout of the PC-MOSHFET.

Fig. 2. (a) IV characteristics of MOSHFET in DC (solid lines), and pulse mode (open

circles). (b) DC transfer curve and transconductance at  $V_{D}\!\!=\!\!20$  V.

**Fig. 3.** Effect of key factors incorporated in the MOSHFET design on (a) maximum drain current and (b) gate leakage current.

Fig. 4. Breakdown characteristics of MOSHFETs with different gate-drain spacing.