# High-Temperature Operation of $Al_xGa_{1-x}N$ (x > 0.4) Channel Metal Oxide Semiconductor Heterostructure Field Effect Transistors with High-*k* Atomic Layer Deposited Gate Oxides

Shahab Mollah,\* Kamal Hussain, Richard Floyd, Abdullah Mamun, Mikhail Gaevski, MVS Chandrashekhar, Iftikhar Ahmad, Grigory Simin, Virginia Wheeler, Charles Eddy, and Asif Khan

Due to their superior breakdown fields compared with GaN and SiC and high thermal conductivity,  $Al_xGa_{1-x}N$  (x > 0.4) channel high-electron-mobility transistors (HEMTs) will find applications in extreme environments such as power electronics. Herein, the high-temperature operation of ultrawidebandgap (UWBG) Al<sub>0.65</sub>Ga<sub>0.35</sub>N/Al<sub>0.4</sub>Ga<sub>0.6</sub>N metal oxide semiconductor heterostructure field effect transistors (MOSHFETs) with atomic layer-deposited (ALD) high-k gate dielectrics TiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and ZrO<sub>2</sub> is reported. As compared with similar geometry HFETs, these devices exhibit a simultaneous reduction in gateleakage current by  $\approx 10^4$  and a positive shift of the threshold voltage as much as 4 V. This positive threshold shift indicates the introduction of negative charges at the oxide/barrier interface and within the thin oxide, attributed to the pre-ALD plasma treatment. The gate leakage increases weakly with temperature up to 250 °C, whereas the peak drain currents decrease from  $\approx$ 0.5 to 0.3 A mm<sup>-1</sup>. An analysis of the C-V and I-V characteristics reveals that this drain current decrease is due to a reduction in channel electron mobility. The potential mechanisms responsible for this are discussed. Up to the measured temperature of 250 °C, the devices withstand repeated temperature cycles without catastrophic degradation or breakdown, underscoring the promise of these materials.

### 1. Introduction

AlGaN channel high-electron-mobility transistors (HEMTs) are potential candidates for the next-generation power switching transistors because of their ultrawide bandgap (UWBG).<sup>[1-7]</sup>

E-mail: mmollah@email.sc.edu

Dr. V. Wheeler, Dr. C. Eddy U.S. Naval Research Laboratory

4555 Overlook Ave SW, Washington, DC 20375, USA

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/pssa.201900802.

DOI: 10.1002/pssa.201900802

The advantages of using wider-bandgap AlGaN material are to enhance the breakdown voltage, which leads to higher output power densities. The breakdown voltage of high-Al composition  $Al_xGa_{1-x}N$  (x > 0.5) is expected to be approximately three times higher than that of GaN, and the thermal conductivity of AlN is six times higher than sapphire and  $1.5 \times -2 \times$  higher than GaN.<sup>[8]</sup> So the thermal conductivity of AlGaN channel is higher than that of GaN and below AlN. Thus, the Baliga Figure of Merit (BFOM) of  $Al_xGa_{1-x}N$  (x > 0.5) channel devices is higher than those of GaN and SiC channels.<sup>[8–10]</sup> They also have been shown to have excellent radiation hardness<sup>[11]</sup> with a cut-off wavelength in the solar-blind spectral region. Thus UWBG III-N materials are promising candidates for compact nextgeneration power electronics,<sup>[8,12–16]</sup> solarblind photodetection,<sup>[17,18]</sup> and nuclear reactor controls requiring radiation hardness.<sup>[19]</sup> As was previously shown, the wider bandgap of material also improves the temperature stability of heterostructure field

effect transistor (HFET) devices with high Al content. A dramatic reduction in gate leakage at a high temperature was achieved when atomic layer-deposited (ALD) high-*k* oxides were used in metal oxide semiconductor heterostructure field effect transistors (MOSHFETs) operating at temperatures up to 500 °C.<sup>[20,21]</sup>

Our research group recently reported on  $Al_{0.65}Ga_{0.35}N/Al_{0.4}Ga_{0.6}N$  MOSHFETs with SiO<sub>2</sub> gate dielectric. SiO<sub>2</sub> was deposited using a plasma-enhanced chemical vapor deposition (PECVD) process.<sup>[22]</sup> These devices showed a record drain current of 0.6 A mm<sup>-1</sup>. However, an oxide thickness greater than 100 Å was required for a factor of 10<sup>3</sup> reduction in the gate current compared with HFET fabricated on the same material. Therefore, the use of SiO<sub>2</sub> increased the threshold voltage (toward more negative) by about 2 V. Our past work with GaN channel MOSHFETs also established that the use of high-*k* gate oxides mitigates this problem by producing very low gate-leakage current without a substantial increase in the threshold voltage.<sup>[23]</sup>

S. Mollah, K. Hussain, R. Floyd, A. Mamun, Dr. M. Gaevski, Prof. M. S. Chandrashekhar, Prof. I. Ahmad, Prof. G. Simin, Prof. A. Khan Department of Electrical Engineering University of South Carolina 301 Main St., Columbia, SC 29208, USA

www.advancedsciencenews.com

This is the motivation behind the study reported in this article. To circumvent the issue of the threshold voltage increase in SiO<sub>2</sub> AlGaN MOSHFETs, we for the first time report the fabrication and characterization of  $Al_{0.65}Ga_{0.35}N/Al_{0.4}Ga_{0.6}N$  MOSHFETs with ALD high-*k* gate dielectrics (TiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and ZrO<sub>2</sub>).

## 2. Experimental Section

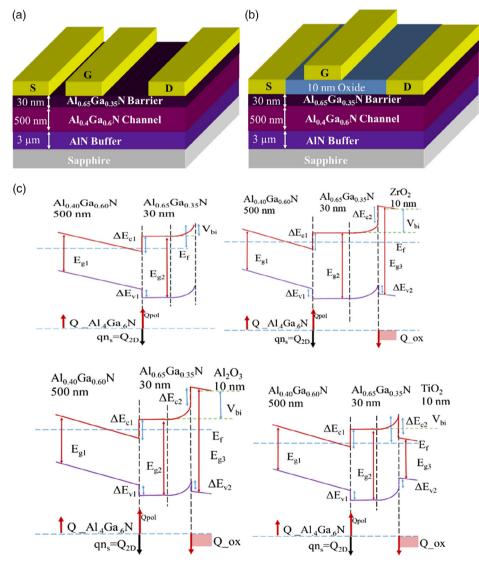

**Figure 1**a shows the epitaxial heterostructure and device geometry. The AlGaN HEMT structure was epitaxially grown on a 3 µm-thick AlN /sapphire template using the metalorganic-chemical-vapor deposition (MOCVD) process. The details of the MOCVD growth procedure can be found in a study by Fareed et al.<sup>[24]</sup> The off axis (102) X-ray peak line width for the AlN layers of our templates was measured to be 330 arcsecs, which translated to an overall defect density of  $(1-3) \times 10^8 \text{ cm}^{-2}$

based on our past calibration. The growth of 500 nm  $Al_{0.40}Ga_{0.60}N$  followed by the 30 nm Si-doped  $Al_{0.65}Ga_{0.35}N$  barrier layer completed the structure. The barrier layer was doped to enable both better contact and a higher sheet charge density in the channel. Post-growth contactless sheet resistance mapping indicated a sheet resistance ( $R_{\rm SH}$ ) of 1900  $\Omega$ . The barrier layer carrier concentration due to Si doping measured from the  $1/C^2$  versus *V* plot was  $\approx 4-6 \times 10^{18} \, {\rm cm}^{-3}$ .

The device processing started with mesa-isolation using Cl<sub>2</sub>based inductively coupled plasma reactive ion etching (ICP-RIE). The device source/drain electrodes of 15 nm Zr/100 nm Al/40 nm Mo/30 nm Au were deposited using electron-beam evaporation followed by rapid thermal annealing (RTA) at 950 °C for 30 s in N<sub>2</sub> environment. The ohmic contact resistance measured by the transmission line model (TLM) method was found to be 1.64  $\Omega$  mm, which gives an equivalent ohmic specific contact resistivity of  $\approx 1.4 \times 10^{-5} \Omega \, \mathrm{cm}^2$ . The gate metal that consisted

Figure 1. The device structure of the a) HFET and b) MOSHFET. c) Band diagram of HFETs and MOSHFETs, following values are for  $ZrO_2$  as representative from this oxide group:  $E_{g1} = 4.52 \text{ eV}$ ,  $E_{g2} = 5.22 \text{ eV}$ ,  $E_{g3} = 6 \text{ eV} \Delta E_{v1} = 0.21 \text{ eV}$ ,  $\Delta E_{c1} = 0.49 \text{ eV}$ ,  $\Delta E_{v2} = 0.234 \text{ eV}$ ,  $\Delta E_{c2} = 0.546 \text{ eV}$ ,  $V_{bi} = 2.7 \text{ V}$ , and  $Q_{ox} = -3.1 \times 10^{13} \text{ q Ccm}^{-2}$ .

of 100 nm Ni/200 nm Au was deposited using electron-beam evaporation. In addition to devices with gate length 1.8  $\mu$ m, gated transmission line model (GTLM) test structures with gate lengths ranging from 10 to 100  $\mu$ m were also fabricated.

Four sets of devices with identical geometries were fabricated on same wafer for this study. These consisted of devices with Schottky gates and with three different oxides under the gate metals. The ALD oxide thickness was 10 nm. The TiO<sub>2</sub> film was deposited by the plasma-enhanced ALD (PE-ALD) system at 350 °C, using tetrakis (dimethylamido) titanium (IV) (TDMAT) and Ar/O<sub>2</sub> plasma (80/20 sccm) as precursors. The TDMAT precursor was heated to 75 °C to ensure sufficient vapor pressure to attain a saturated linear growth rate of  $0.6 \text{ Å cycle}^{-1}$ . The deposition of the  $TiO_2$  film was initiated by 15 in situ plasma pulses prior to the alternating precursor pulses for film growth.<sup>[25-27]</sup> For the ZrO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> gate oxide films, thermal ALD processes at 200 and 250 °C, respectively, were used, with trimethylaluminum (TMA), tetrakis (dimethylamido) zirconium (IV) (TDMAZ), and deionized water as the precursors. The TDMAZ precursor was also heated to 75 °C to achieve a linear growth rate of  $0.7 \text{ Å cycle}^{-1}$ . For both the Al<sub>2</sub>O<sub>3</sub> and the ZrO<sub>2</sub> films, deposition was initiated with 15 water pulses prior to the typical AB pulsing sequence to deposit the gate dielectric to ensure saturation of hydroxyl groups at the AlGaN surface required for conformal ALD nucleation,<sup>[25,28-30]</sup> The thickness of the ALD films was obtained by ellipsometry, using witness samples grown on Si substrates in the same run, giving a thickness of 10 nm. These deposition processes have been thoroughly characterized on III-N devices in previous studies for ZrO<sub>2</sub>,<sup>[31]</sup> Al<sub>2</sub>O<sub>3</sub>,<sup>[30]</sup> and TiO<sub>2</sub><sup>[25,32]</sup> and were shown to give amorphous dielectrics as deposited.

### 3. Results and Discussion

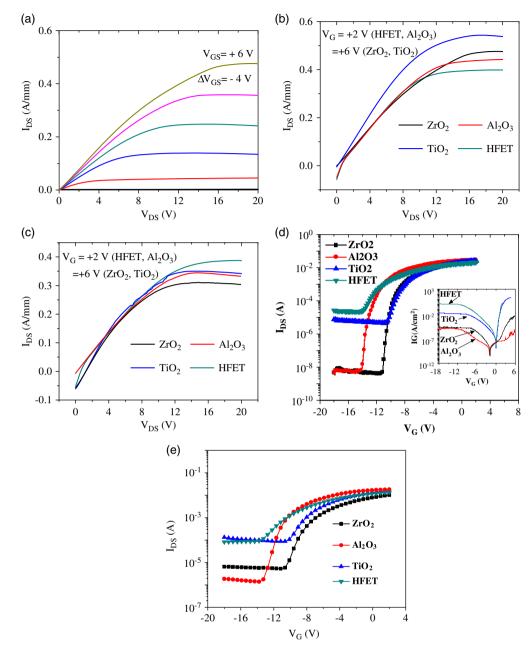

The transfer ( $I_{DS}$  vs  $V_G$ ) and the output I-V characteristics were measured using a parameter analyzer and the capacitance voltage (C-V) measurements were done using a HP 4284 A Precision LCR Meter. Figure 2a shows the drain I-V characteristics of the fabricated AlGaN channel ZrO2 MOSHFET, with a 1.8  $\mu$ m-long gate (L<sub>G</sub>), in a 6  $\mu$ m source–drain spacing. Clear saturation and pinch off are observed. Figure 2b,c shows the peak currents of same geometry ALD MOSHFETs with different dielectrics compared with that of the HFET at room temperature and 250 °C, respectively. The I-V characteristics of Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, and TiO<sub>2</sub> MOSHFETs are similar with peak currents  $\approx$ 0.44 A mm<sup>-1</sup> at  $V_{\rm G}$  = +2 V,  $\approx$ 0.5 A mm<sup>-1</sup> at  $V_{\rm G}$  = +6 V, and  $\approx$ 0.54 A mm<sup>-1</sup> at  $V_{\rm G}$  = +6 V correspondingly at room temperature. These currents are higher than the HFET (i.e., no oxide under gate) peak currents of  $\approx 0.4 \text{ A mm}^{-1}$ , at  $V_{\rm C} = +2 \text{ V}$ , which is maximum gate voltage that can be applied without triggering high gate leakage current. Higher peak currents in MOSHFETs are due to the higher positive voltage that can be applied to the gate. At 250 °C, the peak drain currents of Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, and TiO<sub>2</sub> MOSHFETs are 0.3, 0.31, and  $0.35 \,\mathrm{A}\,\mathrm{mm}^{-1}$ , respectively, whereas for HFET, it is 0.38 A mm<sup>-1</sup> under same gate voltage condition of room temperature. Thus, at 250 °C, the peak currents decrease by 35%, 38%, 32%, and 5% from room-temperature peak current for TiO<sub>2</sub>, ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and HFET, respectively.

The room-temperature transfer characteristics of Figure 2d were measured using 10 µm-long gate MOSHFETs. This was done to ensure that in the subthreshold regime, the gate leakage current is dominated by bulk rather than the surface leakage. This allows a direct comparison of the gate isolation by the different dielectrics. The transfer curves show that the ON/OFF ratio of  $\approx 10^3$  for the HFET increases to  $\approx 6 \times 10^6$  for devices with ZrO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> gate dielectrics. This improvement is primarily from the reduction in the gate leakage current (Figure 2d inset). The  $I_{\rm G}$ - $V_{\rm G}$  curves in the inset of Figure 2d show a reduction in gate leakage current by five orders of magnitude for Al<sub>2</sub>O<sub>3</sub> and ZrO<sub>2</sub> and by approximately two orders of magnitude for TiO<sub>2</sub> gate devices. We attribute the poorer reduction of gate leakage current in TiO<sub>2</sub> devices to a smaller bandgap of this material compared with the other two dielectrics used in our study (Table 1). Using data in Figure 2d, the values of the threshold voltage  $V_{\rm th}$  were obtained as  $V_{\rm G}$  voltages at which the drain current decreases to 30 µA. Figure 2e shows the transfer characteristics of these devices at 250 °C. From room temperature (RT) to 250 °C, the threshold voltage changes from -9.8 to -10 V, -12.7to -12.8 V, -10 to -10.5 V, and -13.5 to -14 V for ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, TiO<sub>2</sub>, and HFET, respectively.

The transfer characteristics of Figure 2d show a positive shift in V<sub>th</sub> for all the ALD MOSHFETs as compared with that of HFET. This is opposite to what is observed for the PECVD  $SiO_2$  MOSHFETs,<sup>[23]</sup> where a reduction in gate leakage current is usually accompanied by a more negative  $V_{\text{th}}$ .<sup>[33]</sup> The threshold voltage,  $V_{\text{th}}$ , showed a "positive shift" by  $\approx 4 \text{ V}$  for the ZrO<sub>2</sub> and TiO<sub>2</sub> dielectrics and by  $\approx 1$  V for the Al<sub>2</sub>O<sub>3</sub> gate devices. A positive threshold voltage shift is an important effect that may help creating normally off (enhancement mode) MOSHFETs which are very important for use in power electronics applications. The shift in  $V_{\rm th}$  can be caused by a fixed negative charge in the oxide or the oxide/barrier interface or both. Oxide and interfacial charges also play an important role in the switching and high-frequency performance of wide-bandgap MOSHFETs.<sup>[34]</sup> Frequency-dependent C-V measurements were done for all ALD MOSHFETs to determine these fixed charges.

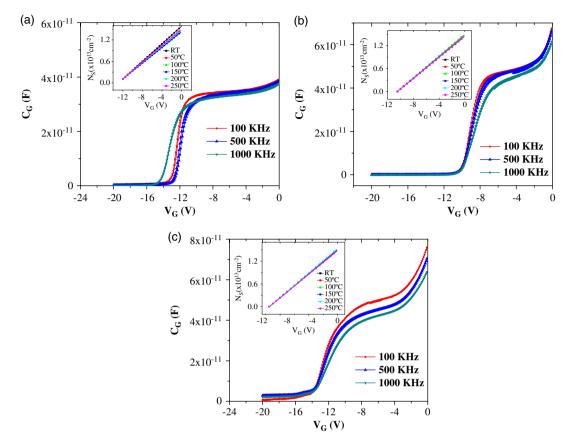

For the study, large-area FETs with gate length  $L_{\rm G} = 100 \,\mu\text{m}$ and gate width  $W = 200 \,\mu\text{m}$  were used to test C-V characteristics. Frequency-dependent C-V characteristics for MOSHFETs are shown in **Figure 3**a–c. The carrier depletion at  $V_{\rm G} = 0$  V only extends partially into the barrier layer and does not reach the two dimensional electron gas (2DEG), which is true for all the MOSHFETs. This phenomena simplifies the analysis. Because of high doping in the barrier layer, it is possible to clearly distinguish three regimes seen in all devices: 1) depletion through barrier layer  $-2 \,V < V_{\rm G} < 0 \,V$  with  $1/C^2$  dependence showing constant doping; 2) 2D electron gas at the barrier/channel interface  $\approx -8 \,V < V_{\rm G} < -2 \,V$ ; and 3) pinch off, with depletion extending into the channel epitaxial layer  $V_{\rm G} << -8 \,V$ .

For all the devices, the boundary between regimes (1) and (2) represents the voltage at which 2DEG is being depleted, from which the capacitance of the gate at 2DEG is measured,  $C_{2D}$ , which is true regardless of whether an oxide is present.

The donor concentration in the barrier layer  $N_{\rm d}$  is extracted from the linear  $1/C^2$  characteristics in regime (1). For all the ALD oxide devices, this was  $\approx 4-5 \times 10^{18} \,{\rm cm}^{-3}$ , whereas for the HFET, this was significantly higher at  $6.8 \times 10^{18} \,{\rm cm}^{-3}$ . **ADVANCED** SCIENCE NEWS \_\_\_\_\_ www.advancedsciencenews.com

**Figure 2.** a) Output characteristics of  $ZrO_2$  MOSHFET. b)The peak current comparison of different MOSHFETs and HFETs at RT. c)The peak current comparison of different MOSHFETs and HFETs at 250 °C. d) The transfer characteristics of HFETs and MOSHFETs at RT. Inset shows the gate leakage current of HFETs and MOSHFETs. e) The transfer characteristics of HFETs and MOSHFETs at 250 °C.

| Table 1. Summary of key transistor parameters. | Here $k$ is the dielectric constant. | $E_{\alpha}$ is the bandgap of | f the gate dielectr | ic, and <i>a</i> is the elementary cl | harge. |

|------------------------------------------------|--------------------------------------|--------------------------------|---------------------|---------------------------------------|--------|

|                                                |                                      |                                |                     |                                       |        |

|                  | $k/E_{\rm g}$ [eV] | V <sub>th</sub> (I–V) | V <sub>bi</sub> (C–V) | On/Off               | SS $[mV dec^{-1}]$ | $N_{\rm d,b}  [{\rm cm}^{-3}]$ | $Q_{2D}  [C  cm^{-2}]$ | $Q_{\rm ox}  [{\rm C}{\rm cm}^{-2}]$ |

|------------------|--------------------|-----------------------|-----------------------|----------------------|--------------------|--------------------------------|------------------------|--------------------------------------|

| HFET             | None               | -13.7                 | 3.0                   | 10 <sup>3</sup>      | 1290               | $6.8\times10^{18}$             | $1.9\times 10^{13} q$  | None                                 |

| $Al_2O_3$        | 8/6 eV             | -12.9                 | 5.5                   | $6 	imes 10^6$       | 105                | $5.0\times10^{18}$             | $1.9\times 10^{13} q$  | $+0.8\times10^{12} q$                |

| ZrO <sub>2</sub> | 25/6 eV            | -10.3                 | 2.6                   | $\rm 6\times 10^{6}$ | 190                | $4.2\times10^{18}$             | $1.5\times 10^{13} q$  | $-3.1\times10^{13}\text{q}$          |

| TiO <sub>2</sub> | 80/3.2 eV          | -10.0                 | 2.0                   | $\rm 2\times 10^4$   | 740                | $4.4\times10^{18}$             | $1.4\times10^{13}q$    | $-1.4\times10^{13} q$                |

Figure 3. Frequency-dependent C-V characteristics of a)  $Al_2O_3$ , b)  $ZrO_2$ , and c)  $TiO_2$  MOSHFETs. Inset figures show the temperature-dependent carrier concentration of corresponding MOSHFETs.

This change from HFET to MOSHFET in  $N_d$  value is due to the in situ pre-ALD surface preparation. From the boundary between regimes (1) and (2) for the HFET, where 2DEG is located at the barrier/channel interface, the barrier thickness is extracted using the formula  $t_b = \epsilon_s/C_{2D}$ , where  $C_{2D}$  is the capacitance of the boundary between regimes (1) and (2) for the HFETs. The extracted barrier thickness is 30 nm. We use this value of  $t_b$  for all the other MOSHFETs, which is justified, given that all these transistors were fabricated on quarters from the same wafer.

The built-in voltage  $V_{\rm bi}$  (defined in Figure 1c band diagram), measured from the  $1/C^2$  *x*-intercept in the figure, can be expressed in terms of  $x_{\rm d}$  as follows<sup>[35]</sup>

$$V_{\rm bi} = \frac{q N_{\rm d} x_{\rm d}^2}{2\epsilon_{\rm s}} + E_{\rm ox} t_{\rm ox} \tag{1}$$

For the HFET,  $t_{ox} = 0$ , so that from the measured  $N_d$  and  $V_{bi}$ ,  $x_d$  is extracted to be 20 nm, in agreement with that extracted from the gate capacitance at  $V_G = 0$  V i.e., C(0), which is  $x_d = \varepsilon_s/C(0) = 24$  nm, showing that our formalism here is self-consistent. The  $Q_{ox}$  extracted is shown in Table 1. The extraction procedure is outlined in our recent report.<sup>[36]</sup> Here, the negative  $Q_{ox}$  is responsible for depleting the 2DEG and making  $V_{th}$  more positive. Al<sub>2</sub>O<sub>3</sub>, being native to the AlGaN system, shows very low  $Q_{ox}$ . The small positive shift from the HFET to the Al<sub>2</sub>O<sub>3</sub> MOSHFET is apparently due to the lower  $N_d$  in the barrier as discussed earlier.

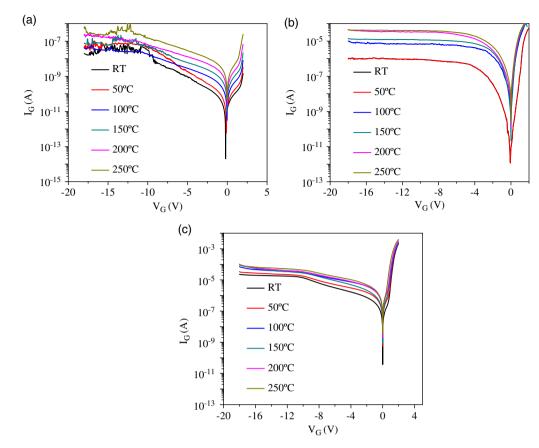

From the difference in the high- and low-frequency *C*–*V* characteristics, the density of interface states,  $D_{it}$ , is obtained in cm<sup>-2</sup>. It is a reasonable assumption that as the barrier here is doped, and relatively thick,  $\approx 30$  nm, the surface oxide charges,  $Q_{ox}$ , do not significantly impact trapping at the barrier/channel interface. At low frequencies, slow traps respond capacitively, whereas at high frequencies, they do not, leading to a decrease in measured capacitance at higher frequencies. Figure 3a–c shows this dispersion for the MOSHFETs. The total integrated trap density is  $\approx 2-3 \times 10^{12} \text{ cm}^{-2}$ . We also note that there is mild hysteresis near  $V_{th}$ , although the charge in the area bounded by this hysteresis is  $\approx 0.5 \times 10^{12} \text{ cm}^{-2}$ , small compared with that by the high-low method. **Figure 4**a–c shows the gate leakage characteristics of the MOSHFETs from RT up to 250 °C. The gate leakage is seen to be weakly dependent on temperature.

Considering the high ON/OFF ratio of these devices, we were also interested to calculate the subthreshold swing (SS), which characterizes how steep the device transition is from the ON to the OFF state as a function of gate voltage. Because the SS depends intrinsically on the barrier/channel interfacial trap density, and extrinsically on gate leakage, we provide our comparison of the SS values in HFETs and ALD MOSHFETs as follows. The results are shown in Table 1. The intrinsic SS is given by<sup>[37]</sup>

$$SS = \frac{60 \text{ mV}}{\text{decade}} \left[ 1 + \frac{qD_{\text{it}}(\text{cm}^{-2})}{C_{\text{G}}(V_{\text{th}})} \right]$$

(2)

Figure 4. Temperature-dependent gate leakage of a) Al<sub>2</sub>O<sub>3</sub>, b) ZrO<sub>2</sub>, and c) TiO<sub>2</sub> MOSHFETs.

where  $D_{\rm it}$  (cm<sup>-2</sup>) is the total interface charge density implying  $^{\circ}2$ -3 × 10<sup>12</sup> cm<sup>-2</sup>, which is obtained by integrating the area under the low-frequency and high-frequency  $C_{\rm G}$  dispersion curve. We note that the HFET and higher-leakage dielectric TiO<sub>2</sub> both display poor SS, which is artificially masked by the large gate leakage (Figure 2b inset) below  $V_{\rm th}$  (Table 1), which also limits the ON/OFF ratio. By reducing the gate leakage with ZrO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>, the intrinsic SS of the barrier/channel interface was recovered, as given by Equation (2), which is comparable with the SS values of previously reported AlGaN channel HEMTs.<sup>[8,38]</sup>

The gate voltage- and temperature-dependent mobilities of HFET and MOSHFETs were extracted using a technique that we have successfully used in the past for our AlGaN channel MOSHFETs,<sup>[22]</sup> as well as GaN channel MOSHFETs.<sup>[39]</sup> The 2D channel electron mobility  $\mu$  is extracted from the measured channel conductance<sup>[22]</sup>

$$G_{\rm ch} = q N_{\rm s} \mu \frac{W}{L_{\rm G}} \tag{3}$$

where *W* is the width of the channel and  $L_{\rm G}$  is the gate length. The electron sheet concentration  $N_{\rm s}$  can be found from the capacitance–voltage measurement using the following formula<sup>[22,39]</sup>

$$qN_{\rm S} = (V_{\rm G} - V_{\rm TG})C_{\rm G} \tag{4}$$

where *q* is the charge of electron,  $V_{\rm T}$  is threshold voltage,  $V_{\rm G}$  is the range of voltage aforementioned threshold, and  $C_{\rm G}$  is the measured gate capacitance per unit area. Figure 3a–c insets show that the  $N_{\rm S}$  value for ZrO<sub>2</sub> MOSHFET at zero gate voltage is  $\approx 1.5 \times 10^{13}$  cm<sup>-2</sup> which is independent of temperature. In Equation (3), the  $G_{\rm ch}$ ,  $N_{\rm s}$ , and  $\mu$  are functions of gate voltage  $V_{\rm G}$ . The channel conductance  $G_{\rm ch}$  in turn, can be calculated from the measured drain–source resistance  $R_{\rm DS}$ , the contact resistances of drain and source (2 $R_{\rm C}$ ), and access region resistances from gate drain ( $R_{\rm GD}$ ) and gate source ( $R_{\rm GS}$ )<sup>[22]</sup>

$$G_{\rm ch}(V_{\rm G}) = 1/[R_{\rm DS}(V_{\rm G}) - 2R_{\rm c} - R_{\rm GD} - R_{\rm GS}]$$

(5)

The contact resistance ( $R_{\rm C}$ ) and sheet resistances ( $R_{\rm SH}$ ) were extracted from the TLM measurements.  $R_{\rm GS}$  and  $R_{\rm GD}$  were found from the extracted  $R_{\rm SH}$  value and calculated with corresponding contact spacing  $L_{\rm GS}$  and  $L_{\rm GD}$ .

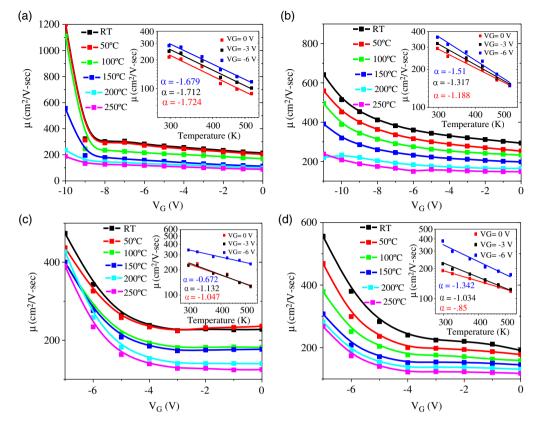

**Figure 5** shows the MOSHFET channel electron mobility plot as a function of gate voltage and temperature, whereas the inset figures show the power law fitting of temperature-dependent mobility. At room temperature, the mobility for ZrO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and TiO<sub>2</sub> MOSHFETs varies from  $\approx$ 200 to  $\approx$ 550 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>,  $\approx$ 300 to  $\approx$ 650 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, and  $\approx$ 240 to  $\approx$ 480 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at zero gate voltage and depleted channel conditions, respectively, whereas for HFETs, it varies from  $\approx$ 250 to  $\approx$ 1200 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. The extracted mobility and sheet carrier density are comparable

Figure 5. a) Temperature-dependent mobility as a function of gate voltage for a) HFET, b)  $Al_2O_3$ , c)TiO<sub>2</sub>, and d) ZrO<sub>2</sub>. Inset figures show power law fitting of mobility versus temperature plot to extract the power coefficient  $\alpha$ .

with the earlier reported mobility and sheet carrier density of AlGaN channel HEMTs from our research group,<sup>[22]</sup> as well as reports of other groups. Baca et al. reported the 70–85% HEMT with RT mobility value of 390 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and sheet carrier density of  $7.2 \times 10^{12}$  cm<sup>-2</sup>.<sup>[40]</sup> Klein et al, in their AlGaN channel HEMT reported a value of mobility 240 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and sheet carrier density of  $1.4 \times 10^{13}$  cm<sup>-2</sup>.<sup>[41]</sup>

**Table 2** shows that, at  $V_G = 0$  V, ZrO<sub>2</sub> MOSHFET mobility is least affected by temperature change. The ZrO<sub>2</sub> MOSHFET mobility drops by <40% from RT mobility where all other oxides' mobility drops by up to  $\approx 60\%$  of RT mobility. In contrast, in the depleted channel condition, TiO<sub>2</sub> is least affected by temperature. The mobility is decreased by  $\approx 17\%$  whereas in other MOSHFETs, it reduces by up to  $\approx 85\%$ . Thus, the mobility in

Table 2. Summary of electron mobility variation with temperature for different dielectrics.

| _                |                                                         |                                                                                      |                                                                                          |                                                                                                 |

|------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|                  | RT mobility at<br>$V_G = 0 V$<br>$[cm^2 V^{-1} s^{-1}]$ | 250 °C mobility at $V_G = 0 V$<br>[cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ] | RT mobility at<br>depleted channel<br>[cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ] | 250 °C mobility<br>at depleted<br>channel<br>[cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ] |

| HFET             | 207                                                     | 87 (58% drop)                                                                        | 1188                                                                                     | 188 (84% drop)                                                                                  |

| $Al_2O_3$        | 293                                                     | 146 (50% drop)                                                                       | 641                                                                                      | 240 (62% drop)                                                                                  |

| $ZrO_2$          | 191                                                     | 118 (38% drop)                                                                       | 554                                                                                      | 267 (51% drop)                                                                                  |

| TiO <sub>2</sub> | 233                                                     | 125 (46% drop)                                                                       | 473                                                                                      | 388 (17% drop)                                                                                  |

MOSHFETs with a higher density of oxide charges  $(Q_{ox})$  is less affected by increase in temperature.

The carrier mobility,  $\mu$ , increased with more negative gate voltage, i.e., as the carrier concentration decreases (see inset of Figure 3a-c). This  $N_s$  dependence implies the presence of phonon scattering.<sup>[42]</sup> The temperature dependence of the MOSHFET channel electron mobility follows a power law  $\mu \approx T^{-\alpha}$ , with  $\alpha$  varying between 1 and 3, further supporting phonon scattering as the dominant mobility limiting process.<sup>[43]</sup> We exclude the possibility of roughness scattering as the epilayer roughnesses were measured to be <1 nm rms. However, alloy scattering cannot be conclusively excluded, we note that it will be similar for all the gate dielectrics, given that the samples were cut from the same epitaxial wafer. We ascribe the small variations in  $\mu$ , and in the temperature dependence, between the different dielectrics to ionized impurity/Coulomb scattering, from charge introduced at the oxide/AlGaN barrier interface. The presence of this charge is shown in Table 1 and is reflected in the threshold voltage shift.

## 4. Conclusions

In summary, we report on room temperature up to 250 °C operation of UWBG MOSHFETs with ALD high-*k* gate dielectrics TiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and ZrO<sub>2</sub>. These devices show gate leakage reduction by four orders of magnitude as well as a positive

shift of the threshold voltage as high as 4 V, as compared with similar geometry HFETs. The devices show stable *I*–Vs in the aforementioned temperature range with weak dependence of gate leakage on temperature. The peak drain current reduces from  $\approx$ 0.5 A mm<sup>-1</sup> at room temperature to  $\approx$ 0.3 A mm<sup>-1</sup> at 250 °C. We attribute this reduction to mobility–temperature dependence, as the carrier concentration was found nearly temperature independent. Our reported devices have excellent potential for use as high-temperature power electronic devices.

### Acknowledgements

This research was supported by ARO contract W911NF-18-1-0029 monitored by Dr. M. Gerhold and National Science Foundation (NSF), ECCS award nos. 1711322 and 1810116, Program Director Dr. Dimitris Pavlidis. It was also partially supported by DARPA DREAM contract (ONR N00014-18-1-2033), Program Manager Dr. Young-Kai Chen, monitored by ONR, Dr. Paul Maki. Part of the AIN template work was supported by MURI program monitored by Dr. Lynn Petersen. The authors also acknowledge the support from the University of South Carolina through the ASPIRE program. Work at the U.S. Naval Research Laboratory was supported by the Office of Naval Research.

## **Conflict of Interest**

The authors declare no conflict of interest.

## **Keywords**

Al<sub>0.65</sub>Ga<sub>0.35</sub>N/Al<sub>0.4</sub>Ga<sub>0.6</sub>N metal oxide semiconductor heterostructure field effect transistors, high-*k* atomic layer-deposited oxides, high temperatures, temperature-dependent mobilities, threshold voltages

Received: September 21, 2019

Revised: January 20, 2020

Published online: February 7, 2020

- S. Hashaimoto, K. Akita, Y. Yamamoto, M. Ueno, T. Nakamura, N. Yafune, K. Sakuno, H. Tokuda, M. Kuzuhara, K. Takeda, M. Iwaya, H. Amano, *Phys. Status Solidi C* 2012, *9*, 373.

- [2] H. Tokuda, M. Hatano, N. Yafune, S. Hashimoto, K. Akita, Y. Yamamoto, M. Kuzuhara, Appl. Phys. Express, 2010, 3, 121003.

- [3] N. Yafune, S. Hashimoto, K. Akita, Y. Yamamoto, H. Tokuda, M. Kuzuhara, *Electron. Lett.* **2014**, *50*, 211.

- [4] H. Hahn, B. Reuters, H. Kalisch, A. Vescan, Semicond. Sci. Technol. 2013, 28, 074017.

- [5] S. Bajaj, T. H. Hung, F. Akyol, D. Nath, S. Rajan, Appl. Phys. Lett. 2014, 105, 263503.

- [6] J. Xie, S. Mia, R. Dalmau, R. Collazo, A. Rice, J. Tweedie, Z. Sitar, Phys. Status Solidi C 2011, 8, 2407.

- [7] S. Mollah, M. Gaevski, K. Hussain, A. Mamun, R. Floyd, X. Hu, M. V. S. Chandrashekhar, G. Simin, A. Khan, *Appl. Phys. Express* 2019, 12, 074001.

- [8] S. Muhtadi, S. M. Hwang, A. Coleman, F. Asif, G. Simin, M. V. S. Chandrashekhar, A. Khan, *IEEE Electron Device Lett.* 2017, 38, 914.

- [9] W. C. Lien, N. Damrongplasit, J. H. Paredes, D. G. Senesky, T. J. K. Liu, A. P. Pisano, *IEEE J. Electron Devices Soc.* 2014, 2, 164.

- [10] R. Menozzi, S. Member, G. A. Umana-membreno, B. D. Nener, G. Parish, G. Sozzi, L. Faraone, U. K. Mishra, *IEEE Trans. Device Mater. Reliab.* 2008, 8, 255.

- [11] K. X. Sun, presented at CLEO: 2011 Laser Applications to Photonic Applications, Baltimore, MD, May 2011.

- [12] J. Y. Tsao, S. Chowdhury, M. A. Hollis, D. Jena, N. M. Johnson, K. A. Jones, R. J. Kaplar, S. Rajan, C. G. Van de Walle, E. Bellotti, C. L. Chua, R. Collazo, M. E. Coltrin, J. A. Cooper, K. R. Evans, S. Graham, T. A. Grotjohn, E. R. Heller, M. Higashiwaki, M. S. Islam, P. W. Juodawlkis, M. A. Khan, A. D. Koehler, J. H. Leach, U. K. Mishra, R. J. Nemanich, R. C. N. Pilawa-Podgurski, J. B. Shealy, Z. Sitar, M. J. Tadjer, A. F. Witulski, M. Wraback, J. A. Simmons, *Adv. Electron. Mater.* 2018, *4*, 1600501.

- [13] R. J. Kaplar, A. A. Allerman, A. M. Armstrong, M. H. Crawford, J. R. Dickerson, A. J. Fischer, A. G. Baca, E. A. Douglas, ECS J. Solid State Sci. Technol. 2017, 6, Q306.

- [14] A. G. Baca, A. M. Armstrong, A. A. Allerman, E. A. Douglas, C. A. Sanchez, M. P. King, M. E. Coltrin, T. R. Fortune, R. J. Kaplar, Appl. Phys. Lett. 2016, 109, 33509.

- [15] S. Bajaj, F. Akyol, S. Krishnamoorthy, Y. Zhang, S. Rajan, Appl. Phys. Lett. 2016, 109, 133508.

- [16] S. Muhtadi, S. Hwang, A. Coleman, F. Asif, A. Lunev, M. V. S. Chandrashekhar, A. Khan, Appl. Phys. Lett. 2017, 110, 171104.

- [17] S. Muhtadi, S. M. Hwang, A. L. Coleman, A. Lunev, F. Asif, V. S. N. Chava, M. V. S. Chandrashekhar, A. Khan, *Appl. Phys. Express* 2017, 10, 011004.

- [18] S. Muhtadi, S. Hwang, A. Coleman, F. Asif, A. Lunev, M. V. S. Chandrashekhar, A. Khan, *Appl. Phys. Lett.* 2017, *110*, 193501.

- [19] A. Owens, A. Peacock, Nucl. Instrum. Methods Phys. Res. 2004, 531, 18.

- [20] P. H. Carey, F. Ren, A. G. Baca, B. A. Klein, A. A. Allerman, A. M. Armstrong, E. A. Douglas, R. J. Kaplar, P. G. Kotula, S. J. Pearton, J. Electron Devices Soc. 2019, 7, 444.

- [21] R. Gaska, M. Gaevski, R. Jain, J. Deng, M. Islam, G. Simin, M. Shur, Solid-State Electron. 2015, 113, 22.

- [22] X. Hu, S. Hwang, K. Hussain, R. Floyd, S. Mollah, F. Asif, G. Simin, A. Khan, IEEE Electron Device Lett. 2018, 39, 1568.

- [23] V. Adivarahan, S. Rai, N. Tipirneni, A. Koudymov, J. Yang, G. Simin, M. A. Khan, *Appl. Phys. Lett.* **2006**, *88*, 182507.

- [24] Q. Fareed, V. Adivarahan, M. Gaevski, T. Katona, J. Mei, F. A. Ponce, A. Khan, Jpn. J. Appl. Phys. 2007, 46, L752.

- [25] N. Y. Garces, D. J. Meyer, V. D. Wheeler, Z. Liliental-Weber, D. K. Gaskill, C. R. Eddy, J. Vac. Sci. Technol. B 2013, 32, 03D101.

- [26] J. P. Niemelä, G. Marin, M. Karppinen, Semicond. Sci. Technol. 2017, 32, 093005.

- [27] D. Wei, T. Hossain, N. Y. Garces, N. Nepal, H. M. Meyer, M. J. Kirkham, C. R. Eddy, J. H. Edgar, ECS J. Solid State Sci. Technol. 2013, 2, N110.

- [28] T. J. Anderson, V. D. Wheeler, D. I. Shahin, M. J. Tadjer, A. D. Koehler, K. D. Hobart, A. Christou, F. J. Kub, C. R. Eddy, *Appl. Phys. Express.* 2016, *9*, 071003.

- [29] H. Jiang, C. W. Tang, K. M. Lau, IEEE Electron Device Lett. 2018, 39, 405.

- [30] C. R. English, V. D. Wheeler, N. Y. Garces, N. Nepal, A. Nath, J. K. Hite, M. A. Mastro, C. R. Eddy, J. Vac. Sci. Technol. B 2013, 32, 03D106.

- [31] D. I. Shahin, T. J. Anderson, A. Christou. ECS Trans. 2017, 80, 139.

- [32] J. R. Avila, S. B. Qadri, J. A. Freitas, D. R. Boris, S. G. Walton, C. R. Eddy, V. D. Wheeler, *Chem. Mater.* **2019**, *31*, 3900.

- [33] S. Rai, V. Adivarahan, N. Tipirneni, A. Koudymov, J. Yang, G. Simin, M. A. Khan, Jpn. J. Appl. Phys. 2006, 45, 4985.

- [34] M. A. Khan, G. Simin, J. Yang, J. Zhang, A. Koudymov, M. S. Shur, R. Gaska, X. Hu, A. Tarakji, *IEEE Trans. Microwave Theory Tech.* 2003, 51, 624.

DVANCED

- [35] S. M. Sze, K. K. Nag, Physics of Semiconductor Devices, Wiley, New York, NY 2006.

- [36] S. Mollah, M. Gaevski, M. V. S. Chandrashekhar, X. Hu, V. Wheeler, K. Hussain, A. Mamun, R. Floyd, I. Ahmad, G. Simin, C. Eddy, A. Khan, Semicond. Sci. Technol. 2019, 34, 125001.

- [37] A. M. Ionescu, H. Riel, Nature 2011, 479, 329.

- [38] R. J. Kaplar, A. A. Allerman, A. M. Armstrong, M. H. Crawford, J. R. Dickerson, A. J. Fischer, A. G. Baca, E. A. Douglas, ECS J. Solid State Sci. Technol. 2017, 6, Q3061.

- [39] M. E. Levinshtein, P. A. Ivanov, M. Asif Khan, G. Simin, J. Zhang, X. Hu, J. Yang. Semicond. Sci. Technol. 2003, 18, 666.

- [40] A. G. Baca, B. A. Klein, J. R. Wendt, S. M. Lepkowski, C. N. Nordquist, A. M. Armstrong, A. A. Allerman, E. A. Douglas, R. J. Kaplar, *IEEE Electron Device Lett.* **2019**, *40*, 17.

- [41] B. A. Klein, E. A. Douglas, A. M. Armstrong, A. A. Allerman, V. M. Abate, T. R. Fortune, A. G. Baca, *Appl. Phys. Lett.* **2019**, *114*, 112104.

- [42] X. Z. Dang, P. M. Asbeck, E. T. Yu, G. J. Sullivan, M. Y. Chen, B. T. McDermott, K. S. Boutros, J. M. Redwing, *Appl. Phys. Lett.* **1999**, *74*, 3890.

- [43] A. Aminbeidokhti, S. Dimitrijev, A. Kumar Hanumanthappa, H. A. Moghadam, D. Haasmann, J. Han, Y. Shen, X. Xu, *IEEE Trans. Electron Devices* 2016, 63, 1013.