# A Millimeter-Wave Receiver Using a Wideband Low-Noise Amplifier With One-Port Coupled Resonator Loads

Rahul Singh<sup>®</sup>, *Member, IEEE*, Susnata Mondal<sup>®</sup>, *Student Member, IEEE*, and Jeyanandh Paramesh<sup>®</sup>, *Senior Member, IEEE*

Abstract—This article presents design techniques to facilitate the use of the driving point impedance  $(Z_{11})$  of one-port transformer-coupled resonators as wideband loads of millimeter-wave amplifier stages for a 28-GHz receiver front end. While the use of both the  $Z_{11}$  of a one-port and the transimpedance  $(Z_{21})$  of a two-port coupled resonator is considered to achieve a wideband response, it is shown that under conditions of low magnetic coupling and constrained network quality factor, the use of  $Z_{11}$  can result in a higher gain-bandwidth product of low-noise amplifier (LNA) amplifier stages. The effect of the complex zero in the  $Z_{11}$  response on the in-band gain ripple is shown to be alleviated merely by lowering the quality factor of the transformer's secondary coil; this strongly motivates the use of compact, nested-inductor transformer layouts. Implemented in a 65-nm CMOS process, a three-stage LNA (with  $Z_{11}$  wideband loads in two stages) achieves a 24.4-32.3-GHz bandwidth (27.9 % fractional bandwidth), a peak S<sub>21</sub> of 24.4 dB (20.4 dB), a minimum noise figure (NF) of 4 dB (4.6 dB), and an input-referred P1dB of -23 dBm (-22 dBm) while consuming 22-mW (9.9 mW) power from a 1.1-V (0.85 V) supply. The use of compact transformers limits the LNA's footprint to only 0.12 mm<sup>2</sup>. A 26.5–32.5-GHz quadrature receiver prototype employing the LNA achieves a 29.5-dB peak conversion gain, a 5.3-dB minimum NF, and a -26-dBm inputreferred P1dB while consuming 33 mW from a 1.1-V supply.

Index Terms—Coupled resonators, low-noise amplifier (LNA), millimeter-wave (mm-wave) integrated circuits, receivers, *RLC* circuits, wideband.

# I. INTRODUCTION

PHASED-ARRAY transceivers [1]–[3] are required to overcome path loss and realize advanced multiple-input—multiple-output (MIMO) communication in emerging 5G networks in the 28-/38-GHz bands [4]. Since antenna arrays with high element count are needed, it is important for the transceiver circuits to be compact, scalable and energy-efficient. In particular, wideband low-noise amplifiers (LNAs)

Manuscript received December 6, 2019; revised January 31, 2020; accepted February 29, 2020. This work was supported in part by the National Science Foundation under Grant EECS-1343324 and Grant CCF-1314876. (Corresponding author: Rahul Singh.)

Rahul Singh was with the Department of Electrical and Computer Engineering, Carnegie Mellon University, Pittsburgh, PA 15217 USA. He is now with Qualcomm Inc., San Diego, CA 92121 USA (e-mail: rahusing@qti.qualcomm.com).

Susnata Mondal and Jeyanandh Paramesh are with the Department of Electrical and Computer Engineering, Carnegie Mellon University, Pittsburgh, PA 15217 USA (e-mail: susnatam@andrew.cmu.edu; paramesh@ece.cmu.edu).

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TMTT.2020.2985676

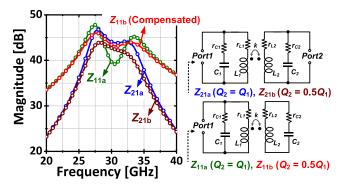

Fig. 1. Comparison of the transimpedance frequency response of a two-port transformer-coupled resonator  $(Z_{21})$  with the frequency response of a ripple-compensated one-port coupled-resonator  $(Z_{11})$  with  $(Q_1=0.5Q_2)$  and without  $(Q_2=Q_1)$  compensation. L=200 pH, C=140.7 fF, k=0.18, and  $Q_1=10$ .  $Q_1$  and  $Q_2$  are the circuit quality factors of the two LC tanks.

that can cover contiguous and/or widely separated narrowband channels of a diverse spectrum [3] with low cost and small die area are of high interest, especially in the 60-GHz [5]-[7] and the 28-GHz bands [3], [8], [9]. Recently, coupled LC resonators have received wide interest in various millimeter-wave (mm-wave) circuits, including LNAs [3], [8]–[10], wide-tuning voltage-controlled oscillators (VCOs) [11], [12], and power amplifiers (PAs) [13], [14]. The resonators can be coupled capacitively, inductively (through an explicit inductor), or magnetically (through a mutual inductance), and each result in a fourth-order transfer function. Magnetic coupling is usually preferred since it results in a lower ripple for a given bandwidth [6]. Recent mm-wave LNAs in this class exclusively use the transimpedance  $(Z_{21})$  of weakly coupled transformer-coupled resonators as wideband loads [3], [5], [6].

In this article, design techniques are introduced to enable the use of the input driving point impedance  $(Z_{11})$  of a one-port coupled resonator as a wideband load. A comparison of the properties of  $Z_{11}$  and  $Z_{21}$  shows that adopting  $Z_{11}$  over  $Z_{21}$  can result in a higher gain-bandwidth (GBW) product if the in-band gain ripple of the  $Z_{11}$  response is adequately tempered. In Section II, it is shown that the  $Z_{11}$  gain ripple has a strong dependence on the quality factor of the transformer's secondary coil, and an effective transformer design technique is introduced to exploit this property. Fig. 1 compares the ripple-compensated  $Z_{11}$  response of a transformer coupled resonator using the proposed technique

0018-9480 © 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

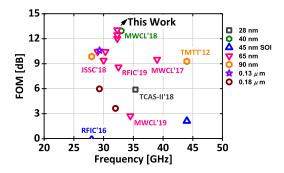

Fig. 2. Comparison of recently published mm-wave CMOS LNAs (<45 GHz).

with the  $Z_{21}$  response—the increase in the GBW product for a similar in-band ripple is evident. A complete receiver using a wideband LNA design based on such ripple-compensated  $Z_{11}$  wideband loads is described in Section III. The characterization results of the 65-nm CMOS prototype are presented in Section IV. Fig. 2 compares the LNA figure of merit<sup>1</sup> (FOM) [6] of the recently reported wideband CMOS LNAs [8], [15]–[28] (only LNAs operating below 45 GHz are considered). The proposed design achieves high FOM and a compact LNA footprint due to the use of nested-inductor transformer layouts. Notably, only [17], implemented in 40-nm CMOS and using spatially offset inductor layouts, achieves comparable FOM but occupies twice the active area.

# II. TRANSFORMER COUPLED-RESONATOR WIDEBAND LOADS

#### A. Coupled-Resonator Analysis

Consider the simplified model of a transformer-coupled resonator, as shown in Fig. 1. Here, the loss of the resonator is modeled using resistances in series with the inductances and capacitances. The following definitions are made:

$$k = \frac{M}{L_1 L_2}, \quad \omega_1 = \frac{1}{\sqrt{L_1 C_1}}, \quad \omega_2 = \frac{1}{\sqrt{L_2 C_2}}, \quad \xi = \left(\frac{\omega_1}{\omega_2}\right)^2.$$

(1)

After discarding the high-frequency zeros, the driving point impedance ( $Z_{11}$ ) and the transimpedance ( $Z_{21}$ ) can be written in the pole-zero form as  $[10]^2$

$$Z_{21}(s) = \frac{sM}{\left(\frac{s^2}{\omega_{p1}^2} + \frac{s}{Q_{p1}\omega_{p1}} + 1\right)\left(\frac{s^2}{\omega_{p2}^2} + \frac{s}{Q_{p2}\omega_{p2}} + 1\right)}$$

$$Z_{11}(s) = \frac{sL_1\left(\frac{s^2}{\omega_{22}^2} + \frac{s}{Q_{z2}\omega_{z2}} + 1\right)}{\left(\frac{s^2}{\omega_{p1}^2} + \frac{s}{Q_{p1}\omega_{p1}} + 1\right)\left(\frac{s^2}{\omega_{p2}^2} + \frac{s}{Q_{p2}\omega_{p2}} + 1\right)}.$$

(2)

<sup>1</sup>The LNA FOM adopted for comparison has been widely used both in the past for narrowband LNAs [29], [30] (where the effect of LNA BW is not considered) as well as in the latest mm-wave research on wideband LNAs [6], [7] (where the effect of LNA BW is included in the FOM calculation).

$^2$ The effect of interwinding capacitance  $C_c$  is omitted here to simplify the analysis. The effect of  $C_c$  on the coupled resonator's frequency response is analyzed rigorously in [5] and [12].

Fig. 3. Definitions of magnitude response parameters.

In (2), the low-frequency zero ( $\omega_{z1}$ ) of  $Z_{11}$  is replaced by a zero at the origin. The quality factors of the complex-conjugate poles can be obtained by a circuit analysis based on successive series—parallel transformations and can be approximated by the following expressions:

$$Q_{p1} = 2\left(\frac{Q_1Q_2}{Q_1 + Q_2}\right)\sqrt{1+k}$$

$$Q_{p2} = 2\left(\frac{Q_1Q_2}{Q_1 + Q_2}\right)\sqrt{1-k}$$

(3)

where  $Q_1$  and  $Q_2$  are the circuit quality factors of the *LC* tanks. The location of the poles can be shown to be [11], [12]

$$\omega_{p1,p2} = \omega_2 \sqrt{\left(\frac{1 + \xi \pm \sqrt{(1 + \xi)^2 - 4\xi(1 - k^2)}}{2(1 - k^2)}\right)}$$

$$\xrightarrow{\xi=1} \omega_{p1,p2} = \frac{\omega_2}{\sqrt{1 \pm k}}.$$

(4)

From (2), it is seen that  $Z_{11}$  has an additional complex-conjugate zero pair, whose frequency and quality factor can be derived as

$$\omega_{z2} = \frac{\omega_2}{\sqrt{1 - k^2}}, \quad Q_{z2} = \frac{Q_1 Q_2 \sqrt{1 - k^2}}{Q_1 + k^2 Q_2} \approx Q_2(\text{low-}k). \quad (5)$$

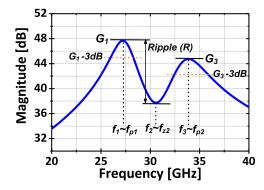

Fig. 3 shows the typical frequency response of magnitudes of  $Z_{11}$  and  $Z_{21}$  of a transformer-coupled resonator. The peak gain magnitudes  $G_1$  and  $G_3$  can be obtained by evaluating (2) at the pole frequencies. Assuming  $\xi = 1$  for simplicity, the following expressions are obtained:

$$G_{1,Z11} = Q_{p1}\omega_{p1}L_1\left(\frac{1+k}{2}\right)\left(1 + \frac{1-k}{k^2Q_{z2}^2}\right)^{1/2}\left(1 + \frac{1-k^2}{4k^2Q_{p2}^2}\right)^{-1/2}$$

$$G_{3,Z11} = Q_{p2}\omega_{p2}L_1\left(\frac{1-k}{2}\right)\left(1 + \frac{1+k}{k^2Q_{z2}^2}\right)^{1/2}\left(1 + \frac{1-k^2}{4k^2Q_{p1}^2}\right)^{-1/2}$$

$$(6)$$

$$G_{1,Z21} = Q_{p1}\omega_{p1}M\left(\frac{1+k}{2k}\right)\left(1+\frac{1-k^2}{4k^2Q_{p2}^2}\right)^{-1/2}$$

$$G_{3,Z21} = Q_{p2}\omega_{p2}M\left(\frac{1-k}{2k}\right)\left(1 + \frac{1-k^2}{4k^2Q_{5,1}^2}\right)^{-1/2}.$$

(7)

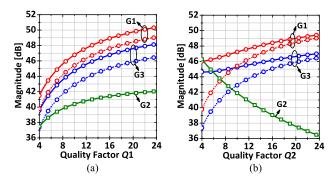

Fig. 4. (a) Primary side Q swept,  $Q_2 = 7.8$ . (b) Secondary side Q swept,  $Q_1 = 12.7$ . The dashed and solid lines represent the magnitude response parameters of  $Z_{21}$  and  $Z_{11}$ , respectively.

Similarly, the magnitude of  $Z_{11}$  at the zero frequency can be written as

$$G_{2,Z11} = \left(\frac{\omega_{p2}L_1(1-k^2)}{Q_{z2}}\right) \left(1 + \frac{1-k}{k^2 Q_{p1}^2}\right)^{-1/2} \left(1 + \frac{1+k}{k^2 Q_{p2}^2}\right)^{-1/2}.$$

(8)

# B. Effect of Quality Factor on GBW Product

In order to achieve high GBW product, the magnitude responses of  $Z_{11}$  and/or  $Z_{21}$  must have three attributes: 1) wide -3-dB bandwidth; 2) high gain; and 3) sufficiently low ripple R. From (4), it is seen that wide bandwidth can be achieved by exploiting the pole-splitting action of a coupled resonator [6] to achieve sufficiently large separation between the poles of the fourth-order system. In order to achieve high gain, the magnitude peaks of  $Z_{11}$  and  $Z_{21}$  ( $G_1$  and  $G_3$  in Fig. 3), which occur roughly at the pole frequencies  $f_{p1}$  and  $f_{p2}$ , must be large. As shown by (6) and (7), these gains increase with the pole quality factors  $Q_{p1}$  and  $Q_{p2}$ , which in turn depend on the quality factors of both primaryand secondary-side resonators, as shown by (3). Flatness of the frequency response within the passband is determined by the difference between gain magnitude  $G_1$  (or  $G_3$ ) and the magnitude  $G_2$  between the two poles, identified as the gain ripple R in Fig. 3. For both  $Z_{11}$  and  $Z_{21}$ ,  $G_2$  can be conveniently approximated as the magnitude at the complex zero frequency  $\omega_{z2}$  of  $Z_{11}$ . Note that the  $Z_{21}$  response does not contain a complex zero and its  $G_2$  magnitude is determined by the gain roll-off responses of the two complex pole pairs. From (4) and (5), it can be observed that  $Z_{11}$ 's complex zero  $\omega_{z2}$  lies between the two complex poles and hence strongly determines  $G_2$ . In particular, the complex zero causes a notch, whose depth increases as the quality factor  $Q_{z2}$  increases.

The earlier observations are illustrated by an example in Fig. 4, where the coupled resonator of Fig. 1 is simulated with  $L_1 = L_2 = 200$  pH, k = 0.15, and  $C_1 = C_2 = 155$  fF. The dependences of the gains  $G_1$ – $G_3$  on  $Q_1$  and  $Q_2$  are plotted in Fig. 4(a) and (b), respectively. Two important conclusions are validated.

1) From (5), it is observed that for low values of k,  $Q_{z2}$  is more strongly affected by the secondary-side quality

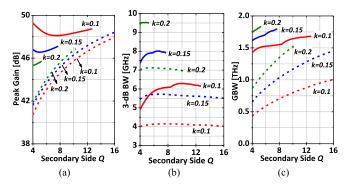

Fig. 5. (a) Peak gain, (b) bandwidth, and (c) GBW for a ripple specification of R = 4 dB. Solid lines represent  $Z_{11}$ , and dashed lines represent  $Z_{21}$ .

- factor  $Q_2$  than the primary-side quality factor  $Q_1$ . Consequently, Fig. 4(a) and (b) reveals that that  $Z_{11}$ 's  $G_2$ [see (8)], which determines the notch depth, varies strongly with the secondary-side  $Q_2$  but is relatively insensitive to the primary-side  $Q_1$ .

- 2) It is also observed that the gain magnitudes  $G_1$  and  $G_3$  of  $Z_{11}$  show a stronger dependence on  $Q_1$  than  $Q_2$ . This contrasts with the behavior of  $Z_{21}$  pole gains  $G_1$  and  $G_3$ , which shows an equally strong dependence on both  $Q_1$  and  $Q_2$ . This observation is validated by (6), where we see that when compared to  $Z_{21}$  expressions in (7), the expressions for  $Z_{11}$ 's  $G_1$  and  $G_3$  contain an additional term dependent on  $Q_{z2}$  (and hence on  $Q_2$ ), which tempers the otherwise strong dependence of these pole magnitudes on  $Q_2$ .

The above mentioned two points lead to a key observation that is exploited in our LNA prototype presented in Section III; the gain ripple in  $Z_{11}$ 's response can be controlled by using moderate values of  $Q_2$  while maintaining sufficiently large values of  $G_1$  and  $G_3$ . In other words, even though the quality factor of the secondary coil is reduced to compensate for the  $Z_{11}$  ripple, the impact on  $Z_{11}$ 's GBW is limited.

#### C. Ripple-Compensated $Z_{11}$ Versus $Z_{21}$

Given a ripple specification R, the GBW of  $Z_{11}$  can be made larger than that of  $Z_{21}$ . This is because ripple compensation by reducing  $Q_2$  still results in high values of  $G_1$  and  $G_3$ , and outside the passband,  $Z_{21}$  has steeper stopband skirts (see Fig. 1) when compared to  $Z_{11}$  which lowers its -3-dB bandwidth. The much steeper upper stopband slope of  $Z_{21}$ , when compared to  $Z_{11}$ , is due to the absence of a complex zero between the poles. Using the Bode plots, it can be deduced that the  $Z_{11}$  response has stopbands that roll off at -20 dB/decade (the upper stopband slope is sum of +20, -40, +40, and -40 dB/decade due to  $\omega_{z1}$ ,  $\omega_{p1}$ ,  $\omega_{z2}$ , and  $\omega_{p2}$ , respectively). On the other hand, the  $Z_{21}$  response will have a -20-dB/decade slope in the lower stopband (due to the zero) and a -60-dB/decade slope in the upper stopband (sum of +20, -40, and -40 dB/decade due to zero at the origin,  $\omega_{p1}$ , and  $\omega_{p2}$ , respectively).

Fig. 5 shows the effect of reducing  $Q_2$  on the GBW and the peak gains for  $Z_{11}$  and  $Z_{21}$  for different values of k.

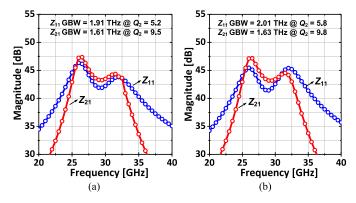

Fig. 6. (a)  $Z_{11}$  and  $Z_{21}$  magnitude response with R=4 dB, where  $L_1=L_2=200$  pH, k=0.2, and  $C_1=C_2=155$  fF. (b) Magnitude response with unequal resonant frequencies ( $\xi=1.06$ ), where  $C_1=150$  fF,  $C_2=160$  fF, and  $Q_1=12.7$ , to equalize gain peaks G1 and G3 in the  $Z_{11}$  response.

A ripple specification R = 4 dB is chosen in this example, which imposes a maximum value of  $Q_2$  beyond which a single concurrent band can no longer be assumed. Note that this definition is somewhat arbitrary and is assumed here for illustrative purposes, and the validity of the analysis below remains unaltered by choosing a different specification for the ripple constraint. In these simulations,  $L_1 = L_2 = 200$  pH, k = 0.2, and  $C_1 = C_2 = 155$  fF. The primary-side quality factor is set to  $Q_1 = 12.7$ , which is a reasonable value at 28 GHz considering the losses of both the inductor and capacitor. It is clear that for different values of k, higher peak gain, bandwidth, and GBW can be consistently achieved with  $Z_{11}$  when compared with  $Z_{21}$ . Fig. 6(a) plots the magnitude response of  $Z_{11}$  and  $Z_{21}$ , given the 4-dB ripple constraint, for a k of 0.2. It is observed that the maximum GBWs of 1910 and 1607 GHz are achieved for  $Z_{11}$  and  $Z_{21}$  at  $Q_2 = 5.2$  and 9.5, respectively. A further advantage of using  $Z_{11}$  is that the zero frequency  $\omega_{z2}$  can be adjusted to achieve equal gain peaks  $G_1$  and  $G_2$ . By choosing unequal tank resonant frequencies ( $\xi \neq 1$ ) through unequal primary- and secondary-side capacitances,  $\omega_{z2}$  in the  $Z_{11}$  response can be positioned either close to  $\omega_{p1}$  ( $\xi > 1$ ) or close to  $\omega_{p2}$  ( $\xi < 1$ ). An example is shown in Fig. 6(b), where  $\xi$  is set to 1.06 to equalize the  $Z_{11}$  gain peaks. The  $Z_{21}$  response lacks a complex zero and hence lacks this responsiveness to  $\xi$ .

For designs that use  $Z_{11}$ , certain disadvantages should be noted at this juncture. Here, the transconductor and the load circuits are both connected to the primary side of the coupled resonator, and therefore, their capacitances appear in parallel with the primary-side inductor. This limits the budget allowed for an external (possibly tunable) capacitance that is typically necessary to achieve design margin and tunability. On the other hand, in designs that use  $Z_{21}$ , the transconductor and load circuit capacitances appear across that primary and secondary sides, respectively. Therefore, a higher budget is available for the insertion of explicit tuning capacitors on each side. The ability to separate the transconductor and load capacitances can be very beneficial in applications where these capacitances are typically large, for example, the driver stages of a PA [13], [14]. However, in an mm-wave LNA amplifier operating around 28 GHz, which is the focus of this article,

Fig. 7. Cascaded gain stages using (a)  $Z_{11}$  and (b)  $Z_{21}$  wideband loads.

these capacitances are much smaller, and a  $Z_{11}$  wideband load with tunable capacitors is as easily realized as a  $Z_{21}$  load. In designs using  $Z_{21}$ , the secondary inductor can be used to bias the succeeding stage; however, ac-coupling capacitors and bias resistors are necessary when using a  $Z_{11}$  wideband load. Finally, while both  $Z_{11}$  and  $Z_{21}$  can serve as wideband loads in both single-ended and differential implementations, a  $Z_{21}$  load can also conveniently interface between a single-ended first stage and succeeding differential stages [3], [8], [9], [17].

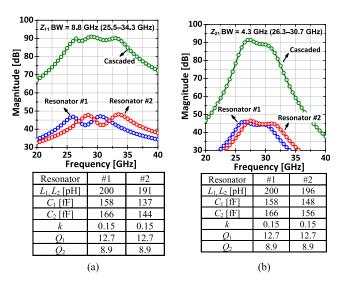

## D. Stagger-Tuned Cascaded Gain Stages

To simultaneously achieve high gain and large fractional bandwidth at mm-wave frequencies, gain stages with low-k coupled-resonator loads should be cascaded and stagger-tuned such that higher ripple (often greater than 3 dB) can be tolerated in each stage [15]. This is illustrated using an example in Fig. 7 where two stagger-tuned  $Z_{21}$  and  $Z_{11}$  responses of two cascaded stages are compared. The GBW advantage of  $Z_{11}$  is again clearly evident; the overall  $Z_{11}$  response achieves a bandwidth nearly twice that of the  $Z_{21}$  response while achieving similar peak gains. It should be noted that since  $Z_{21}$  has steeper skirts in the transition band, it exhibits higher group delay in the passband. However, it was observed that by stagger-tuning stages, it is possible to obtain a reasonably flat group delay profile in the passband with both  $Z_{11}$  and  $Z_{21}$  wideband loads.

# III. WIDEBAND RECEIVER DESIGN

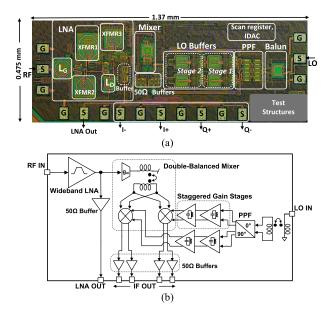

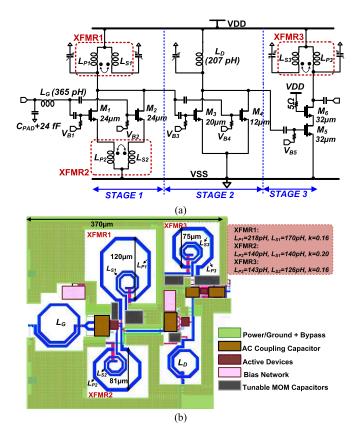

The previously discussed techniques were applied to design a wideband LNA that was used in a quadrature receiver front end. Fig. 8 shows the die photograph and the block diagram of the receiver, designed in a 65-nm CMOS technology.

#### A. Wideband Low-Noise Amplifier

The proposed wideband LNA design employs three gain stages, as shown in Fig. 9(a). The first stage comprises two inductively generated common-source (CS) legs—M1 and M2,

Fig. 8. (a) Die photograph and (b) block diagram of the receiver chip in 65-nm CMOS.

Fig. 9. (a) Circuit schematic and (b) layout floorplan of the three-stage LNA. All transistors are of minimum length (60 nm).

degenerated by source inductors  $L_{P2}$  and  $L_{S2}$ . In contrast to conventional inductive degeneration, weak coupling is introduced between the two inductors ( $k \sim 0.2$ ), laid out in nested configuration to save area. The two CS legs are designed to be symmetrical with identical transistor sizes (24  $\mu$ m) and degenerating inductances (142 pH). To avoid the noise penalty, a cascode transistor was not used. The first stage

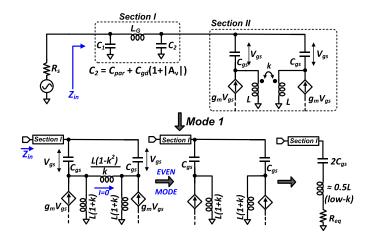

Fig. 10. Equivalent circuit model of the input matching network. Note that in mode 1, Section II only has an "even" mode of operation due to symmetry and reduces to a series-*RLC* resonant circuit.

employs a coupled-resonator load (XFMR1) comprising a nested transformer and a combination of fixed and switched metal-oxide-metal (MOM) capacitors in the primary and secondary ports; design details of nested transformers and the MOM capacitors are described in Section III-C. The second CS stage comprises two transistors M3 and M4 in parallel with a simple LC resonator load; this stage serves to correct the droop in the frequency response of the first stage. The third cascode stage (transistors M5 and M6) uses another coupled-resonator load (XFMR3) whose frequency response staggered-tuned with respect to the first stage to extend the overall bandwidth. Each of the CS transistors (M1-M5) was biased through a digitally controlled current DAC, thereby allowing independent control of the parallel CS branches in stages 1 and 2. The design of the LNA is typically governed by the need to accommodate large input signals due to the presence of large interferers. In this design, higher linearity configurations can be enabled by turning off parts of the first and second stages, which facilitates linearity to be traded for noise and voltage gain. In Mode #1, all transistors are ON, whereas in Mode #2, M<sub>1</sub>-M<sub>3</sub>-M<sub>4</sub> are ON and M<sub>2</sub> is turned off. In Mode #3, only  $M_1$  and  $M_4$  are ON, whereas  $M_2$  and M<sub>3</sub> are turned off.

The layout floorplan of the LNA is shown in Fig. 9(b). A low-impedance power/ground routing network (using stacked metal layers) is integrated on top of multiple small bypass capacitor elements and distributed throughout the layout. This approach minimizes the parasitic impedances in the ac current loops through the bypass capacitances of each LNA stage and the ground return paths. Transformer layouts with nested inductors (see Section III-C) enable a compact layout (370  $\mu$ m  $\times$  325  $\mu$ m) and help to shorten the high-frequency interconnects.

#### B. Input Matching

A good input match should be maintained in all operating modes. This is ensured by an approach described next with reference to Fig. 10, which shows the equivalent circuit of the input matching network. The input network is partitioned

Fig. 11. (a) Offset and (b) nested low-k transformer.

into two sections to facilitate analysis. The first section is a  $\pi$ -network comprising the gate inductor  $L_{\varrho}$  and capacitances,  $C_1$  and  $C_2$ .  $C_1$  is the total capacitance from the input pads, trace, and an explicit 24-fF capacitor, whereas  $C_2$  represents the trace parasitics and the Miller-multiplied gate-to-drain capacitance  $(C_{gd})$  of the first stage CS transistors. The second section comprises the CS stage with transformer source degeneration. When one half of CS stage is OFF (i.e., Mode #2), the second section reduces to a series-RLC resonant circuit. In Mode #1, when both CS stages are ON, the transformer in the source can be replaced by the  $\pi$ -equivalent network. Since the two partitions of the input CS stage were designed to be symmetric, no current flows through the cross inductor in the  $\pi$ -network, and the network again reduces to a second-order system. Cascading the low-Q  $\pi$ -network with a low-Q series-RLC second section, as shown in Fig. 10, results in wideband input matching [15]. Furthermore, the presence of the  $\pi$ -network reduces the value of the gate inductance required for input matching [31]. However, reverse signal flow through the Miller-multiplied  $C_{gd}$  due to the absence of a cascode transistor in the first stage causes the fourth-order response of the first-stage load to modify the input match. Nevertheless, since  $S_{11} \sim -10$  dB was observed in all three modes, no additional wideband input matching techniques were employed.

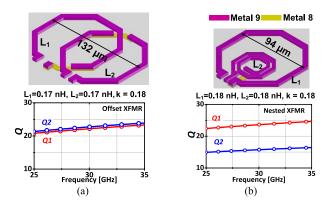

#### C. Transformer Layout and Tunable MOM Capacitors

In order to minimize die area, transformer-coupled resonators that achieve the requisite low k but are compact are necessary. A common approach to design for low k is to have spatially offset inductors [5], [6], [8], [15]; in this case, both coils exhibit similar Qs [see Fig. 11(a)]. However, the area penalty can be severe for low-k designs. Therefore, nested layouts were used in this design, as shown in Fig. 11(b). Since  $L_1 \approx L_2$ ,  $L_2$  has two turns, whereas  $L_1$  has a single turn, and low values of k can be achieved. Due to pronounced current-crowding effects in multiturn inductors, the secondary coil has a smaller Q than the primary coil. A key advantage of the nested layout is that a lower secondary coil Q is consistent with the ripple compensation technique described in Section II-B and can be readily used to realize wideband  $Z_{11}$ loads. Moreover, the overall area of the transformer remains the same as that of a single-turn inductor.

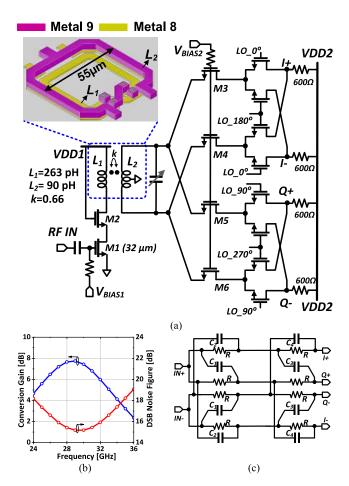

Fig. 12. (a) Circuit schematic and (b) simulated CG and DSB NF of the double-balanced mixer (IF frequency = 1 GHz). (c) Circuit schematic of the two-stage wideband PPF ( $R=150.3~\Omega,~C_1=38.5~\mathrm{fF},~C_2=36.9~\mathrm{fF},~C_3=30.7~\mathrm{fF},~\mathrm{and}~C_4=29.7~\mathrm{fF}).$

Custom interdigitated MOM capacitors were designed using the fifth, sixth, and seventh metal layers (each 0.22  $\mu$ m thick) of the nine-metal process. The single-ended switched MOM capacitor banks were implemented with 15-fF switched MOM unit capacitor cells (density  $\sim 0.63$  fF/ $\mu$ m<sup>2</sup>) in series with a 12- $\mu$ m NMOS switch (25- $\Omega$   $R_{\rm ON}$ ). The OFF-state capacitance of this unit cell was 7.2 fF, thus achieving a  $C_{\rm ON}/C_{\rm OFF}$  ratio of  $\sim$ 2. The ON- and OFF-state Qs of the unit cell were simulated to be 14 and 54, respectively (at 30 GHz).

# D. RF Mixer and I/Q LO Generation

An active double-balanced Gilbert cell mixer was used in this design [see Fig. 12(a)]. The first stage, a single-ended transconductor  $(g_m)$ , is coupled to the switching quad through a single-ended to differential balun. Additional common-gate transistors were inserted between the secondary winding of the balun and the switching quad to improve RF-to-LO isolation. The use of a balun decouples the dc current of the switching stage from that of the  $g_m$ -stage, which allows for a higher load resistance at the output of the mixer and, consequently, a higher conversion gain (CG) [2]. The simulated CG of the mixer was 7.7 dB at 28 GHz [see Fig. 12(b)] while consuming  $\sim$ 11 mA of current. The mixing stage was followed by 50- $\Omega$  IF buffers to drive the instrument load. Also, an additional

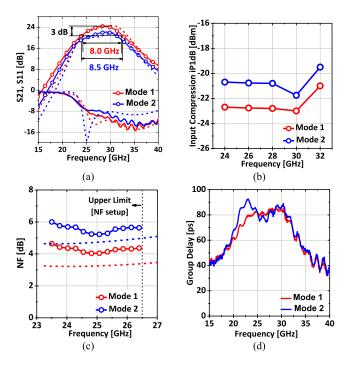

Fig. 13. LNA measurement results. (a)  $S_{21}$  and  $S_{11}$ , (b) variation of input-referred 1-dB compression point (iP1dB) with RF frequency, (c) variation of NF with RF frequency, and (d) group delay variation. Simulated  $S_{21}$ ,  $S_{11}$ , and NF are shown with dashed lines.

measurement buffer was added at the output of the LNA to facilitate the standalone characterization.

To simplify the measurement setup, quadrature LO signals for the mixer were generated on-chip using an external sinusoidal LO signal source. An input balun provided input matching and converted the single-ended LO input to a differential signal. A two-stage polyphase filter (PPF) followed the balun. Layout and parasitic compensation techniques, introduced in [32], were followed to improve the PPF's I/Q accuracy over a wide bandwidth. The circuit schematic is shown in Fig. 12(c). To compensate for the high signal loss in the two-stage PPF, two differential staggered-gain stages followed the PPF, which ensured a reasonable voltage swing at the mixer inputs. The image rejection ratio (IRR) of the LO path was simulated to be better than 29 dB between 25 and 32 GHz.

# IV. MEASUREMENT RESULTS

#### A. Breakout LNA Measurements

The LNA was measured in each of its three modes at its nominal 1.1-V  $V_{\rm DD}$  and also at reduced  $V_{\rm DD}$  of 0.95 and 0.85 V. Fig. 13(a) shows the measured and simulated gain ( $S_{21}$ ) and input match ( $S_{11}$ ) of the LNA, respectively. The simulated loss of the measurement buffer was deembedded from the measurement. The addition of the measurement buffer and the presence of a long interconnection between the LNA and the mixer resulted in a slight reduction in bandwidth. Good correlation between the simulations and measurements was observed. The in-band input match was better than -7.5 dB.

The linearity of the LNA was characterized through its input-referred input compression point (iP1dB). Fig. 13(b) shows the improvement in the linearity performance of the

LNA between Mode #1 and Mode #2. At an RF frequency of 28 GHz, iP1dB in Mode #1and Mode #2 were measured to be -23 and -21 dBm, respectively. The iP1dB in Mode #3 was measured to be -19 dBm; however, this mode was not further characterized as the LNA NF was measured to be higher than expected (6.2 dB).

The variation of the LNA's NF with RF frequency is shown in Figs. 13(c). A Noisecom NC346V noise source in conjunction with an Agilent E4440A spectrum analyser was used for NF measurement. Due to the upper frequency limit of the measurement setup, the NF could only be measured up to 26.5 GHz. In the low-NF Mode #1 of operation, a minimum NF of 4 dB was observed at 25 GHz. Over 55% reduction in power was observed in the low-power mode (0.85-V supply). The use of local current mirrors (sharing the LNA VDD) resulted in lowering of transistor biases at reduced supply voltages, thereby further reducing the power. The group-delay variation in Mode #1 was measured to be  $73 \pm 13$  ps over the -3-dB bandwidth, as shown in Fig. 13(d).

# B. Comparison With LNA State of the Art

A summary of the LNA performance and benchmarking against similar work is provided in Table I. The LNA demonstrates a best-case FOM<sub>1</sub> [6], [7], [33], [34] of 12.94 dB, highest among similar designs, while occupying the smallest area. FOM<sub>1</sub>, expressed in dB, adds the impact of LNA bandwidth to the FOM in [29] and [30]. To include the effect of linearity, FOM<sub>2</sub> can be used [17]. Unlike FOM<sub>1</sub>, FOM<sub>2</sub> is not expressed in dB to avoid negative values. The definitions of FOM1 and FOM2 are noted in Table I. A few LNAs reported in Table II have higher values of FOM<sub>2</sub>, but they are either single-stage designs with low gain [19], [23], [25], [26] or operate at a higher supply voltage [19], [15]. Recent mm-wave LNAs operating beyond 60 GHz have reported FOMs as high as 18 dB [6] and 16 dB [7]. However, these LNAs have been implemented in the 28- and 22-nm CMOS processes where lower transistor parasitics, higher transistor cutoff frequencies  $(f_T)$ , and transconductance efficiencies facilitate high FOMs. Furthermore, due to the low quality factor of integrated on-chip capacitors beyond 50 GHz [35], amplifier designs at these frequencies avoid using switched MOM capacitors, and inductors and transformers are often designed to resonate only with the parasitic capacitances [6]. This limits post-fabrication tunability but enables higher GBW compared with the designs at 28 GHz, such as in this article, where explicit capacitors are necessary to provide tunability and avoid very large inductor sizes. It should be noted that it is difficult for a single FOM or performance metric to capture the intricacies or the advantages of a new design; therefore, Table II lists several other pertinent metrics such as output-referred P1dB (oP1dB), fractional bandwidth, and the GBW product in addition to FOM<sub>1</sub>, FOM<sub>2</sub>, and the common LNA performance parameters of gain, -3-dB and fractional bandwidth, noise figure (NF), and power consumption.

## C. Receiver Measurements

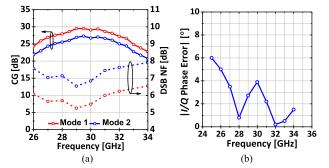

The receiver was measured with the LNA configured in its different modes. Fig. 14(a) shows the measured CG and

TABLE I

MEASUREMENT RESULTS AND COMPARISON WITH STATE-OF-THE-ART mm-WAVE LNAs

|                                                                                                                                                                                                                     | Technology        | Number of<br>Stages,<br>Topology   | VDD<br>[V] | Freq<br>[GHz]                          | Peak<br>S <sub>21</sub><br>[dB] | NF min<br>[dB]   | iP <sub>IdB</sub><br>[dBm] | Power<br>[mW]     | OP <sub>IdB</sub> <sup>4</sup><br>[dBm] | GBW<br>[THz] | Area<br>[mm²] | FBW<br>[%] | FOM <sub>1</sub><br>[dB] | FOM <sub>2</sub><br>[GHz] |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------|------------|----------------------------------------|---------------------------------|------------------|----------------------------|-------------------|-----------------------------------------|--------------|---------------|------------|--------------------------|---------------------------|

|                                                                                                                                                                                                                     |                   | 1 0,                               |            | LNA                                    |                                 | 45 GHz           |                            |                   |                                         |              |               |            |                          |                           |

|                                                                                                                                                                                                                     |                   | 3 (SE*), 2 CS<br>stages, 1 Cascode | 1.1        |                                        | 24.4                            | $4.0^{1}$        | -23 <sup>2</sup>           | $22^{3}$          | 0.4                                     | 0.131        | 0.12          |            | 11.91                    | 0.18                      |

| Mode 1                                                                                                                                                                                                              | 65 nm CMOS        |                                    | 0.95       | 24.4-32.3                              | 22.3                            | 4.41             | -23 <sup>2</sup>           | 14 <sup>3</sup>   | -1.7                                    | 0.103        |               | 27.9       | 12.45                    | 0.19                      |

| (T                                                                                                                                                                                                                  | (This work)       |                                    | 0.85       |                                        | 20.4                            | 4.6 <sup>1</sup> | -22 <sup>2</sup>           | 9.9 <sup>3</sup>  | -2.6                                    | 0.083        |               |            | 12.94                    | 0.26                      |

| Mode 2                                                                                                                                                                                                              |                   |                                    | 1.1        | 24.0-32.5                              | 22.1                            | 5.21             | -21 <sup>2</sup>           | 19.3 <sup>3</sup> | 0.1                                     | 0.108        | 30.1          | 7.70       | 0.18                     |                           |

| [16] TCAS-II'18                                                                                                                                                                                                     | 28 nm LP CMOS     | 2 (SE), Cascode                    | 1.2        | 33±2.35                                | 18.6                            | 4.9              | -25.5                      | 9.7               | -7.9                                    | 0.040        | 0.23          | 14.2       | 5.89                     | 0.05                      |

| [17] MWCL'18                                                                                                                                                                                                        | 40 nm CMOS        | 3, 1 SE CS, 2<br>DIFF <sup>#</sup> | 1.1        | 26-33                                  | 27.1                            | 3.3              | -21.6                      | 31.4              | 4.5                                     | 0.159        | 0.26          | 23.7       | 12.95                    | 0.28                      |

| [18] GSMM'18                                                                                                                                                                                                        | 45 nm SOI         | 3 (SE), Cascode                    | 1.1        | 24-44                                  | 20                              | 4.2              | -19                        | 58                | 0                                       | 0.200        | 0.2           | 58.8       | 6.53                     | 0.24                      |

| [19] RFIC'16                                                                                                                                                                                                        | 45 nm SOI         | 1, Cascode                         | 1.5        | 24-28                                  | 8.5                             | 2.8              | -4                         | 12                | 3.6                                     | 0.011        | _             | 15.4       | 0.00                     | 3.60                      |

| [20] RFIC'19                                                                                                                                                                                                        | 65 nm CMOS        | 2, 1 DIFF CS, 1<br>DIFF Cascode    | 1.2        | 24.9-32.5                              | 18.33                           | 3.25             | -24                        | 20.5              | -6.7                                    | 0.064        | 0.11          | 26.5       | 8.60                     | 0.10                      |

| [21] MWCL'19                                                                                                                                                                                                        | 65 nm CMOS        | 2, Cascode                         | 1.5        | 30-34.5                                | 20.8                            | 3.71             | -20.4                      | 26.7              | -0.6                                    | 0.049        | -             | 14.0       | 2.73                     | 0.11                      |

| [8] JSSC'18<br>(Simulated)                                                                                                                                                                                          | 65 nm CMOS        | 2, 1 CG, 1 DIFF<br>CS              | 1.0        | 25-30                                  | 18                              | 3.7              | -12.45                     | 10                | 4.6                                     | 0.040        | 0.135         | 18.2       | 9.40                     | 1.55                      |

| [22] MWCL'17                                                                                                                                                                                                        | 65 nm CMOS        | 2 (SE), Cascaded<br>CG and CS      | 1.0        | 7.6-29                                 | 10.7                            | 4.5              | -8.2                       | 12.1              | 1.5                                     | 0.073        | 0.23          | 116.9      | 10.45                    | 4.60                      |

| [23] MWCL'17                                                                                                                                                                                                        | 65 nm CMOS        | 1 (SE), Cascode                    | _          | 15.8-30.3                              | 10.2                            | 3.3              | -10.1                      | 12.4              | -0.9                                    | 0.047        | 0.18          | 62.9       | 10.45                    | 2.96                      |

| [24] MWCL'13                                                                                                                                                                                                        | 65 nm CMOS        | 3 (SE), 2 CS, 1<br>Cascode         | ı          | 2.1-39                                 | 11.5                            | 4.5              | -15.3                      | 25.5              | -6.5                                    | 0.139        | 0.16          | 179.6      | 9.51                     | 0.81                      |

| [25] TMTT'12                                                                                                                                                                                                        | 90 nm LP CMOS     | 1 (SE), Cascode                    | 1.2        | 29–44                                  | 13.8                            | 3.8              | -10                        | 18                | 1.7                                     | 0.073        | 0.48          | 41.2       | 9.28                     | 2.66                      |

| [26] TMTT'10                                                                                                                                                                                                        | 90 nm CMOS        | 1, Cascode                         | 1.2        | 1.6-28                                 | 10.7                            | 3.7              | -9                         | 21.6              | 0.7                                     | 0.09         | $0.14^{6}$    | 178.4      | 9.86                     | 3.58                      |

| [27]<br>Springer'15                                                                                                                                                                                                 | 0.13 μm CMOS      | 2 (SE), Cascaded<br>CG and CS      | 1.2        | 17.3-29.3                              | 18                              | 4.7              | >-20.65                    | 14.4              | -3.6                                    | 0.095        | 0.19          | 51.5       | 10.60                    | 0.27                      |

| [28] TMTT'11                                                                                                                                                                                                        | 0.18 μm CMOS      | 3 (SE), CS                         | -          | 14.3-29.3                              | 9.9                             | 4.3              | -12                        | 13.9              | -3.1                                    | 0.047        | 0.54          | 68.8       | 6.02                     | 1.15                      |

| [15] JSSC'09                                                                                                                                                                                                        | 0.18 μm<br>BiCMOS | 2 (SE), 1 CS, 1<br>Cascode         | 1.5        | 23-32                                  | 12                              | 4.5              | >-15.9 <sup>5</sup>        | 13                | -4.9                                    | 0.036        | 0.25          | 32.7       | 3.64                     | 0.36                      |

| LNAs above 45 GHz                                                                                                                                                                                                   |                   |                                    |            |                                        |                                 |                  |                            |                   |                                         |              |               |            |                          |                           |

| [6] JSSC'17                                                                                                                                                                                                         | 28 nm CMOS        | 4, 1 DIFF CG, 3<br>DIFF CS         | 0.9        | 68.1-96.4                              | 29.6                            | 6.4              | -28.1                      | 31.3              | 0.5                                     | 0.855        | 0.25          | 34.4       | 18.18                    | 0.11                      |

| [7] RFIC'18                                                                                                                                                                                                         | 22 nm CMOS        | 2 (SE), CS                         | 0.9        | 68.1 <b>-</b> 96.4<br>68.6 <b>-</b> 79 | 18<br>20                        | 7.8<br>4         | -12.1<br>-22.8             | 11.7<br>10.8      | 4.7<br>-3.8                             | 0.255        | 0.155         | 14.1       | 16.08                    | 2.05<br>0.30              |

| [33] JSSC'17                                                                                                                                                                                                        | 65 nm CMOS        | 3 (SE), Cascode                    | 1.2        | 63.5-91                                | 13.3                            | 6.4              | -9.8                       | 12                | 2.5                                     | 0.127        | 0.24          | 35.6       | 9.70                     | 2.92                      |

|                                                                                                                                                                                                                     |                   |                                    | 1.8        | 62.5-92.5                              | 18.5                            | 5.5              | -19.5                      | 27                | -2.0                                    | 0.252        |               | 38.7       | 11.29                    | 0.38                      |

| [34] JSSC'17                                                                                                                                                                                                        | 65 nm CMOS        | 4 (SE), CS                         | 1.0        | 54.5-90                                | 17.7                            | 5.4              | -11.7                      | 19                | 1.3                                     | 0.273        | 0.37          | 49.1       | 15.31                    | 1.53                      |

| Measured up to 26.5 GHz, ${}^{2}$ Measured at 28 GHz, ${}^{3}$ Excludes the LNA buffer, ${}^{4}$ Approximated as $(Gain_{dB} - 1) + iP_{1dB}$ when measurement result not available, ${}^{5}$ Calculated from IIP3, |                   |                                    |            |                                        |                                 |                  |                            |                   |                                         |              |               |            |                          |                           |

Measured up to 26.5 GHz, <sup>2</sup>Measured at 28 GHz, <sup>3</sup>Excludes the LNA buffer, <sup>4</sup> Approximated as (Gain<sub>dB</sub> – 1) + iP<sub>1dB</sub> when measurement result not available, <sup>5</sup>Calculated from IIP3 fincluding pads. \*Single-ended, \*Differential.

$$FBW[\%] = \left(\frac{\text{BW}}{f_c}\right) \times 100, \ f_c \text{ is the center of the -3-dB bandwidth.} \ FoM_1[\text{dB}] = 20\log_{10}\left(\frac{\text{Gain}_{\text{lin}} \cdot \text{BW}_{\text{[GHz]}}}{(F-1) \cdot P_{\text{dc[mW]}}}\right); \ FoM_2[\text{GHz}] = \frac{\text{Gain}_{\text{lin}} \cdot \text{BW}_{\text{[GHz]}} \cdot iP_{\text{ldB[mW]}}}{(F-1) \cdot P_{\text{dc[mW]}}}, F=\text{Noise Factor.}$$

TABLE II

RECEIVER MEASUREMENT RESULTS

|                                                                                                   | VDD<br>[V] | Freq<br>[GHz] | CG<br>(Max) [dB] | NF min<br>DSB [dB] |     | Power [mW] <sup>2</sup> | I/Q<br>Phase<br>Error <sup>3</sup> |  |

|---------------------------------------------------------------------------------------------------|------------|---------------|------------------|--------------------|-----|-------------------------|------------------------------------|--|

| Mode 1                                                                                            | 1.1        | 26.5-32.5     | 29.5             | 5.3                | -28 | 33                      | < 5°                               |  |

|                                                                                                   | 0.95       |               | 27.0             | 5.7                | -27 | 22.3                    |                                    |  |

|                                                                                                   | 0.85       |               | 24.7             | 6.5                | -26 | 16.7                    | ≥ 3                                |  |

| Mode 2                                                                                            | 1.1        | 26.5-32.5     | 27.3             | 6.5                | -25 | 30.4                    |                                    |  |

| Measured at 28 GHz, <sup>2</sup> Excludes IF Buffer, <sup>3</sup> Measured at a low IF of 50 MHz. |            |               |                  |                    |     |                         |                                    |  |

the DSB NF. A maximum CG of 29.5 dB and a minimum DSB NF of 5.3 dB were measured in Mode #1. The output IF buffer's loss was deembedded from the measurement results. In the receiver's low-power mode, where the LNA

Fig. 14. Receiver measurement results. (a) CG (IF = 1 GHz) and DSB NF (IF = 2 GHz). (b) I/Q phase mismatch (absolute) measured at the IF output at a low IF frequency of 50 MHz.

operates in Mode #1 at a reduced  $V_{\rm DD}$  of 0.85 V, a peak CG of 24.7 dB and a minimum DSB NF of 6.5 dB were measured.

When the receiver is configured to operate in its Mode #2, an improvement of 3 dB in the measured iP1dB is observed over Mode #1. The receiver achieved an RF bandwidth of 6 GHz between 26.5 and 32.5 GHz. Reduction in the RF bandwidth of the receiver, compared with the LNA, can be attributed to the nonwideband design of the mixer's  $g_m$ -stage. The measured IF bandwidth was 2.5 GHz, limited by the pole at the mixer's output.

The quadrature phase error of the LO path with the wideband PPF was also estimated by measuring the phase difference between the I+ and Q+ IF outputs. Note that the LO phase error appears directly at the IF output, whereas the LO gain error is mostly rejected by the mixer at sufficiently large LO amplitudes. To minimize the contributions from the signal path layout mismatches and the measurement setup to the LO I/Q phase error, the measurement was carried out at a low IF of 50 MHz. The I/Q phase error, shown in Fig. 14(b), was measured to be smaller than  $5^{\circ}$  in the 26-33-GHz band. The gain imbalance was smaller than 0.32 dB. These measurement results are summarized in Table II.

#### V. CONCLUSION

This article describes the design of a wideband receiver in 65-nm CMOS. A compact, wideband, reconfigurable LNA using the driving-point impedance ( $Z_{11}$ ) of one-port transformer-coupled resonators is described. Design guidelines and insights are presented for the use of  $Z_{11}$  as a wideband load. Nested-layout transformers are shown to simultaneously minimize area and flatten the  $Z_{11}$  response. The effectiveness of the proposed techniques is demonstrated through the measurements of a 28-GHz quadrature receiver prototype and its constituent LNA.

#### REFERENCES

- [1] R. W. Heath, Jr., N. Gonzalez-Prelcic, S. Rangan, W. Roh, and A. M. Sayeed, "An overview of signal processing techniques for millimeter wave MIMO systems," *IEEE J. Sel. Topics Signal Process.*, vol. 10, no. 3, pp. 436–453, Apr. 2016.

- [2] S. Kundu and J. Paramesh, "A compact, supply-voltage scalable 45–66 GHz baseband-combining CMOS phased-array receiver," *IEEE J. Solid-State Circuits*, vol. 50, no. 2, pp. 527–542, Feb. 2015.

- [3] S. Mondal, R. Singh, A. I. Hussein, and J. Paramesh, "A 25-30 GHz 8-antenna 2-stream hybrid beamforming receiver for MIMO communication," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2017, pp. 112–115.

- [4] (Apr. 2017). 5G Spectrum Recommendations. [Online]. Available: https://www.5gamericas.org/files/9114/9324/1786/5GA\_5G\_Spectrum\_ Recommendations\_2017\_FINAL.pdf

- [5] V. Bhagavatula, T. Zhang, A. R. Suvarna, and J. C. Rudell, "An ultra-wideband IF millimeter-wave receiver with a 20 GHz channel bandwidth using gain-equalized transformers," *IEEE J. Solid-State Circuits*, vol. 51, no. 2, pp. 323–331, Feb. 2016.

- [6] M. Vigilante and P. Reynaert, "On the design of wideband transformer-based fourth order matching networks for E-band receivers in 28-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 52, no. 8, pp. 2071–2082, Aug. 2017.

- [7] W. Shin, S. Callender, S. Pellerano, and C. Hull, "A compact 75 GHz LNA with 20 dB gain and 4 dB noise figure in 22nm FinFET CMOS technology," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2018, pp. 284–287.

- [8] S. Mondal, R. Singh, A. I. Hussein, and J. Paramesh, "A 25–30 GHz fully-connected hybrid beamforming receiver for MIMO communication," *IEEE J. Solid-State Circuits*, vol. 53, no. 5, pp. 1275–1287, May 2018.

- [9] S. Mondal, R. Singh, and J. Paramesh, "A reconfigurable 28/37 GHz hybrid-beamforming MIMO receiver with inter-band carrier aggregation and RF-domain LMS weight adaptation," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 72–74.

- [10] R. Singh, S. Mondal, and J. Paramesh, "A compact digitally-assisted merged LNA vector modulator using coupled resonators for integrated beamforming transceivers," *IEEE Trans. Microw. Theory Techn.*, vol. 67, no. 7, pp. 2555–2568, Jul. 2019.

- [11] A. Bevilacqua, F. P. Pavan, C. Sandner, A. Gerosa, and A. Neviani, "Transformer-based dual-mode voltage-controlled oscillators," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 54, no. 4, pp. 293–297, Apr. 2007.

- [12] G. Li, L. Liu, Y. Tang, and E. Afshari, "A low-phase-noise wide-tuning-range oscillator based on resonant mode switching," *IEEE J. Solid-State Circuits*, vol. 47, no. 6, pp. 1295–1308, Jun. 2012.

- [13] S. V. Thyagarajan, A. M. Niknejad, and C. D. Hull, "A 60 GHz drain-source neutralized wideband linear power amplifier in 28 nm CMOS," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 61, no. 8, pp. 2253–2262, Aug. 2014.

- [14] S. Mondal, R. Singh, and J. Paramesh, "21.3 a reconfigurable bidirectional 28/37/39 GHz front-end supporting MIMO-TDD, carrier aggregation TDD and FDD/Full-duplex with self-interference cancellation in digital and fully connected hybrid beamformers," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2019, pp. 348–350.

- [15] M. El-Noza, E. Sanchez-Sinencio, and K. Entesari, "A millimeter-wave (23–32 GHz) wideband BiCMOS low-noise amplifier," *IEEE J. Solid-State Circuits*, vol. 45, no. 2, pp. 289–299, Feb. 2010.

- [16] M. Keshavarz Hedayati, A. Abdipour, R. Sarraf Shirazi, C. Cetintepe, and R. B. Staszewski, "A 33-GHz LNA for 5G wireless systems in 28-nm bulk CMOS," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 65, no. 10, pp. 1460–1464, Oct. 2018.

- [17] M. Elkholy, S. Shakib, J. Dunworth, V. Aparin, and K. Entesari, "A wideband variable gain LNA with high OIP3 for 5G using 40-nm bulk CMOS," *IEEE Microw. Wireless Compon. Lett.*, vol. 28, no. 1, pp. 64–66, Jan. 2018.

- [18] V. Chauhan and B. Floyd, "A 24–44 GHz UWB LNA for 5G cellular frequency bands," in *Proc. 11th Global Symp. Millim. Waves (GSMM)*, May 2018, pp. 1–3.

- [19] U. Kodak and G. M. Rebeiz, "A 42 mW 26–28 GHz phased-array receive channel with 12 dB gain, 4 dB NF and 0 dBm IIP3 in 45 nm CMOS SOI," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2016, pp. 348–351.

- [20] S. Kong, H.-D. Lee, S. Jang, J. Park, K.-S. Kim, and K.-C. Lee, "A 28-GHz CMOS LNA with stability-enhanced Gm-boosting technique using transformers," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2019, pp. 4–7.

- [21] S. Lee, J. Park, and S. Hong, "A Ka-band phase-compensated variable-gain CMOS low-noise amplifier," *IEEE Microw. Wireless Compon. Lett.*, vol. 29, no. 2, pp. 131–133, Feb. 2019.

- [22] P. Qin and Q. Xue, "Design of wideband LNA employing cascaded complimentary common gate and common source stages," *IEEE Microw. Wireless Compon. Lett.*, vol. 27, no. 6, pp. 587–589, Jun. 2017.

- [23] P. Qin and Q. Xue, "Compact wideband LNA with gain and input matching bandwidth extensions by transformer," *IEEE Microw. Wireless Compon. Lett.*, vol. 27, no. 7, pp. 657–659, Jul. 2017.

- [24] C. Feng, X. P. Yu, W. M. Lim, and K. S. Yeo, "A compact 2.1–39 GHz self-biased low-noise amplifier in 65 nm CMOS technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 23, no. 12, pp. 662–664, Dec. 2013.

- [25] H.-C. Yeh, C.-C. Chiong, S. Aloui, and H. Wang, "Analysis and design of millimeter-wave low-voltage CMOS cascode LNA with magnetic coupled technique," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 12, pp. 4066–4079, Dec. 2012.

- [26] H.-K. Chen, Y.-S. Lin, and S.-S. Lu, "Analysis and design of a 1.6–28-GHz compact wideband LNA in 90-nm CMOS using a π-match input network," *IEEE Trans. Microw. Theory Techn.*, vol. 58, no. 8, pp. 2092–2104, Aug. 2010.

- [27] S. Kundu and J. Paramesh, "A transformer-neutralized 0.6 V V<sub>DD</sub> 17–29 GHz LNA and its application to an RF front-end," Analog Integr. Circuits Signal Process., vol. 83, no. 2, pp. 173–186, May 2015.

- [28] Y.-T. Lo and J.-F. Kiang, "Design of wideband LNAs using parallel-to-series resonant matching network between common-gate and common-source stages," *IEEE Trans. Microw. Theory Techn.*, vol. 59, no. 9, pp. 2285–2294, Sep. 2011.

- [29] J. Borremans, P. Wambacq, C. Soens, Y. Rolain, and M. Kuijk, "Low-area active-feedback low-noise amplifier design in scaled digital CMOS," *IEEE J. Solid-State Circuits*, vol. 43, no. 11, pp. 2422–2433, Nov. 2008.

- [30] M. Parlak and J. F. Buckwalter, "A 2.9-dB noise figure, Q-band millimeter-wave CMOS SOI LNA," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Sep. 2011, pp. 1–4.

- [31] A. Mazzanti, M. Sosio, M. Repossi, and F. Svelto, "A 24 GHz subharmonic direct conversion receiver in 65 nm CMOS," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 1, pp. 88–97, Jan. 2011.

- [32] S. Kulkarni, D. Zhao, and P. Reynaert, "Design of an optimal layout polyphase filter for millimeter-wave quadrature LO generation," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 60, no. 4, pp. 202–206, Apr. 2013.

- [33] G. Feng et al., "Pole-converging intrastage bandwidth extension technique for wideband amplifiers," *IEEE J. Solid-State Circuits*, vol. 52, no. 3, pp. 769–780, Mar. 2017.

- [34] Y. Yu, H. Liu, Y. Wu, and K. Kang, "A 54.4–90 GHz low-noise amplifier in 65-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 52, no. 11, pp. 2892–2904, Nov. 2017.

- [35] E. Mammei, E. Monaco, A. Mazzanti, and F. Svelto, "A 33.6-to-46.2 GHz 32 nm CMOS VCO with 177.5 dBc/Hz minimum noise FOM using inductor splitting for tuning extension," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2013, pp. 350–351.

Susnata Mondal (Student Member, IEEE) received the B.Tech. and M.Tech. degrees in electronics engineering from IIT Kharagpur, Kharagpur, India, in 2015. He is currently pursuing the Ph.D. degree in electrical and computer engineering at Carnegie Mellon University, Pittsburgh, PA, USA.

In 2013, he joined RWTH Aachen University, Aachen, Germany, as a Research Intern. From 2014 to 2015 and from 2016 to 2019, he was a Teaching Assistant with IIT Kharagpur and Carnegie Mellon University, respectively. His current research

interests include millimeter-wave circuit designs for emerging fifth-generation (5G) applications.

Mr. Mondal was a recipient of the DAAD WISE Fellowship in 2013, the Institute Proficiency Prize—the Best B.Tech. Project Award at IIT Kharagpur in 2014, the Analog Devices Outstanding Student Designer Award in 2017, and the IEEE Solid-State Circuits Society Predoctoral Achievement Award in 2019.

Rahul Singh (Member, IEEE) received the B.Tech. degree in electronics engineering from IIT (BHU) Varanasi, Varanasi, India, in 2008, the M.S. degree from Seoul National University, Seoul, South Korea, in 2011, and the Ph.D. degree in electrical engineering from Carnegie Mellon University, Pittsburgh, PA, USA, in 2018.

From 2011 to 2013, he was with the Processor Development Group, Samsung Electronics, Gyeonggi-do, South Korea. He was a Research Intern with Maxlinear Inc., Carlsbad, CA, USA, in

2017, where he worked on the design of GaN power amplifiers. In 2018, he joined Qualcomm Inc., San Diego, CA, USA, where he is currently working on circuit design of 4G/5G cellular transceivers.

Dr. Singh was a recipient of the Samsung Global Scholarship between 2009 and 2011, and the Analog Devices Outstanding Student Designer Award in 2015.

Jeyanandh Paramesh (Senior Member, IEEE) received the B.Tech. degree in electrical engineering from IIT Madras, Chennai, India, the M.S. degree in electrical engineering from Oregon State University, Corvallis, OR, USA, and the Ph.D. degree in electrical engineering from the University of Washington, Seattle, WA, USA.

He has held product development and research positions at AKM Semiconductor (Analog Devices), Motorola, and Intel. He is currently an Adjunct Professor of electrical and computer engineering

with Carnegie Mellon University, Pittsburgh, PA, USA. His current research interests include the design of RF and mixed-signal integrated circuits and systems for a wide variety of application.