# Saturation-Volume Estimation for Multisegment Copper Interconnect Wires

Zeyu Sun, *Student Member, IEEE*, Sheriff Sadiqbatcha, *Student Member, IEEE*, Hengyang Zhao, *Student Member, IEEE*, and Sheldon X.-D. Tan<sup>®</sup>, *Senior Member, IEEE*

Abstract—Recently, many physics-based electromigration (EM) models have been proposed to mitigate the overconservativeness of existing Black-Blech-based EM models. To assess EM failures, one needs to estimate how the void grows after the nucleation phase. As a result, it is important to estimate the saturation volume of a void, which is important for EM mortality check. The existing saturation void volume model only works for a single wire segment. In this paper, we propose a new model for fast estimation of the void's saturation volume for general multisegment interconnect wires. The new model is based on the fundamental atom conservation at the steadystate condition of void growth phases. The new formula agrees with the existing saturation void volume formula for the singlesegment wire case and is a natural extension of the single-segment case to general multisegment wires. In addition, we consider the impacts of the void volume on final stress distributions of the wire to further improve the accuracy of the proposed formula. Based on the new formula, we propose a new EM immortality check flow, which considers both the recently proposed EM immortality in the void nucleation phase and the void saturation volume in the growth phase. The new flow can further reduce the conservativeness of the existing EM failure effect analysis. The numerical results show that the proposed formula agrees well with a published work for two-segment cases, which are supported by experimental data. The formula is also validated by the recently proposed physics-based 3-D finite-element (FEM) analysis tool for general multisegment interconnect wires. We also demonstrate new EM immortality check flow to quickly identify the new type of immortal wires, which are nucleated but with smaller-than-critical voids.

*Index Terms*—Electromigration, FEM, immortality check, reliability, saturation volume.

# I. INTRODUCTION

ELECTROMIGRATION (EM) is one of the top reliability concerns of copper-based back-end-of-the-line interconnects, both for current and future ICs in 10-nm technology and below. 2015 ITRS interconnect predicts that EM lifetime of interconnects in VLSI chips will be reduced by half for each generation of nodes [1]. This is

Manuscript received September 28, 2018; revised December 30, 2018; accepted February 8, 2019. Date of publication March 15, 2019; date of current version June 26, 2019. This work was supported in part by the National Science Foundation (NSF) under Grant CCF-1527324 and Grant CCF-1741961 and in part by the Defense Advanced Research Projects Agency under Grant HR0011-16-2-0009. (Corresponding author: Sheldon X.-D. Tan.)

Z. Sun, S. Sadiqbatcha, and S. X.-D. Tan are with the Department of Electrical and Computer Engineering, University of California at Riverside, Riverside, CA 92521 USA (e-mail: stan@ee.ucr.edu).

H. Zhao is with Google, Inc., Mountain View, CA 94043 USA.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TVLSI.2019.2901824

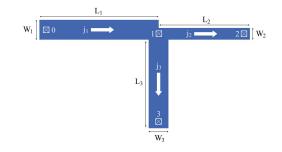

Fig. 1. Illustration of a multisegment interconnect wire structure.

primarily due to increasing current densities and shrinking wire line cross sections, which determine the critical sizes for EM effects. On the other hand, many applications ranging from automatic electronics to medical devices and aerospace equipment require a very long lifetime and have very demanding reliability requirements. As a result, testing and verification of the reliability, specially EM-reliability, of VLSI chips used in those applications become critical.

Recently, a number of physics-based EM models and assessment techniques have been proposed [2]-[14]. These EM models are primarily based on the hydrostatic stress diffusion kinetics in the confined metal wires and, therefore, have a more accurate time to failure estimation for general interconnect wires over a wide range of stress conditions. Furthermore, all these models consider a multiphase EM process. Most of these works focus on the nucleation phase before the void formed and many of them just assume void will grow in a constant speed. However, in the postvoiding phase, the void will grow into the so-called saturated volume in the steady state. Although methods exist for fast saturation-volume estimation of two-segment wires [15]), no such methods exist for general multisegment interconnect structures, such as the one shown in Fig. 1. The saturation-volume estimation of a void is important for determining the immortality of multisegment interconnect wires (especially with reservoirs) in the steady state.

In this paper, we propose a new formula for fast estimation of the void's saturation volume for general multisegment interconnect wires. The new formula is based on the fundamental atom conservation at the steady-state condition of void growth phases. The new void saturation estimation formula agrees with the existing single-segment wire saturation void volume formula and is a natural extension of the single-segment case to general multisegment wires. In addition, we consider the impacts of the void volume on final stress distributions of the wire to further improve the accuracy of the proposed formula. The proposed saturation void volume estimation can be applied for fast EM immortality check for nucleated wires,

1063-8210 © 2019 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

which were considered to be failed wires in the past. Combined with the recently proposed EM immortality check for nucleation [8], [13], we propose a new EM immortality check algorithm, which considers both void nucleation and void growth for the first time, thus overcoming the conservativeness of the existing EM immortality check method. Our numerical results show that the proposed formula agrees well with a published work for two-segment cases, which are supported by experimental data. The formula is also validated by the recently proposed physics-based 3-D finite element (FEM) analysis tool for general multisegment interconnect wires. We also demonstrate that the new EM immortality check flow can quickly identify the new type of immortal wires, which are nucleated but with smaller-than-critical voids.

This paper is organized as follows. Section II reviews the recently proposed physics-based EM model and points out the lack of fast saturation-volume estimation methods in the existing EM models for multisegment interconnects. Section III introduces the new saturation-volume estimation method and formula. This section starts with the review of the existing saturation-volume estimation for single wire segment. Section IV presents the new EM immortality check flow that considers both nucleation and void growth for the first time. Section V presents accuracy analysis of the proposed models against a published work for two-segment wires and against the 3-D finite-element analysis (FEM) results. Section VI concludes this paper.

# II. REVIEW OF EM PHYSICS AND STRESS MODELING

# A. Review of EM Physics and Stress Modeling

EM is a physical phenomenon of the migration of metal atoms along the direction of the applied electrical field. Atoms (ether lattice atoms or defects/impurities) migrate along the trajectory of conducting electrons. During the migration process, hydrostatic stress is generated inside the embedded metal wire due to momentum exchange between lattice atoms. Over time, void and hillock formation is caused by conducting electrons at the opposite ends of the wire. Indeed, when metal wire is passivated into a rigid confinement, which is the case for copper dual damascene structure, the wire volume changes (induced by the atom depletion and accumulation due to migration) and creates tension at the cathode end and compression at the anode end of the line.

Mathematically, transient hydrostatic stress evolution due to EM effects in confined metal  $\sigma(x, t)$  before void is formed can be described by Korhonen's equation [16]

$$\frac{\partial \sigma}{\partial t} = \frac{\partial}{\partial x} \left[ \kappa \left( \frac{\partial \sigma}{\partial x} + G \right) \right], \quad \text{at } 0 < t < t_{\text{nuc}}$$

$$BC : \frac{\partial \sigma}{\partial x}(0, t) = -G, \text{ at } 0 < t < t_{\text{nuc}}$$

$$BC : \frac{\partial \sigma}{\partial x}(L, t) = -G, \text{ at } 0 < t < t_{\text{nuc}}$$

(1)

where  $\kappa = D_a B \Omega/kT$ , T is the absolute temperature, k is Boltzmann's constant, B is the effective bulk elasticity modulus, and  $G = (eZ\rho j/\Omega)$ , where e is the electron charge, eZ is the effective charge of the migrating atoms,  $\Omega$  is the

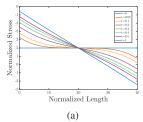

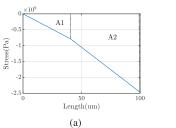

Fig. 2. (a) EM-stress distribution change over time in a simple metal wire. (b) EM-stress evaluation versus time.

atomic volume,  $\rho$  is the wire electrical resistivity, and j is the current density.

Fig. 2(a) shows stress development over time in a metal line with Korhonen's equation. Over time, tensile (positive) stress will develop at the cathode (left) node and compressive (negative) stress will develop at the anode (right) node. The stress changes polarity in the middle of the wire. The built-up stress (its gradient) will serve as the counter force for atomic flux. Fig. 2(b) shows stress evolution on the cathode, which reaches a steady state over time. If the highest stress at the cathode node exceeds the critical stress, voids will be created. The time to reach the critical stress is called nucleation time ( $t_{\text{nuc}}$ ). After the void is nucleated, it will begin to grow, consequently raising the wire resistance.

However, partial differential equations from those models have to be solved using numerical methods, which make them less efficient for fast EM assessment. To resolve this issue, a physics-based EM model has recently been proposed [3], [6], [12]. Those models, however, mainly work for the void nucleation phases. Many of them simply ignore the void growth phase or just use a simple linear model for the growth phase. Actually, it is more complicated than it appears. The void will grow until it reaches the saturation volume, which was less studied in the past especially for the general multisegment interconnect wires. These methods often result in immortal wires being identified as mortal, consequently making the design overly conservative. A model which can estimate saturation volume and determine immortality correctly is, therefore, required.

# III. NEW VOID SATURATION-VOLUME ESTIMATION FOR GENERAL MULTISEGMENT WIRE

# A. Review of the Void Saturation Volume for Single Segment

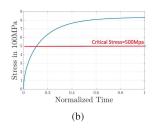

As previously mentioned, computing the saturation void volume at steady state is critical for the immortality check of a wire. After a void is formed in a segment, the tensile (positive) stress around the void will gradually reduce to zero and the stress distribution will become compressive (negative), as shown in Fig. 3.

From the physics perspective, once a void is formed, the void volume  $V_v(t)$  in a multisegment wire will satisfy the following atom conservation equation [17]:

$$V_{v}(t) = -\int_{\Omega_{t}} \frac{\sigma(t)}{B} dV \tag{2}$$

Fig. 3. Typical stress evolution on a  $30-\mu m$  copper wire computed by the finite-element analysis.

where  $\Omega_L$  is the volume of the remaining interconnect wire. Here, W is the width of the wire and h is the thickness of the wire. In the steady state, the stress is compressive and negative. As a result, there is a negative sign in (2). For the 1-D single-segment case with wire length L, the steady-state saturation volume ( $V_{\rm sat}$ ) of the void becomes

$$V_{\text{sat}} = -A \int_0^L \frac{\sigma(x)}{B} dx = -\frac{A\sigma_{\text{max}}L}{2B}$$

(3)

where  $\sigma_{\rm max}$  is the maximum stress in steady state and A is its cross-sectional area which can be calculated by  $A=W\times h$ . Since the length of the void is typically much smaller than the length of the wire (smaller than 1% of the segment), total length L is used here instead of the length of the remaining interconnect without the void. Another formula considering the length of remaining interconnect will be discussed in Section III-B.

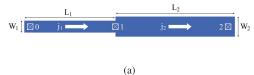

If we only consider the one-segment wire in the 1-D case as shown in Fig. 4(a), (3) essentially says that the saturation volume depends on the product of  $\sigma_{\text{max}}$  and L. If we plot the stress versus the length for this one-segment case, the product actually is the area A1 in Fig. 4(b). Such observation is important as it will lead us to the solution for the multisegment case shown later.

To compute  $\sigma_{max}$ , we need to go back to Korhonen's equation, in the steady state, in which we have

$$\frac{\partial \sigma}{\partial x} = \frac{\sigma_{\text{max}}}{L} = -\frac{j\rho e Z^*}{2\Omega}$$

$$\sigma_{\text{max}} = -\frac{j\rho e Z^* L}{2\Omega} = -\frac{\mathcal{V}e Z^*}{2\Omega}$$

(4)

where  $\mathcal{V}=j\times L\times \rho$  is the branch/node voltage between the cathode and anode of the wire which was also used to represent the immortality condition here. For a single wire segment, Blech's criterion or Blech limit is defined as  $(jL)_{\rm crit}=(\Omega(\sigma_{\rm crit}-\sigma_{\rm init})/eZ\rho)$ , where  $\sigma_{\rm crit}$  is the critical stress and  $\sigma_{\rm init}$  is the initial stress in the wire. As we can see, the immortality condition of a wire  $(jL<(jL)_{\rm crit})$  depends on the product of j (current density) and L (length). The Blech limit can also be actually written as  $(jL)_{\rm crit}*\rho=\mathcal{V}_{\rm crit}=(\Omega(\sigma_{\rm crit}-\sigma_{\rm init})/eZ)$ . As a result, the immortality criteria can be further written in terms of critical branch voltage  $\mathcal{V}_{\rm crit}$ . Recent study shows that using the branch voltage for immortality check will

Fig. 4. (a) One-segment wire and the direction indicate electron flow. (b) Stress integration area of a one-segment wire.

become much more convenient than current density for the multisegment case, as shown in [8] and [13].

Using (3) and (4), we get

$$V_{\text{sat}} = \frac{Aj\rho eZ^*L^2}{2\Omega B} = \frac{A\mathcal{V}eZ^*L}{2\Omega B}$$

(5)

where A is the cross-sectional area of the wire:  $A = W \times h$ . If we have the initial stress distribution, then

$$V_{\text{init}} = \frac{A\sigma_{\text{init}}L}{B}.$$

(6)

Therefore, void saturation volume,  $V_{\text{sat}}$ , for a single wire can be expressed as

$$V_{\text{sat}} = A \left( \frac{\sigma_{\text{init}} L}{B} + \frac{j \rho e Z^* L^2}{2\Omega B} \right) = A \left( \frac{\sigma_{\text{init}} L}{B} + \frac{\mathcal{V} e Z^* L}{2\Omega B} \right) (7)$$

which agrees exactly with [18]. However, this method only works for 1-D single wires.

#### B. Proposed Void Saturation Volume for Multisegment Wires

In this paper, we propose a formula to estimate the saturation volume for general multisegment interconnect wires where each wire segment may have different widths.

Before we present this paper, we would like to remark that void volume depends on many factors, such as shape and location. The void location and shapes are stochastic in nature and depend on the capping and barrier materials used and the fabrication process. The void shape also keeps changing over time and the void itself may migrate as well during the growth process [19], [20]. As a result, it is very difficult to completely consider all those effects. With all the modeling works, we have to make some assumptions based on the fundamental physics of EM effects and wire structures. Specifically, in this paper, we assume that the void has a square shape initially and eventually will grow to occupy a cross section of the wire with moving edges toward the atom migration direction. Eventually, the void shape will become the shape of a wire or via section [14]. For the void position,

Fig. 5. (a) Two-segment wire and the direction indicate electron flow. (b) Stress integration area of a two-segment wire.

statistically, the void most likely nucleates in or close to the cathode node of the wire. For the copper dual damascene wire structure, if the via is not blocked by the void, the resistance does not increase. Therefore, the volume above the via can be recognized as the critical void volume (void fatal volume) [21], [22].

As mentioned earlier, the void is typically formed around the cathode node of the wire. Since tensile stress at the cathode is the highest part of the wire, stress at this position exceeds the critical stress first and void formation starts here. However, experimental data indeed show that voids can also form somewhere near the cathode nodes [23]. But, the location of the voids will not significantly affect the saturation-volume estimation, as the steady-state compressive stress distributions of the wires will be similar if the void location with zero stress is not far away from the cathode node. If void volume occupies the significant portion of the wire, zero stress location may not be very close to the cathode. But in this case, the wire will be mortal anyway and the estimation of saturation volume is less important.

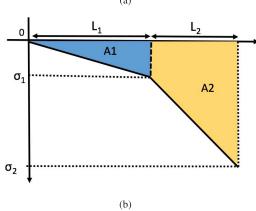

Based on the previous observation, for the multisegment case, based on (3), the saturation volume will be equal to the area under the multisegment wires (A1 + A2), as shown in Fig. 5 for a two-segment case with equal widths. As a result, the saturation volume can be boiled down to computing those areas as shown in the following.

In general, for a single segment [such as  $L_1$  from Fig. 5(a)], the stress between the cathode and the anode can be expressed as

$$\sigma_c - \sigma_a = \frac{(\mathcal{V}_a - \mathcal{V}_c)eZ}{\Omega} = \frac{jL\rho eZ}{\Omega}$$

(8)

where  $\sigma_c$  and  $\sigma_a$  represent the stress on the cathode and the anode, respectively, and  $V_c$  and  $V_a$  represent the voltages on the cathode and the anode respectively. At the steady state, the stress is linearly distributed on the metal wire as shown by the shaded areas in Fig. 5(b). Since we need to consider the width

of each segment, which may be different, the problem becomes a 2-D stress-area integration problem. Then, the contribution from the steady-state void volume,  $V_{\text{sat},i}$ , for a segment i, can be found by computing the stress areas (width times length of the wire)

$$V_{\text{sat},i} = h \times ((-\sigma_{c,i}) + (-\sigma_{a,i})) \times \frac{L_i W_i}{2B}$$

$$= h \times \left(-2\sigma_{c,i} + \frac{V_i eZ}{\Omega}\right) \times \frac{L_i W_i}{2B}$$

$$= h \times \left(-2\sigma_{c,i} + \frac{j_i L_i \rho eZ}{\Omega}\right) \times \frac{L_i W_i}{2B}$$

(9)

where  $V_i$ ,  $j_i$ ,  $L_i$ , and  $W_i$  are the voltage difference between anode and cathode, current density, length, and width of the ith segment, respectively. h is the thickness of the wire, which is the same for all the wire segments.  $\sigma_{c,i}$  is the steady-state stress on the cathode of segment i, which becomes 0 where the void is nucleated. We note that except for the segment with the void, steady-state stress on the cathode node of other segments is actually the anode of the segment connected to them.

Total void volume at steady state will be calculated, which is essentially the void saturation volume, given the steady-state void volume contribution from segment i,  $V_{\text{sat},i}$  in (9). The total void volume can be calculated by adding all the contributions together based on (2). Then, we have the following results.

Proposition 1: For a general multisegment wire, assume that a void is formed in the cathode node of one of the segments and all the initial stress are zero. Then, the saturation volume of the void  $V_{\rm sat,total}$  can be computed as

$$V_{\text{sat,total}} = \sum_{i} V_{\text{sat},i} = h \times \sum_{i} \left( -2\sigma_{c,i} + \frac{V_{i}eZ}{\Omega} \right) \times \frac{L_{i}W_{i}}{2B}$$

$$= h \times \sum_{i} \left( -2\sigma_{c,i} + \frac{j_{i}L_{i}\rho eZ}{\Omega} \right) \times \frac{L_{i}W_{i}}{2B}$$

(10)

where  $V_{\text{sat},i}$  defined in (9) represents the saturation-volume contribution from the *i*th segment. If a nonzero initial stress is considered, we can add the initial stress contributions, as shown in (7).

Equation (10) shows that the saturation volume is a quadratic function of wire segment lengths and a linear function of wire width in the interconnect trees. As a result, the saturation volume can be adjusted or controlled by wire width and length sizing.  $V_{\text{sat,total}}$  is smaller than the critical volume, and resistance will not increase. So the interconnect tree can be considered as immortal in this case. And the interconnect tree would fail if the saturation volume is larger than the critical volume.

However, since a void is formed at the cathode of the main branch, the length of the main branch is reduced. In order to have a better accuracy, a reduced main branch with the length of  $\hat{L}_m$  is used in the calculation. Since the final saturation volume affects the remaining length of the main branch, which further impacts the final saturation volume, iterations are required to compute the final results. But for our method,

Fig. 6. Stress distribution for the two-segment wire at steady state.

we only iterate once, which is sufficient as we show later. Thus, a new formula is as follows:

$$\hat{L}_{m} = L_{m} - \frac{V_{\text{sat,total}}}{hW_{m}}$$

$$\hat{V}_{\text{sat,total}} = h \times \sum_{i \neq m} \left( -2\hat{\sigma}_{c,i} + \frac{V_{i}eZ}{\Omega} \right) \times \frac{L_{i}W_{i}}{2B}$$

$$+ h \times \left( \frac{V_{m}eZ}{\Omega} \right) \times \frac{\hat{L}_{m}W_{m}}{2B}$$

$$= h \times \sum_{i \neq m} \left( -2\hat{\sigma}_{c,i} + \frac{j_{i}L_{i}\rho eZ}{\Omega} \right) \times \frac{L_{i}W_{i}}{2B}$$

$$+ h \times \left( \frac{j_{m}\hat{L}_{m}\rho eZ}{\Omega} \right) \times \frac{\hat{L}_{m}W_{m}}{2B}. \tag{11}$$

Note that the  $\sigma_{c,i}$  also changes to  $\hat{\sigma}_{c,i}$  since the stress on main branch changes. In the following, we go through a few example to illustrate the new formula (10). The first example is a three-terminal wire shown in Fig. 5. Here, stress at nodes 1 and 2 can be expressed as

$$\sigma_{1} = 0 - \frac{(\mathcal{V}_{1} - 0)eZ}{\Omega} = -\frac{j_{1}L_{1}\rho eZ}{\Omega}

\sigma_{2} = -\sigma_{1} - \frac{(\mathcal{V}_{2} - \mathcal{V}_{1})eZ}{\Omega} = -\frac{(j_{1}L_{1} + j_{2}L_{2})\rho eZ}{\Omega}.$$

(12)

Fig. 6 shows calculated stress at steady state during the growth phase. The stress estimation agrees with the results in (12). As a result, the void saturation can be computed as

$$V_{\text{sat,2seg}} = h \times \frac{-\sigma_1 L_1 W_1 + (-\sigma_1 - \sigma_2) W_2 L_2}{2B}$$

$$= h \times \left( \frac{j_1 L_1^2 W_1 \rho e Z}{2B\Omega} + \frac{(2j_1 L_1 + j_2 L_2) L_2 W_2 \rho e Z}{2B\Omega} \right). \tag{13}$$

If we consider the void volume effect using (11), the reduced main branch length  $\hat{L}_1$  can be calculated by

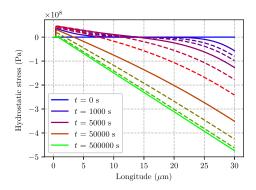

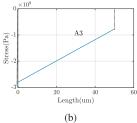

Fig. 7. T-shaped wire. Arrows: electron flow.

Fig. 8. (a) Stress on horizontal segment 0–2. (b) Stress on vertical segment 1–3.

$V_{\text{sat,2seg}}$  in (13)

$$\hat{L}_{1} = L_{1} - \frac{V_{\text{sat}}}{hW_{1}}$$

$$\hat{V}_{\text{sat,2seg}} = h \times \frac{-\hat{\sigma}_{1}L_{1}W_{1} + (-\hat{\sigma}_{1} - \hat{\sigma}_{2})W_{2}L_{2}}{2B}$$

$$= h \times \left(\frac{j_{1}\hat{L}_{1}^{2}W_{1}\rho eZ}{2B\Omega} + \frac{(2j_{1}\hat{L}_{1} + j_{2}L_{2})L_{2}W_{2}\rho eZ}{2B\Omega}\right).$$

(14)

For the other example, we will consider the T-intersection shown in Fig. 7. In this case, a void will be formed at node 0, and stress at other nodes can be calculated as

$$\sigma_{1} = -\frac{\mathcal{V}_{1}eZ}{\Omega} = -\frac{j_{1}L_{1}\rho eZ}{\Omega}$$

$$\sigma_{2} = \sigma_{1} - \frac{(\mathcal{V}_{2} - \mathcal{V}_{1})eZ}{\Omega} = -\frac{(j_{1}L_{1} + j_{2}L_{2})\rho eZ}{\Omega}$$

$$\sigma_{3} = \sigma_{1} - \frac{(\mathcal{V}_{3} - \mathcal{V}_{1})eZ}{\Omega} = -\frac{(j_{1}L_{1} + j_{3}L_{3})\rho eZ}{\Omega}. \quad (15)$$

Fig. 8 shows stress at steady state during the growth phase. Here, the saturation void volume can be calculated as

$$V_{\text{sat,3seg}} = h \times \frac{-\sigma_1 L_1 W_1 + (-\sigma_1 - \sigma_2) L_2 W_2}{2B\Omega} + \frac{(-\sigma_1 - \sigma_3) L_3 W_3}{2B} = h \times \left(\frac{j_1 L_1^2 W_1 \rho e Z}{2B\Omega} + \frac{(2j_1 L_1 + j_2 L_2) L_2 W_2 \rho e Z}{2B\Omega} + \frac{(2j_1 L_1 + j_3 L_3) L_3 W_3 \rho e Z}{2B\Omega}\right).$$

(16)

We can also consider volume effects by converting  $L_1$  to  $\hat{L}_1$ , as shown in (11), to improve the simulation accuracy.

In order to validate this model, we validate the estimated saturation void volume with a recently proposed 3-D FEM analysis tool [14], [24]. This tool employs the stress model in [16], the current density model, as well as the Joule heating-induced temperature model in the FEM-based analysis method for void growth simulation. This model has high accuracy with the FEM analysis; hence, we use it to validate the model proposed in this paper. The validation results are shown in Section V.

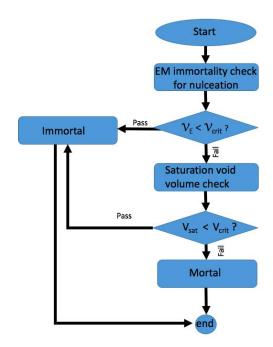

#### IV. NEW EM IMMORTALITY CHECK ALGORITHM

In this section, we propose a new EM immortality check algorithm for general multisegment wires based on the new formula for estimating the saturation void volume discussed in Section III.

First, we review the recently proposed EM immortality check for nucleation, called the voltage-based EM (VBEM) method [8], [13]. In the new EM immortality check model, which can be viewed as a natural extension of the well-known *Blech product* [25] for immortality check of a single wire, the immortality of an interconnect tree can be summarized as

$$V_{\text{crit},\text{EM}} > V_E - V_{\text{cat}}$$

(17)

where  $\mathcal{V}_{\text{cat}}$  is the voltage at cathode.  $\mathcal{V}_{\text{crit},\text{EM}}$  is the critical EM voltage defined by  $\mathcal{V}_{\text{crit},\text{EM}} = (1/\beta)(\sigma_{\text{crit}} - \sigma_{\text{init}})$  where  $\sigma_{\text{init}}$  is the initial stress.  $\mathcal{V}_E$  is called EM voltage, which is computed as  $\mathcal{V}_E = (1/2A)\sum_{k\neq g} a_k \mathcal{V}_k$ , where  $\mathcal{V}_k$  is the normal nodal voltage (with respect to cathode node g) at node k of the wire.  $a_k$  is the total area of branches connected to node k. Since generally the cathode node has the lowest voltage within an interconnect wire, we may just check the cathode node using (17). However, this EM immortality check does not consider the case where a void is nucleated in a wire, but the saturation void volume is less than the critical volume.

As a result, we propose the following new EM immortality check algorithm. Given a new multisegment wire W with its branch current and node voltage given, the new algorithm first checks (17) for the cathode node. If it passes, then the wire can be considered as immortal. Otherwise, we compute the saturation void volume  $V_{\rm sat}$  from (10) or (11). If  $V_{\rm sat} < V_{\rm crit}$ , the wire is still immortal. Otherwise, it is mortal. Then, numerical methods are needed to compute the time to failure [12]. The whole algorithm flow is shown in Fig. 9.

The new EM immortality analysis flow in Fig. 9 can be integrated with the P/G network analysis tool for more accurate full-chip EM-aware IR drop analysis. When void volume reaches over the critical volume, the current starts to flow over the barrier layer and wire resistance starts to increase. But for power-grid networks with redundant wiring, the current indeed can start to flow in alternative paths in the P/G networks. As a result, the resulting P/G networks will become a time-varying network and the wire resistance changing over time can be modeled by the proposed method, which will be very efficient (closed form expression) and more accurate than the previous method to further remove the conservativeness.

Fig. 9. EM immortality check algorithm flow.

#### V. NUMERICAL RESULTS AND DISCUSSION

In this section, we validate the proposed saturation-volume EM model by comparing it against other models for the postvoiding process. In Section V-A, we first validate the saturation volume of the two-segment wire in Fig. 5 using the method in [15] and the proposed method. In Sections V-B and V-C, we study a T-shaped wire and a more complicated 13-segment wire against the physics-based 3-D FEM analysis tool [14], [24], respectively. And in Section V-D, we compare the proposed EM immortality check algorithm with the VBEM method [8], [13] using two-segment wire test cases with different lengths and current densities.

#### A. Model Validation on Two-Segment Wire

For a two-segment wire structure, the saturation void volume estimation was proposed in [15], where segment 2 is treated as a reservoir ( $j_2 = 0$ ). However, in this paper, the problem is still considered as 1-D, where all wire segments are assumed to have the same width. The saturation void volume,  $V_{\rm max}$ , computed using this method is given in the following:

$$V_{\text{max}}/Wh = L_1 + L_2 - \frac{B}{K} \left[ \sqrt{\left(\frac{Kp}{B} + 1\right)^2 + \frac{2L_1K}{B}} - 1 \right]$$

(18)

where  $K = eZ\rho j/\Omega$ . Note,  $V_{\rm max}/wh$  is actually the saturation length. This paper considers the void size formulated in the cathode of the  $L_1$  segment and its impact on the stress distributions. In order to validate our model, we compare the void volume computed using this model with that of the proposed model. Our analysis shows that the void size can be small compared to the segment length and therefore negligible. Comparisons of the void volume calculated using the method

| $L_1$ $(um)$ | $L_2 (um)$ | $j (A/m^2)$       | $V_1 \ (um^3) \ [15]$ | $V_{w/o} \ (um^3)$ | $V_w (um^3)$ |

|--------------|------------|-------------------|-----------------------|--------------------|--------------|

| 10           | 10         | $10^{10}$         | 0.0183                | 0.0184             | 0.0183       |

| 20           | 10         | $10^{10}$         | 0.0485                | 0.0491             | 0.0485       |

| 10           | 20         | $10^{10}$         | 0.0303                | 0.0307             | 0.0303       |

| 10           | 10         | $5 \times 10^{9}$ | 0.0092                | 0.0092             | 0.0092       |

TABLE I  $\label{eq:comparison} \text{Comparison of Void Area of Two Methods (Wire Width = 1 um and Thickness = 0.3 um) }$

Fig. 10. (a) Case 1. (b) Case 2. (c) Case 3. (d) Case 4.

in [15] and the proposed method are presented here. The results are shown in Table I, where  $V_1$  is the saturation volume calculated using [15],  $V_{\rm W/o}$  is the saturation volume calculated using the proposed method without void volume effect, and  $V_w$  is the saturation volume calculated using the proposed method considering void volume effect. Among the four test cases in Table I, the maximum difference is only 1.32% between  $V_1$  and  $V_{\rm W/o}$ . And the result  $V_w$  considering void volume effect is almost the same with  $V_1$ . It can be seen that the proposed method without void volume effect is already very close to the method in [15] and if the void volume effect is considered, their results match exactly.

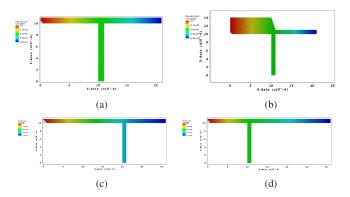

### B. Model Validation on a T-Shaped Wire

In this section, we compare the saturation volume estimated by the proposed method and a physics-based 3-D FEM analysis tool [14], [24] on a T-shaped three-segment wire. Four test cases with their estimated void volumes generated by the FEM tool are shown in Fig. 10. The results of the aforementioned test cases are shown in Table II, where  $V_{\rm FEM}$  is the saturation volume calculated using the FEM analysis tool, and  $V_w$  is the saturation volume calculated using the proposed method considering the void volume effect. We can see among the four test cases in Table II, the maximum difference is only 3.2% between  $V_{\rm FEM}$  and  $V_w$ .

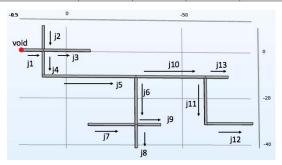

# C. Model Validation on a More Complicated Wire

Now, we compare our estimation with the FEM simulation from The physics-based 3-D FEM analysis tool [14], [24] on a more complicated wire structure with 13 segments, as shown in Fig. 11. Here, the width of all the wires is 0.2 um and thickness is 0.1 um. The current densities and lengths of all

TABLE II

COMPARISON OF VOID AREA OF TWO METHODS (WIRE THICKNESS = 0.1 um)

|                    | Case 1    | Case 2    | Case 3    | Case 4    |

|--------------------|-----------|-----------|-----------|-----------|

| $L_1 (um)$         | 10        | 10        | 20        | 10        |

| $L_2 (um)$         | 10        | 10        | 10        | 20        |

| $L_3 (um)$         | 10        | 10        | 10        | 10        |

| $W_1$ $(um)$       | 1         | 4         | 1         | 1         |

| $W_2 (um)$         | 1         | 1         | 1         | 1         |

| $W_3 (um)$         | 1         | 1         | 1         | 1         |

| $j_1 (A/m^2)$      | $10^{10}$ | $10^{10}$ | $20^{10}$ | $20^{10}$ |

| $j_2 (A/m^2)$      | $10^{10}$ | $10^{10}$ | $10^{10}$ | $10^{10}$ |

| $j_3 (A/m^2)$      | 0         | 0         | 0         | 0         |

| $V_{FEM} \ (um^3)$ | 0.0125    | 0.0185    | 0.0510    | 0.0368    |

| $V_w (um^3)$       | 0.0121    | 0.0183    | 0.0495    | 0.0356    |

Fig. 11. Complex multisegment structure.

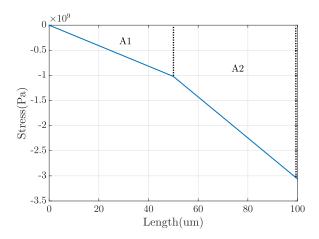

the segments are given in Table III, where Brch is the branch index, J is the current density, and the Lth is the length of the wire. Critical void volume is  $0.004 \text{ um}^2$ . As shown in Fig. 12, the void is formed on segment 1.

The saturation void volume estimated by the proposed method is 0.1025 um<sup>3</sup>, while the saturation void volume calculated by the FEM analysis tool is 0.1021 um<sup>3</sup>. As we can see, the results are almost identical (about 0.39% difference). We remark that the errors for this complicated wire structure are much smaller than the previous T-shaped wire. The reason is that the saturation volumes for the T-shaped wire are much smaller, while the 13-segment wire has much large void volume compared to the length of the wires. As a result, we obtained much smaller relative errors for the latter case.

#### D. Results From the New EM Immortality Check Flow

Last, but not least, we show that we can easily identify a new type of immortal wires, which have voids formed and

|   | TABLE III                                       |

|---|-------------------------------------------------|

|   | Parameters for the 13-Segment Interconnect Wire |

| # | $CD(A/m^2)$ Lth $(um)$ Brch# $J(A/m^2)$ Lt      |

| Brch# | $CD (A/m^2)$       | Lth (um) | Brch# | $J(A/m^2)$         | Lth (um) |

|-------|--------------------|----------|-------|--------------------|----------|

| 1     | $10 \times 10^{9}$ | 10       | 8     | $15 \times 10^{9}$ | 10       |

| 2     | $5 \times 10^{9}$  | 10       | 9     | $5 \times 10^{9}$  | 10       |

| 3     | $5 \times 10^{9}$  | 20       | 10    | $10 \times 10^{9}$ | 30       |

| 4     | $5 \times 10^{9}$  | 10       | 11    | $5 \times 10^{9}$  | 20       |

| 5     | $10 \times 10^{9}$ | 40       | 12    | $5 \times 10^{9}$  | 20       |

| 6     | $5 \times 10^{9}$  | 20       | 13    | $5 \times 10^{9}$  | 10       |

| 7     | $5 \times 10^{9}$  | 20       | _     | _                  | _        |

$TABLE\ IV \\ Comparison\ of\ Void\ Area\ of\ Two\ Methods\ (Wire\ Width = 1\ um\ and\ Thickness = 0.3\ um)$

|       | $L_1 (um)$ | $L_2 (um)$ | $j_1 (A/m^2)$ | $j_2 (A/m^2)$ | VBEM     | Proposed method |

|-------|------------|------------|---------------|---------------|----------|-----------------|

| case1 | 10         | 10         | $10^{10}$     | $10^{10}$     | Immortal | Immortal        |

| case2 | 20         | 10         | $10^{10}$     | $10^{10}$     | Mortal   | Immortal        |

| case3 | 10         | 50         | $20^{10}$     | $20^{10}$     | Mortal   | Mortal          |

Fig. 12. (a) Complex multisegment structure result from the FEM analysis tool. (b) Result zoomed to void area.

still remain immortal due to the voids being the critical void volumes. We use two-segment wires with different lengths and current densities to perform the proposed new EM immortality check considering both saturation volume and EM immortality check for nucleation in Section IV. The result is shown in Table IV, where VBEM represents the EM immortality check for nucleation for general multisegment wires [8], [13].

As we can see in Table IV, case 2 is recognized as mortal in the VBEM method. However, in our method, we can see this wire is actually immortal, as the void volume is smaller than the critical volume. That means the VBEM method is still too conservative and the new method can identify more immortal cases in the EM analysis, which can translate into further reduced guard bands and reduced circuit areas and better performance.

#### VI. CONCLUSION

In this paper, we have proposed a novel formula for fast estimation of void's saturation volume for general multisegment wires. The proposed new formula is less conservative than the existing method since the void growth phase is also considered. The new void saturation estimation formula agrees with the existing single-segment wire saturation void volume formula and is the natural extension of the singlesegment case to general multisegment wires. Based on the new formula, a new EM immortality check flow is proposed, including both the recently proposed nucleation-based EM immortality and the void saturation volume. The new flow can further reduce the conservativeness of existing EM failure effect analysis which only considers the nucleation-based EM immortality check. Numerical results from the proposed formula also agree well with a published work for two-segment cases, where the maximum difference is only 1.32%. The formula is also validated by the recently proposed physicsbased 3-D finite-element (FEM) analysis tool for general multisegment interconnect wires where the maximum error is only 3.2%. We also demonstrate that the new EM immortality check flow can quickly identify the new type of immortal wires, which are nucleated but with smaller-than-critical voids.

#### REFERENCES

[1] (2015). International Technology Roadmap for Semiconductors (ITRS) Interconnect. [Online]. Available: http://public.itrs.net

- [2] S. X.-D. Tan, M. Tahoori, T. Kim, S. Wang, Z. Sun, and S. Kiamehr, VLSI Systems Long-Term Reliability–Modeling, Simulation and Optimization. Springer, 2019.

- [3] X. Huang, T. Yu, V. Sukharev, and S. X.-D. Tan, "Physics-based electromigration assessment for power grid networks," in *Proc. Design Autom. Conf. (DAC)*, Jun. 2014, pp. 1–6.

- [4] V. Sukharev, X. Huang, H.-B. Chen, and S. X.-D. Tan, "IR-drop based electromigration assessment: Parametric failure chip-scale analysis," in *Proc. Int. Conf. Comput. Aided Design (ICCAD)*, Nov. 2014, pp. 428–433.

- [5] H.-B. Chen, S. X.-D. Tan, X. Huang, T. Kim, and V. Sukharev, "Analytical modeling and characterization of electromigration effects for multibranch interconnect trees," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 35, no. 11, pp. 1811–1824, Nov. 2016.

- [6] X. Huang, A. Kteyan, X. Tan, and V. Sukharev, "Physics-based electromigration models and full-chip assessment for power grid networks," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 35, no. 11, pp. 1848–1861, Feb. 2016.

- [7] V. Mishra and S. S. Sapatnekar, "Predicting electromigration mortality under temperature and product lifetime specifications," in *Proc. 53nd ACM/EDAC/IEEE Design Autom. Conf. (DAC)*, Jun. 2016, pp. 1–6.

- [8] Z. Sun, E. Demircan, M. D. Shroff, T. Kim, X. Huang, and S. X.-D. Tan, "Voltage-based electromigration immortality check for general multi-branch interconnects," in *Proc. Int. Conf. Comput. Aided Design (ICCAD)*, Nov. 2016, pp. 1–7.

- [9] X. Huang, V. Sukharev, T. Kim, H. Chen, and S. X.-D. Tan, "Electromigration recovery modeling and analysis under time-dependent current and temperature stressing," in *Proc. Asia South Pacific Design Autom. Conf. (ASPDAC)*, Jan. 2016, pp. 244–249.

- [10] X. Huang, V. Sukharev, T. Kim, and S. X.-D. Tan, "Dynamic electromigration modeling for transient stress evolution and recovery under time-dependent current and temperature stressing," *Integration*, vol. 58, pp. 518–527, Jun. 2017.

- [11] S. Chatterjee, V. Sukharev, and F. N. Najm, "Power grid electromigration checking using physics-based models," *IEEE Trans. Comput.-Aided Design Integr.*, vol. 37, pp. 1317–1330, Jul. 2018.

- [12] S. X.-D. Tan, H. Amrouch, T. Kim, Z. Sun, C. Cook, and J. Henkel, "Recent advances in EM and BTI induced reliability modeling, analysis and optimization," *Integration*, vol. 60, pp. 132–152, Jan. 2018.

- [13] Z. Sun, E. Demircan, M. D. Shroff, C. Cook, and S. X.-D. Tan, "Fast electromigration immortality analysis for multi-segment copper interconnect wires," *IEEE Trans. Computer-Aided Design Integr. Circuits Syst.*, vol. 37, pp. 3137–3150, Dec. 2018.

- [14] H. Zhao and S. X.-D. Tan, "Postvoiding fem analysis for electromigration failure characterization," *IEEE Trans. Very Large Scale Integr.* (VLSI) Syst., vol. 26, no. 11, pp. 2483–2493, Nov. 2018.

- [15] C. W. Chang et al., "Electromigration resistance in a short three-contact interconnect tree," J. Appl. Phys., vol. 99, no. 9, pp. 094505-1–094505-8, May 2006.

- [16] M. A. Korhonen, P. Bo-Rgesen, K. N. Tu, and C.-Y. Li, "Stress evolution due to electromigration in confined metal lines," *J. Appl. Phys.*, vol. 73, no. 8, pp. 3790–3799, 1993.

- [17] M. A. Korhonen, P. Borgesen, D. D. Brown, and C.-Y. Li, "Microstructure based statistical model of electromigration damage in confined line metallizations in the presence of thermally induced stresses," *J. Appl. Phys.*, vol. 74, no. 8, p. 4995, 1993.

- [18] R. G. Filippi, R. A. Wachnik, H. Aochi, J. R. Lloyd, and M. A. Korhonen, "The effect of current density and stripe length on resistance saturation during electromigration testing," *Appl. Phys. Lett.*, vol. 69, no. 16, pp. 2350–2352, Oct. 1996.

- [19] C. M. Tan and A. Roy, "Electromigration in ulsi interconnects," *Mater. Sci. Eng.*, *R*, *Rep.*, vol. 58, nos. 1–2, pp. 1–75, 2007.

- [20] V. Mishra and S. S. Sapatnekar, "Probabilistic wire resistance degradation due to electromigration in power grids," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 36, no. 4, pp. 628–640, Apr. 2017.

- [21] C.-K. Hu et al., "Effects of overlayers on electromigration reliability improvement for cu/low k interconnects," in Proc. IEEE Int. Rel. Phys. Symp., Apr. 2004, pp. 222–228.

- [22] L. Zhang, "Effects of scaling and grain structure on electromigration reliability of Cu interconnects," Ph.D. dissertation, Dept. Mech. Eng., Lab. Interconnect Packag., Microelectron. Res. Center, Univ. Texas Austin, Austin, TX, USA, 2010.

- [23] T. N. Marieb, E. Abratowski, J. C. Bravman, M. Madden, and P. Flinn, "Direct observation of the growth and movement of electromigration voids under passivation," AIP Conf. Proc., vol. 305, no. 1, pp. 1–14, 1994

- [24] H. Zhao and S. Tan, "Multi-physics-based FEM analysis for post-voiding analysis of electromigration failure effects," in *Proc. Int. Conf. Comput. Aided Design (ICCAD)*, 2018, p. 124.

- [25] I. A. Blech, "Electromigration in thin aluminum films on titanium nitride," *J. Appl. Phys.*, vol. 47, no. 4, pp. 1203–1208, Apr. 1976.

**Zeyu Sun** (S'16) received the B.S. degree in electronic and computer engineering from The Hong Kong University of Science and Technology, Hong Kong, in 2015. He is currently working toward the Ph.D. degree at the Department of Electrical and Computer Engineering, University of California, Riverside, Riverside, CA, USA.

His current research interests include electromigration modeling and assessment and reliability-aware performance optimization.

Sheriff Sadiqbatcha (S'15) received the B.S. degree in computer engineering from California State University at Bakersfield, Bakersfield, CA, USA, in 2016, where he was selected as the most outstanding graduate of the year in the Department of Computer and Electrical Engineering. He is currently working toward the Ph.D. degree in electrical engineering at the University of California at Riverside, Riverside, CA, USA.

His current research interests include hot-spot identification and system-level thermal modeling for

multicore microprocessors, as well as accelerating electromigration effects for fast failure testing.

Mr. Sadiqbatcha has received several other university-level distinctions and research awards, including best paper awards in the IEEE conferences.

Hengyang Zhao (S'15) received the B.S. degree in computer science and the M.S. degree in metering and instrumentation engineering from Shanghai Jiao Tong University, Shanghai, China, in 2011 and 2014, respectively, and the Ph.D. degree in electrical engineering from the University of California at Riverside, Riverside, CA, USA, in 2018.

He is currently a Software Engineer with Google Inc. His current research interests include VLSI reliability modeling, smart building energy optimization, finite-element method-based simula-

tion, and machine learning applications.

Sheldon X.-D. Tan (S'96–M'99–SM'06) received the B.S. and M.S. degrees in electrical engineering from Fudan University, Shanghai, China, in 1992 and 1995, respectively, and the Ph.D. degree in electrical and computer engineering from The University of Iowa, Iowa City, IA, USA, in 1999.

He was a Visiting Professor with Kyoto University, Kyoto, Japan. He is currently a Professor with the Department of Electrical Engineering, University of California at Riverside, Riverside, CA, USA, where he is also a Cooperative Faculty Member with the

Department of Computer Science and Engineering. His current research interests include VLSI reliability modeling, optimization and management at circuit and system levels, hardware security, thermal modeling, optimization and dynamic thermal management for many-core processors, parallel computing and adiabatic, and Ising computing based on GPU and multicore systems. He has published more than 290 technical papers and has coauthored six books on these areas.

Dr. Tan was a JSPS Fellow from 2017 to 2018. He received the NSF CAREER Award in 2004. He also received three Best Paper Awards from ICSICT'18, ASICON'17, ICCD'07, and DAC'09 and the Honorable Mention Best Paper Award from SMACD'18. He currently serves as the Editor-in-Chief for Integration (Elsevier), the VLSI journal, and an Associate Editor for three journals: the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, the ACM Transactions on Design Automation of Electronic Systems, and Microelectronics Reliability (Elsevier).