## **Stopping Resistance Drift in Phase Change Memory Cells**

Raihan S. Khan<sup>1</sup>, ABM Hasan Talukder<sup>1</sup>, Faruk Dirisaglik<sup>1,2</sup>, Ali Gokirmak<sup>1</sup> and Helena Silva<sup>1</sup>

Department of Electrical and Computer Engineering, University of Connecticut, Storrs, CT 06269, USA

Department of Electrical and Electronics Engineering, Eskisehir Osmangazi University, Eskisehir 26480, Turkey

Email: raihan.khan@uconn.edu / Phone: +1 860 208 9253

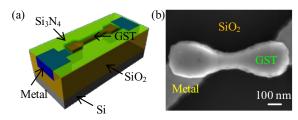

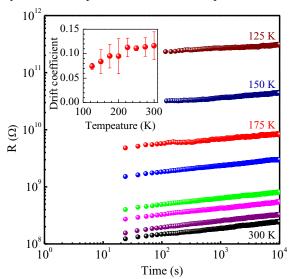

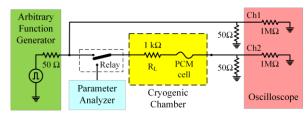

Phase change memory (PCM) is a high speed, high endurance, high density non-volatile memory technology that utilizes chalcogenide materials such as  $Ge_2Sb_2Te_5$  (GST) that can be electrically cycled between highly resistive amorphous and low resistance crystalline phases. The resistance of the amorphous phase of PCM cells increase (drift) in time following a power law [1], which increases the memory window in time but limits in the implementation of multi-bit-per-cell PCM. There has been a number of theories explaining the origin of drift [1]–[4], mostly attributing it to structural relaxation, a thermally activated rearrangement of atoms in the amorphous structure [2]. Most of the studies on resistance drift are based on experiments at or above room temperature, where multiple processes may be occurring simultaneously. In this work, we melt-quenched amorphized GST line cells with widths ~120-140 nm, lengths ~390-500 nm, and thickness ~50nm (Fig. 1) and monitored the current-voltage (I-V) characteristics using a parameter analyzer (Fig. 2) in 85 K to 350 K range. We extracted the drift co-efficient from the slope of the resistance vs. time plots (using low-voltage measurements) and observed resistance drift in the 125 K -300 K temperature range (Fig. 3). We found an approximately linear increase in drift coefficient as a function of temperature from ~ 0.07 at 125 K to ~ 0.11 at 200 K and approximately constant drift coefficients in the 200 K to 300 K range (Fig. 3 inset). These results suggest that structural relaxations alone cannot account for resistance drift, additional mechanisms are contributing to this phenomenon [5], [6].

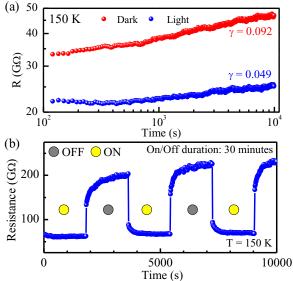

Amorphous chalcogenides have a large number of traps in their bandgaps, therefore, if the resistance drift is significantly affected by the capturing and emission of trapped charges, a change in resistance drift is expected with photoexcitation. We performed experiments using a white LED installed in our probe station, minimizing the thermal load on the system. We observed a significantly lower drift coefficients in amorphized GST line cells under light compared to dark (Fig. 4a). If the LED was periodically switched on and off, a fast response (decrease/increase) followed by a gradual change in resistance was observed as the light was turned on and off (decrease/increase) (Fig. 4b). The fast changes can be attributed to the band-to-band processes by the photo-excited carriers. The long time-scale associated with slow changes suggests emptying of the traps when the light is turned on and filling of the traps when the light is turned off, similar to phosphorescence in high trap-density materials [7]. The photo-excitation experiments point to an electronic component in resistance drift, and trapping and detrapping of the charges giving rise to changes in the current-voltage characteristics.

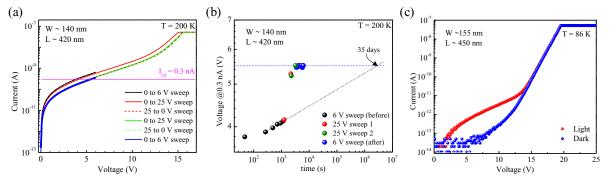

When we continuously swept voltage across the cell from 0 V up to 25 V with 0.1 V steps and back to 0 V using a parameter analyzer, with a current compliance set to 50 nA (for  $T < 200 \, \text{K}$ ), we observed a hysteresis loop in the I-V characteristics in the first measurement on each device. The consecutive measurements on the same device were very stable (Fig 5a). Measurements performed using small voltage sweeps that do not disturb the cell before and after application of a high-voltage sweep show the expected power-law behavior for the voltage required to reach a reference current level ( $I_{ref}$ ) before the application of the high-voltage sweep and the required voltage completely stabilized after two high-voltage sweeps (Fig. 5a,b). Since the compliance current is very low and the ambient temperature is  $< 200 \, \text{K}$ , we do not expect the cells to self-heat to promote accelerated structural relaxation. Furthermore, the acceleration of resistance drift and reaching a final value within a few minutes with application of high electric fields suggest that resistance drift, observed as a slow relaxation process in unperturbed cells, is due to relaxation of trapped charges. High-voltage sweeps performed on stabilized cells under light and dark show a significant difference between the two cases in low-voltage range (Fig. 5c). The relative contribution of the photoexcited carriers decrease with increasing temperature as conduction gets dominated by thermally excited carriers.

In conclusion, our observations show that charge trapping and detrapping play a very significant role in resistance drift in PCM cells, and resistance drift can be mitigated by application of high fields after reset operations (waveform engineering), thus achieving stable multi-bit-per-cell operation in PCM.

This work is supported by US NSF through grant # ECCS 1711626.

[1] A. Pirovano et. al., IEEE Trans. Electron Devices, pp. 714–719 (2004); [2] D. Ielmini et. al., in Technical Digest - IEDM, pp. 939–942 (2007); [3] M. Mitra et. al., Appl. Phys. Lett. (2010); [4] S. R. Elliott, J. Phys. D. Appl. Phys. (2020). [5] R. S. Khan et al., Bull. Am. Phys. Soc. (2019); [6] A. H. Talukder et al., Bull. Am. Phys. Soc. (2019); [7] J. T. Randall et al., Proc. R. Soc., Lond., Ser. A, vol. 184, no. 999, p. 365 (1945).

**Fig. 1.** (a) Schematic layout and (b) SEM image of the GST line cell. The cells have bottom metal contacts (W with Ti/TiN liner), are capped with Si<sub>3</sub>N<sub>4</sub> to prevent evaporation, and are annealed to 675 K to ensure initial crystalline state prior to the electrical experiments.

**Fig. 3.** Resistance (R) vs. time (t) plots for line cells amorphized at 125 K - 300 K temperature range at 25 K intervals. Inset: drift coefficients extracted from R-t plots of multiple amorphized line cells at different temperatures.

Fig. 2. Schematic of the electrical characterization setup. The 1  $k\Omega$  resistor limits the current during amorphization. The relay switches between the parameter analyzer and the pulse generator.

Fig. 4. (a) Resistance versus time plots for two different line cells amorphized and monitored under dark (red) and light (blue) at 150 K. (b) Effect of light on resistance of amorphous line cells at 150 K showing a fast decrease/increase in resistance, followed by a slow decrease/increase in resistance with turning on/off of the LED.

**Fig. 5.** (a) 0 to 6 V sweeps before (black) and after (blue) 0 to 25 V sweeps (red and green) at 200 K. (b) Time versus voltage required for current to reach reference current 0.3 nA, where the required voltage follows a power law behavior (black) before the application of high-voltage sweep (red), and becomes constant after the high-voltage sweep (blue). (c) High-voltage sweeps under light (red) and dark (blue) at 86 K after the cell was stabilized with several high-voltage sweeps, showing the contribution of the photoexcited carriers.