# Guidelines for Ferroelectric FET Reliability Optimization: Charge Matching

Shan Deng, Student Member, IEEE, Zhan LiuG, Student Member, IEEE, Xueqing u O, Member, IEEE, T. P. Ma, Life Fellow, IEEE, and Kai Ni, Member, IEEE

Abstract- Anoptimization principle for ferroelectric FET (FeFET), centered around charge matching between the ferroelectric and its underlying semiconductor, is theoretically investigated. This letter shows that, by properly reducing the ferroelectric constant, and the harden and its barrier and the harden and the harde

enable simultaneously: i) reduction of the interlayer and semiconductor electric fields during programming, reading, and retention, leading to prolonged endurance and reten-

tion; ii) improvement of the memory window; and iii) suppression of device-to-device variations by affording full polarization switching. Theseattributes provide anincentive for the presentation of the proposed guidelines for FeFET optimization as detailed in this letter.

*Index Terms*-Ferroektric, FeFET, reliability optimization, charge matching.

### I. INTRODUCTION

ERROELECTRIC memory has received a strong resurgence of interest since the discovery of scalable and CMOS-compatible ferroelectrics based on Hf(h. Excellent performance (e.g., more than 1V memory window for ~10nm thick HfO2, write time as short as lOns, and ultralow write energy on the order of lOfJ, etc.) has been demonstrated in advanced technology nodes [1], [2]. However, challenges in reliability remains a major roadblock for its adoption, such as charge trapping [3], [4], degraded endurance [5], and unacceptable variations upon scaling [2], [6]. Therefore, optimization of device reliability without degrading other performance metrics will be critical for its success.

We believe that many of the reliability issues are associated with the large charge mismatch between the ferroelectric layer and the semiconductor. With the typical polarization charge around  $20\mu\text{C/cm}^2$  for HfO 2, compared with the corresponding charge on the silicon side (including the depletion charge and the channel inversion charge) of less than  $2\mu\text{C/cm}^2$ , there is a large charge mismatch between the two, as illustrated

Manuscript received July 8, 2020; accepted July 19, 2020. Date of publication July 21, 2020; date of current version August 26, 2020. The work of Zhan Liu and T. P Ma was supported by the NSF under Award 1941316. The reviewof this letter was arranged by Editor D. Ha. (Corresponding author: Kai Ni.)

ShanDeng and Kai Ni are with the Department of Microsystems Engineering, Rochester Institute of Technology, Rocheste, rNY 14623 USA (e-mail: kai.ni@rit.edu).

ZhanLiuand T.P Maarewiththe Department of Electrical Engineering, Yale University, New Haven, CT 06520 USA.

Xueqing Li is with the Department of Electrical Engineering Tsinghua University, Beijing 100084, China.

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2020.3011037

Fig. 1. Overv iew of charge mismatch between the ferroelectric and semiconductor, and the mitigation strategy. (a) For a normal Hf0 2-based FeFET withlargePr and eFE, the large polarization charge <PW IPW during programming significantlystresses the interlayer and semiconductor. The blueline is the MOS loadline and the red curve is the ferroelectric OrcE - VFE loop. (b) Reduced Pr and eFE limit the switched polarization charge, and enable full polarizations witching with less stress on the interlayer and semiconductor. (c) The model that is utilized to investigate the optimization guidelines of FeFET.

in Fig. 1 (a). This stresses the semiconductor and interlayer significantly during programming with Va = +Vw/-Vw, because a large polarization charge, Pw+IPw-, has to be so reened by the semiconductor. Hence, substantial charge trapping and defect generation are induced by the write pulses, degrading FeFET endurance [3]. The charge mismatch also forces the ferroelectric to work on non-saturated hysteresis loops [7]. It bas been shown that partial polarization switching induces significant variations due to the stochasticity during domain switching [6]. Therefore, mitigating charge mismatch becomes critical for reliability improvement.

There have been several device designs that are tar-geted at addressing this charge mismatch, such as FeMFET (or MFMIS) structure [8]- [10]. In those devices, a metal-ferroelectric-metal (MFM) capacitor is integrated on top of the gate of a MOSFET. By scaling down the area of the MFM capacitor with respect to the MOSFET, the electric field in the MOSFET is reduced, and the ferroelectric can operate along the saturation loop. Challenges with this approach are the small area ratio (e.g.,  $\sim 0.1$ ) required, which limits the device scaling capability as well as retention degradation due to leakage current and depolarization field. Therefore, other approaches to improve charge matching without compromising performance are desirable.

In this work, we demonstrate an alternative approach for optimization, i.e., to reduce the ferroelectric polarization (*P*,) and its background dielectric constant (8FE) [11], [12],

as shown in Fig. 1 (b). In doing so, the amount of polarization that needs to be screened by the semiconductor is reduced, relieving the electrical stress in interlayer and semiconductor during programming, and thus improving the endurance, as also proposed in [13]. Additionally, it also enables the fer-roelectric to operate along the saturation loop that minimizes the variation [6].

### 11. E VA L UAT ION A PPR OAC H

A recently developed model for FeFET [14] is utilized to theoretically study the optimization strategy. The ferroelectric is modeled as a lumped capacitor, which is connected with the gate of a MOSFET. The voltage division equation and charge

conservation equation are solved self-consistently to obtain the

FeFET characteristics, as shown in Fig. 1(c). The ferroelectric film is composed of multiple independent switching domains, where each domain can be in the up or down polarization state. A nucleation limited switching model is applied to describe the polarization switching dynamics [15]. With this model, the size scaling, inter-device variation, switching stochasticity, and polarization accumulation can be successfully captured.

# III. RESULTS ANDDISCUSS NS

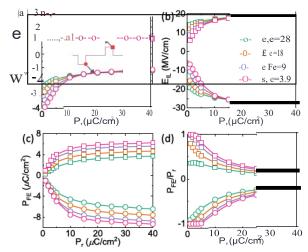

Write pulses of  $\pm 4V$ ,  $1\mu s$  are applied to FeFETs with 8nm Hf(h as the ferrodectric and 1nm Si(h as the interdyer Theelectric fields in the ferroelectrics (£FE) and interlayers (£IL) at the end of write pulses as functions of P, with four different eFE are shown in Figs. 2(a) and (b), respectively. At a given f:fE, the less the polarization charge that needs to be screened, the smaller the EJL. This is consistent with the charge conservation requirement (Fig. 1 (c)). A smaller P, improves the charge matching between the ferroelectric and the semiconductor, relieving the electrical stress on the interlayer and semiconductor. Moreover, additional drop in £IL can be achieved by lowering f:fE• For example, during the - 4V write pulse, £IL reduces merely 1.3x when P, shrinks from  $20\mu\text{C/cm}^2$  to  $2\mu\text{C/cm}^2$  for f:FE = 28; while reduces as much as 2x for eFE = 9. Such decline in £IL is beneficial for

endurance improvement, as it can reduce charge trapping and interface defect generation.

The boost of £FE is a direct consequence of the reduction in *EJL.* As such, the £FE increases by 1.7x when *P*, shrinks from  $20\mu$  C/cm<sup>2</sup> to  $2\mu$ C/cm<sup>2</sup> for f:f E = 28, and grows by 2.5x for f:FE = 9. Note that this *EFE* increase should not degrade the endurance of the Hf(h -based FeFET ( $\sim 10^5$  cycles [1], [2]), as it is mainly limited by charge trapping [5]. This is further illustrated by the much higher endurance (> 108 cycles [16], [17]) in MFM capacitors cycled with similar £FE stress (£ FE ~ 3MV/cm). The absolute and nor-malized polarization charge (PFE) at the end of write pulses are shown in Figs. 2(c) and (d), respectively. The enhancement in switched PFE with P, becomes marginal when P, grows beyond 15μC/cm<sup>2</sup>. This indicates that, for the optimization of FeFET, pursuing a high P, is the wrong direction because: (i) it will not improve the switched PFE, and even worse, (ii) it will increase the stress on the interlayer and semiconductor, degrad- ing its reliability. The normalized PFE indicates the portion of domains that participate in the switching process. Interestingly, it exhibits an opposite trend to the absolute PFE due to the sa turating behavior of PFE with respect to P<sub>1</sub>. For small P<sub>2</sub>, especially at small eFE, the PFEIP, is close to 1, indicating full polarization switching due to the charge matching. The benefit of full polarization switching in controlling the variation will be explained below.

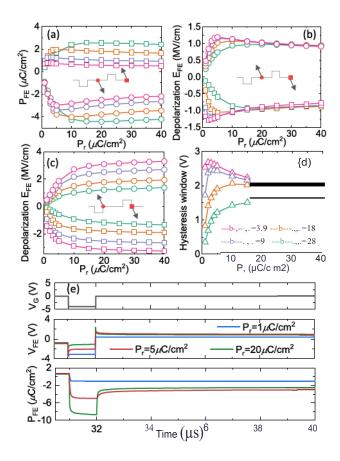

When the applied gate pulse is turned off, some of the switched domains will flip back, relaxing the polarization. Fig. 3(a) shows that PFE during retention exhibits a peak at some intermediate *P*,, especially for small e FE. This is related to the depolarization field [18], shown in Eq. 1, that causes the polarization relaxation.

$$VFE rel = -- PFE _$$

$$, CFE + C1s$$

(1)

where VFE,ret is the voltage across the ferroelectric during retention, C1s is the series combination of the interlayer and the semiconductor capacitance. As shown in Fig. 3(c), the depolarization field at the initial relaxation moment strengthens with increasing P,, and get further enhanced for small E:fE, which is consiste nt with Eq. (1). For small P,, the depolarization field is sufficiently small such that PFE during retention follows the switched ffE after the write pulse (Fig. 2(c)). However, for a large  $P_{c}$ , the depolarization field is strong enough to cause significant polarization relaxation after the write pulse, causing the decline of ffE- This is also illustrated in the transient waveform for a - 4V write pulse, shown in Fig. 3(e). At the moment when Va switches from - 4V to 0 V, the VFE,ret is greater for higher P,, causing more polarization relaxation. As a result, a nonmonotonic dependence is observed. Note that even after polarization relaxation, shown in Fig. 3(a), nearly full polarization switch- ing is observed for small P, and E:fE, suggesting its potential for suppressing interdevice variations.

According to Eq.(1), there is a tradeoffbetween the memory window and depolarization field, hence retention performance. The depolarization field during retention, shown in Fig. 3(b) follows a similar trend as the Fig. 3(a), due to Eq. (1).

It suggests that even though the depolarization field at the initial relaxation moment (Fig. 3(c)) is much higher for a film with a smaller eFE, it does not hold for the depolarizationfield during retention. This is because PFe during retention is also reduced for small EfE, thus rendering similar depolarization field during retention, irrespective of the EfE. For example, for a eFE of 9, the EFE during retention increases approximately only 30% when Pr reduces from  $25\mu\text{C/cm}^2$  to  $5\mu\text{C/cm}^2$  (the peak of the curve). It is also possible to maintain the same depolarization field as the existing HfO2 FeFET (Pr of 20  $\mu$  C/cm $^2$  and EfE of 28) by simultaneously decreasing Pr and EfE . Therefore , it is still possible to improve the device reliability, including retention, while maintaining the same device performance.

Fig. 3(d) shows the FeFET memory windows as functions of Pr for four different E:fE. It suggests that the degradation in memory window caused by weak Pr can be compensated by reducing E:fE. This again demonstrates that pursuing a high Pr is no t the right direction as only marginal improvement in memory window can be achieved given the limited write voltage. Thus, the FeFET reliability can be improved without degrading its performance.

The simulated device-to-device variations in scaled FeFET are presented in Fig. 4. The model incorporates a Monte Carlo

Fig. 4. Device-to-device variations of FeFETs with 3 different Pr and eFE combinations. The distributions of PFE alter+4V and -4V write pulses are shown. 200 devices each with 20 domains are simulated.

induced by the switching process [14]. For a FeFET with Pr of  $20\mu\text{C/cm}^2$  and eFE of 28, only 20% of domains participate

in the switching. Reducing Pr to  $2\mu$ C/cm increases EFE framework, which allows to capture the intrinsic variations

during write, resulting in nearly full polarization switching. Reducing *eFE* to 9 further suppresses the variation. This suggests that, by proper charge matching between the ferroelectric and the semiconductor, *EFE* can be enhanced to enable full polarization switching, regardless of the ferroelectric domain distribution. This could potentially provide a way to suppress the variations. Note that this model only cap tures the lower bound of the variation as it only considers variation induced by the intrinsic ferroelectric switching process without taking into account the phase inhomogeneity [19] and sources for conventional transistor variations [20]. The appropriate design of relatively low *Pr* and *EIFE* ferroe lec trics compared to the prevailing values currently being pursued, should therefore be the target for the optimization of FeFETs for memory applications.

Engineering a HfO2 based ferroelectric film with low Pr and eFE should therefore be the target for the optimization of FeFET. Previously, a polarization reduction strategy has been proposed, which is to control the polarization orientation so that the out of plane polarization component can be reduced [13]. However, its effectiveness remains to be tested. Moreover, several other strategies can also be potentially applied. For example, it has been shown that by inhomoge- neous layering of HfO2 and SiO2, the remnant polarization and potentially also the dielectric constant can be reduced [21]. Another interesting approach to reduce Pr and eFE is through film engineering by adjusting the atomic layer deposition cycle ratio of HfO2 and ZrOi [22]. Therefore, exp loration in the process ing tech niques and their effectiveness in reducing Pr and EiFE, and thus improvement in FeFET reliability, will need to be performed in the future.

## IV. CONCLUSION

Based on the simple principle of proper charge matching between the ferroelectric and its underlying semiconductor, we have presented a set of guidelines for optimizing HfO2-based FeFETs for nonvolatile memory applications. Specifically, our simulation results have demonstrated that, by appropriately reducing the ferroelectric's Pr and its background EiFE , the electrical stress in the interlayer/semiconductor can be reduced, the memory window can be improved, and the inter-device variations can be suppressed.

#### **R EFERENCES**

- [1] M. Trentzsch, S. Flachowsky, R. Richter, J. Paul, B. Reimer, D. Utess, S. Jansen, H. Mulaosmanovic, S. Miiller, S. Slesazeck, J. Ocker, M. Noack, J. Miiller, P. Polakowski, J. Schreiter, S. Beyer T. Mikolajick and B. Rice, "A 28 nm HKMG super low power embedded NVM technology based on ferroelectric FETs; in *JEDM Tech. Dig.*, Dec. 2016, pp. 294-297, doi: 10.1109/IEDM.2016.7838397.

- [2] S. Dunke, I. M. Trentzsch, R. Richter, P. Moll, C. Fuchs, O. Gehring, M. Majer, S. Wittek, B. Miiller, T. Melde, H. Mulaosmanovic, S. Slesazeck, S. Miiller, J. Ocker, M. Noack, D.-A. Lohr, P. Polakowski, J. Miiller, T. Mikolajick, J. Hontschel, B. Rice, J. Pellerin, and S. Beyer, "A FeFET based super-low-power ultra-fast embedded NVM technology for 22 nm FDSOI and beyond," in *JEDM Tech. Dig.*, Dec. 2017, pp. 485-488, doi: 10.1109/IEDM.20178268425

- [3] K. Ni, P.Sharma, J. Zhang, M. Jerry, J. A. Smith, K. Tapily, R. Clark, S. Mahapatra, and S. Datta, "Critical role of interlayer in Hfo.5Zró 02 ferroelectric FET nonvolatile memory performance," *IEEE Tral1s. Electro11 Devices*, vol. 65, no. 6, pp. 2461-2469, Jun. 2018, doi: 10.1109ffED.2018.2829122.

- [4] E. Yurchuk, J. Miiller, S. Miiller, J. Paul, M. Pesic, R. van Bentum, U. Schroeder, and T. Mikolajick, "Charge-trapping phenomena in Hf02 -bas ed FeFET-type nonvolatile memories," *IEEE Tral1s. Electro11 Devices*, vol. 63, no. 9, pp. 3501- 3507, Sep. 2016, doi: 10.1109ffED.2016.2588439.

- [5] E. Yurchuk, S. Mueller, D. Martin, S. Slesazeck, U. Schroeder, T. Mikolajick, J. Miiller, J. Paul, R. Hoffmann, J. Sundqvist, T. Schlosser, R. Boschke, R. van Bentum, and M. Trentzsch, "Origin of the endurance degradation in the novel HfO2-based IT ferroelectric non-volatile memories," in *Proc. IEEE /11t. Rel. Phys. Symp.*, Jun. 2014, pp. 2E-1- 2E-5, doi: 10.1109/IRPS.20146860603.

- [6] K. Ni, W. Chakraborty, J. S mith, B. Grisafe, and S. Datta, "Fundamental understanding and control of device-to-device variation in deeply scaled ferroelectric FETs," in *Proc. Symp. VLSITech110I.*, Jun. 2019, pp. 40-41, doi: 10.23919NLSIT.2019.8776497.

- [7] K. Ni, M. Jerry, J. A. Smith, and S. Datta, "A circuit compatible accurate compact model for ferroelectri-cFETs," in *Proc. IEEE Symp. VLSI Tech11ol.*, Jun. 2018, pp. 131-132, doi: 10.1109NLSIT.2018.8510622.

- [8] K. Ni, J. A. Smith, B. Grisafe, T. Rakshit, B. Obradovic, J. A. Kitti, M. Rodder, and S. Datta, "SoC logic compatible multi-bit FeMFET weight cell for neuromorphic applications," in *JEDM Tech. Dig.*, Dec. 2018, pp. 296--299, doi: 10.1109/IEDM.201.88614496.

- [9] E. Tokumita, G. Fujii, and H. Ishiwara, "Electrical properties of metal-ferroelectric-insulator-semiconductor (MFIS)- and metalferroelectric-metal-insulator-semiconductor (MFMIS)-FETs using ferroelectric SrBi2Ta2O9 film and SrTa2O6/SiON buffer layer," *Jpn. J. Appl. Phys.*, vol. 39, pp. 2125-2130, Apr. 2000, doi: 10.1143/JJAP.39.2125.

- [10] S.-J. Yoon, D.-H. Min, S.-E. Moon, K. S. Park, J. I. Won, and S.-M. Yoon, "Improvement in long-term and high-temperature retention stability of ferroelectric field-effect memory transistors with metalferroelectric-metal-insulator--.semiconductor gate-stacks using Al-0oped Hf02thin films," *IEEE TrallS. Electron Devices*, vol. 67, no. 2, pp. 499- 504, Feb. 2020. [Online]. Available: https://ieeexplore.ie ee.org/abstract/document/8954955

- [11] T. Li, S. T. Hsu, B. Ulrich, H. Ying, L. Stecker, D. Evans, Y.Ono, J.-S. Maa, and J. J. Lee, "Fabrication and characterization of a Pb5Ge3O11 one-transistor-memory device," *Appl. Phys. Lett.*, vol. 79, no. 11, pp. 1661-1663, Sep. 2001, doi: 10.1063/1.1401092.

- [12] T. Li,S. T. Hsu, B. D. Ulrich, L. Stecker, D.R. Evans, and J. J. Lee, "One transistor ferroelectric memory with Pt/Ph5Ge3O11/lr/Poly-Si/SiO2/Si gate stack," *IEEE Electro11 Device Lett.*, vol. 23, no. 6, pp. 339-341, Jun. 2002, doi: 10.1109/LED.2002.1004228.

- [13] J. MUiier, P. Polakowski, S. Millier, H. Mulaosmanovic, J. Ocker, T. Mikolajick, S. Slesazeck, S. Miiller, J. Ocker, T. Mikolajick, S. Flachowsky, and M. Trentzsch, "High endurance strategies for hafnium oxide based ferroelectric field effect transistor," in *Proc. Nol1-volatile Memory Technol. Symp.(NVMTS)*, Oct. 2016, pp. 1-7, doi: 10.1109/NVMTS.2016.7781517.

- [14] S. Deng, G. Yin, W. Chakraborty, S. Dutta, S. Datta, X. Li, and K. Ni, "A comprehensive model for ferroelectric FET capturing the key behaviors: Scalability, variation, stochasticity, and accumulation," in *Dig. Tech. Papers-Symp. VLSI Technol.*, 2020.

- [15] C. Alessandri, P. Pandey, A. Abusleme, and A. Seabaugh, "Monte Carlo simulation of switching dynamics in polycrystalline ferroelectric capacitors," *IEEE Tral1s. Electro11 Devices*, vol. 66, no. 8, pp. 3527-3534, Aug. 2019, doi: 10.1109/TED019.2922268.

- [16] M. Pe ic, F. P. G. Fengler, L. Larcher, A. Padovan, T. Schenk, E. D. Grimley, X. Sang, J. M. LeBeau, S. Slesazeck, U. Schroeder, and T. Mikolajick "Physical mechanisms behind the field-cycling behavior of Hf02-based ferroelectric capacitors," *Adv. Funct. Mater.*, vol. 26, no. 25, pp. 4601-4612, Jul. 2016, doi: 10.1002/adfm.206100590.

- [17] S. Mueller, J. Miiller, R. Hoffmann, E. Yurchuk, T. Schlosser, R. Boschke J. Paul, M. Goldbach, T. Herrmann, A. Zaka, U. Schroder, and T. Mikolajick, "From MFM capacitors toward ferroelectric transistors: Endurance and disturb characteristics of HfO2 -based FeFET devices," *IEEE TrallS. Electron Devices*, vol. 60, no. 12, pp. 4199-4205, Dec. 2013, doi: 10.1109/TED.2013.2283465.

- [18] T. P. Ma and J.-P. Han, "Why is nonvolatile ferroelectric memory field-effect transistor still elusive?" *IEEE Electron Device Lett.*, vol. 23, no. 7, pp. 386-388, Jul. 2002, doi: 10.1109/LED.2002.1015207.

- [19] Y.-S. Liu and P. Su, "Variability analysis for ferroelectric FET non-volatile memories considering random ferroelectric-0ielectric phase distribution," *IEEE Electron Device Lett.*, vol. 41, no. 3, pp. 369-372, Mar. 2020, doi: 10.1109/LED.2020.2967423.

- [20] K. Ni, A. Gupta, 0. Prakash, S. Thomann, X. S. Hu, and H. Amrouch, "Impact of extrinsic variation sources on the device-to--0evice variation in ferroelectric FET," in *Proc. IEEE /11!. Rel. Phys. Symp. (/RPS)*, Apr. 2020, pp. 1-5, doi: 10.1109/IRPS45951.2020.9128323.

- [21] P.D. Lomenzo, Q. Takmeel, C. Zhou, Y. Liu, C. M. Fancher, J. L. Jones, S. Moghaddam, and T. Nishida, "The effects of layering in ferroelectric Si-doped HfOi thin films," *Appl. Phys. Lett.*, vol. 105, no. 7, Aug. 2014, Art. no. 072906, doi: 10.1063/1.4893738.

- [22] J. Liao, B. Zeng, Q. Sun, Q. Chen, M. Liao, C. Qiu, Z. Zhang, and Y. Zhou, "Grain size engineering of ferroelectric Zr-doped HfO2 for the highly scaled devices applications," *IEEE Electron Device Lett.*, vol. 40, no. 11, pp. 1868-1871, Nov. 2019, doi: 10.1109/LED.2019. 2944491.