# **Applications and Impacts of Nanoscale Thermal Transport in Electronics Packaging**

Ronald J. Warzoha<sup>1,†,¶</sup>, Adam A. Wilson<sup>2,¶</sup>, Brian F. Donovan<sup>3</sup>, Nazli Donmezer<sup>4</sup>, Ashutosh Giri<sup>5</sup>, Patrick E. Hopkins<sup>5</sup>, Sukwon Choi<sup>6</sup>, Darshan Pahinkar<sup>7</sup>, Jingjing Shi<sup>8</sup>, Samuel Graham<sup>8</sup>, Zhiting Tian<sup>9</sup>, Laura Ruppalt<sup>10</sup>

<sup>1</sup>Department of Mechanical Engineering, United States Naval Academy, Annapolis, MD, 21402, USA

<sup>2</sup>United States Combat Capabilities Development Command Army Research Laboratory, Adelphi, MD, 20783, USA

<sup>3</sup>Department of Physics, United States Naval Academy, Annapolis, MD, 21402, USA

<sup>4</sup>Department of Mechanical Engineering, Boğaziçi University Bebek, Istanbul, 34342, Turkey

<sup>5</sup>Department of Mechanical and Aerospace Engineering, University of Virginia, Charlottesville, VA, 22807, USA

<sup>6</sup>Department of Mechanical Engineering, Florida Institute of Technology, Melbourne, FL 32901, USA

<sup>8</sup>George W. Woodruff School of Mechanical Engineering, Georgia Institute of Technology, Atlanta, GA, 30332, USA

<sup>9</sup>Sibley School of Mechanical and Aerospace Engineering, Cornell University, Ithaca, NY, 14853, USA

<sup>†</sup>Corresponding Author; e-mail: <u>warzoha@usna.edu</u> <sup>¶</sup>These authors contributed equally to this work.

# ABSTRACT

This review introduces relevant nanoscale thermal transport processes that impact thermal abatement in power electronics applications. Specifically, we highlight the importance of nanoscale thermal transport mechanisms at each layer in material hierarchies that make up modern electronic devices. This includes those mechanisms that impact thermal transport through: (1) substrates, (2) interfaces and 2-D materials and (3) heat spreading materials. For each material layer, we provide examples of recent works that (1) demonstrate improvements in thermal performance and/or (2) improve our understanding of the relevance of nanoscale thermal transport across material junctions. We end our discussion by highlighting several additional applications that have benefited from a consideration of nanoscale thermal transport phenomena, including RF electronics and neuromorphic computing.

# A. INTRODUCTION

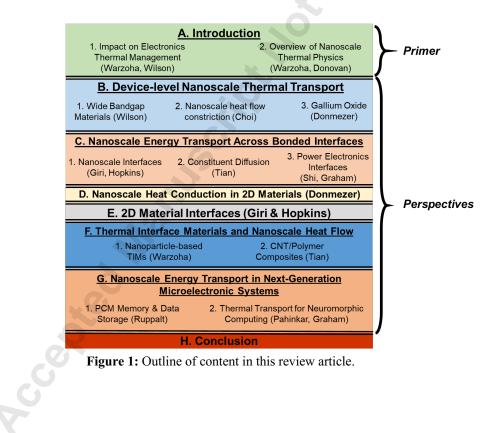

This review discusses relevant nanoscale thermal transport processes impacting thermal abatement in power electronics applications. In the introduction section, the impact of nanoscale thermal transport on electronics thermal management is established, and a primer is given on the physics governing nanoscale thermal transport. With core concepts established, several brief perspectives are provided on relevant topics dealing with nanoscale thermal transport in power electronics. Figure 1 depicts the organization of the contents of this paper.

# A.1. Impact on Electronics Thermal Management

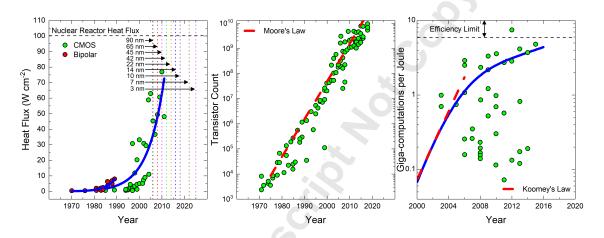

Electronics thermal management is critical to the implementation of modern computational architectures [1], power electronics [2], re-writeable media [3] and, more recently, data storage and transfer [4, 5]. Increasingly at odds with continued advancements in the performance of such applications, however, is a reduction in the characteristic length scales of heat generating elements that support primary functionality. The magnitude of this singular issue is now widely expected to result in the violation of Moore's Law within the next decade, captured by Fig. 2 and described below.

**Figure 2:** (a) Historical trend in heat flux of Bipolar and CMOS-based CPU architectures (data taken from [6, 7]) (b) Rate of increase in CPU transistor count relative to Moore's Law (red dashed line; data taken from [8, 9]) and (c) Computational efficiency of CPUs as a function of year and transistor length-scale (data and trends taken from [10]).

Moore's Law has remained stable for nearly five decades, principally due to advancements in cooling technologies and simultaneous improvements in computational efficiency with developments in parallel processing, GPU architectures and, more recently, 3-D chip stacks [11]. However, both computational efficiency and cooling technologies are beginning to approach their fundamental limits [12]. Consequently, Moore's Law for conventional CMOS-based architectures is predicted by some to run its course within the next decade [13-15]. Beyond these fundamental limits, the size of individual electronic components are fast approaching length scales that are on the order of the primary mean free paths of thermal energy carriers. FinFET technologies, for example, are expected to result in the fabrication of 3 nm transistors in the near future [16], orders of magnitude smaller than the majority of thermal carrier mean free paths in silicon [17]. As thermal management is concerned, the physics that govern heat dissipation within a material and across an interface are not the same as those experienced in bulk material systems. At these length scales, the physics that govern heat dissipation within a material and across interfaces deviate significantly from bulk thermal properties.

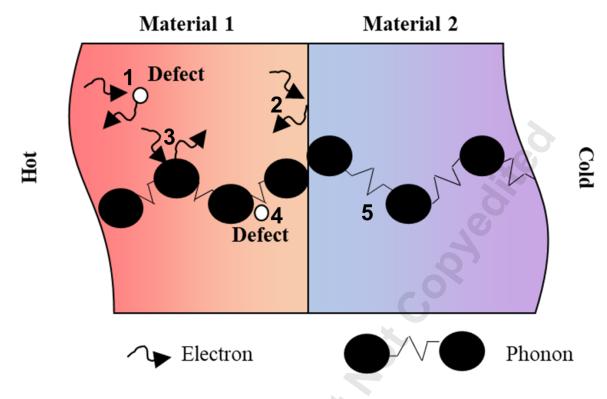

Accordingly, when exploring the thermal impact of electronic size scaling, we need to consider the nanoscale properties of the thermal carriers carefully. At these scales, heat energy carriers (primarily phonons in non-conducting materials) can be interrupted by atomic defects, phonon-phonon interactions, nanoparticles, grain boundaries, material mismatches in phonon density of states at a boundary and, in electrically conducting materials, electron-phonon and electron-interface interactions [18]. Figure 3 illustrates the variety of phonon scattering mechanisms that govern thermal transport at these length scales.

Given the level of complexity associated with nanoscale thermal transport physics and the scattering mechanisms outlined in Fig. 3, it is *critical* to understand and model these energy exchange and transfer mechanisms for the successful development and implementation of next-generation electronics devices. In this work we specifically focus on nanoscale thermal transport in next-generation microelectronic devices.

**Figure 3:** Schematic of phonon scattering mechanisms within individual materials and across interfaces, including: 1) electron-defect scattering [19], 2) electron-interface scattering [20], 3) electron-phonon scattering [21], 4) phonon-defect scattering [22], 5) phonon-phonon scattering [23] and 6) scattering across an interface based on mismatches in material density of states [24], interface surface roughness [25], etc.

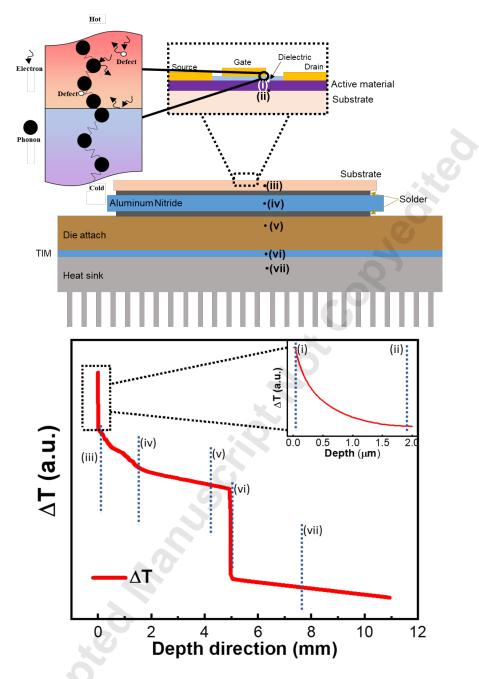

To demonstrate the key areas where phonon scattering plays a critical role in electronics packaging, we consider a typical electronic package configuration. This is depicted in Fig. 4, together with a representative temperature distribution of the device, which depends on the thermal resistance of each constituent element. The device is comprised of several layers of differing materials, interfaces between those materials, and a bulk substrate. The devices are packaged on die attached via thermal interface materials and are then coupled to a heat sink. Each of these components in the package contain opportunities for nanoscale thermal transport to provide a substantial enhancement in device performance. At the device level, the interfaces and small scale of the devices make nanoscale thermal metrology crucial for further development – whether the goal is to reach higher power or to continue trends in device miniaturization. At the package level,

nanoscale thermal transport is necessary to understand what makes a better thermal interface material, or how to remove heat from the package at the heat sink effectively. Furthermore, the materials used may see reduction in phonon scattering by removing scattering sites such as defects and dislocations via improved processing parameters, thus increasing the thermal conductivity of the layer adjacent to the interface. Therefore, in the electronics package, from material-level to device-level to packaging-level, nanoscale thermal transport is critical to further advances in performance.

**Figure 4:** Representative electronics package and active device temperature profile. Temperature profiles are combined from adapted data appearing in [26] and [27].

In this work, we put forth a series of perspectives constructed by the authors to highlight the nanoscale thermal physics used to model scattering mechanisms within materials and across interfaces. In particular, we provide the reader with analytical and numerical techniques that lend physical insight into heat flow through materials and interfaces that are critical in electronics packaging and discuss experimental evidence of these consequences in application. A final discussion of nanoscale thermal transport in RFbased devices and thermoelectric materials is provided to demonstrate the broad class of application space where these physics are critical to electronic device performance and cooling.

#### A.2. Nanoscale Thermal Physics

In the ensuing sub-sections, we provide a limited overview of the physics that are typically used to analytically model thermal transport both (a) within materials and (b) across device interfaces. These topics are covered in great detail elsewhere [18, 28-30] and are provided here to give those readers unfamiliar with nanoscale thermal transport context for the perspectives written as part of this work.

# A.2.i. Thermal Transport within Nanostructured Materials

In solids, heat is carried predominantly by electrons (for metals) and/or phonons (for non-conducting materials). At device length scales proportional to the mean free path of these energy carriers, scattering elements like grain boundaries and point defects can profoundly reduce the thermal conductivity of a material, which then makes thermal abatement significantly more challenging for packaging engineers. Consequently, a fundamental understanding of energy carrier scattering is critical to the design of thermal management solutions for next-generation packaging systems.

For electrically conducting materials, thermal conductivity ( $\kappa$ ) is governed by an electronic component ( $\kappa_e$ ) and a phononic component ( $\kappa_{ph}$ ) such that  $\kappa = \kappa_e + \kappa_{ph}$ . The

electronic component of thermal conductivity can be approximated by the Wiedemann-Franz Law [31],

$$\kappa_e = \sigma \cdot \frac{\pi^2}{3} \cdot k_{B,eV}^2 \cdot T \tag{1}$$

where  $\sigma$  is the electrical conductivity of the material (S/m),  $k_{B,eV}$  is the Boltzmann constant in electron volts, and T is the absolute temperature of the material (K). We note that the electronic structure and scattering in materials can result in the underprediction of  $\kappa_e$  when applying the Wiedemann-Franz Law, but for most electrically-conducting materials, the Wiedemann-Franz Law provides accuracy to within ~40% at non-cryogenic temperatures [32-34]. Several mechanisms can contribute to electron scattering, including electronelectron and electron-phonon scattering [35]. In the remainder of this work, we limit further discussion of nanoscale thermal transport to phononic contributions to thermal conductivity as the majority of our nanoscale constituents and interfaces include nonconducting materials.

Phonons are quantized lattice vibrations that are best thought of as a collective set of atomic oscillations about their equilibrium positions. The oscillations are governed by the atomic mass(es) of atoms, the strength of the bonds between neighboring atoms and the material system geometry. Together, these material characteristics synchronize the modes of vibration, which are collectively termed "phonons".

The phononic contribution to thermal conductivity can be quantitatively determined using a variety of analytical, numerical and experimental techniques. Commonly used analytical techniques include solutions to the Boltzmann Transport Equation (BTE) [36, 37] and augmentations to the well-known phonon gas model [38] (more on this below). Computational simulations can be performed using molecular

dynamics (MD) simulations [39-42], density functional theory (DFT) [43, 44] and Monte Carlo ray tracing simulations [45, 46]. Finally, nanoscale experimental techniques include electro-thermal characterization ( $3-\omega$  [47], transient electro-thermal [48, 49], and scanningprobe based [50-52] systems) and optical pump-probe thermoreflectance characterization (time-domain thermoreflectance, or TDTR [53-56] frequency-domain thermoreflectance, or FDTR [57-59] and steady-state thermoreflectance, or SSTR [60]).

We use the phonon gas model [18, 61] here to illustrate the impacts of nanostructuring on the intrinsic thermal properties of Si due to its simplicity and the ability to model independent scattering parameters such that we can demonstrate their potential impacts on thermal conductivity. This model represents the phonons in our system as a gas of energetic carriers with thermal energy, speed, and mean free paths that depend on the mode of vibration given by,

$$\kappa = \frac{1}{3} \sum_{j} \int_{0}^{k_{max}} C_{\nu,k} \cdot \nu_{j}^{2} \cdot \tau_{j} \, dk \tag{2}$$

where,

$$C_{\nu,k} = \frac{1}{2\pi^2} \sum_j \int_0^{k_{max}} \hbar \cdot \omega \cdot \frac{\partial f_{BE}}{\partial T} \cdot k^2 \, dk \tag{3}$$

In Eqn. 2,  $C_v$  is the volumetric heat capacity of the solid (J/m<sup>3</sup>·K), v is the phonon group velocity (or sound speed in a Debye approximation [62]) within the solid (m/s) and  $\tau$  is the phonon scattering time (s). In Eqn. 3, which assumes an isotropic, spherical Brillouin zone,  $\hbar$  is Planck's constant (J·s),  $\omega$  is angular frequency (rad/s),  $\partial f_{BE}/\partial T$  is the temperature-dependent Bose-Einstein distribution, and k is wave vector (rad/m). Note that one must incorporate contributions from all polarization branches, j, to compute the total thermal conductivity,  $\kappa$ , and volumetric heat capacity,  $C_v$ . There are several phonon scattering mechanisms that are particularly relevant to microelectronic and power electronic-based material systems. These include phonon-phonon scattering (or so-called "Umklapp" and "Normal" scattering),  $\tau_{ph}$ , baseline impurity scattering,  $\tau_{bulk}$ , boundary scattering,  $\tau_b$  and defect scattering,  $\tau_d$ . Boundary scattering refers to phonons that collide and scatter off of a physical boundary, which could be the characteristic dimension of the system (i.e., the layer thickness) or inherent boundaries within the system (i.e., grain boundaries). Likewise, the defect scattering term represents both point defects and vacancies.

Typically, the theoretical (or ideal) temperature-dependent thermal conductivity  $(\kappa(T))$  for a bulk material is used to determine the magnitude impact of phonon-phonon and baseline impurity scattering by fitting Eqn. 2 to [18],

$$\tau_{bulk} = \left(A \cdot T \cdot \omega^2 \cdot e^{-B/T} + C \cdot \omega^4\right)^{-1} \tag{4}$$

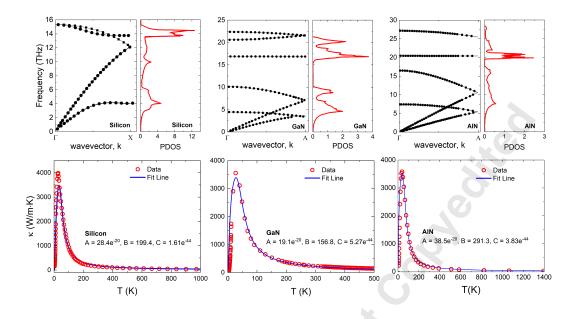

where A, B and C are fitting constants. Provided these fitting constants, one can then determine the impact that characteristic length-scales, material impurities and crystalline microstructure have on thermal conductivity. We choose to demonstrate the magnitude that length-scale has on thermal conductivity for three relevant materials: Si, GaN and AlN. Using the phonon dispersion provided above each temperature-dependent thermal conductivity distribution in Fig. 5, we determine constants A, B and C for each bulk material.

**Figure 5:** *Top*: Plots of phonon dispersion relations along a representative direction of high symmetry in the primitive unit cell for Si [63] (*left*), Wurtzite GaN [64] (*middle*) and Wurtzite AlN [64] (*right*) next to the phonon density of states [65] (units: States/THz-Unit Cell). Note that we assume a spherical, isotropic Brillouin Zone for the Wurtzite GaN and AlN only for instructional purposes. In a real Wurtzite material system, a more rigorous (and complex) anisotropic model must be used. *Bottom*: Temperature-dependent thermal conductivity for Si (*left*) [66], Wurtzite GaN (*middle*) [67] and Wurtzite AlN [68] (*right*) used to determine constants A [s·K<sup>-1</sup>], B [K] and C [s<sup>3</sup>] in Eqn. 4 (blue lines represent fit lines, and red circles represent data). Note that we fit to the dispersion branches using 4<sup>th</sup> order polynomial relationships.

With knowledge of these bulk fitting parameters (A, B, and C), we can accurately estimate the impact that scattering from additional mechanisms may have on material thermal conductivity. In this work, we provide the reader with context for the impacts that the characteristic length scale ( $d_{film}$ ), and the mass and concentration of defects ( $M_{def}$  and  $\phi_{def}$ ) have on the intrinsic thermal conductivity of the Si, GaN and AlN materials detailed in Fig. 5. To account for the impact that characteristic length scale has on thermal conductivity, we utilize [59],

$$\frac{1}{\tau_b} = \frac{v_g}{d_{film}} \tag{5}$$

where  $\tau_b$  is the boundary scattering parameter (s),  $\upsilon_g$  is the phonon group velocity (m/s) and  $d_{film}$  is the characteristic dimension (in this case the film thickness, m). Likewise, we

quantify the impact that both defect mass and concentration have on these thermal conductivities with [22],

$$\frac{1}{\tau_d} = \omega^4 \cdot \chi_d \cdot \left[ \left( \frac{\Delta M_d}{M_h} \right)^2 + 2 \cdot \left[ \left( \frac{\Delta G_d}{G_h} \right) - 6.4 \cdot \gamma \cdot \left( \frac{\Delta \delta_d}{\delta_h} \right)^2 \right] \right]$$

(6)

where  $\tau_d$  represents the defect scattering parameter,  $\omega$  is the angular frequency of the phonon modes (1/s),  $\chi_d$  is defect concentration,  $\Delta M_d$  is the difference in mass between the defect and the average host atom (M<sub>h</sub>),  $\Delta G_d$  is the difference in shear strength between the defect and the average host atom (G<sub>h</sub>),  $\gamma$  is the Grüneisen parameter and  $\Delta \delta_d$  is the difference between defect and average host atom radii ( $\delta_h$ ).

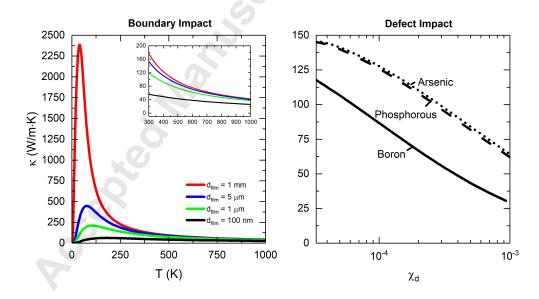

To vary the impact of characteristic length scale, the thermal conductivity of 100 nm to 1 mm-thick films of Si is determined using Eqns. 2 and 5 in tandem. Similarly, the concentration of defects ( $\chi_d$ ) is changed to demonstrate its impact on thermal conductivity. Both results are reported in Fig. 6.

**Figure 6:** *Left*: Thermal conductivity of Si as a function of temperature and film thickness (red line = 1 mm thick, blue line = 5  $\mu$ m thick, green line = 1  $\mu$ m thick and black line = 100 nm thick; Note: inset represents the same distribution over the high temperature range exclusively), *Right*: Thermal conductivity of Si as a function of defect concentration,  $\chi_d$ , for typical dopants B, P and As.

Figure 6 clearly indicates that nanostructuring can have an extreme impact on the thermal properties of microelectronics and power electronics-based materials. In this case, thin films of materials and material defects negatively impact (i.e., reduce) the thermal conductivity of the host material(s) and therefore increase the need for more aggressive thermal abatement strategies.

# A.2.ii. Thermal Transport across Nanostructured Materials

As with the thermal properties of the films themselves, thermal transport across thin-film interfaces can be impacted by nano-sized features. Critically, even perfectly bonded interfaces experience a temperature drop due to a finite thermal boundary conductance [30]. This is particularly important as device length-scales are reduced and the interfaces between materials begin to contribute more significantly to the overall thermal resistance in the device stack, rendering it difficult to remove heat at the device level. In general, this is not always a detriment; one can deliberately scatter phonons by engineering interfaces, which has proven critical for the development of advanced, nanostructured thermoelectric materials [63, 69, 70].

The conventional analytical framework for determining the so-called "thermal boundary conductance" (or  $h_{BD}$ ) across a bonded interface is predicated on whether energy carrier scattering occurs diffusely or is governed by acoustic reflections of phonons at a material junction. In particular, the Diffuse Mismatch Model (DMM) and Acoustic Mismatch Model (AMM) were developed to better understand heat flow across atomically smooth interfaces [71].

The AMM treats phonon scattering as a purely specular process at an individual interface (note that the analog to this treatment is the handling of optical reflections via Snell's Law [30, 72]). In order to quantify the thermal conductance across an interface, we

compute the difference in heat flux across the interface according to [35],

$$q''_{1\to2} = \frac{1}{4} \cdot \frac{\Gamma_{12}}{v_{j,1}^2} \cdot \sum_j \int_0^{\omega_m} \hbar \cdot \omega \cdot v_{j,1}^3 \cdot f_1(\omega, T_1) \cdot D(\omega) d\omega$$

(7)

where  $q''_{1\rightarrow 2}$  is the heat flux from side (or material) 1 of the interface to side (or material) 2 of the interface (W/m<sup>2</sup>),  $v_{1,1}$  is the longitudinal speed of sound for material 1 (s),  $\hbar$  is Planck's constant (J·s),  $f_1(\omega,T_1)$  is the Bose-Einstein distribution for material 1 and D( $\omega$ ) is the material density of states. We note that the upper bound of the integral in Eqn. 7 is the cut-off frequency of each phonon branch (where phonon cut-off frequency is related to the Debye Temperature,  $\theta_D$ , and the Boltzmann Constant,  $k_B$ , via  $\omega_m = k_B \cdot \theta_D / \hbar$ ). Additionally,  $\Gamma_{12}$  is represented as,

$$\Gamma_{12} = 2 \cdot \int_0^{\pi/2} \tau_{12} \cdot \cos\theta_1 \cdot \sin\theta_1 d\theta_1 \tag{8}$$

where  $\tau_{12}$  is the transmission coefficient for phonon transport across the interface at a given phonon frequency. The transmission coefficient for the AMM is found according to,

$$\tau_{12} = \frac{4 \cdot \rho_1 \cdot \rho_2 \cdot v_{l,1}^2 \cdot \cos(\theta_1) \cdot \cos(\theta_2)}{\left(\rho_1 \cdot v_{l,1} \cdot \cos(\theta_2) + \rho_2 \cdot v_{l,2} \cdot \cos(\theta_2)\right)^2} \tag{9}$$

In Eqns. 8 and 9,  $\rho$  is material density, v<sub>1</sub> represents longitudinal sound speed and  $\theta$  represents the incident polar angle for phonons that interact with (i.e. transmit or reflect across) an interface.

One must then compute  $q''_{2 \rightarrow 1}$  in order to calculate the net heat flux  $q''_x = q''_{1 \rightarrow 2} - q''_{2 \rightarrow 1}$ . Given the relationship between heat flux and thermal boundary conductance via Fourier's Law ( $q''_x = h_{BD} \cdot \Delta T$ , where  $h_{BD}$  is the thermal boundary conductance), and operating on a differential basis and in the limit as  $\Delta T \rightarrow 0$ , one obtains,

$$h_{BD} = \frac{1}{4} \cdot \sum_{j} \frac{\Gamma_{1,j}}{v_{1,j}^2} \cdot \int_0^{\omega_m} \hbar \cdot \omega \cdot v_{1,j}^3 \cdot \frac{\partial f_{BE,j}}{\partial T} \cdot D(\omega) d\omega$$

(10)

The AMM itself is typically reserved for computations of thermal boundary conductance at extremely low temperatures where the thermal phonon wavelengths are long relative to length scales of interfacial asperities (< 7 K [30]).

For most practical applications (particularly those that operate near or above room temperature), the DMM has proven to be more effective when predicting  $h_{BD}$ . The DMM assumes that phonon interfacial scattering is diffusive. In this case, phonons that traverse the boundary have no inherent memory of magnitude and direction, and thus repopulation of phonon states can occur within the bounds of the phonon density of states for the opposing material. The DMM makes modification to the transmission coefficient in Eqn. 9, which is represented by [73-75],

$$\tau_{12} = \frac{\sum_{j} \int_{0}^{\omega_{m}} \hbar \cdot \omega \cdot v_{2,j} \cdot f_{BE} \cdot D(\omega) d\omega}{\sum_{j} \int_{0}^{\omega_{m}} \hbar \cdot \omega \cdot v_{1,j} \cdot f_{BE} \cdot D(\omega) d\omega + \sum_{j} \int_{0}^{\omega_{m}} \hbar \cdot \omega \cdot v_{2,j} \cdot f_{BE} \cdot D(\omega) d\omega}$$

(11)

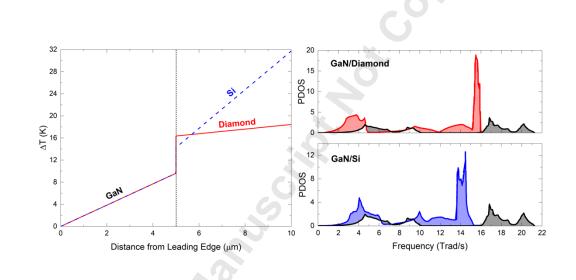

A variety of works have been performed to assess the validity of the above model, with variations to the transmission coefficient made to account for a full density of states when necessary (for instance, when the elastic constants at an interface are highly anisotropic [76]). Here, we elucidate the representative magnitude of  $h_{BD}$  on the overall thermal resistance of a multilayer system (where we compute the thermal resistance across the interface as  $R_{th,int} = 1/h_{BD}$ ) in the form of a temperature rise in Fig. 7 for GaN/diamond and GaN/Si. In these computations, we assume each layer is 5 µm thick and heat dissipation through the material system is q" = 5 kW/cm<sup>2</sup>, consistent with future device-level thermal abatement requirements [77, 78].

The thermal boundary conductances for each of the aforementioned interfaces are

provided in Table 1 alongside experimentally determined values from literature.

**Table 1.** Thermal boundary conductance ( $h_{BD}$ ) across GaN/diamond and GaN/Si interfaces computed withthe Diffuse Mismatch Model (DMM). DMM computations are compared to experimentally measured  $h_{BDs}$ at similar material interfaces.

| Interface   | DMM h <sub>BD</sub><br>(MW/m <sup>2</sup> ·K) | Experimental h <sub>BD</sub><br>(MW/m <sup>2</sup> ·K) |

|-------------|-----------------------------------------------|--------------------------------------------------------|

| GaN/Diamond | 30.88                                         | 24.39 - 58.82 [79]                                     |

| GaN/Si      | 35.07                                         | 30.3 – 128.21 [80]                                     |

**Figure 7:** *Left*: Temperature distribution across GaN/substrate stacks, inclusive of the interface (represented by the dotted black line), *Right*: Phonon Density of States overlap between GaN and diamond (top) and GaN and Si (bottom). Units for PDOS are States/THz-Unit Cell.

With little overlap in the phonon density of states (white region of overlap in the right-most plots in Fig. 7) between both GaN and diamond and GaN and Si, the  $h_{BD}$  across the interface is expectedly low relative to other material combinations having greater overlap (such as Al/Si, which has a reported  $h_{BD}$  of ~ 208 MW/m<sup>2</sup>·K [81]). As a result, there is a large temperature difference across the interface shown in the left-most plot of Fig. 7. Note that we do not account for any grain gradient distribution in either the GaN or

the diamond and instead assume a constant thermal conductivity through the thickness of each material. As will be discussed, however, many high-throughput growth techniques result in a grain gradient distribution that has significant impacts on thermal conduction through each material. Nevertheless, Fig. 7 demonstrates the importance of considering nanoscale interfacial thermal transport in electronics packaging material systems.

For the remainder of this work, the authors provide the reader with individual perspectives on the impacts of nanoscale thermal transport within and across relevant device features (such as those shown in Fig. 4). Each individual section is titled with individual author contributions, where each author in the manuscript has contributed a perspective (or series of perspectives) that reflect their area of expertise. The collection of contributing authors in this work was established with different elements of Fig. 4 in mind and within the specific context of nanoscale thermal transport.

#### B. DEVICE-LEVEL NANOSCALE THERMAL TRANSPORT

Mitigation of heat at the device and material level is critical to the successful development of next generation electronics devices. Substantial thermal challenges arise by: a) the selection and growth of materials and b) the interfaces between the active material and the other layers in the device. Perspectives on strategies to mitigate these challenges are presented in the next sections.

# **B.1.** Wide Bandgap Materials for High Power Devices and RF Electronics (Wilson)

The goals of electronic materials development have primarily been focused in two directions: faster switching speed (i.e. higher frequency) [82-84] and higher power [85-90]. In communications [82-84, 91, 92] and computational electronics [11, 13-15], higher

frequency is desirable, while higher power delivery is desired for electric vehicles [26, 88, 93], industrial and utilities [2, 94, 95], and military applications [96-98]. To move successfully in both directions, the industry must transition away from silicon, and to devices made from wide bandgap materials.

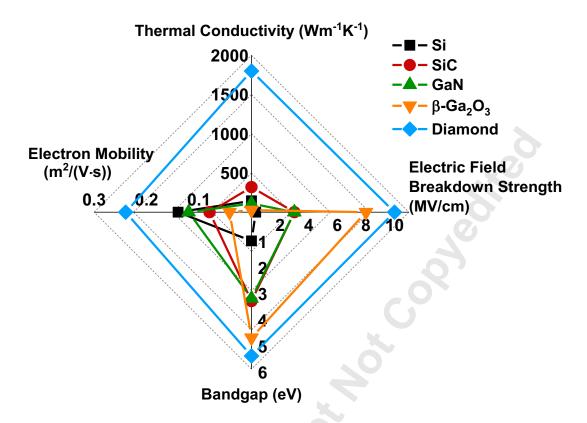

To that end, several materials have been researched to replace silicon as a semiconductor material. However, due to established procedures and architectures in place, and a lack of material that can be readily folded into existing manufacturing capabilities, silicon remains the material most widely used in semiconductor devices [88, 90], despite several important limitations in key properties for performance. These include: maximum electric field strength before breakdown, maximum operating temperature, thermal conductivity, electron mobility, and bandgap [88, 99]. Wide bandgap (WBG) materials (with bandgap greater than 1.5 eV) offer potentially viable alternatives to silicon. Viable alternatives include SiC, GaN-based devices, GaO<sub>x</sub>, and diamond-based devices. Performance metrics either substantially surpass or rival those of silicon in each case. Figure 8 depicts a comparison of properties of wide-bandgap materials proposed as alternatives to Si. Data found in Figure 8 are from literature values at room temperature, reported in references [27, 66, 100-113].

Figure 8. Web plot depicting relative strengths of several WBG electronics options

For each WBG material, the benefits, drawbacks, and current outlook are summarized. Because SiC is a well-understood material, and devices using it are mature technology, currently in use in many commercial products with advantages over Si wellestablished, discussion on SiC as a WBG material is skipped. For more information on SiC as a WBG material, please read [87].

# B.1.i. Diamond

It can clearly be observed that diamond boasts advantage over silicon in every area in Fig. 8. Research has been heavily focused in this area, and recent demonstrations have shown that diamond can be made into an electronic material [43, 66, 102, 104, 114-121]. However, several substantial challenges with production, integration, doping, and contacts remain [114, 115]. For many years, diamond was regarded as an excellent choice for passive thermal regulation, but because of high processing temperatures, it was doubtful that it would be useful as an active material [94]. However, as recently as 2018, it has been shown that diamond can be made as a robust active material, with excellent electron and hole mobility [94]. Terminating the diamond with hydrogen allows for a 2-dimensional hole gas (2DHG) to form, significantly boosting maximum current (from ~1 mA/mm to ~100 mA [94]). However, it is difficult to control doping levels and device performance for both n-type and p-type diamond [94, 116]. This may potentially be remedied by hybridizing WBG materials to achieve high power, high frequency devices [122, 123].

Thermal conductivity is routinely touted as a superior characteristic of diamond, boasting a value of over 2000 Wm<sup>-1</sup>K<sup>-1</sup>[124]. However, in practice, diamond grown by chemical vapor deposition (CVD) or epitaxy is susceptible to significantly varying thermal properties in-plane versus cross-plane. While thermal conductivity is extremely high within a grain (~1800 Wm<sup>-1</sup>K<sup>-1</sup> [66]), diamond grown by CVD tends to form a seed layer as the film begins growth. This leads to significant phonon scattering at the grain boundaries, reducing the thermal conductivity in the direction perpendicular to grain boundaries by nearly a factor of four (to ~500 Wm<sup>-1</sup>K<sup>-1</sup>) [102]. Also, due to expense, diamond is typically grown in thin-film form. Due to diamond's extremely large phonon mean free path, size effects play a significant role, even at high temperatures. Donovan & Warzoha theorize that 50nm diamond films will have thermal conductivity less than 100 Wm<sup>-1</sup>K<sup>-1</sup> [125]. Thermal conductivity of doped diamond is also significantly reduced compared with pristine diamond; boron dopants with >10<sup>19</sup> concentrations have been shown to lead to thermal conductivity values of only 700-1200 Wm<sup>-1</sup>K<sup>-1</sup> at room temperature [126, 127]. The literature is surprisingly sparse on thermal conductivity of doped diamond and hydrogen-terminated diamond, and this is a point of concern. Since diamond's ultra-high thermal conductivity hinges on its large phonon mean free path, it is critical to characterize the effect of adding dopants or altering termination bonds on the thermal conductivity of diamond.

Overall, the outlook on diamond electronics is quite promising. Given the progress made in the field in very recent years, diamond is well-poised to emerge as the best option among WBG semiconductors to advance power and RF electronics.

# *B.1.ii. Ga*<sub>2</sub>*O*<sub>3</sub>

Gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) has recently garnered significant attention as a WBG material, owing to its low cost, wide bandgap (4.7 eV), and advantageous electrical performance properties compared with other WBGs and especially silicon [128, 129]. Compared with Si, SiC, and GaN,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is projected to be much more efficient and have a much higher electric field break-down strength [130], and is thus potentially ideal for high-voltage applications.

However,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has relatively low electron mobility (~4.67x lower than Si), and is therefore not well-suited for high-frequency applications. Perhaps the most substantial issue with  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is that it significantly lacks ability to conduct heat. Thermal conductivity in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is highly anisotropic, and is significantly lower than other WBGs and Si (~27 Wm<sup>-1</sup>K<sup>-1</sup> in the (001) direction and ~12 Wm<sup>-1</sup>K<sup>-1</sup> in the (100) direction)[103]. Proponents of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> suggest that thermal conductivity matters less for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> than other WBG materials due to substantial enhancements in efficiency, temperature stability, and maximum temperature operation [130]. However, devices will generate heat as they operate, and that heat will need to be dissipated, which  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is not well-equipped to do. Interestingly,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> shares many of the phonon scattering characteristics of GaN, which has around ten times larger thermal conductivity [131]; however, three-phonon scattering processes dominate in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, leading to a much shorter phonon relaxation time, which manifests as a significant reduction in thermal conductivity. To mitigate this issue,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has been applied to higher thermal conductivity substrates (such as diamond) [132]. However, the interface thermal resistance between  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and diamond, as well as between  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and metal have been found to be quite large [132, 133]. This is attributable to differences in the phonon density of states between  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and the other materials. Recently, it was demonstrated that by adding a carefully selected interlayer, thermal boundary conductance between metal and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> can be significantly enhanced, by more than 10x [133].

The outlook on  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is promising; however, thermal challenges will be a significant barrier to realization in a commercial device. The path to successful integration in high power electronics will be through thin layers of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> on interfaces that have been engineered to enhance phonon transport, thereby mitigating the deleterious effects of the poor thermal properties of the material itself.

# B.1.iii. GaN

GaN is exceedingly attractive for the manufacturer, especially for high voltage operation, and high switching frequencies. These devices are capable of operating at high voltage and high frequency by nature of the two-dimensional electron gas (2DEG) that is formed between the typical AlGaN layer deposited on GaN. This 2DEG forms due to spontaneous polarization of GaN, as well as a large discontinuity in the conduction band between the GaN and AlGaN layers. The properties of the 2DEG change significantly in the presence of electric fields. Electron mobility is extremely high for AlGaN/GaN heterostructures (>2000 cm<sup>2</sup>/(V·s)) [134]. There are several other practical benefits to using AlGaN-based devices as well including current density [134], boost in switching frequency [88], etc. However, the early developers of these devices did not consider thermal properties (particularly thermal resistance added at heterogeneous material interfaces) among the most important concerns. Since bulk GaN has thermal conductivity comparable to Si, substrate thermal conductivity is a severely limiting factor. Because of this, GaN device layers are frequently removed from substrate and attached to substrates of higher thermal conductivity (or grown on substrates other than Si or sapphire) [135].

Recent studies have shown that the thermal boundary resistance at heterogeneous material interfaces (especially between active material and substrate) may account for a substantial portion of the overall device thermal resistance [136-139]. Graham, et. al., have reported values recorded by them and others [137, 140-142] of GaN-based devices on various substrates and find that although substrate thermal conductivity may be vastly improved by replacing Si with SiC or diamond, interface thermal resistance may take a hit (going from a record low of 1.5 to 2 m<sup>2</sup>K/GW for GaN on Si to ~10-100 m<sup>2</sup>K/GW for GaN on diamond [115, 119, 143]).

Although much attention has been given to the interface between GaN and the substrate, very little attention has gone into investigating the thermal resistance that occurs between the active layers in the device and the metallization, or even the interface between

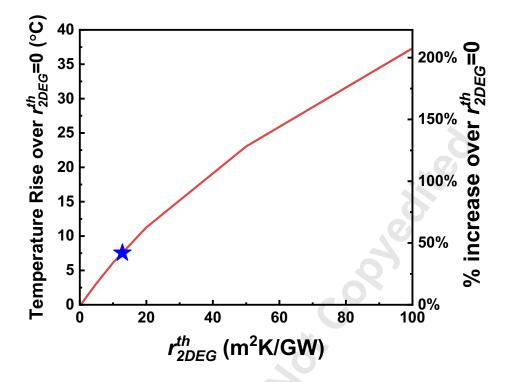

AlGaN and GaN, where the 2DEG forms. Several recent studies have proposed methodologies for probing the peak device temperature, using a combination of thermoreflectance and Raman temperature measurement techniques [144, 145]. In conjunction with multi-scale finite element and molecular dynamics models, accurate determination of the peak temperature rise in the devices for a given measured temperature rise at the surface or of the volume may be inferred [144, 146]. However, owing to the interfaces that are necessary to make a device with AlGaN on GaN, the overall thermal resistance of the devices increases, leading to peak temperature rise of up to 42% over the case where the interface is perfectly thermally conductive.

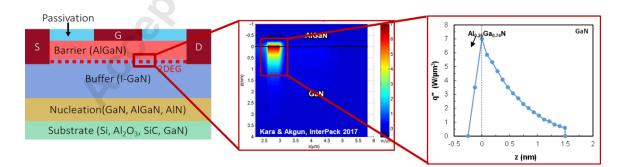

Figure 9 depicts this, based on a combination of 3DFE simulations from a phonon hydrodynamic model, and experimental measurements of the AlGaN/GaN interface via FDTR [147]. Therefore, in power electronics, material properties as well as properties of material interfaces are critically important to the development of better devices. Thermal resistance in multi-layered structures leads to significant build-up of peak temperature, while bulk thermal conductivity is the limiting factor when using substrates with lower thermal conductivity. In both cases, processing conditions, functionalization, and careful selection of interstitial layers will allow for optimal thermal performance of wide-bandgap devices to be used in power and RF electronic devices.

**Figure 9.** Effect of AlGaN/GaN interface on peak temperature in AlGaN/GaN HEMTs. Adapted from [147]with permission, ©2019 IEEE.

#### B.2. Nanoscopic heat flow constriction in wide bandgap (WBG) electronics (Choi)

5G wireless networks offer significant advantages over the current 4G technology, including higher speed and lower latency, suitable for serving as the backbone of the Internet of Things (IoT), connecting more than a trillion devices to the internet. However, in order to compensate for the increased energy and range demands arising from the network growth, significant improvement in the energy efficiency of base stations is necessary[83]. Approximately 60% of the total power consumption of base stations is attributed to the loss associated with radio frequency (RF) power amplifiers[91].

Gallium nitride (GaN)-based radio frequency (RF) power amplifiers, that feature broadband operation and high efficiency, are key components to realize 5G network base stations and small cell applications including mobile devices[82, 84]. However, the last

piece of the puzzle to enable GaN for 5G is to overcome thermal reliability concerns stemming from localized extreme temperature gradients beyond predictions based on macroscale heat transfer principles such as Fourier's law of heat conduction.

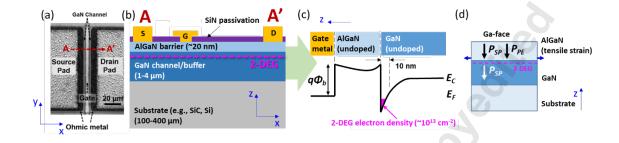

**Fig. 10.** (a) Top view and (b) cross-sectional structure of a GaN HEMT. (c) Conduction band ( $E_C$ ) bending near the AlGaN/GaN heterointerface forms a quantum well below the Fermi level ( $E_F$ ) and 2-DEG[148]. (d) Spontaneous ( $P_{SP}$ ) and piezoelectric ( $P_{PE}$ ) polarization effects result in massive electron accumulation in the quantum well[149].

Fig. 10 (a) and (b) show the structure of a GaN-based high electron mobility transistor (HEMT)[89, 150-154]. To construct the device, a 1-4  $\mu$ m thick GaN layer is heteroepitaxially grown on a non-native substrate where the common choices are silicon (Si) and silicon carbide (SiC) substrates. Subsequently, a thin (~20 nm) aluminum gallium nitride (AlGaN) layer is pseudomorphically grown over GaN. A physical effect that governs the device behavior is the formation of a two-dimensional electron gas (2-DEG)[149] which serves as the current channel. The 2-DEG is an electron aggregate that is free to move in two dimensions (x- and y-directions in Fig. 10), but tightly confined in the third dimension (z-direction). Accumulation of the high density 2-DEG without impurity doping is due to the formation of a deep spike-shaped quantum well at the AlGaN/GaN heterointerface, where there is a large conduction-band offset (Fig. 10 (c)). A vast amount of electrons are drawn into the quantum well due to the large piezoelectric polarization induced via tensile strain built in the AlGaN layer (Fig. 10 (d)). This translates

into a large current-carrying capability between the drain and source electrodes compared to conventional devices[149, 155]. The current level can be modulated (reduced) by applying a negative gate voltage to partially deplete the 2-DEG channel. The wide band gap ( $E_G$ =3.4 eV) of GaN results in a breakdown field of ~3 MV/cm which is an order of magnitude larger than that for conventional materials that have been used to build RF power amplifiers. This enables higher voltage operation with a smaller device footprint.

The power amplifier's role is, as the name suggests, to convert a small input signal (e.g., the gate voltage of a transistor) into a much larger power (current×voltage between the drain and source electrodes) to be delivered to the load. Therefore, GaN HEMTs, when employed as RF power amplifiers, offer high power density (=current×voltage/active area), power added efficiency, gain and ease in impedance-matching that significantly improves the overall efficiency in the RF chain. Moreover, the ability of GaN transistors to work in the high-frequency range gives promise for them to evolve from 5G base stations to small cell applications and, potentially into mobile devices.

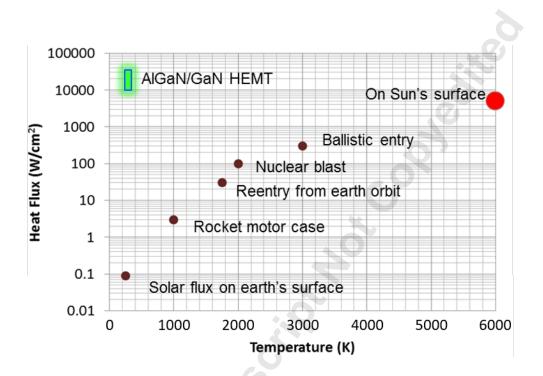

However, this substantial improvement in size, weight, and power translates into extreme power densities (>50 kW/cm<sup>2</sup>) in the active region of GaN HEMTs as shown in Fig. 11[92, 156]. Thermal failure (Fig. 11 (b)) and reduced component lifetime[157, 158] caused by device self-heating are major roadblocks to the successful implementation of GaN technology into 5G network components. Intense channel temperature rise caused by high voltage and power operation[159] was shown to trigger and aggravate various degradation mechanisms[160-164]. Such failure mechanisms include mechanical damage in the AlGaN barrier due to induction of thermo-elastic stress[159] and thermally-assisted inter-diffusion at the semiconductor/metal interface[165]. Although GaN HEMTs have

been commercialized for small-scale applications (e.g., laptop chargers), questions regarding GaN device thermal reliability remain unanswered[166, 167], as evidenced by the continued research into their life expectancies[157, 168, 169].

Figure 11. GaN HEMT heat flux challenge.

The industry-standard method to estimate GaN HEMT lifetime is the temperatureaccelerated direct current operational-life test[170]. The Arrhenius extrapolations reported in the literature[157, 169] show extremely long predicted median times that significantly over-predict the actual device lifetime in field applications. This is a major concern in industry because such false prediction may lead to catastrophic events in reliability-critical applications[157, 168, 169]. The over-prediction of device lifetime stems from inaccurate estimation of the device peak temperature at the site of degradation/failure during the accelerated high power testing. It was shown that an error of only 2°C in the estimation of device peak temperature used in the temperature-accelerated life test can skew the predicted lifetime by a factor of two[166, 167].

Currently, industrial practices for device thermal analysis and accelerated direct current operational life tests[157, 169] rely on simulation data based on the simple and widely accepted Fourier's law of heat conduction. However, a limited number of pioneering theoretical studies[170-174] have suggested that a nanoscale temperature spike or a socalled "hot-spot" forms in GaN HEMTs, which can be significantly hotter than predictions based on purely diffusive thermal transport models (i.e., the Fourier's law of heat conduction). This unanswered question has inhibited the use of GaN devices for high power RF applications where demonstrated long product lifetimes are required[158, 175].

In practice, large voltages are applied between the drain and source (e.g.,  $V_{DS}$ =28-48 V) of GaN RF power amplifiers to reduce or eliminate the need for step-down voltage conversion to match the operating voltage of commercial systems (e.g. wireless base station)[176]. In addition, the wide bandgap of the material allows the use of considerably shorter channel lengths (several microns) than conventional devices. This results in considerable electric field concentration within the 2-DEG channel underneath the drain side corner of the gate[177].

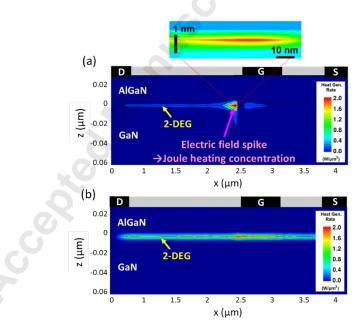

Fig. 12 shows heat generation profiles of a GaN HEMT under two different bias conditions resulting in an identical total power dissipation (e.g.,  $P_{DISS}=V_{DS}\times I_{DS}=500$  mW;  $P_{DISS}$ ,  $V_{DS}$ , and  $I_{DS}$  stand for dissipated power, drain-source voltage, and drain-source current, respectively). Fig. 12 (a) shows the Joule heating is highly concentrated beneath the drain end of the gate for high voltage-low current conditions (e.g.,  $V_{DS} = 50$  V,  $V_{GS} = -1$  V,  $I_{DS} = 10$  mA). On the other hand, Fig. 12 (b) shows that a relatively uniform Joule

heating distribution occurs for low voltage-high current conditions (e.g.,  $V_{DS} = 5$  V,  $V_{GS} = 2.5$ V,  $I_{DS} = 100$  mA). For low voltage-high current conditions, the lower  $V_{DS}$  produces the same amount of power dissipation (500 mW) since the channel is fully open (manifested by a large  $I_{DS}$ ). The 2-DEG current flow is not constricted, causing the heat generation profile to be relatively uniform across the entire channel. In contrast, for high voltage-low current conditions, to accomplish an identical power dissipation,  $I_{DS}$  is restricted by applying a negative voltage on the gate ( $V_{GS}$ ), thereby forming a local depletion region that partially pinches off the channel. This local depletion region with high electrical resistance causes spatial confinement of the 2-DEG Joule-heating. This leads to formation of a nanoscale hotspot[170, 172-174] subject to extreme local heat flux (>1 MW/cm<sup>2</sup>). According to fully-coupled electro-thermal simulation[158, 175, 178] shown in Fig. 12 (a), the domain size of the peak heat generation zone can be less than 10 nm×50 nm which is in agreement with theoretical predictions in literature[172, 179].

**Figure 12.** (a) Nanoscale spatial confinement of the heat generation zone under a high voltage-low current condition. (b) Uniformly distributed heat generation occurs under low voltage-high current open channel conditions.

The thermal conductivity of solids can be resolved as a function of phonon mean free path[180] via a thermal conductivity accumulation ( $k_{accum}$ ) function:

$$k_{accum}(\Lambda,T) = \sum_{s} \int_{0}^{\Lambda^{*}} \frac{1}{3} c(\Lambda,T) \cdot v(\Lambda,T) \cdot \Lambda(T) d\Lambda$$

<sup>(12)</sup>

where  $\Lambda$  is the phonon mean free path, T is the temperature, c is the volumetric heat capacity per unit phonon mean free path, v is the phonon group velocity, and s indexes the phonon polarizations (i.e., different vibrational modes). Since the integral is defined from 0 to  $\Lambda^*$ ,  $k_{accum}$  quantifies the contribution of phonons with a mean free path less than  $\Lambda^*$  to the overall bulk thermal conductivity.

The thermal conductivity accumulation function of GaN[181] indicates that phonons with  $\Lambda$  less than 550 nm and 1000 nm contribute to ~50% of the bulk thermal conductivity of GaN at T= 415 K and 309 K, respectively. At higher temperatures, the larger phonon population results in more frequent phonon-phonon scattering events which reduce the effective mean free path of the principal heat carriers (i.e., phonons).

Under high voltage-low current operation (Fig. 12 (a)), because of the extreme heat source size reduction, heating would take place primarily over length scales less than the mean free path (MFP) of phonons tasked with energy delivery. As mentioned above, phonons with mean free paths greater than ~550 nm are responsible for more than 50% of the thermal conduction in the GaN lattice at ~400 K[182, 183]. Therefore, within the nanoscale heat source domain (< 50 nm), the opportunity to effectively transport energy away via phonons with longer mean free paths (> 550 nm) is lost, i.e., the onset of ballistic transport occurs. Thus, this nanoscopic "heat source size effect" will restrict thermal

transport from the device hot-spot causing a net increase in channel temperature beyond predictions based on Fourier's law.

A recent study[184] has investigated the self-heating behavior of a GaN HEMT fabricated on a Si substrate operating under high  $V_{DS}$ -low  $I_{DS}$  conditions that are expected to cause non-Fourier thermal transport. A near-ultraviolet (UV) thermoreflectance imaging technique and a coupled 3D electro-thermal model[178] that accounts for ballistic-diffusive thermal transport effects were used to study amplified heating beyond predictions solely based on the Fourier's law of heat conduction.

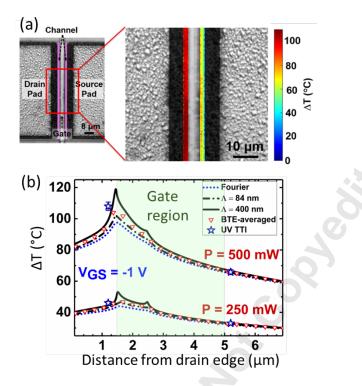

Temperature measurement of the device channel was performed using a near-UV illumination source with a center wavelength of 365 nm. Results are shown in Fig. 13 (a). The diffraction limited lateral spatial resolution was 300 nm. Since absorption is strong near the GaN surface for near-UV illumination, the measured temperature was weighted toward the 2-DEG channel region, within ~55 nm[185-189] from the GaN surface. The coupled electro-thermal modeling scheme was similar to that in [158, 167, 178] but was extended to three dimensions. This device model was developed to validate the near-UV thermoreflectance results. The coupled modeling scheme self-consistently solved, for each mesh point, the Poisson, current continuity, and electro-hydrodynamic equations (for electronic transport), and the Boltzmann transport equation (BTE)[170, 172] (for thermal transport) to derive the electrostatic potential, electron/hole concentration and their energy/temperature distributions, heat generation, and electron/hole/lattice temperature rise. Consequently, the model accounted for the nanoscopic heat source size effect.

**Figure 13.** (a) Near-UV thermoreflectance temperature map of a device channel for  $V_{DS}$ =45 V,  $V_{GS}$ =-1 V, and  $P_{DISS}$ =500 mW. (b) Comparison of temperature profiles across the 2-DEG channel obtained by near-UV thermoreflectance, Fourier- and BTE-based simulation. Images were adapted from [184].

Channel peak temperatures were deduced from experiments and modeling for multiple bias conditions. Results are displayed in Fig. 13 (b). Measurement, Fourier-, and BTE-based simulation shown excellent agreement for low to moderate  $V_{DS}$  bias conditions for all tested power dissipation levels. In stark contrast, a large disagreement (>10%) in channel peak temperatures between the Fourier and BTE simulation results was observed for high  $V_{DS}$  conditions, for all tested power dissipation levels (Fig. 13 (b)). Moreover, experimental values shown excellent agreement with the simulated temperature profiles from the BTE gray model reflecting the mean free path spectra of GaN acoustic phonons[170, 183, 190-193]. Results of this study clearly suggest that non-Fourier thermal transport mechanisms are in play, leading to the observed amplified heating. Many laser-based pump-probe

experiments[181, 194-200] support this experimental study. They have demonstrated that under conditions where the heat source domain size is less than the mean free path of dominant heat carriers, the heat source region exhibits a local reduction of the effective thermal conductivity compared to the bulk value.

#### **B.3.** Gallium Oxide: A Promising Ultra-wide Bandgap Material (Donmezer)

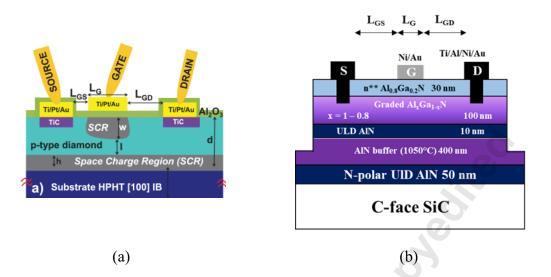

A new and exciting group of materials emerging within the electronics community is the ultra-wide bandgap (UWBG) materials. These materials, such as AlN, diamond, cubic BN and  $Ga_2O_3$  (with bandgaps that exceed 3.4 eV), have the potential for superior performance relative to conventional and wide band-gap materials such as GaAs and GaN. Devices fabricated from these materials are still immature due to a variety of fabrication challenges and material performance limitations. The absence of readily available largearea, low-defect density, single-crystal substrates and doping control issues remain fabrication challenges for the commercialization of AlGaN/AlN and diamond based electronic devices. Despite these problems, researchers fabricated functioning electronic devices such as diamond [201] and AlN/AlGaN field effect transistors [202-204] as shown in Fig. 14.

Figure 14: Schematic of (a) diamond (recreated from [201]) and (b) AlGaN/AlN (recreated from [204]) field-effect transistors.

Among all UWBG materials,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is the most promising one since low-cost and large substrates are available for its growth [205].  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> power devices are poised to reach the commercial sector with performance rivaling or surpassing that of GaN and SiC devices at much lower cost.

Although not investigated in detail, thermal problems observed in high-power devices are also present. Similar to AlGaN/GaN HEMT transistors and Si MOSFETs, these devices experience reliability issues associated with localized heating in their active areas. Thermal transport from the active areas is controlled by the thermal conductivity of each material and the thermal boundary conductance ( $h_{BD}$ ) between individual material layers. Epitaxial material layers can have thicknesses varying between tens of nm (as in Fig. 14) to a few µm. Thus they often have thermal conductivities smaller than their bulk counterparts due to thin film size effects. Diamond, which has a much larger bulk thermal conductivity than most other substrates due to longer phonon mean free paths, suffers as a result of these size effects to an even greater extent. Alloy semiconductor layers such as AlGaN with low thermal conductivity due to additional phonon scattering events caused

by the alloy particles also requires special attention.  $h_{BD}$  between material layers caused by the significant lattice mismatch can also play a significant role in heat transfer.

To design better performing devices, accurate thin film thermal conductivities and  $h_{BDS}$  obtained via experimental and/or theoretical approaches should be used for thermal characterization studies. Bulk  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has low thermal conductivity (k = 15 W/m·K) and is doped in most of its functioning devices. Moreover, its thickness is often in the range of hundreds of nanometers. These factors may lead to further reduction in thermal conductivity in accordance with the physics presented within the Introduction (Nanoscale *Thermal Physics*). In the past, thermal conductivities of doped and undoped bulk and thin film  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> samples were measured at different temperatures using techniques such as  $3\omega$  and time domain thermoreflectance (TDTR) [206-208]. Thermal conductivities of 300 -1000 nm thick AlN thin films obtained using  $3\omega$  technique are measured to be between  $k = 5.4 - 17.7 \text{ W/m} \cdot \text{K}$  [209]. Moreover, phonon thermal conductivity - mean free path spectra of UWBG materials obtained through experimental and theoretical approaches can be used the predict size dependence of thermal conductivity [181, 210]. Finally, the h<sub>BDS</sub> between β-Ga<sub>2</sub>O<sub>3</sub>/diamond[132], β-Ga<sub>2</sub>O<sub>3</sub>/metal [133], and AlN/AlGaN [211] interfaces have been obtained using a variety of experimental and theoretical approaches. These findings generally show that the already low thermal conductivity of UWBG materials is further reduced in their thin film form; when combined with the low h<sub>BD</sub> between these materials and their substrates, a thermal bottleneck can form and result in inadequate heat dissipation. Consequently, the impacts that nano-sized features have on thermal transport within the device and at its boundaries should be considered carefully in device analysis.

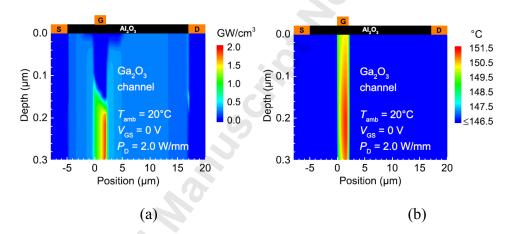

With the help of accurate thermal conductivities and  $h_{BDS}$ , thermal characterization of devices can be performed through simulations to analyze device temperatures and provide relevant metrics for thermal solutions. Past attempts have used anisotropic thermal conductivities of Ga<sub>2</sub>O<sub>3</sub> (though ignored the impact of potentially high  $h_{BDS}$ ) to analyze MOSFET and MESFETs through electro-thermal simulations[212-214]. Although this remains an area under active investigation, results from previous studies highlight the importance of non-uniform Joule heating distribution and its effects on temperature, as shown in Fig. 15. Non-uniform heating distribution is also observed near Schottky junction of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> diodes [215], in MISFETs with h-BN gate insulators [216], and expected in vertical FinFETs [217].

Figure 15. Simulated (a) lattice temperature and (b) heat power contours in the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOSFET [212].

Electro-thermal simulations of devices are mainly performed with commercial electrical device simulators (i.e. ATLAS, Sentaurus, Silvaco etc.) which solve Fourier's heat diffusion equation to obtain temperature distribution in devices. Yet, when the heat is localized, heat transfer becomes partially ballistic in these regions. When this is the case Fourier's heat diffusion equation is no longer valid. Even though one can use size dependent thermal conductivities for material layers it won't be sufficient to characterize

the thermal transport in localized hotspots. To obtain accurate temperatures profiles, ballistic-diffusive effects should be considered by solving the phonon Boltzmann Transport Equation (BTE) [170]. The gray phonon BTE is expressed by:

$$\nabla \cdot \left( v_g \vec{s} e \right) = \frac{e^0 - e}{\tau} + q^{\prime \prime \prime} \tag{13}$$

where *e* is the integrated energy density found by integrating the phonon energies along all frequencies and polarizations, q''' is the volumetric heat generation term that represents the Joule heating of the device,  $\tau$  is the relaxation time,  $v_g$  is the phonon group velocity, and  $\vec{s}$  is a unit vector pointing in the direction of the phonon group velocity [218].

Therefore, Joule heating distribution, ballistic-diffusive heat transport near hotspots, thin film thermal conductivities, and  $h_{BD}$  values should all be considered for accurate device simulations, and highlights the importance of nanoscale energy transport considerations for thermal management of high-power electronic devices. Additionally, accurate representations of the device geometry and its peripheral components with an appropriate 3D model and the proper selection of thermal boundary conditions is critical to understanding such impacts on device performance. Therefore, the development of multiphysics and multiscale simulation techniques with reasonable computational cost is crucial for the development of next-generation UWBG devices.

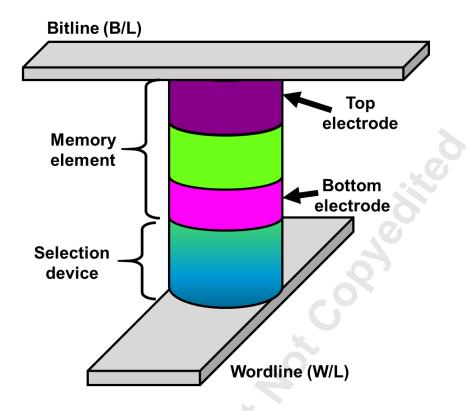

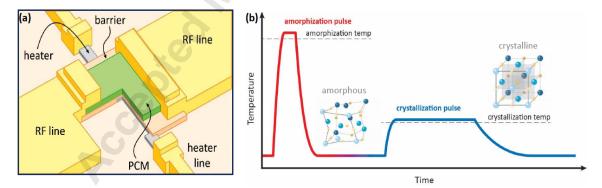

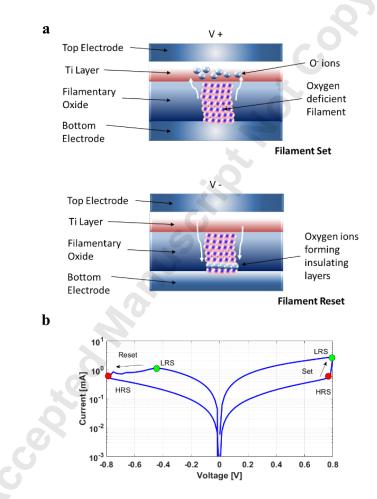

### C. NANOSCALE ENERGY TRANSPORT ACROSS BONDED INTERFACES

The performance of high power electronics, thermoelectrics, phase change memory, and logic circuits are frequently limited by the thermal boundary resistance ( $R_{th}$ ) at interfaces of devices [219, 220]. These interfaces are designed to optimize the electrical

performances without considering thermal management at the same time. As characteristic length- and time-scales become comparable to the mean-free-paths and lifetimes of energy carriers in materials and devices, thermal resistance associated with interfaces between solids can become a major impediment and may lead to thermal breakdown of devices if heat cannot be dissipated efficiently [221]. R<sub>th</sub> is sometimes comparable to (or even larger than) the thermal resistance of materials, thus contributing significantly to the overall resistance of the whole device. Therefore, increasing thermal boundary conductance ( $h_{BD}=1/R_{th}$ ) is necessary in order to maintain reasonable device temperature to avoid thermal breakdown.

For typical crystalline interfaces where heat transfer is primarily driven by lattice vibrations, typical values of measured  $h_{BD}$  are in the range of ~20 to 300 MW/m<sup>2</sup>·K ( $R_{th} \approx 3.3 \cdot 10^{-9}$  to  $50 \cdot 10^{-9}$  m<sup>2</sup>·K/W). In addition to the fundamental properties of the energy carriers in the two solids, interfacial resistance also depends on a variety of other factors such as temperature, interfacial disorder, roughness and dislocations at the interface, and weak interfacial bonding. Experimental and simulation approaches to further understand these effects at interfaces are presented in the following sections.

### C.1. Nanoscale Interfaces (Giri, Hopkins)

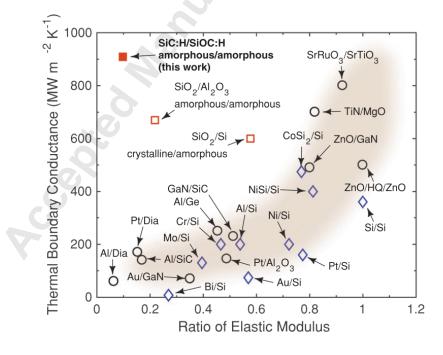

The understanding of the various factors dictating  $h_{BD}$  has been greatly facilitated by recent advancements in experimental metrologies used to measure  $h_{BD}$  across buried interfaces or interfaces comprised of 2D material systems and computational advances in atomistic simulations that can mimic realistic interfaces. For example, it has been shown that interfaces formed with an amorphous solid can have very high interfacial conductances (Fig. 16), which is counterintuitive to the conventional wisdom that disorder usually enhances thermal resistance [222, 223]. Likewise, electron-dominated thermal transport across interfaces (usually between two metals in contact, with interfacial thermal conductance typically on the order of 1 GW/m<sup>2</sup>K) have been shown to possess more than an order of magnitude higher conductances than typical phonon-dominated heat flow (on the order of 100 MW/m<sup>2</sup>K) across interfaces [224-226]. Moreover, epitaxial interfaces formed between materials with similar lattice constants and high quality of interfaces have also been shown to demonstrate high conductances ( $h_{BD} > 500 \text{ MW/m}^2$ ·K) [227-229].On the contrary, extremely low conductances have been measured for materials with highly dissimilar vibrational density of states and large mismatch in their elastic constants such as bismuth deposited on diamond substrates with reported  $h_{BD}$  of 8 MW/m<sup>2</sup>·K. To put things into perspective and highlight the disparity in the measured  $h_{BD}$ , the resistance of bismuth/diamond interface is greater than that of a 100 nm thick amorphous SiO<sub>2</sub> layer, whereas the resistance measured for a TiN/MgO epitaxial interface is comparable to that of a 1 nm thick amorphous SiO<sub>2</sub> layer.

**Figure 16** - Compilation of experimental data showing conventional trend in thermal boundary conductance vs ratio of elastic modulus, showing it is possible to achieve higher thermal boundary conductance by matching to amorphous layers. Reproduced from [223] with permission.

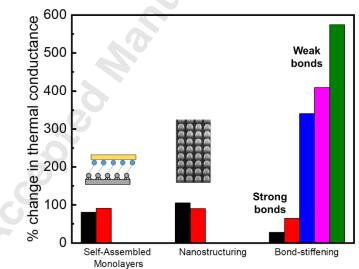

Extrinsic factors such as pressure and nanostructuring through interfacial mixing, roughing with non-planar structures, and chemical functionalization has been shown to control and enhance  $h_{BD}$  in a wide range across various types of interfaces [230-241]. For example, Losego et al. [240] experimentally demonstrated that interfaces formed with weak van der Waals interactions can be converted to covalent bonding via self-assembled monolayers (SAMs) between Au and quartz, leading to an increase in  $h_{BD}$  by as much as 80%. Similarly, increase in the overall contact area by patterning nonplanar features of nanofabricated fin-like projections at metal/dielectric interfaces can substantially increase the measured  $h_{BD}$  [230, 231]. Stiffening the bonds at the interface via mechanical strain (performed with diamond load cells) has also been experimentally shown to be an effective way to enhance  $h_{BD}$  [119, 242]. These strategies for enhancement in thermal conductance are summarized in Fig. 17.

**Figure 17** - % change in thermal conductance between the high conductance case and the low one, demonstrating that several strategies have significant impact on  $h_{BD}$ . Data on tailoring  $h_{BD}$  via self-assembled monolayers comes from [240, 241]; nanostructuring data is from [230, 231]; bond-stiffening data is from [119, 242].

Along with the experimental advances, atomistic simulations based on molecular dynamics (MD) simulations have led to tremendous progress in understanding the mode- and spectral-level contributions to interfacial thermal conductance between materials[23, 118, 243-249]. Some of these works have highlighted the importance of considering localized and nondispersive interfacial modes to accurately describe h<sub>BD</sub>, which are ignored while treating h<sub>BD</sub> with the typical formalisms based on the phonon gas models such as the DMM and AMM as discussed above. Furthermore, the assumption of elastic scattering in the aforementioned models that hinder their applicability to realistic material interfaces at room temperature and elevated temperatures is avoided in MD simulations that inherently account for elastic as well as inelastic pathways of heat transfer due to multiple phonon interactions that can play a significant role in dictating interfacial heat transfer across solids.

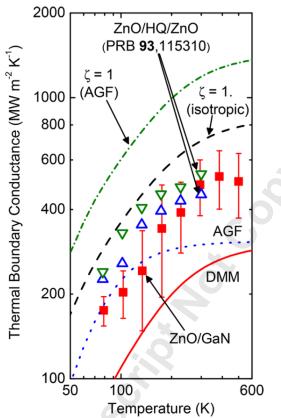

The failure of the phonon gas models has also been exemplified by comparing their predictions with experimental measurements of  $h_{BD}$  on high crystalline quality nonmetallic solids as carried out in [229] for epitaxially grown ZnO/GaN interface (Fig. 18). This work directly highlights the inapplicability of the Landauer/transmission formalism-based theories by showing that the measured value of  $h_{BD}$ =490 MW/m<sup>2</sup>·K for ZnO/GaN is nearly a factor of 2 greater than the values predicted by these theories at elevated temperatures of ~200 K and above. The disagreement points to the fact that the harmonic approximation adopted in the models could be incorrect and anharmonic channels of energy transfer could contribute to the enhancement of  $h_{BD}$  as the temperature is increased. Anharmonic channels with multiple phonon scattering events affecting the transmission of vibrational energy

across interfaces can lead to an increase in  $h_{BD}$  by opening additional channels for interfacial heat flow [245, 250-255].

**Figure 18** – Comparison of model predictions for  $h_{BD}$  to experimentally measured values. This demonstrates that atomistic simulations may prove more useful than standard phonon gas theory predictions. Reprinted from [229] with permission. © 2018 American Chemical Society.

### C.2. Effect of Constituent Diffusion (Tian)

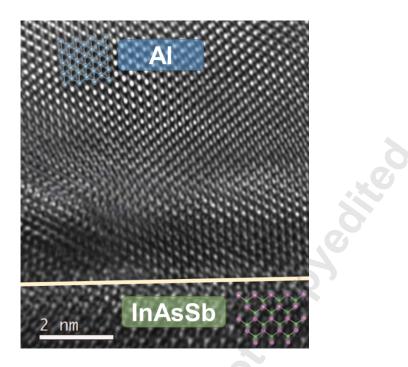

Interface roughness due to constituent diffusion commonly occurs at material interfaces [30]. Atomistic Green's function (AGF) is a powerful tool to study thermal transport across interfaces.

Figure 19 – Transmission electron micrograph of interfacial roughness between aluminum and indium arsenide antimonide. Reprinted from [256] with permission.

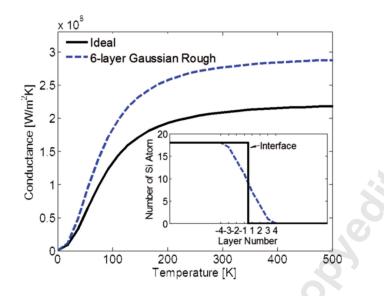

Unlike the widely-used acoustic mismatch model (AMM) and diffuse mismatch model (DMM), which only consider the material properties on both sides, AGF includes the details of the microscopic structures at the interface (as depicted in Fig. 19). Using AGF, Tian *et al.*[257] studied the effect of constituent diffusion on  $h_{BD}$  in the harmonic limit. To mimic the atomic diffusion, they created the atomic distribution at the interface to obey the half-Gaussian distribution. They found that the phonon transmission (and hence,  $h_{BD}$ ) is significantly enhanced by atomic diffusion compared to a smooth interface [257], which was contrary to the conventional notion at that time (Fig. 20).

Figure 20: Demonstration of enhanced  $h_{BD}$  due to atomic diffusion at a rough surface compared with a smooth one. Reprinted from [257] with permission.

They attributed this enhancement to the effect of bridging phonon density of states of bulk leads by the mixed region. In brief, atomistic diffusion can increase phonon transmission across two dissimilar materials if the diffusion length is properly controlled. It shares the same essence with later studies on enhanced thermal interface conductance by nanopillar arrays [258] and adding a layer of impedance matcher at interface [259].

| Enhancement Mechanism      | h <sub>BD,low</sub><br>(MW/m <sup>2</sup> ·K) | h <sub>BD,enhanced</sub><br>(MW/m <sup>2</sup> ·K) |

|----------------------------|-----------------------------------------------|----------------------------------------------------|

| Nanopillar arrays [258]    | 230 (@300K)                                   | 438 (@300K)                                        |

| Interlayer [259]           | 1012.9 (@30K)                                 | 1251.7 (@30K)                                      |

| Interface roughening [257] | 210 (@300K)                                   | 277 (@300K)                                        |

| <b>Table 2.</b> Strategies to enhance $h_{BD}$ | with references, | and degree of enhancement | (at given temperature). |

|------------------------------------------------|------------------|---------------------------|-------------------------|

|                                                |                  |                           |                         |

# C.3. Enhancement of Thermal Transport Across Power Electronics Interfaces (Shi and Graham)

To enhance the thermal transport at interfaces, we first need to understand the mechanisms leading to thermal resistance at the interface. However, there are plenty of factors which can affect the  $h_{BD}$  and  $R_{th}$  across interfaces [227], such as inelastic phonon scattering [246, 260], interface disorder [261], different bonding strength [240, 262], crystal orientation [121, 263, 264], and electron-phonon coupling [265, 266]. Experiments and simulations are usually applied to study the contributions to thermal transport at interfaces of different mechanisms. For experiments, the time domain thermoreflectance (TDTR) method is one of the widest used and reliable methods to measure  $h_{BD}$  [28, 56, 267]. For simulations, people usually use molecular dynamics (MD) or Landauer formula with transmission functions from acoustic mismatch model (AMM), diffuse mismatch model (DMM), atomistic Green's function (AGF), or phonon wave-packet method [71, 257, 268-274]. Within the framework of MD methods, non-equilibrium MD (NEMD) [275-277] and interface conductance modal analysis (ICMA) [115, 143, 278-284] are usually applied to predict  $h_{BD}$ . The advantages of MD are that the anharmonic phonon scattering is included from the higher-order force constants of empirical interatomic potentials, and the interface structures are quite flexible, that complex interfacial details (like strong interfacial disorder and interfaces with dimensional mismatch) can be simulated. However, MD is computationally expensive and does not consider quantum effects, which will lead to inaccuracy at low temperature or small dimension. Also, MD relies on interatomic potentials and cannot be applied to systems without appropriate potentials. The advantage of Landauer approach is the consideration of quantum phonon statistics which is important at sub-Debye temperatures. Moreover, for Landauer method with transmission functions from AMM, DMM or AGF, phonon properties can be obtained from first-principle calculations, which means that interatomic potentials are not necessary, and for Landauer with AMM or DMM, the computational costs are not high. However, it is very difficult to include anharmonicity in Landauer approach, and the consideration of detailed interface structure or interface bonding strength in AMM or DMM is very hard to implement. Recently, there are several studies of considering anharmonicity in AGF [271, 280], but there are still some limitations like high computational costs and inaccuracy from estimated scattering rate at interfaces.

At interfaces between two crystalline materials, because of the growth limitation, the crystalline quality of one or both of the materials near the interface is usually not very good or the interfacial bonding is not very strong from different growing methods, like evaporation [263], chemical vapor deposition (CVD) [115, 281], and atomic layer deposition (ALD) [282, 285]. The low quality polycrystalline or even amorphous region near the interface will have reduced thermal conductivity compared to bulk crystal and will contribute an additional thermal resistance, and that thermal resistance might impede the thermal transport from devices, especially for high frequency applications. In a recent study of Al/sapphire interface with TDTR and Landauer approach with transmission from AGF and DMM, it is found that an ultraclean and atomically smooth interface can be obtained by growth via molecular beam epitaxy (MBE) [283]. There are several reasons that the MBE Al/sapphire interface is ultraclean: the good quality of sapphire substrate, there is no reaction between sapphire and Al during growth, and the orientation of sapphire is carefully selected to insure small lattice mismatch and similar crystalline structure. It is observed

that the  $h_{BD}$  at the MBE-grown Al/sapphire interface is larger than all other  $h_{BD}$  measurements in literature [283]. It is also observed that at the ultraclean Al/sapphire interface, the elastic phonon scattering dominates the phonon transmission, while inelastic scattering and electron-phonon coupling are not important.

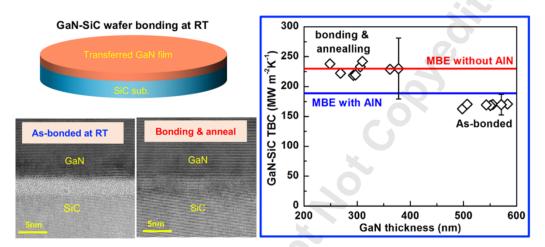

From previous studies, some strategies to enhance the thermal transport at interfaces have been developed, such as lighter atom substitution [286], patterned interface [115], and room-temperature surface-activated bonding (SAB) technique [143, 284]. From a study of h<sub>BD</sub> at SiC/GaN with NEMD method, it is found that substituting Ga atoms in the GaN lattice with lighter atoms near the interface can increase the  $h_{BD}$  by up to 50% [286]. From a study at Si/diamond interface with TDTR, NEMD, and Landauer formalism, it is observed that it is possible to increase the  $h_{BD}$  at semiconductor dielectric interfaces by graphoepitaxially growing diamond on nanopatterned silicon wafers. Because of the importance of thermal transport at both semiconductor-semiconductor and semiconductordielectric interfaces in power electronic devices, there are studies attempting to directly bond crystalline semiconductor and dielectric materials together. If two single-crystalline materials could be directly bonded together, the material quality near the interface should be better than directly growing one material on another, and a high thermal conductivity dielectric material or semiconducting material (e.g. diamond) can be used as heat spreading material to enhance heat dissipation in the device. Although very high values of hBD are realized via MBE deposition, the growth is very slow and the process is difficult to scale in an industrial setting [143, 284]. On the other hand, if two materials are bonded at high temperature, there will be residual stress at the interface because of different thermal expansion coefficients of two materials. The stress will affect interface quality and introduce additional thermal resistance [143, 284]. Therefore, a room-temperature SAB technique is developed to achieve the high-quality interface of MBE with the manufacturing ease of material bonding. From the TDTR measurements, the measured  $h_{BD}s$  at both GaN/SiC and GaN/diamond room-temperature SAB interfaces are among the high values reported in the literatures. Fig. 21 reports the results of this study.