# COMMUNICATION

View Article Online

View Journal | View Issue

**Cite this:** *Nanoscale*, 2020, **12**, 23488

Received 24th September 2020, Accepted 13th November 2020 DOI: 10.1039/d0pr06872a

rsc.li/nanoscale

Kai Xu, Da Wei Jiang, Xueshi Gao, Zijing Zhao, Tony Low and Wenjuan Zhu +

Indium Selenide (In<sub>2</sub>Se<sub>3</sub>) is a newly emerged van der Waals (vdW) ferroelectric material, which unlike traditional insulating ferroelectric materials, is a semiconductor with a bandgap of about 1.36 eV. Ferroelectric diodes and transistors based on In<sub>2</sub>Se<sub>3</sub> have been demonstrated. However, the interplay between light and electric polarization in In<sub>2</sub>Se<sub>3</sub> has not been explored. In this paper, we found that the polarization in In2Se3 can be programmed by optical stimuli, due to its semiconducting nature, where the photo generated carriers in In<sub>2</sub>Se<sub>3</sub> can alter the screening field and lead to polarization reversal. Utilizing these unique properties of In<sub>2</sub>Se<sub>3</sub>, we demonstrated a new type of multifunctional device based on 2D heterostructures, which can concurrently serve as a logic gate, photodetector, electronic memory and photonic memory. This dual electrical and optical operation of the memories can simplify the device architecture and offer additional functionalities, such as ultrafast optical erase of large memory arrays. In addition, we show that dual-gate structure can address the partial switching problem commonly observed in In<sub>2</sub>Se<sub>3</sub> ferroelectric transistors, as the two gates can enhance the vertical electric field and facilitate the polarization switching in the semiconducting In<sub>2</sub>Se<sub>3</sub>. These discovered effects are of general nature and should be observable in any ferroelectric semiconductor. These findings deepen the understanding of polarization switching and light-polarization interaction in semiconducting ferroelectric materials and open up their applications in multifunctional electronic and photonic devices.

van der Waals (vdW) ferroelectric materials emerged in recent years as a new class of ferroelectric materials.<sup>1–3</sup> Contrary to traditional ferroelectric materials such as perovskite compounds, vdW ferroelectric materials are free from dangling bonds and offer additional merits such as bandgap tunability, mechanical flexibility, and high carrier mobility.<sup>1,4,5</sup> More

importantly, they can be synthesized on common substrates and allow for easy integration with general semiconducting materials. Therefore, these new vdW ferroelectrics are not only scientifically intriguing but also promising for applications, including nanosensors, actuators, non-volatile memories, and multifunctional devices.

In<sub>2</sub>Se<sub>3</sub> is a recently discovered vdW ferroelectric material.6-11 Unlike SnTe which has narrow bandgap (0.18 eV in bulk)12 and CIPS which has wide bandgap (2.9 eV),13 In2Se3 has a semiconducting gap (1.36 eV α-phase).14 Ferroelectric diodes and memristive devices based on In<sub>2</sub>Se<sub>3</sub> and graphene were demonstrated. 9,15,16 Back-gate ferroelectric field-effect transistors (FETs) with In<sub>2</sub>Se<sub>3</sub> as the channel have been realized. 17 However, the In<sub>2</sub>Se<sub>3</sub> FETs with thick gate oxides show clockwise hysteresis loops (opposite direction to the ferroelectric hysteresis), due to partial polarization switching in In<sub>2</sub>Se<sub>3</sub>.<sup>17</sup> In this paper, we show that sandwiching In<sub>2</sub>Se<sub>3</sub> between two sets of gates can address this problem. By enhancing the vertical electric field across In2Se3, full control of polarization switching in In<sub>2</sub>Se<sub>3</sub> can be achieved. More importantly, the interplay between light and polarization in In<sub>2</sub>Se<sub>3</sub> has not been explored so far. In this work, we discovered that light can induce polarization reversal in In<sub>2</sub>Se<sub>3</sub>. The mechanism of the photo-induced polarization reversal is proposed. Furthermore, we demonstrated for the first time multifunctional devices based on In<sub>2</sub>Se<sub>3</sub> heterostructures, which can concurrently serve as a logic gate, photodetector, electronic memory and photonic memory.

# Electrical control of polarization switching

The electrical control of polarization switching in  $In_2Se_3$  was investigated using metal/ $In_2Se_3$ /metal and graphene/ $In_2Se_3$ / metal structures.  $\alpha$ - $In_2Se_3$  nanosheets are mechanically exfoliated on the highly doped silicon substrate. The crystal phase of the  $In_2Se_3$  flake was confirmed by Raman and photo-

<sup>&</sup>lt;sup>a</sup>Department of Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana, Illinois 61801, USA. E-mail: wjzhu@illinois.edu

<sup>&</sup>lt;sup>b</sup>Department of Electrical and Computer Engineering, University of Minnesota, Minneapolis, Minnesota 55455. USA

$<sup>\</sup>dagger$  Electronic supplementary information (ESI) available: The more details of characterizations and simulation of devices. See DOI: 10.1039/d0nr06872a

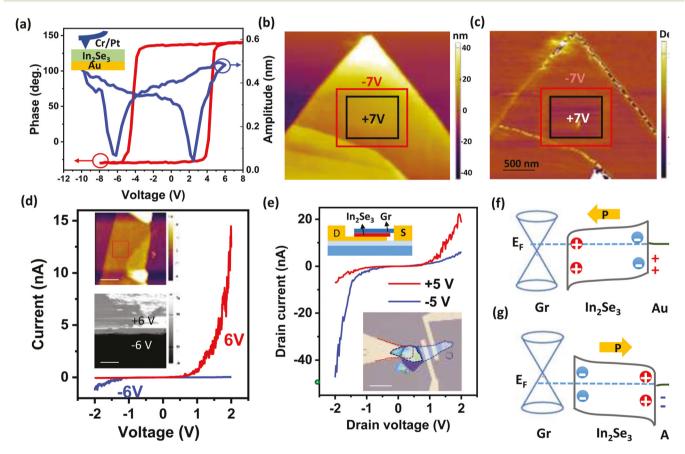

luminescence (PL) measurements, as shown in Fig. S1 in ESI.† The local piezoelectric loops of In<sub>2</sub>Se<sub>3</sub> were measured by switching spectroscopy piezoresponse force microscopy (SS-PFM), as shown in Fig. 1a. The phase shows sharp change up to 180° and the amplitude shows butterfly-like voltage dependence, which are typical characteristics for ferroelectric materials. The domain switching in In<sub>2</sub>Se<sub>3</sub> was further investigated by PFM mapping. A box-in-box pattern was written using conductive atomic force microscopy (CAFM) with opposite sample voltages (-7 and +7 V). Fig. 1b and c show the topography and PFM phase images of an In<sub>2</sub>Se<sub>3</sub> flake after the write operation. In the ±7 V region, the out-of-plane phases of the In<sub>2</sub>Se<sub>3</sub> are about ±90° respectively, corresponding to the polarization up and down states respectively. The resistive switching in metal/In<sub>2</sub>Se<sub>3</sub>/metal structures was investigated by CAFM. Fig. 1d shows the IV curves taken in the regions programmed with -6 V and +6 V, which exhibit rectifying behavior. When the sample bias is positive, the current after +6 V program-

ming is significantly higher than that after -6 V programming. The current mapping also manifests two distinct current states, as shown in the inset of Fig. 1d. More importantly, the on/off ratio for the ferroelectric diodes at 2 V is more than  $10^2$ . Furthermore, vertical ferroelectric Schottky diodes based on In<sub>2</sub>Se<sub>3</sub>/graphene vdW heterostructure were also fabricated as shown in Fig. 1e. After a 5 V write pulse, the DC IV of the vertical diode exhibits forward rectifying behavior, while after a -5 V write pulse, it shows reverse rectifying behavior. Both the write and read voltages were applied on the metal electrode (drain terminal). These results indicate that the polarization in In<sub>2</sub>Se<sub>3</sub> can affect the Schottky barrier height and switch the diode polarity. The energy band diagrams are shown in Fig. 1f and g to explain the reversible rectifying current behavior. When a 5 V write voltage is applied on the metal electrode, the ferroelectric polarization points from metal to graphene, which will raise the Fermi level and induce n-doping in graphene. Subsequent application of positive read bias at the

Fig. 1 Electrical control of polarization switching in  $In_2Se_3$ . (a) Local hysteresis loop of 27 nm  $In_2Se_3$  measured by SS-PFM. The 180° reversal for phase and "butterfly" curve for amplitude confirm the piezoelectricity of  $In_2Se_3$ . The sample structure is illustrated in the inset. (b) Topography and (c) PFM phase image of a 36 nm  $In_2Se_3$  flake in a PFM measurement. In (b), an illustration of the box-in-box pattern is overlaid on the topography image. In (c), the phase contrast indicates the polarization direction is switched by external electric field. (d) IV curves measured by CAFM at regions programmed with -6 V and 6 V respectively. The inset shows the topography of the  $In_2Se_3$  flake (top) and current mapping of the -6 V and +6 V programmed regions (bottom). The scale bars are 1  $\mu$ m and 200 nm respectively. (e) The IV characteristics of a vertical ferroelectric Schottky diode based on  $In_2Se_3$ /graphene heterostructure. The schematic and optical image of the device are shown in the insets. By switching the polarization with +5 V and -5 V applied on the gold terminal, the IV curves manifest forward and reverse rectifying behavior respectively. The scale bars are 20  $\mu$ m. (f) and (g) Energy diagrams of the graphene/ $In_2Se_3$  ferroelectric Schottky diodes after positive and negative program pulses applied on the gold terminal, respectively.

Communication Nanoscale

metal would then induce the required band bending in the In<sub>2</sub>Se<sub>3</sub>, allowing for electrons injection from graphene. When a negative pulse is applied, the polarization of In<sub>2</sub>Se<sub>3</sub> switches direction, thus barrier height on the graphene side increases while that on the metal side decreases. As a result, electrons are easier to inject from the metal side, changing the forward to reverse rectifying behavior. The calculated band structures of In<sub>2</sub>Se<sub>3</sub>-graphene heterostructures under two different polarization directions are shown in Fig. S2 in ESI.†

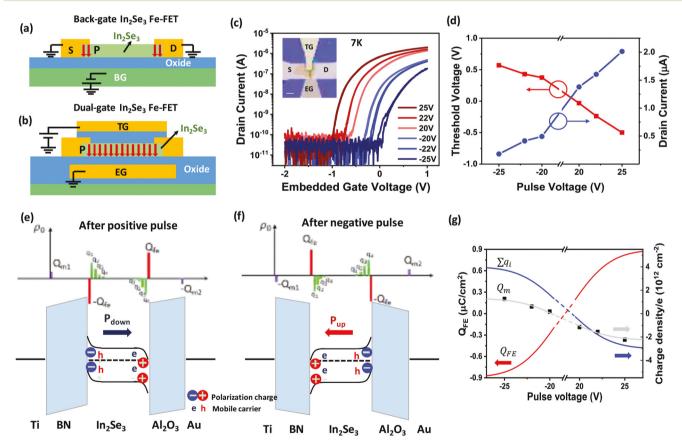

Utilizing the electrical controlled polarization and the semiconducting nature of In<sub>2</sub>Se<sub>3</sub>, we can fabricate ferroelectric In<sub>2</sub>Se<sub>3</sub> transistors. Different from traditional ferroelectric transistors where the ferroelectric layer serves as the insulator, here the ferroelectric semiconducting In<sub>2</sub>Se<sub>3</sub> serve as the channel. The polarization in In<sub>2</sub>Se<sub>3</sub> can induce mobile screening carriers, which can participate the current transport in the transistor. By modulating the direction and amplitude of the polarization in In<sub>2</sub>Se<sub>3</sub>, we can control the carrier type/concentration and thus the drain current of the transistor. Recently, back-gated ferroelectric In<sub>2</sub>Se<sub>3</sub> transistors were demonstrated, 17 however, trap-like hysteresis window was observed due to partial polarization switching in In2Se3 transistors, especially in the transistors with thick oxide. In the back-gate structure, only part of the In2Se3 channel is sandwiched between the source (or drain) electrode and back-gate, so there is not enough vertical electric field to completely switch the polarization in the In<sub>2</sub>Se<sub>3</sub> channel, illustrated in Fig. 2a. To address this problem, we propose to use dual-gate structure, illustrated in Fig. 2b. The top and embedded gates will induce a vertical electrical field across the entire In<sub>2</sub>Se<sub>3</sub> channel to ensure the sufficient polarization switching. Using this structure, we were able to observe large ferroelectric windows in the In<sub>2</sub>Se<sub>3</sub> transistors. Fig. 2c shows the transfer characteristics of a double-gated In<sub>2</sub>Se<sub>3</sub> transistor measured at 7 K after applying

Fig. 2 Electrical memories based on ferroelectric In<sub>2</sub>Se<sub>3</sub>. (a) Illustration of a back-gate In<sub>2</sub>Se<sub>3</sub> transistor. Applying a voltage between the back gate and the source/drain terminals leads to a partial switching of polarization in In<sub>2</sub>Se<sub>3</sub>. (b) Illustration of a dual-gate In<sub>2</sub>Se<sub>3</sub> transistor, where the ferroelectric In<sub>2</sub>Se<sub>3</sub> channel is sandwiched between the top and bottom gates with insulators in between. Applying a voltage between the top and bottom gates leads to a vertical electric field across the In<sub>2</sub>Se<sub>3</sub> channel, which can effectively switch the polarization in In<sub>2</sub>Se<sub>3</sub>. (c) Transfer characteristics after various program pulses at 7 K shows large memory window ( $\sim$ 1 V) and high current ratio ( $\sim$ 10<sup>4</sup>) between two memory states ( $\pm$ 25 V). The inset shows the optical image of the device and the scale bar is 10 µm. (d) The threshold voltage and drain current at back-gate voltage of 1 V are extracted and plotted as a function of program pulse voltages. The monotonic decrease of the threshold voltage and increase of the drain current as the pulse voltage increases indicate excellent ferroelectric tunability of the electrical properties of In<sub>2</sub>Se<sub>3</sub> FETs. (e) and (f) The schematic band diagrams of the dual metal gate device with the polarization direction pointing to the right and left respectively. (g) Simulated polarization charge density ( $Q_{FE}$ , red) and free carrier density in  $In_2Se_3$  ( $q_i$ , blue) as a function of program pulse voltage based on the estimated charge density near the metallic surface ( $Q_{\rm m}$ , gray line and black dots).

program pulses with various amplitudes. The program pulses were applied on the top gate with the back gate grounded. When the program pulse amplitude exceeds 20 V, the transfer curves shift toward opposite directions after positive and negative program pulses, which can be attributed to the ferroelectric polarization switching in In<sub>2</sub>Se<sub>3</sub>. The details of the measurement are shown in Fig. S3.† Large memory window ( $\sim$ 1 V) and high current ratio ( $\sim$ 10<sup>4</sup>) between the two ferroelectric polarization support their robust function as memory states. The threshold voltages  $(V_{th})$  and drain currents  $(I_d)$  at back-gate voltage of 1 V were extracted and plotted as a function of program pulse amplitude (Fig. 2d). The threshold voltage decreases and the drain current increases with increasing program voltage, indicating excellent non-volatile tunability of the electrical characteristics of In<sub>2</sub>Se<sub>3</sub> transistors, through ferroelectric domains switching. The transfer curves

measured at various temperatures all exhibit large and stable

ferroelectric memory window (Fig. S5†).

The ferroelectric windows in the In<sub>2</sub>Se<sub>3</sub> transistors were also analyzed using electrostatic model. The semiconducting nature of In<sub>2</sub>Se<sub>3</sub> implies the presence of conducting free carriers, which can be induced by the polarization charges, and is responsible for the observed device current. Fig. 2e and f show the energy diagrams of the device, depicting the charge densities at the metallic gates  $(Q_m)$ , the polarization charges in the ferroelectric  $In_2Se_3$  ( $Q_{FE}$ ), as well as the free carriers within the semiconducting ferroelectric vdW layers denoted as  $(q_i)$ . The latter requires proper electrostatic analysis, which differs from the analysis of traditional three-dimensional (3D) ferroelectric materials. Due to relatively weak vdW stacking, the bandgap of individual layers remains relatively unchanged in multilayers (Fig. S6†). Therefore, the induced charges within the ferroelectric semiconductor can be treated as discretely distributed charge layers  $q_i$  near the  $In_2Se_3$  interfaces. Due to electrostatic screening, these  $q_i$  decrease away from the interface, where the out-of-plane electric field is the largest, as depicted in the Fig. 2e and f. The charge distribution within the ferroelectric In<sub>2</sub>Se<sub>3</sub> can be obtained for a given potential profile by minimizing the total energy  $U = U_{el} + U_{b}$ , in which  $U_{el}$  and  $U_{b}$  represent the electrostatic interaction between layers and the band-filling energy, respectively. However, the solution for the discretely distributed charges  $q_i$  should be solved self-consistently with Poisson's equation,  $\nabla^2 \phi = -\rho/\varepsilon$ , with the boundary condition enforced by the work function difference between metal and ferroelectric materials. From this, we can get the complete charge distribution profile, electric field and potential profile of the dual gate device. For simplicity, we consider the case where the In<sub>2</sub>Se<sub>3</sub> has no residual doping and the two metal contacts are the same.

Fig. 2g shows the modeled charge components as a function of the program pulse voltages. The initial charge density on the metal without polarization  $Q_{\rm m0}$  was solved using electrostatic model, while the change of the charge density on the metal due to polarization  $\Delta Q_{\rm m}$  was estimated from the threshold voltage shift after program pulses, which was measured experimentally, as depicted in Fig. 2c and d. With

the total charge density on the metal ( $Q_{\rm m} = Q_{\rm m0} + \Delta Q_{\rm m}$ ), we solved for the polarization charge density  $Q_{\rm FE}$  and free carrier density  $q_{\rm i}$  self-consistently using the electrostatic model described above (details of the modeling are in ESI†). The screening charges obtained are on the order of  $10^{12}$  cm<sup>-2</sup> when the magnitude of the pulse voltage is larger than 20 V, which constitutes the ON-state of the In<sub>2</sub>Se<sub>3</sub> semiconductor channel.

In making the comparison with experiments, we reiterate the observation that the ferroelectric polarization for the +25 V pulse renders a negative shift in threshold voltage, which means more electron-doped, as compared to the -25 V case. These observations are consistent with the scenario that only the bottom channel is conducting. The asymmetry in the conduction can be explained by the different top/bottom gate and source/drain metals. The choice of Au for bottom gate, in conjunction to Ti as the source/drain contacts render it an Ohmic contact to electrons in  $In_2Se_3$ . The fact that the transistor transfer curves reveal only electron carrier conduction is due to the low work function Ti contact at source/drain, which provides low injection barrier for electrons. In addition, the drain voltage applied is 0.1 V, which is far below the coercive voltage for the in-plane ferroelectric polarization.  $^{16}$

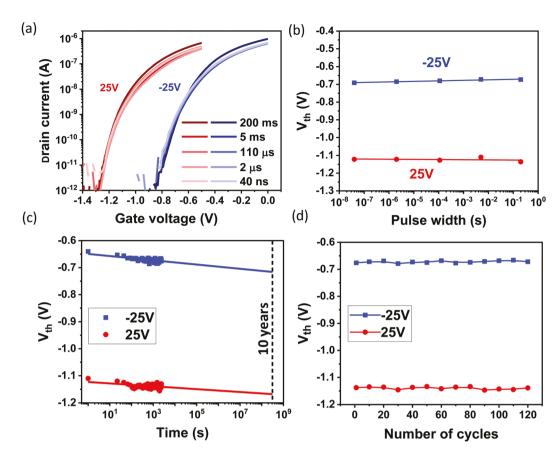

Furthermore, we studied the pulse width and amplitude dependence of the memory window. Fig. 3a shows the transfer curves of a dual-gate In<sub>2</sub>Se<sub>3</sub> transistor after +25 V and -25 V program pulses. When the pulse width scales down from 200 ms to 40 ns, the memory window is nearly unchanged. These results ruled out the possibility of hysteresis effects arising from slow moving mobile ions. In addition, the memory window shows a step function of the program pulse amplitude and has a sharp transition at ~20 V (Fig. S3c†), which corresponds to the coercive field of 0.12 V nm<sup>-1</sup> in the ferroelectric In<sub>2</sub>Se<sub>3</sub>. This result indicates that the memory window is due to ferroelectric polarization instead of interface traps. We also systematically characterized the retention and endurance of the In2Se3 memory devices. The threshold voltages were plotted as a function of retention time, shown in Fig. 3c. At room temperature, over 90% of the memory window remains after extrapolation to 10 years. The endurance of the In<sub>2</sub>Se<sub>3</sub> memory is shown in Fig. 3d. The memory window was nearly unchanged after 120 cycles. These results indicate that the ferroelectric devices based on In<sub>2</sub>Se<sub>3</sub> have excellent reliability.

# Optical control of polarization switching and multifunctional devices based on In<sub>2</sub>Se<sub>3</sub>

Most traditional ferroelectric materials are insulators with wide bandgaps, such as Pb (Zr,Ti)O<sub>3</sub>, (PZT) with bandgap of 3.3-3.55 eV and BiFeO<sub>3</sub> with a bandgap of 2.7 eV. The absorption spectrum of these wide bandgap materials does not fully address the visible light range. In contrast, In<sub>2</sub>Se<sub>3</sub> has a much

Communication Nanoscale

Fig. 3 Memory window of a dual-gate  $ln_2Se_3$  transistor. (a) The transfer curves of the dual-gate  $ln_2Se_3$  transistor measured using various program pulse voltages and widths. (b) Threshold voltage of the dual-gate  $ln_2Se_3$  transistor as a function of program pulse width. When the pulse width scales down from 200 ms to 40 ns, the memory window is nearly unchanged, indicating that the memory window is due to ferroelectric polarization instead of mobile ions. (c) The retention and (d) endurance of the  $ln_2Se_3$  transistor. The extrapolated retention time is over 10 years. The measurement temperature is 50 K for (a)-(d).

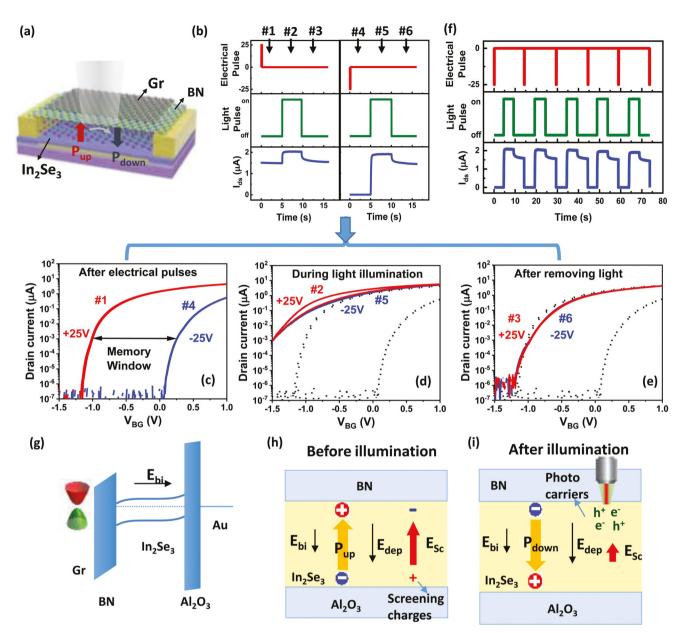

smaller bandgap (1.36 eV in bulk), which is photoactive to the entire visible spectrum. 24,25 Combining the photoactive, ferroelectric and semiconducting properties of In<sub>2</sub>Se<sub>3</sub>, we can create multifunctional devices, which can detect light, and process these optical signals simultaneously. Here, dual-gate In<sub>2</sub>Se<sub>3</sub> devices were fabricated with multi-layer graphene as the transparent top electrode to facilitate the light absorption. The device structure is shown in Fig. 4a. Electrical and optical pulses were applied on the device sequentially and the drain current was measured as a function of time, as shown in Fig. 4b. In addition, the transfer characteristics were tested after electrical pulse, during light illumination and after light removal (corresponding to the time points #1 to #6 marked in Fig. 4b). As shown in Fig. 4c, the polarization of the In<sub>2</sub>Se<sub>3</sub> was programmed by the electrical pulses and a large memory window was observed after ±25 V pulses, which is consistent with the dual-gate In<sub>2</sub>Se<sub>3</sub> devices with metal top electrodes discussed in the previous section. The threshold voltage after +25 V pulse is around −1 V, corresponding to the downward polarization  $(P_{\text{down}})$  in  $\text{In}_2\text{Se}_3$ , while the threshold voltage after -25V pulse is around 0.2 V, corresponding to the upward polarization  $(P_{up})$  in  $In_2Se_3$ . As a result, the drain current at zero gate

voltage is high after a +25 V pulse and low after a -25 V pulse, as shown in Fig. 4b. Moreover, this device is very sensitive to light, exhibiting an excellent photoresponse, as shown in Fig. 4d. The drain current increased dramatically when the device was illuminated with mild lamp light (4400  $\mu$ W cm<sup>-2</sup>). More interestingly, after the light was removed, all the transfer curves exhibit a threshold voltage around -1 V, regardless of whether the device was programed with a +25 V or -25 V pulse previously, as shown in Fig. 4e. This means that light can erase the polarization of In<sub>2</sub>Se<sub>3</sub> to P<sub>down</sub> state and reset the threshold voltage of the dual-gate In<sub>2</sub>Se<sub>3</sub> device. The time evolution of the drain current in Fig. 4b confirms that the device was set to an "on" state (high drain current) by the light illumination and remains at the "on" state even after the light removal. This photo-induced polarization reversal was also observed in MoS<sub>2</sub>/PZT stacks previously. 18,19 Fig. S7† shows the photo-induced polarization switching in other In<sub>2</sub>Se<sub>3</sub> transistors. These results indicate that this effect is repeatable and reliable. The cyclic operation with electrical pulses and light illumination were conducted as shown in Fig. 4f. It clearly displays the excellent periodic modulation of the drain current induced by the electrical and light stimuli. Time evolution of

Fig. 4 Optical control of polarization switching in  $In_2Se_3$ . (a) Illustration of the dual-gate  $In_2Se_3$  device with graphene top electrode. (b) Programming and erasing the  $In_2Se_3$  memory using electrical pulses ( $\pm 25$  V) and light illumination. The width of the electrical pulse is 200 ms. The light intensity is 4400 µW cm<sup>-2</sup>. (c) Transfer characteristics of the device after  $\pm 25$  V program pulses, showing clear memory window. (d) The transfer characteristics of the device during the light illumination. (e) Transfer curves of the device after removing the light. In (d) and (e), the red and blue lines correspond to the device previously programmed with +25 V and -25 V pulses respectively. For comparison, the transfer curves before the light illuminations are also included as the dashed black lines in (d) and (e). (f) The cyclic operations of the memory device with electrical pulses and light illumination show reproducible modulation of the drain current. (g) Energy diagram of the dual-gate  $In_2Se_3$  device at equilibrium. The built-in electric field,  $E_{bir}$  is pointing to the bottom electrode. (h) and (i) Illustrations of the polarization and electric field in  $In_2Se_3$  after -25 V pulse before and after light illumination respectively. (h) Before light illumination,  $P_{up}$  develops after -25 V pulse is applied on the top gate. The depolarization field due to the polarization charge,  $E_{dep}$ , is balanced by the electric field due to the screening charges,  $E_{sc}$ , thus the polarization is stabilized. (i) After light illumination, photo-generated electrons and holes neutralize the screening charges at the surfaces and weaken the screening field  $E_{sc}$ . The built-in electric field,  $E_{bir}$  and the depolarization field induced by the polarization charge,  $E_{dep}$ , reverse the polarization from  $E_{up}$  to  $E_{down}$  in  $E_{up}$  to  $E_{u$

the drain current with various light intensities was also tested as shown in Fig. S8.† It took longer time for the light with low intensity to neutralize the screening charges and reset the polarization as compared to the light with high intensity.

In the following, we propose a physical mechanism for this photo-induced polarization reversal and threshold voltage reset in  $\rm In_2Se_3$  devices. In this dual-gate device, due to the work function difference between the top graphene electrode

Communication Nanoscale

and the bottom gold electrode, a built-in electric field pointing toward the bottom electrode exists under equilibrium, as illustrated in Fig. 4g. This built-in electric field will induce an imprint in  $In_2Se_3$  with  $P_{down}$  being the preferred polarization state. This polarization state can be reversed, however, under a high electric field. When a -25 V pulse is applied on the top gate, the polarization of the In<sub>2</sub>Se<sub>3</sub> is switched to the upward direction  $(P_{up})$  and the threshold voltage shifts to around 0.2 V, as shown in Fig. 4b. Since  $In_2Se_3$  is a semiconductor, a  $P_{up}$ polarization will attract negative (positive) screening charges at the top (bottom) surface. These screening charges result in an electric field  $E_{sc}$  pointing upward, which will help to stabilize the polarization, as shown in Fig. 4h. When light is illuminated on the sample, the photo-generated carriers will neutralize the negative and positive screening charges at the surfaces and significantly reduce the electric field  $E_{\rm sc}$ . Then the depolarization field from the polarization charges and the built-in electric field will reverse the polarization from  $P_{\rm up}$  to  $P_{\text{down}}$ , as illustrated in Fig. 4i. As a result, the transfer curve with the -25 V program pulse after light illumination shifts back to around -0.7 V, corresponding to a  $P_{\text{down}}$  polarization, as shown in Fig. 4d. The fact that the threshold voltages are all around -1 V after removing light regardless the program voltages further confirms that  $P_{\text{down}}$  polarization is the preferred polarization state.

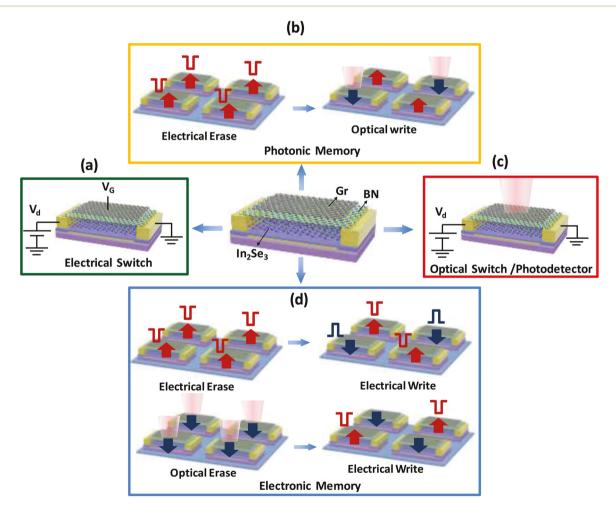

Combining the electrical and optical control of the polarization, we demonstrate multifunctional devices based on vdW ferroelectric In<sub>2</sub>Se<sub>3</sub>, which can serve as a logic switch, photodetector, electronic memory, and photonic memory concurrently, as illustrated in Fig. 5. The ferroelectric semiconducting channel based on In<sub>2</sub>Se<sub>3</sub> enables the device to response actively to both electrical and optical stimuli. The dual-gate structure ensures efficient electrical control of the polarization in the ferroelectric channel. Transparent graphene electrode

Fig. 5 Illustration of the multifunctionality of the dual-gate In<sub>2</sub>Se<sub>3</sub> transistor with transparent electrode. (a) Electrical logic switch, where the drain current is controlled by the gate voltage. (b) Optical memory, which can be erased electrically and programmed optically. The polarization direction of  $ln_2Se_3$  is indicated by the arrow (blue downward arrow:  $P_{down}$ ; red upward arrow:  $P_{up}$ ). (c) Optical switch, where the drain current is modulated by the optical illumination. (d) Electrical memory, where the write operation is carried out by applying electrical pulses. The memory array can be erased either electrically or optically. In electrical erase operation, the devices are addressed individually and the polarization of In<sub>2</sub>Se<sub>3</sub> can be reset by applying pulses on the top and bottom gates. In the optical erase operation, the polarization of In<sub>2</sub>Se<sub>3</sub> in the entire memory block can be reset to  $P_{\text{down}}$  state simultaneously by light illumination.

Nanoscale Communication

facilitates light absorption of the ferroelectric channel, which can induce not only photocurrent but also polarization reversal in the In<sub>2</sub>Se<sub>3</sub>. For photonic memory, the memory array can be reset electrically to  $P_{\rm up}$  state (ON state), then the data can be written optically by illuminating individual devices using a focused light source such as a laser to switch the polarization of the In<sub>2</sub>Se<sub>3</sub> to P<sub>down</sub> state (OFF state) (Fig. 5b). For electronic memory, the polarization of In<sub>2</sub>Se<sub>3</sub> is programmed using electrical pulses. The erase operations can be carried out either electrically or optically (Fig. 5d). In the electrical erase operation, the polarization of In<sub>2</sub>Se<sub>3</sub> is reset by applying pulses between the top and bottom gates. In the optical erase operation, the polarization of In<sub>2</sub>Se<sub>3</sub> in the entire memory block can be reset to  $P_{\text{down}}$  state (OFF state) simultaneously by light illumination. As compared to electrical erase, which is carried out sequentially on individual device(s), optical erase is a parallel process and is much faster. In addition, these devices can also serve as electrical switches where the drain current is controlled by the gate voltage, and as optical switches/photodetectors where the drain current is modulated by the light illuminating the device. This dual electrical and optical operation of the memories can simplify the device architecture and offer additional functionalities, such as an ultrafast optical erase of large memory arrays. Traditionally, ferroelectric devices are used in memory blocks while non-ferroelectric transistors are used for logic blocks in central processing units (CPUs). The memory and logic blocks are physically separated. Here, due to the ferroelectric and semiconducting nature of In<sub>2</sub>Se<sub>3</sub>, an In<sub>2</sub>Se<sub>3</sub>-based transistor enables the realization of memory and logic functions in one device. These logic-inmemory devices can potentially reduce the data transportation between memory and logic blocks and thus reduce the energy consumption and process latency. Moreover, traditional ferroelectric materials are insulators with large bandgaps (2-4 eV), while In<sub>2</sub>Se<sub>3</sub> has a small bandgap of 1.36 eV, which is photoactive to the entire visible spectrum. This implies that In<sub>2</sub>Se<sub>3</sub> devices can sense the light signal, process the signal in situ, and store the information locally, which enables in-sensor computing. These devices will have broad applications in sensor networks and un-manned vehicles.

In summary, we found that the polarization states of the In<sub>2</sub>Se<sub>3</sub> can be programmed by both electronic pulse and optical illumination. Through DFT calculations and electrostatic analysis, we revealed the underlying physical mechanisms that explain the experimental observation and could be generalized to other 2D ferroelectric semiconductors. Furthermore, we demonstrated multifunctional device based on In<sub>2</sub>Se<sub>3</sub>, which can serve as logic gate, electronic memory, photodetector, and photonic memory simultaneously for the first time, large memory window (~2.3 V) and a high current ratio ( $\sim 10^4$ ) between two memory states ( $\pm 25$  V) were realized. These electronic and photonic memories are non-volatile and energy efficient. A single device, which can detect light, store information and process electrical signals, will not only increase the packing density of the circuit, but also enable insensor and in-memory computing architecture, which can significantly reduce the latency and energy consumption related to the data movement. These results indicate that 2D ferroelectric In<sub>2</sub>Se<sub>3</sub> and its heterostructures are an excellent platform for future multifunctional electronics and optoelectronics.

## Methods

#### Material characterization

In<sub>2</sub>Se<sub>3</sub> ultrathin flakes were mechanically exfoliated from bulk In<sub>2</sub>Se<sub>3</sub> (HQ graphene) using the typical Scotch tape method, and then transferred by gel film. The crystal structure and optical bandgap of In2Se3 were examined using a confocal Raman microscope (Renishaw, 532 nm excitation laser). The thickness, surface morphology, local ferroelectric properties and current mapping were obtained using an Asylum Research Cypher scanning probe microscope and MFP-3D systems.

#### Device fabrication and measurements

Electrical devices were fabricated by standard lithography and metal deposition. Electrical measurements were conducted in Lakeshore probe station (CPX-VF) connected to Keysight B1500 parameter analyzer. The photoelectric measurements were performed in our home-made optical systems.

#### DFT calculation

The total-energy electronic-structure calculations were carried out using first-principles methods based DFT. The generalized gradient approximation exchange-correlation potentials plus the projector augmented wave method for the electron-ion interaction was used,20 as implemented in Vienna ab initio simulation package (VASP) code.21 The In2Se3 thin film slabs were cleaved from the bulk α-In<sub>2</sub>Se<sub>3</sub> structure with a lattice constant of 4.106 Å. The heterostructures of In<sub>2</sub>Se<sub>3</sub>/graphene were constructed using a  $3 \times 3/5 \times 5$  supercell to have a relatively small lattice mismatch. To avoid interaction between slabs, a vacuum region of more than 15 Å was introduced for the slab systems. DFT-D3 method is applied to properly treat the van der Waals interaction between layers.22 An electric field is applied along the z direction with the dipole corrections performed to avoid interactions between the periodically repeated images due to the intrinsic ferroelectricity of the In<sub>2</sub>Se<sub>3</sub>.<sup>23</sup> All self-consistent calculations were performed with a plane-wave cutoff of 500 eV. The geometric optimizations were carried out without any constraint until the force on each atom is less than 0.01 eV Å and the change of total energy per cell is smaller than  $10^{-5}$  eV. The Brillouin zone k-point sampling was set with a 12 × 12 × 1 Γ-centered Monkhorst-Pack grids. Bader charge analysis was performed to study the charge transfer within and between In2Se3 layers.

### Conflicts of interest

There are no conflicts to declare.

Communication Nanoscale

# Acknowledgements

The authors would like to acknowledge support from the National Science Foundation (NSF) under Grants ECCS 16-53241 CAR and from the Office of Naval Research (ONR) under grant NAVY N00014-17-1-2973.

# References

- 1 C. J. Cui, F. Xue, W. J. Hu and L. J. Li, Two-dimensional materials with piezoelectric and ferroelectric functionalities (vol 2, 18, 2018), *npj 2D Mater. Appl.*, 2018, 2, 18.

- 2 M. H. Wu and P. Jena, The rise of two-dimensional van der Waals ferroelectrics, *Wiley Interdiscip. Rev.: Comput. Mol. Sci.*, 2018, **8**(5), e1365.

- 3 L. Chang, L. You and J. L. Wang, The path to flexible ferroelectrics: Approaches and progress, *Jpn. J. Appl. Phys.*, 2018, 57(9), 0902A3.

- 4 K. Chang, J. W. Liu, H. C. Lin, N. Wang, K. Zhao, A. M. Zhang, F. Jin, Y. Zhong, X. P. Hu, W. H. Duan, Q. M. Zhang, L. Fu, Q. K. Xue, X. Chen and S. H. Ji, Discovery of robust in-plane ferroelectricity in atomic-thick SnTe, *Science*, 2016, 353(6296), 274–278.

- 5 F. C. Liu, L. You, K. L. Seyler, X. B. Li, P. Yu, J. H. Lin, X. W. Wang, J. D. Zhou, H. Wang, H. Y. He, S. T. Pantelides, W. Zhou, P. Sharma, X. D. Xu, P. M. Ajayan, J. L. Wang and Z. Liu, Room-temperature ferroelectricity in CuInP2S6 ultrathin flakes, *Nat. Commun.*, 2016, 7, 12357.

- 6 C. J. Cui, W. J. Hu, X. G. Yan, C. Addiego, W. P. Gao, Y. Wang, Z. Wang, L. Z. Li, Y. C. Cheng, P. Li, X. X. Zhang, H. N. Alshareef, T. Wu, W. G. Zhu, X. Q. Pan and L. J. Li, Intercorrelated In-Plane and Out-of-Plane Ferroelectricity in Ultrathin Two-Dimensional Layered Semiconductor In2Se3, *Nano Lett.*, 2018, 18(2), 1253–1258.

- 7 Y. Zhou, D. Wu, Y. H. Zhu, Y. J. Cho, Q. He, X. Yang, K. Herrera, Z. D. Chu, Y. Han, M. C. Downer, H. L. Peng and K. J. Lai, Out-of-Plane Piezoelectricity and Ferroelectricity in Layered alpha-In2Se3 Nanoflakes, *Nano Lett.*, 2017, 17(9), 5508–5513.

- 8 C. X. Zheng, L. Yu, L. Zhu, J. L. Collins, D. Kim, Y. D. Lou, C. Xu, M. Li, Z. Wei, Y. P. Zhang, M. T. Edmonds, S. Q. Li, J. Seidel, Y. Zhu, J. Z. Liu, W. X. Tang and M. S. Fuhrer, Room temperature in-plane ferroelectricity in van der Waals In2Se3, *Sci. Adv.*, 2018, 4(7), eaar7720.

- 9 S. Y. Wan, Y. Li, W. Li, X. Y. Mao, W. G. Zhu and H. T. Zeng, Room-temperature ferroelectricity and a switchable diode effect in two-dimensional alpha-In2Se3 thin layers, *Nanoscale*, 2018, **10**(31), 14885–14892.

- 10 S. M. Poh, S. J. R. Tan, H. Wang, P. Song, I. H. Abidi, X. Zhao, J. D. Dan, J. S. Chen, Z. T. Luo, S. J. Pennycook, A. H. C. Neto and K. P. Loh, Molecular-Beam Epitaxy of Two-Dimensional In2Se3 and Its Giant Electroresistance Switching in Ferroresistive Memory Junction, *Nano Lett.*, 2018, 18(10), 6340–6346.

- 11 M. Si, A. K. Saha, S. Gao, G. Qiu, J. Qin, Y. Duan, J. Jian, C. Niu, H. Wang, W. Wu, S. K. Gupta and P. D. Ye, A ferroelectric semiconductor field-effect transistor, *Nat. Electron.*, 2019, 2(12), 580–586.

- 12 A. Belianinov, Q. He, A. Dziaugys, P. Maksymovych, E. Eliseev, A. Borisevich, A. Morozovska, J. Banys, Y. Vysochanskii and S. V. Kalinin, CuInP(2)S(6) Room Temperature Layered Ferroelectric, *Nano Lett.*, 2015, 15(6), 3808–3814.

- 13 I. P. Studenyak, V. V. Mitrovcij, G. S. Kovacs, M. I. Gurzan, O. A. Mykajlo, Y. M. Vysochanskii and V. B. Cajipe, Disordering effect on optical absorption processes in CuInP2S6 layered ferrielectrics, *Phys. Status Solidi B*, 2003, 236(3), 678–686.

- 14 R. Bacewicz, J. Filipowicz and A. Wolska, Optical properties of indium-rich phases in the Cu-In-Se system, *Ternary Multinary Compd.*, 1998, 152, 507–510.

- 15 S. Y. Wan, Y. Li, W. Li, X. Y. Mao, C. Wang, C. Chen, J. Y. Dong, A. M. Nie, J. Y. Xiang, Z. Y. Liu, W. G. Zhu and H. L. Zeng, Nonvolatile Ferroelectric Memory Effect in Ultrathin -In2Se3, Adv. Funct. Mater., 2019, 29(20), 1808606.

- 16 F. Xue, X. He, J. R. D. Retamal, A. L. Han, J. W. Zhang, Z. X. Liu, J. K. Huang, W. J. Hu, V. Tung, R. H. He, L. J. Li and X. X. Zhang, Gate-Tunable and Multidirection-Switchable Memristive Phenomena in a van der Waals Ferroelectric, *Adv. Mater.*, 2019, 31(29), 1901300.

- 17 M. W. Si, A. K. Saha, S. J. Gao, G. Qiu, J. K. Qin, Y. Q. Duan, J. Jian, C. Niu, H. Y. Wang, W. Z. Wu, S. K. Gupta and P. D. D. Ye, A ferroelectric semiconductor field-effect transistor, *Nat. Electron.*, 2019, 2(12), 580–586.

- 18 A. Lipatov, P. Sharma, A. Gruverman and A. Sinitskii, Optoelectrical Molybdenum Disulfide (MoS2)— Ferroelectric Memories, ACS Nano, 2015, 9(8), 8089–8098.

- 19 T. Li, A. Lipatov, H. Lu, H. Lee, J.-W. Lee, E. Torun, L. Wirtz, C.-B. Eom, J. Íñiguez, A. Sinitskii and A. Gruverman, Optical control of polarization in ferroelectric heterostructures, *Nat. Commun.*, 2018, 9(1), 3344.

- 20 G. Kresse and D. Joubert, From ultrasoft pseudopotentials to the projector augmented-wave method, *Phys. Rev. B: Condens. Matter Mater. Phys.*, 1999, **59**(3), 1758–1775.

- 21 G. Kresse and J. Hafner, Ab initio molecular dynamics for liquid metals, *Phys. Rev. B: Condens. Matter Mater. Phys.*, 1993, 47(1), 558–561.

- 22 S. Grimme, J. Antony, S. Ehrlich and H. Krieg, A consistent and accurate ab initio parametrization of density functional dispersion correction (DFT-D) for the 94 elements H-Pu, J. Chem. Phys., 2010, 132(15), 154104.

- 23 G. Makov and M. C. Payne, Periodic boundary conditions in ab initio calculations, *Phys. Rev. B: Condens. Matter Mater. Phys.*, 1995, 51(7), 4014–4022.

- 24 P. Hou, S. Xing, C. Chen, X. Zhong, J. Wang and X. Ouyang, Resistive switching behavior in  $\alpha$ -In2Se3 nanoflakes modulated by ferroelectric polarization and interface defects, *RSC Adv.*, 2019, **52**, 30565.

- 25 B. Tang, L. Hou, M. Sun, F. Lv, J. Liao, W. Ji and Q. Chen, UV-SWIR broad range photodetectors made from few-layer α-In2Se3 nanosheets, *Nanoscale*, 2019, 11, 12817–12828.