Research Article www.acsami.org

# Strong Temperature Effect on the Ferroelectric Properties of CulnP<sub>2</sub>S<sub>6</sub> and Its Heterostructures

Zijing Zhao, Kai Xu, Hojoon Ryu, and Wenjuan Zhu\*

Cite This: ACS Appl. Mater. Interfaces 2020, 12, 51820-51826

**ACCESS** I

III Metrics & More

Article Recommendations

Supporting Information

ABSTRACT: Van der Waals (vdW) ferroelectric insulator CuInP<sub>2</sub>S<sub>6</sub> (CIPS) has attracted intense research interest due to its unique ferroelectric and piezoelectric properties. In this paper, we systematically investigate the temperature and frequency dependence of the ferroelectric properties of CIPS. We find that there is a large imprint in the CIPS capacitor, which can be attributed to the fixed dipoles induced by defects. At high temperatures and low frequencies, the amplitude and direction of the imprint become tunable by the preset pulse, as the copper ions are more mobile and these dipoles become switchable. When the polarization in CIPS changes direction, the graphene/CIPS/graphene ferroelectric diode exhibits switchable resistance since the Fermi level in graphene is modulated by the polarization in CIPS. For CIPS/MoTe<sub>2</sub> dual-gate transistor, a temperaturedependent nonvolatile memory window is observed, which can be attributed to the

interplay between ferroelectric polarization and interface traps. This research provides experimental groundwork for vdW ferroelectric materials, expands the understanding of ferroelectricity in CIPS, and opens up exciting opportunities for novel electronic devices based on vdW ferroelectric materials.

KEYWORDS: CuInP<sub>2</sub>S<sub>6</sub>, van der Waals ferroelectrics, temperature effect, ferroelectric heterostructure, imprint

# **■** INTRODUCTION

Ferroelectric materials with switchable polarization have broad applications including nonvolatile memory, electromechanical systems, and sensors. 1-4 Most technologically important ferroelectrics are perovskite oxides such as PbZr, Ti1-rO3 (PZT), BaTiO<sub>3</sub> (BTO), which are typically grown on crystal substrate via epitaxy.<sup>5-7</sup> However, these perovskites suffer from the lattice match restriction, surface dangling bonds, and incompatibility with silicon.<sup>8,9</sup> Recently, it was discovered that several van der Waals (vdW) materials are ferroelectric as well, such as CuInP<sub>2</sub>S<sub>6</sub> (CIPS), 10,111 In<sub>2</sub>Se<sub>3</sub>, 12-14 SnS, 15 SnSe, 16 SnTe, 17 WTe<sub>2</sub>, MoTe<sub>2</sub>, 19 and hybrid perovskite BA<sub>2</sub>PbCl<sub>4</sub>. <sup>20</sup> Due to the weak van der Waals forces between layers, ultrathin ferroelectric flakes can be conveniently obtained. It is intriguing that these materials retain ferroelectricity even down to atomic scale. More importantly, these materials can be stacked on other vdW materials and form vertical heterostructures and superlattices with highquality interfaces, providing a versatile material platform for multifunctional and reconfigurable devices. 21-24

CuInP<sub>2</sub>S<sub>6</sub> (CIPS) has a wide band gap (2.9 eV) and a high Curie temperature (315 K), which are important traits as a gate dielectric to ensure low leakage current and roomtemperature operation of the electronic device. 10,25-27 In contrast to traditional ferroelectric materials, CIPS shows high ionic conductivity above 231 K due to the highly mobile Cu ions.<sup>28</sup> The defects in CIPS play an important role in its

ferroelectric properties. Sulfur vacancy can induce a defect state near the valence band and suppress the ferroelectricity. 25 The interstitial Cu ions in vdW gaps lead to pinned dipoles and the negative piezoelectric effect. <sup>30,31</sup> The movement of the Cu ion is slower than that of electrons and has a strong temperature dependence.<sup>32</sup> These unique properties of CIPS together with its layered structure make it an intriguing candidate for novel ferroelectric heterostructures.

In this work, we investigate the temperature-dependent ferroelectric response of CIPS, and its implications for capacitors, ferroelectric diodes, and transistors. The ferroelectric switching of CIPS is affected by the strong polarization field of the defect dipoles, leading to an imprint in the hysteresis loop and small remanent polarization at low temperatures. Moreover, variable write measurement reveals the characteristic time constant for the ion-assisted switching. The temperature dependence of polarization is also confirmed in the ferroelectric heterostructures, including graphene/ CIPS/graphene diodes and CIPS/MoTe<sub>2</sub> transistors. Ferroelectric resistive switching and ferroelectric memory window

Received: August 4, 2020 October 22, 2020 Accepted: Published: November 5, 2020

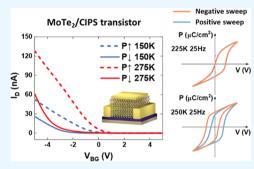

Figure 1. Temperature and frequency dependence of polarization in CIPS. (a) Optical image of a CIPS capacitor. The capacitance area is  $627 \, \mu \text{m}^2$ . The CIPS thickness is 395 nm. (b, c) Pulse waveforms (voltage as a function of time) in the hysteresis loop measurements with negative and positive sweep directions respectively. (d) Temperature-dependent hysteresis loops measured at 25 Hz. The remanent polarization as a function of temperature is shown in the inset. (e) Frequency-dependent hysteresis loops measured at 275 K. The inset shows the remanent polarizations measured at various frequencies. (f–i) Imprint of the hysteresis at various temperatures and frequencies. (f) The hysteresis loops measured at 250 K using positive and negative sweeps shift to opposite directions. (g) The hysteresis loops measured at 225 K using positive and negative sweeps show identical imprint. Opposite shifts are also observed in 500 Hz sweep (h), while they are not observed in 2.5 kHz sweep (i) at 275 K.

were observed in these devices. These novel ferroelectric heterostructures offer new opportunities for both fundamental studies and applications in data storage and electronics.

## ■ RESULTS AND DISCUSSION

Ferroelectricity of CIPS was measured on metal/CIPS/metal capacitors. Figure 1a shows the optical image of a CIPS capacitor, where the active area is marked. The thickness of the CIPS is 395 nm. Triangular read pulses with a preset pulse are used to measure the hysteresis loops, and the different sweep directions are named as "positive" and "negative" according to the direction of the first read pulse (Figure 1b,c). The preset pulse has the same rise/fall time as the read pulses and has opposite polarity as the first read pulse. The periods of the pulses are longer than the RC delay of the measurement circuits. The temperature-dependent hysteresis loops of the capacitor measured using positive sweep are shown in Figure 1d. A symmetric hysteresis loop is observed at 275 K with a remanent polarization of 4.8  $\mu$ C/cm<sup>2</sup>, which is consistent with the previous reports on CIPS near room temperature. 10,26,27,33 When the temperature reduces from 250 to 100 K, the hysteresis loop shifts toward the positive direction, and the remanent polarization decreases, as shown in the inset of Figure 1d. No hysteresis loop is observed below 50 K. Figure 1e presents hysteresis loops measured at various frequencies at 275 K with the positive sweep. The low-frequency hysteresis loop is symmetric, while the hysteresis loops at high

frequencies shift to the positive direction. The remanent polarization decreases logarithmically with the frequency, as shown in the inset of Figure 1e.

The imprint of the ferroelectric hysteresis loops can be attributed to the defect dipoles that cannot be switched at low temperatures or high frequencies. An opposite external electric field is required to cancel the polarization field from these dipoles; therefore, the central voltage of the hysteresis loop shifts oppositely. The Cu ions in CIPS are immobile when the temperature is below 231 K, and Cu atoms trapped in the interlayer sites can be the candidate for the pinned dipoles.<sup>31,34</sup> This hypothesis is supported by the hysteresis loops in Figure 1f-i measured with different sweep directions. At 250 K (Figure 1f), the hysteresis loop is shifted to the right under a positive sweep and to the left under a negative sweep. However, at 225 K (Figure 1g), identical right-shifted loops are observed for both sweep directions. This behavior is attributed to the temperature-dependent dipole switching. During the preset pulse, polarization of the dipoles can be aligned to the preset electric field, which causes the positive and negative shifts at 250 K. Since the dipole switching is associated with ion movement, these dipoles cannot switch at 225 K, which leads to identical hysteresis loops. The imprint of the ferroelectric hysteresis also has a strong frequency dependence. At 275 K, the imprint of the hysteresis loops measured at 500 Hz changes polarity depending on the sweep direction, as shown in Figure 1h. However, the imprint of the hysteresis

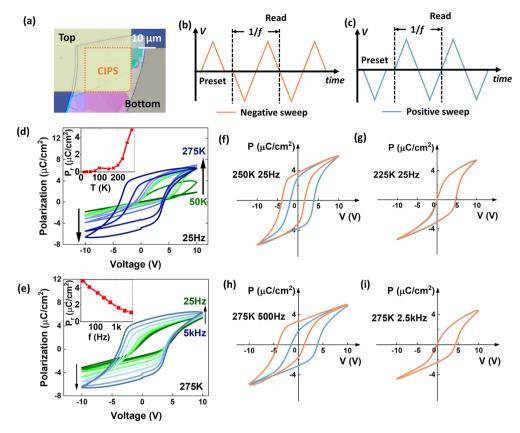

Figure 2. Variable write measurement and characteristic switching time in CIPS. (a) Illustrations of the pulse waveform used in the variable write measurement. The preset pulse pre-poles the film to certain polarization direction. The write pulse switches the polarization partially or completed depending on the amplitude and width of the pulse. The two read pulses measure the amount of polarization switched by the write pulse. (b) Switched polarization as a function of write pulse width at various pulse amplitudes. The inset shows the extracted characteristic switching time constant as a function of the reciprocal of the write pulse amplitude. The symbols are measured data, and the line is fitted using the NLS model.

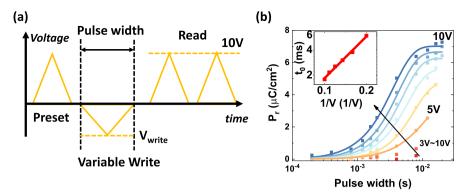

Figure 3. CIPS/MoTe<sub>2</sub> memory devices. (a, b) Schematic and optical image of a dual-gate MoTe<sub>2</sub> transistor with CIPS as the top-gate dielectric and 90 nm SiO<sub>2</sub> as the bottom-gate dielectric. The CIPS thickness is 310 nm, and the MoTe<sub>2</sub> thickness is 6.6 nm. Cr/Au and Ni/Au are used as channel contacts and top-gate electrode respectively. (c) Upward polarization in CIPS will induce hole doping in the MoTe<sub>2</sub> channel. (d) Transfer curves measured by sweeping the top gate at various temperatures. The clockwise hysteresis in the p-type transistor can be attributed to the ferroelectric switching. The drain voltage is 0.1 V. The temperature-dependent hysteresis window is shown in (e). (f) Memory effect measured using back gate. After applying positive or negative pulse on the top gate, the transfer curves are measured by sweeping the back gate. The transfer curve shifts to negative (positive) direction, corresponding to polarization down (up) states in the CIPS at both 150 and 275 K. (g) The memory window as a function of temperature.

loops at 2.5 kHz (Figure 1i) is identical regardless of the sweep direction, indicating that the defect dipoles are not switched by the fast preset pulse.

The switching behavior was further investigated using variable write measurement. The measurement consists of four voltage pulses, as illustrated in Figure 2a. The preset pulse pre-poles the film to certain polarization direction. The write pulse switches the polarization partially or completely depending on the amplitude and width of the pulse. The two read pulses measure the amount of polarization switched by the write pulse. The first read pulse is a switching pulse, while the second read pulse is a nonswitching pulse, which determines linear response of the dielectrics. By integrating the difference of the displacement currents in these two read

pulses, we can extract the amount of polarization switched by the write pulse

$$P_{\rm sw} = \frac{1}{A} \int_0^T (I_{\rm s} - I_{\rm ns}) \mathrm{d}t \tag{1}$$

where  $I_{\rm s}$  and  $I_{\rm ns}$  are the displacement currents measured in the first and second read pulses, respectively, A is the area of the device, and T is the pulse width. (The details of the variable write measurement are discussed in the Supporting Information.) The switched polarization measured at 275 K is plotted as a function of write pulse width at various pulse amplitudes, shown in Figure 2b. When the write pulse amplitude is low, one needs a rather long pulse to switch the polarization. In contrast, if the write pulse is sufficiently large, a short pulse

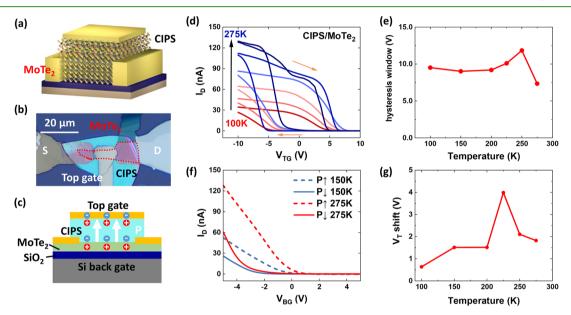

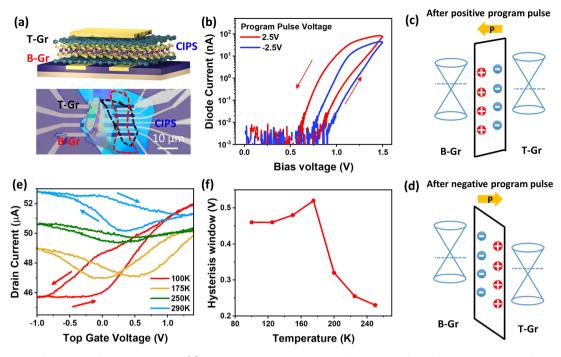

**Figure 4.** Graphene/CIPS multifunctional devices. (a) Schematic and optical image of a graphene/CIPS/graphene device. The thickness of the CIPS is 32 nm. (b) *IV* curves of graphene/CIPS/graphene ferroelectric vertical diode after positive and negative program pulses. The program pulse and DC drain voltage are applied on the top graphene with the bottom graphene grounded. (c, d) Band diagrams of graphene/CIPS/graphene after positive and negative program pulses, respectively. (e) Temperature-dependent transfer curves of the transistor with bottom graphene as channel, CIPS as the gate dielectric, and top graphene as gate. (f) Temperature-dependent hysteresis window of the graphene/CIPS transistor.

could switch a large amount of polarization. These results fit well with the nucleation-limited switching (NLS) model<sup>35</sup>

$$p(t) = 1 - e^{-(t/t_0)^n}$$

(2)

where p(t) is the fraction of the volume of the ferroelectric switched by time t,  $t_0$  is a characteristic switching time, and n is a parameter related to geometric dimension of the domain growth. The extracted n value shows a narrow distribution in the range of 1.4–1.6. The characteristic switching time is plotted as a function of 1/V, where V is the applied voltage, as shown in the inset of Figure 2b. The data are fitted using Merz's law:  $\tau = \tau_0 \exp((V_0/V)^n)$ ), where n=1 is used here;  $\tau_0$  is the switching time at infinite applied electric field and  $V_0$  is the activation voltage. The extracted  $\tau_0$  in CIPS is 0.59 ms, which is several orders of magnitude longer than  $\tau_0$  in doped HfO<sub>2</sub> (0.1 ps), indicating that the polarization switching in CIPS is very slow.

Based on the understanding of the ferroelectricity in CIPS, we further investigated the electronic devices based on CIPS heterostructures. First, we studied ferroelectric memory based on CIPS/MoTe<sub>2</sub> stacks. The structure and optical image of the device are shown in Figure 3a,b respectively. Dual-gate MoTe<sub>2</sub> transistors are fabricated, where CIPS serves as the top-gate dielectric and 90 nm SiO<sub>2</sub> serves as the bottom-gate dielectric. The CIPS thickness is 310 nm, and the MoTe<sub>2</sub> thickness is 6.6 nm. When the CIPS polarization switches direction, the polarization-induced doping in the MoTe<sub>2</sub> channel will also change polarity. A negative bias on the top gate will induce upward polarization, leading to hole doping to the MoTe<sub>2</sub> channel, as shown in Figure 3c. Conversely, a positive bias will introduce electron doping in MoTe<sub>2</sub>. The transfer curve measured by sweeping the top gate shows a clockwise

hysteresis loop for all temperatures (Figure 3d), which can be attributed to the ferroelectric switching at these temperatures. Further, the hysteresis window, defined as the shift of threshold voltage between the forward and backward sweeps, is plotted as a function of temperature, as shown in Figure 3e. As the temperature increases from 150 to 250 K, the hysteresis window increases slightly, indicating more dipoles become switchable. When the temperature exceeds 250 K, the hysteresis window starts to decrease and the underlying mechanism can be 2-fold. First, the interface traps at the MoTe<sub>2</sub>/CIPS interface are more active at high temperatures. Since the hysteresis induced by the interface traps is in the opposite direction to that induced by ferroelectric polarization, the total hysteresis window will reduce as temperature increases. Second, the dielectric constant of CIPS also increases as the temperature approaches the Curie temperature, which will lead to a smaller threshold voltage shift for a given polarization charge density.<sup>38</sup> The memory effect is also studied using back gate. Here, a square pulse with pulse amplitude of 8 V and pulse width of 10 s is applied on the top gate to pole the CIPS into upward or downward polarization. Furthermore, the memory windows of the CIPS/MoTe<sub>2</sub> transistors were also investigated. After applying positive and negative program pulses on the top gate, the transfer curves were measured by sweeping the back-gate bias, as shown in Figure 3f. A negative program pulse on the top gate will switch the polarization in CIPS to an upward direction, which will induce hole doping in the MoTe2 channel and a positive shift in the threshold voltage. The memory window, defined as the difference between the threshold voltages after positive and negative program pulses, is plotted as a function of temperature, as shown in Figure 3g. The memory window is found to increase from 100 to 225 K due to increased

remanent polarization in CIPS. The decrement of the memory window after 225 K indicates that the interface traps at the  ${\rm SiO_2/MoTe_2}$  interface start to shift the threshold voltage in an opposite direction.

Furthermore, we investigated the multifunctional devices based on graphene/CIPS/graphene heterostructures. The schematic and optical image of the device are shown in Figure 4a. CIPS is sandwiched by two layers of graphene in the vertical direction. In each layer of graphene, there are multiple electrodes so that both the vertical and lateral transport can be characterized concurrently. This device can serve as a ferroelectric junction, memory device, and logic device simultaneously. First, we investigated the ferroelectric junction between top and bottom graphene electrodes. A program pulse was applied on the top graphene electrode with bottom graphene electrode grounded. Then, the current of the junction was measured by sweeping the voltage on the top graphene, as shown in Figure 4b. We can see that the IV curve of the junction shifts toward the negative direction after positive program pulse. The current shift can be attributed to the polarization switching in CIPS. Figure 4c,d displays the energy diagrams of graphene/CIPS/graphene heterostructure after positive and negative program pulses, respectively. After positive program pulse, a downward polarization is formed in CIPS, which will induce negative charges and raise the Fermi level in the bottom graphene. The reduced Schottky barrier between the bottom graphene and CIPS will lead to a higher electron current, which is consistent with the left shift of the IV curve observed experimentally. Second, we studied the CIPS/ graphene ferroelectric transistor, where the top graphene serves as the gate, the bottom graphene serves as the channel, and CIPS serves as the gate dielectric. Figure 4e shows the temperature-dependent transfer curves of the graphene transistor measured from 100 to 290 K. All curves exhibit clockwise hysteresis loops for hole branch and counterclockwise hysteresis loops for electron branch, which are typical features for ferroelectric transistor. More importantly, the CIPS/graphene transistor exhibits no obvious ferroelectric hysteresis below 50 K, which is consistent with the temperature dependence of polarization in the CIPS capacitors, as shown in the inset of Figure 1d. Further, the hysteresis window of the graphene transistor is plotted as a function of temperature, shown in Figure 4f. As the temperature increases, the hysteresis window first increases and then decreases, similar to the CIPS/MoTe<sub>2</sub> transistor, which can be explained by the temperature dependence of polarization in CIPS and the influence of interface traps at high temperatures.

#### CONCLUSIONS

In summary, the temperature and frequency dependences of remanent polarization in CIPS capacitor are investigated systematically. The remanent polarization decreases dramatically as temperature goes below 250 K and disappears as temperature decreases below 50 K. Moreover, the remanent polarization degrades logarithmically as frequency increases. These phenomena can be explained by the defect-related dipoles, which pin the polarization at low temperatures and become switchable at high temperatures. These defect dipoles also lead to the strong temperature and frequency dependence of the imprint of the CIPS capacitors. These unique characteristics of CIPS are important factors to consider in designing and characterizing CIPS-based electronic devices.

Based on the understanding of the ferroelectricity in CIPS, we further investigated the electronic devices based on CIPS heterostructures including CIPS/MoTe<sub>2</sub> memory and graphene/CIPS/graphene multifunctional devices. Memory window and ferroelectric-induced resistive switching are observed in these devices, which can be explained by the electrostatic doping induced by the ferroelectric polarization. Temperature dependence of the hysteresis window in the CIPS transistors can be attributed to the interplay between remanent polarization in CIPS and interface traps. This research enriches the understanding of van der Waals ferroelectric materials and opens new opportunities for multifunction devices based on two-dimensional (2D) ferroelectric heterostructures.

## METHODS

The CIPS capacitors were fabricated on highly doped Si substrate with 90 nm SiO<sub>2</sub>. The bottom electrodes were patterned using photolithography followed by metal deposition of 5/15 nm Cr/Au. CIPS flakes were exfoliated on poly(dimethylsiloxane) (PDMS) films and then transferred onto the bottom electrodes. The top electrodes (20/50 nm Ni/Au) were then formed on CIPS. For the dual-gate memory devices, the MoTe2 channels were exfoliated on p-type Si substrate with 90 nm SiO<sub>2</sub>. Cr/Au (5/15 nm) was deposited to serve as the S/D contact. The CIPS flakes were then transferred on top of the MoTe2 channel. A subsequent photolithography step defined the top gates, and 20/80 nm Ni/Au was used as the top electrode. For the graphene/CIPS multifunctional devices, the CIPS flakes were exfoliated on the transparent gel film. Bulk graphite was exfoliated on a poly(methyl methacrylate)/poly(vinyl alcohol) (PMMA/PVA) film, and monolayer graphene can be identified by optical microscopy. Then, graphene, CIPS, and graphene are transferred on the bottom electrode (5/10 nm Ti/Au) respectively. Finally, electron beam lithography, metal deposition (5/20 nm Ti/Au), and liftoff process were conducted sequentially. We have fabricated four CIPS capacitors, three CIPS/MoTe<sub>2</sub> transistors, and two CIPS/graphene transistors. The representative results are shown in the main text and in the Supporting Information.

The voltage pulses were generated by Keithley 4225-RPM units, and the current was collected using a Keithley 4200-SCS analyzer. A Keysight B1500A analyzer was used to characterize CIPS memory devices and graphene/CIPS/graphene heterostructures. The thicknesses of the CIPS and MoTe<sub>2</sub> flakes were measured using an Asylum Cypher atomic force microscope (AFM).

#### ASSOCIATED CONTENT

#### **Supporting Information**

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsami.0c13799.

Procedure of variable write measurement for extraction of switchable polarization in CIPS; AFM topographic images and height profiles of the CIPS devices; comparison of the drain current and gate current of the CIPS transistors; and temperature-dependent transfer curves of the CIPS/graphene transistor (PDF)

# AUTHOR INFORMATION

# **Corresponding Author**

Wenjuan Zhu — Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana, Illinois 61801, United States; ⊚ orcid.org/0000-0003-2824-1386; Email: wjzhu@illinois.edu

#### **Authors**

- Zijing Zhao Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana, Illinois 61801, United States

- Kai Xu Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana, Illinois 61801, United States

- Hojoon Ryu Electrical and Computer Engineering, University of Illinois at Urbana-Champaign, Urbana, Illinois 61801, United States

Complete contact information is available at: https://pubs.acs.org/10.1021/acsami.0c13799

#### **Author Contributions**

Z.Z. and K.X. contributed equally. The manuscript was written through contributions of all authors. All authors have given approval to the final version of the manuscript.

#### **Notes**

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

The authors acknowledge support from the National Science Foundation (NSF) under grant ECCS 16-53241 CAR and from the Office of Naval Research (ONR) under grant NAVY N00014-17-1-2973.

## REFERENCES

- (1) Chanthbouala, A.; Crassous, A.; Garcia, V.; Bouzehouane, K.; Fusil, S.; Moya, X.; Allibe, J.; Dlubak, B.; Grollier, J.; Xavier, S.; Deranlot, C.; Moshar, A.; Proksch, R.; Mathur, N. D.; Bibes, M.; Barthelemy, A. Solid-State Memories Based on Ferroelectric Tunnel Junctions. *Nat. Nanotechnol.* **2012**, *7*, 101–104.

- (2) Si, M.; Jiang, C.; Chung, W.; Du, Y.; Alam, M. A.; Ye, P. D. Steep-Slope WSe<sub>2</sub> Negative Capacitance Field-Effect Transistor. *Nano Lett.* **2018**, *18*, 3682–3687.

- (3) Wu, G. J.; Tian, B. B.; Liu, L.; Lv, W.; Wu, S.; Wang, X. D.; Chen, Y.; Li, J. Y.; Wang, Z.; Wu, S. Q.; Shen, H.; Lin, T.; Zhou, P.; Liu, Q.; Duan, C. G.; Zhang, S. T.; Meng, X. J.; Wu, S. W.; Hu, W. D.; Wang, X. R.; Chu, J. H.; Wang, J. L. Programmable Transition Metal Dichalcogenide Homojunctions Controlled by Nonvolatile Ferroelectric Domains. *Nat. Electron.* **2020**, *3*, 43–50.

- (4) Hong, X.; Zou, K.; DaSilva, A. M.; Ahn, C. H.; Zhu, J. Integrating Functional Oxides with Graphene. *Solid State Commun.* **2012**, *152*, 1365–1374.

- (5) Martin, L. W.; Rappe, A. M. Thin-Film Ferroelectric Materials and Their Applications. *Nat. Rev. Mater.* **2017**, 2, No. 16087.

- (6) Park, M. H.; Lee, Y. H.; Kim, H. J.; Kim, Y. J.; Moon, T.; Kim, K. D.; Muller, J.; Kersch, A.; Schroeder, U.; Mikolajick, T.; Hwang, C. S. Ferroelectricity and Antiferroelectricity of Doped Thin HfO<sub>2</sub>-Based Films. *Adv. Mater.* **2015**, *27*, 1811–1831.

- (7) Katsouras, I.; Asadi, K.; Li, M.; van Driel, T. B.; Kjaer, K. S.; Zhao, D.; Lenz, T.; Gu, Y.; Blom, P. W.; Damjanovic, D.; Nielsen, M. M.; de Leeuw, D. M. The Negative Piezoelectric Effect of the Ferroelectric Polymer Poly(Vinylidene Fluoride). *Nat. Mater.* **2016**, 15, 78–84.

- (8) Cui, C.; Xue, F.; Hu, W.-J.; Li, L.-J. Two-Dimensional Materials with Piezoelectric and Ferroelectric Functionalities. *npj 2D Mater. Appl.* **2018**, *2*, No. 18.

- (9) Mehta, R. R.; Silverman, B. D.; Jacobs, J. T. Depolarization Fields in Thin Ferroelectric Films. *J. Appl. Phys.* **1973**, 44, 3379–3385.

- (10) Liu, F.; You, L.; Seyler, K. L.; Li, X.; Yu, P.; Lin, J.; Wang, X.; Zhou, J.; Wang, H.; He, H.; Pantelides, S. T.; Zhou, W.; Sharma, P.; Xu, X.; Ajayan, P. M.; Wang, J.; Liu, Z. Room-Temperature Ferroelectricity in  $CuInP_2S_6$  Ultrathin Flakes. *Nat. Commun.* **2016**, 7, No. 12357.

- (11) Deng, J. M.; Liu, Y. Y.; Li, M. Q.; Xu, S.; Lun, Y. Z.; Lv, P.; Xia, T. L.; Gao, P.; Wang, X. Y.; Hong, J. W. Thickness-Dependent In-Plane Polarization and Structural Phase Transition in Van Der Waals Ferroelectric CuInP<sub>2</sub>S<sub>6</sub>. Small **2020**, 16, No. 1904529.

- (12) Ding, W.; Zhu, J.; Wang, Z.; Gao, Y.; Xiao, D.; Gu, Y.; Zhang, Z.; Zhu, W. Prediction of Intrinsic Two-Dimensional Ferroelectrics in In<sub>2</sub>Se<sub>3</sub> and Other III<sub>2</sub>-VI<sub>3</sub> Van Der Waals Materials. *Nat. Commun.* **2017**, *8*, No. 14956.

- (13) Cui, C.; Hu, W. J.; Yan, X.; Addiego, C.; Gao, W.; Wang, Y.; Wang, Z.; Li, L.; Cheng, Y.; Li, P.; Zhang, X.; Alshareef, H. N.; Wu, T.; Zhu, W.; Pan, X.; Li, L. J. Intercorrelated In-Plane and Out-of-Plane Ferroelectricity in Ultrathin Two-Dimensional Layered Semiconductor In<sub>2</sub>Se<sub>3</sub>. *Nano Lett.* **2018**, *18*, 1253–1258.

- (14) Xiao, J.; Zhu, H.; Wang, Y.; Feng, W.; Hu, Y.; Dasgupta, A.; Han, Y.; Wang, Y.; Muller, D. A.; Martin, L. W.; Hu, P.; Zhang, X. Intrinsic Two-Dimensional Ferroelectricity with Dipole Locking. *Phys. Rev. Lett.* **2018**, *120*, No. 227601.

- (15) Higashitarumizu, N.; Kawamoto, H.; Lee, C. J.; Lin, B. H.; Chu, F. H.; Yonemori, I.; Nishimura, T.; Wakabayashi, K.; Chang, W. H.; Nagashio, K. Purely In-Plane Ferroelectricity in Monolayer SnS at Room Temperature. *Nat. Commun.* **2020**, *11*, No. 2428.

- (16) Chang, K.; Kuster, F.; Miller, B. J.; Ji, J. R.; Zhang, J. L.; Sessi, P.; Barraza-Lopez, S.; Parkin, S. S. P. Microscopic Manipulation of Ferroelectric Domains in SnSe Monolayers at Room Temperature. *Nano Lett.* **2020**, *20*, 6590–6597.

- (17) Chang, K.; Liu, J.; Lin, H.; Wang, N.; Zhao, K.; Zhang, A.; Jin, F.; Zhong, Y.; Hu, X.; Duan, W.; Zhang, Q.; Fu, L.; Xue, Q. K.; Chen, X.; Ji, S. H. Discovery of Robust In-Plane Ferroelectricity in Atomic-Thick SnTe. *Science* **2016**, *353*, 274–278.

- (18) Fei, Z.; Zhao, W.; Palomaki, T. A.; Sun, B.; Miller, M. K.; Zhao, Z.; Yan, J.; Xu, X.; Cobden, D. H. Ferroelectric Switching of a Two-Dimensional Metal. *Nature* **2018**, *560*, 336–339.

- (19) Yuan, S.; Luo, X.; Chan, H. L.; Xiao, C.; Dai, Y.; Xie, M.; Hao, J. Room-Temperature Ferroelectricity in MoTe<sub>2</sub> Down to the Atomic Monolayer Limit. *Nat. Commun.* **2019**, *10*, No. 1775.

- (20) You, L.; Liu, F.; Li, H.; Hu, Y.; Zhou, S.; Chang, L.; Zhou, Y.; Fu, Q.; Yuan, G.; Dong, S.; Fan, H. J.; Gruverman, A.; Liu, Z.; Wang, J. In-Plane Ferroelectricity in Thin Flakes of Van Der Waals Hybrid Perovskite. *Adv. Mater.* **2018**, *30*, No. 1803249.

- (21) Yap, W. C.; Jiang, H.; Liu, J. L.; Xia, Q. F.; Zhu, W. J. Ferroelectric Transistors with Monolayer Molybdenum Disulfide and Ultra-Thin Aluminum-Doped Hafnium Oxide. *Appl. Phys. Lett.* **2017**, *111*. No. 013103.

- (22) Lipatov, A.; Sharma, P.; Gruverman, A.; Sinitskii, A. Optoelectrical Molybdenum Disulfide (MoS<sub>2</sub>)—Ferroelectric Memories. *ACS Nano* **2015**, *9*, 8089–8098.

- (23) Si, M.; Liao, P. Y.; Qiu, G.; Duan, Y.; Ye, P. D. Ferroelectric Field-Effect Transistors Based on  $MoS_2$  and  $CuInP_2S_6$  Two-Dimensional Van Der Waals Heterostructure. *ACS Nano* **2018**, *12*, 6700–6705.

- (24) Wang, X. D.; Wang, P.; Wang, J. L.; Hu, W. D.; Zhou, X. H.; Guo, N.; Huang, H.; Sun, S.; Shen, H.; Lin, T.; Tang, M. H.; Liao, L.; Jiang, A. Q.; Sun, J. L.; Meng, X. J.; Chen, X. S.; Lu, W.; Chu, J. H. Ultrasensitive and Broadband MoS<sub>2</sub> Photodetector Driven by Ferroelectrics. *Adv. Mater.* **2015**, *27*, 6575–6581.

- (25) Studenyak, I. P.; Mitrovcij, V. V.; Kovacs, G. S.; Gurzan, M. I.; Mykajlo, O. A.; Vysochanskii, Y. M.; Cajipe, V. B. Disordering Effect on Optical Absorption Processes in CuInP<sub>2</sub>S<sub>6</sub> Layered Ferrielectrics. *Phys. Status Solidi B* **2003**, 236, 678–686.

- (26) Shusta, V. S.; Prits, I. P.; Guranich, P. P.; Gerzanich, E. I.; Slivka, A. G. Dielectric Properties of CuInP<sub>2</sub>S<sub>6</sub> Crystals under High Pressure. *Condens. Matter Phys.* **2007**, *10*, 91–94.

- (27) Belianinov, A.; He, Q.; Dziaugys, A.; Maksymovych, P.; Eliseev, E.; Borisevich, A.; Morozovska, A.; Banys, J.; Vysochanskii, Y.; Kalinin, S. V. CuIn $P_2S_6$  Room Temperature Layered Ferroelectric. *Nano Lett.* **2015**, *15*, 3808–3814.

- (28) Balke, N.; Neumayer, S. M.; Brehm, J. A.; Susner, M. A.; Rodriguez, B. J.; Jesse, S.; Kalinin, S. V.; Pantelides, S. T.; McGuire, M. A.; Maksymovych, P. Locally Controlled Cu-Ion Transport in

- Layered Ferroelectric CuInP<sub>2</sub>S<sub>6</sub>. ACS Appl. Mater. Interfaces 2018, 10, 27188–27194.

- (29) Sun, Z.; Huang, H.; Xun, W.; Shi, S.; Hao, X.; Ju, S.; Wu, Y. First-Principle Study of Sulfur Vacancy and O<sub>2</sub> Adsorption on the Electronic and Optical Properties of Ferroelectric CuInP<sub>2</sub>S<sub>6</sub> Monolayer. *J. Phys.: Condens. Matter* **2020**, 32, No. 335001.

- (30) You, L.; Zhang, Y.; Zhou, S.; Chaturvedi, A.; Morris, S. A.; Liu, F.; Chang, L.; Ichinose, D.; Funakubo, H.; Hu, W.; Wu, T.; Liu, Z.; Dong, S.; Wang, J. Origin of Giant Negative Piezoelectricity in a Layered Van Der Waals Ferroelectric. Sci. Adv. 2019, 5, No. eaav3780.

- (31) Brehm, J. A.; Neumayer, S. M.; Tao, L.; O'Hara, A.; Chyasnavichus, M.; Susner, M. A.; McGuire, M. A.; Kalinin, S. V.; Jesse, S.; Ganesh, P.; Pantelides, S. T.; Maksymovych, P.; Balke, N. Tunable Quadruple-Well Ferroelectric Van Der Waals Crystals. *Nat. Mater.* **2020**, *19*, 43–48.

- (32) Maisonneuve, V.; Reau, J. M.; Dong, M.; Cajipe, V. B.; Payen, C.; Ravez, J. Ionic Conductivity in Ferroic CuInP<sub>2</sub>S<sub>6</sub> and CuCrP<sub>2</sub>S<sub>6</sub>. Ferroelectrics **1997**, *196*, 257–260.

- (33) Si, M.; Saha, A. K.; Liao, P. Y.; Gao, S.; Neumayer, S. M.; Jian, J.; Qin, J.; Balke Wisinger, N.; Wang, H.; Maksymovych, P.; Wu, W.; Gupta, S. K.; Ye, P. D. Room-Temperature Electrocaloric Effect in Layered Ferroelectric CuInP<sub>2</sub>S<sub>6</sub> for Solid-State Refrigeration. *ACS Nano* **2019**, *13*, 8760–8765.

- (34) Zhou, S.; You, L.; Chaturvedi, A.; Morris, S. A.; Herrin, J. S.; Zhang, N.; Abdelsamie, A.; Hu, Y. Z.; Chen, J. Q.; Zhou, Y.; Dong, S. A.; Wang, J. L. Anomalous Polarization Switching and Permanent Retention in a Ferroelectric Ionic Conductor. *Mater. Horiz.* **2020**, *7*, 263–274.

- (35) Tagantsev, A. K.; Stolichnov, I.; Setter, N.; Cross, J. S.; Tsukada, M. Non-Kolmogorov-Avrami Switching Kinetics in Ferroelectric Thin Films. *Phys. Rev. B* **2002**, *66*, No. 214109.

- (36) Merz, W. J. Domain Formation and Domain Wall Motions in Ferroelectric BaTiO<sub>3</sub> Single Crystals. *Phys. Rev.* **1954**, *95*, 690–698.

- (37) Gong, N.; Sun, X.; Jiang, H.; Chang-Liao, K. S.; Xia, Q.; Ma, T. P. Nucleation Limited Switching (NLS) Model for HfO<sub>2</sub>-Based Metal-Ferroelectric-Metal (MFM) Capacitors: Switching Kinetics and Retention Characteristics. *Appl. Phys. Lett.* **2018**, *112*, No. 262903.

- (38) Banys, J.; Samulionis, V.; Cajipe, V. Dielectric Properties in the Vicinity of Phase Transition of New Ferroelectric CuInP<sub>2</sub>S<sub>6</sub>. Ferroelectrics **1999**, 223, 43–50.