Ionic liquid gel gate tunable p-Si/MoS<sub>2</sub> heterojunction p-n diode

Kelotchi S. Figueroa<sup>1</sup>, Nicholas J. Pinto<sup>1,a</sup>, Chengyu Wen<sup>2</sup>, A.T. Charlie Johnson<sup>2</sup>, Meng-

Qiang Zhao<sup>3</sup>

<sup>1</sup>Department of Physics and Electronics, University of Puerto Rico at Humacao, Humacao, PR

00791

<sup>2</sup>Department of Physics and Astronomy, University of Pennsylvania, Philadelphia, PA 19104

<sup>3</sup>Department of Chemical and Materials Engineering, New Jersey Institute of Technology,

*Newark. NJ 07102*

**Abstract:**

Monolayer MoS<sub>2</sub> crystals investigated in this work were grown via chemical vapor

deposition on Si/SiO2 substrates. Using a wet KOH etch, these crystals were transferred on to the

edge of a freshly cleaved p-Si/SiO<sub>2</sub> wafer where they formed mechanically robust heterojunctions

at the p-Si/MoS<sub>2</sub> interface. Electrical characterization of the device across the junction yielded an

asymmetric I-V response similar to a *p-n* diode. The I-V response was electrostatically tunable *via*

an ionic liquid gel gate. This is the first report demonstrating reversible gate control of the p-

Si/MoS<sub>2</sub> diode current by several orders of magnitude while lowering its turn-on voltage. Fermi

energy level shifts within the MoS<sub>2</sub> band gap by the gate was believed responsible for the observed

effects. The ease of fabrication, low operating voltages ( $<\pm 2V$ ) and moderately high throughput

currents (~ 1µA) are attractive features of this diode, especially for use in sensors and power saving

electronics.

<sup>a</sup>Corresponding Author; email: nicholas.pinto@upr.edu

1

#### I. Introduction

Modern-day solid-state devices are a result of scientific progress in the physics of semiconductors. Impurity doping gives these materials technologically important attributes, for e.g. Choice of charge carrier type[1] and control of charge concentration *via* for example an external electric field[2]. Generally classified as *p*- or *n*-type, semiconductors are an essential component of the electronics industry. Bonding together a *p*- and an *n*-type semiconductor yields a junction diode that possesses unique characteristics, such as allowing current to flow in one direction across the junction while blocking it in the other[3]. It is a device that can rectify alternating signals and forms the fundamental building block in complex integrated circuits. Expanding the use of a *p*-*n* diode beyond rectification is an active field of study that has led to novel applications ranging from solar cells[4], to LASERS[5] and light emitting diodes[6]. Controlling some of the diode parameters, like the current or the turn-on voltage, further enhances its functionality and is the primary focus of this work.

The recently discovered two-dimensional (2D) transition metal dichalcogenides (TMDC's) have similar electronic properties as classical semiconductors[7,8]. Investigating these materials is important from the viewpoint of new physics and device applications. Molybdenum disulfide (MoS<sub>2</sub>) is one such TMDC that exhibits stable *n*-type semiconducting behavior and can be controllably grown in the laboratory *via* chemical vapor deposition (CVD)[9, 10]. Diodes using MoS<sub>2</sub> have recently been shown to be tunable in addition to exhibiting electro-optic properties[11-15]. We previously reported on a UV light tunable, CVD grown MoS<sub>2</sub>/*p*-Si junction diode with rectifying capability[16]. Herein we extend that study to include electrostatic tuning of a similar diode *via* an ionic liquid (IL) gel gate. Two factors motivated us to use an IL gel for gating: the diode architecture that was ideally suited for manual application of a liquid gate material (no

cumbersome spin-coating or thermal evaporation was needed), and the high IL specific capacitance that ensured low operating voltages. This is the first report where IL gel gating is shown to reversibly control a MoS<sub>2</sub> based diode current by several orders of magnitude while lowering its turn-on voltage. The ease of fabrication, low operating voltages ( $<\pm 2V$ ) and moderately high throughput currents ( $\sim 1\mu A$ ) makes this diode useful in sensors and as a power saving device in battery operated electronics.

## II. Experimental

Monolayer MoS<sub>2</sub> crystals of varying sizes were grown on Si/SiO<sub>2</sub> substrates *via* CVD as reported earlier[10] and transferred to a new substrate for diode fabrication. In the transfer process, a thin film of poly (methyl methacrylate)-PMMA was spun coated over the original substrate and then immersed in a 1M KOH solution. Slow dissolution of the SiO<sub>2</sub> layer resulted in a free standing PMMA film with MoS<sub>2</sub> crystals adhered to it on the underside. The film was placed in distilled water for several hours to ensure complete removal of KOH prior to the final transfer.

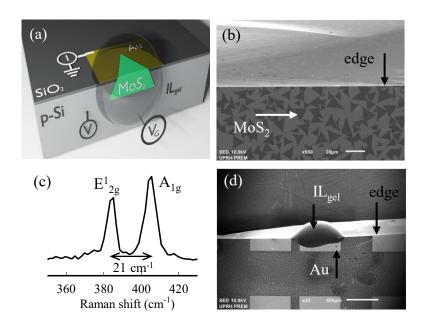

Separately, a p-(Boron) doped Si ( $\rho$  = 0.1-0.5  $\Omega$ -cm) substrate with a 200nm thermally grown oxide layer was pre-patterned with Au electrodes using standard photolithography and lift off techniques. This substrate was then cleaved through the electrodes, resulting in several sliced Au contacts lining the cleaved edge. The PMMA film described above was carefully fished out of the water using the pre-patterned substrate, making sure that part of the film reached past the cleaved edge. After drying in air at 90 °C overnight, the substrate was carefully washed in acetone to dissolve the PMMA. This resulted in MoS<sub>2</sub> crystals sticking firmly to the substrate top and the freshly exposed cleaved surfaces. Some crystals also lay bent along the cleaved edge, firmly contacting the Au electrodes above and the p-Si below the oxide layer. Figure 1(a) shows a

schematic of the device together with the electrical circuit used to characterize it. Figure 1(b) shows a top view scanning electron microscope image of the actual device. MoS<sub>2</sub> crystals are seen lying on the substrate top surface and along the cleaved edge. Some crystals can also be seen on the sloped section of the cleaved surface, though blurry, as it was difficult to focus at once on the entre substrate. Figure 1(c) shows the Raman spectra of the as grown MoS<sub>2</sub> crystals. The peak separation of 21 cm<sup>-1</sup> between the in-plane E<sup>1</sup><sub>2g</sub> and the out-of-plane A<sub>1g</sub> modes confirmed that the MoS<sub>2</sub> used was monolayer thick and of high purity[17]. The IL 1-ethyl-3-methylimidazolium bis(trifluoromethylsulfonyl) imide was used in this work because of its chemical stability and large specific capacitance. The final gate material (ILgel) was prepared by gelation of the IL with the triblock copolymer poly(styrene-b-methyl methacrylate-b-styrene) in dichloromethane as reported earlier[18,19,20]. The gel was placed in an oven at 70 °C for several minutes to increase its viscosity via solvent evaporation. This kept it from spreading after being cast on the substrate. A small drop of ILgel was placed at the location of the diode, and a gold wire inserted into the drop served as the gate electrode. Figure 1(d) shows the same substrate as in Figure 1(b), but at a lower magnification and after the IL<sub>gel</sub> drop was placed over the substrate edge at the location of the diode. External electrical contacts to the device as seen in Figure 1(a) were hard wired using silver epoxy prior to electrical characterization. The asymmetric current-voltage (I-V) response confirms the formation of a p-n diode at the  $p-Si/MoS_2$  interface as explained later.

Electrical characterization of the diode was performed using a Keithley Model 6517B Electrometer in conjunction with a Keithley Model 2400 Source Meter. All measurements were made in the dark at room temperature, and in a vacuum of 10<sup>-2</sup> Torr to avoid effects of moisture. The IL was electrically characterized using an Agilent Technologies Model 4294A Precision Impedance Analyzer in conjunction with a HP 16453A modified dielectric test fixture.

### III. Results and Discussion

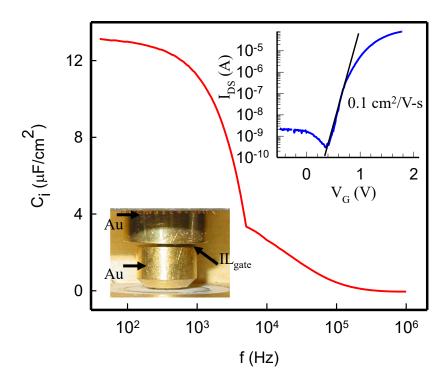

The IL<sub>gel</sub> was electrically characterized in air prior to testing it in the device. For capacitance measurements, the IL<sub>gel</sub> was carefully inserted into the space between closely spaced parallel Au electrodes of the test fixture via capillary action as seen in the lower insert to Figure 2. Figure 2 shows the IL<sub>gel</sub> specific capacitance ( $C_i$ ) as a function of the exciting electric field frequency in the range 40Hz – 1MHz. The voltage was fixed at 500mV.  $C_i$  is relatively constant at low frequencies, consistent with previous results[20], and decreases at high frequencies due to the inability of the heavy ions in the IL<sub>gel</sub> to follow the oscillating electric field. Extrapolating the graph in Figure 2, at very low frequencies  $C_i$  approaches 13  $\mu$ F/cm<sup>2</sup> which is relatively high due to the formation of nanometer thick electrical double layers at the electrode-ionic liquid gel interface[21]. For comparison, the specific capacitance of a 150nm thick SiO<sub>2</sub> layer is 20 nF/cm<sup>2</sup> [22]. An advantage of using a high  $C_i$  gate material is the large electric field generated by a low applied voltage.

Monolayer MoS<sub>2</sub> has a band gap of 1.8eV and exhibits *n*-type conduction[8, 23]. This was independently verified by fabricating a MoS<sub>2</sub> field effect transistor (FET) in bottom contact geometry with Au source and drain electrodes and top IL<sub>gel</sub> gating. The upper inset to Figure 2 shows the FET trans-conductance curve i.e. Drain-source current (I<sub>DS</sub>) as a function of gate voltage (V<sub>G</sub>) for a fixed drain-source voltage (V<sub>DS</sub>) on a semi-logarithmic scale. Figure S1(a) (Supplementary material) shows the device I<sub>DS</sub> vs. V<sub>DS</sub> curves for various gate voltages, and S1(b) shows the device trans-conductance curve using a linear scale, together with the gate leakage current. No reference electrode was inserted into the IL<sub>gel</sub> for voltage measurements since the leakage current was several orders of magnitude smaller that the MoS<sub>2</sub> channel current. In all these Figures, I<sub>DS</sub> increased as V<sub>G</sub> was made more positive, and stayed small and relatively constant

when V<sub>G</sub> was made more negative. This confirmed *n*-type conduction with accumulation mode transport under a positive gate voltage and depletion mode for voltages below the threshold voltage ( $\sim 0.3 \text{V}$ )[8]. The mobility calculated from the device trans-conductance was  $\sim 0.1 \text{ cm}^2/\text{V}$ -s and the on/off ratio was  $\sim 3 \times 10^5$ . These values were consistent with previous measurements[16, 24]. Mirco-cracks and/or wrinkles on the MoS<sub>2</sub> surface during the transfer process could be a reason for the low mobility. The linear variation of I<sub>DS</sub> at low V<sub>DS</sub> in Figure S1(a) shows the absence of Schottky barriers, while the symmetric I<sub>DS</sub>-V<sub>DS</sub> in the upper inset to Figure S1(a) confirms Ohmic MoS<sub>2</sub> contacts with the Au source and drain electrodes. In addition, the channel resistance of 5.3 k $\Omega$  calculated from the slope of the line in Figure S1(a) confirmed a low contact resistance between MoS<sub>2</sub> and the Au electrodes[9]. These measurements are presented to support our explanation of the *p*-Si/MoS<sub>2</sub> diode response to a gate voltage.

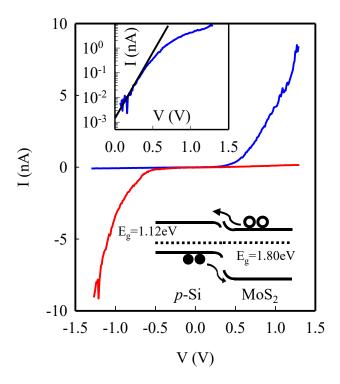

Figure 3 shows the I-V response curves of the diode as seen in Figure 1(d) with  $V_G = 0V$ . Connecting the external power supply positive terminal to the p-Si contact and the negative power supply terminal to the MoS<sub>2</sub> contact of the diode resulted in the blue curve, where the diode was forward biased in the first quadrant and reverse biased in the third quadrant. Reversing the external connections yielded the red curve. These results were consistent with the standard operation of a p-n diode[3]. The Ohmic and low contact resistance of MoS<sub>2</sub> with the Au electrodes, as discussed earlier, suggested that the non-linear I-V curve in this device arose from the p-Si/MoS<sub>2</sub> junction. The observed currents were limited by the series resistances of each material away from the junction. Several diodes were tested with similar asymmetric I-V curves. For this diode, the turn-on voltage was 0.70V and was determined by extrapolating the linear portion of I-V curve under forward bias toward the voltage axis at zero current. The turn-on voltage for the other diodes tested with  $V_G = 0V$  are not the same. This could be due to differences in the physical contact between

p-Si and MoS<sub>2</sub> at the interface for each diode. The ratio of the "on" state current to the "off" state current measured at the bias voltage of  $\pm 1.3$ V respectively was  $\sim 100$  for this diode. The asymmetric I-V curve can be qualitatively explained using the band diagram corresponding to the two semiconductors as shown in the lower inset to Figure 3. MoS<sub>2</sub> has a band gap of 1.8eV[8, 23] while for p-Si it is  $\sim 1.12 \text{eV}[1]$ . The relative positions of the valence, conduction and Fermi energy levels in each semiconductor are indicated in the inset. With no external bias voltage (V) and in thermal equilibrium, electrons (open circles) in MoS<sub>2</sub> diffuse across the junction and recombine with holes (closed circles) in p-Si creating a depletion zone inside p-Si (since monolayer MoS<sub>2</sub> does not support a depletion region under forward bias[13]). This resulted in band bending inside p-Si that established a constant Fermi level across the junction. As a result, a potential barrier was set-up that prevented further diffusion of electrons into p-Si. Externally biasing the diode resulted in the observed I-V curves of Figure 3, as the Fermi levels readjusted in such way that the potential barrier to current across the junction increased (reverse bias) or decreased (forward bias) as V was varied. The I-V curve under forward bias increased exponentially and can be analyzed using the diode equation  $I = I_s[\exp(\frac{eV}{nk_BT}) - 1]$ , where  $I_s$  is the reverse saturation current, e is the electronic charge, n is the ideality parameter,  $k_{\rm B}$  is the Boltzmann constant and T the temperature[25]. The upper inset to Figure 3 shows the same data in the forward bias region on a semi-logarithmic plot. Using the slope of the straight line and the equation above we calculated an ideality parameter of ~3.4 for this diode. Applying a gate voltage retained the asymmetric shape of the I-V curve, but also led to changes in the diode current and turn-on voltage as discussed in the next paragraph.

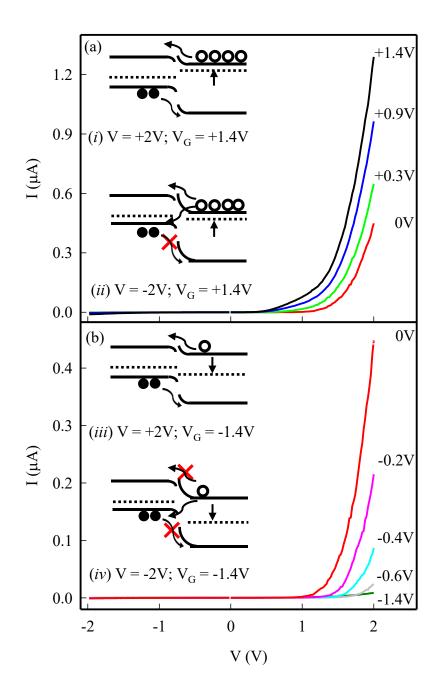

Figures 4(a) and (b) show the IL gated diode I-V curves for different gate voltages starting at  $V_G = -1.4V$ . At the end of each I-V scan,  $V_G$  was increased by +0.1V successively until  $V_G = -1.4V$ .

+1.4V. The data plotted in Figure 4 are split in two panels to better observe the changes in the "on" state current that is measured at V = +2V. Each panel contains data for a few selected gate voltages as indicated near each plot. Figures S2(a) and (b) shows the complete I-V measurements as V6 was changed from -1.4V  $\rightarrow$  +1.4V  $\rightarrow$  -1.3V in steps of 0.1V and confirmed the reversibility of these results. If the MoS2 film in the diode was replaced with a drop of silver paint, the I-V curve was symmetric with no significant changes as V6 was varied as seen in Figure S3. This strengthens our claim that the p-Si/MoS2 interface results in a junction diode. Figure S3 also shows that a IL gating does not affect charge concentration in p-Si. Two distinct features are visible in Figures 4(a), (b) and Figure S2(a). The "on" state currents increase and the diode turn-on voltage decrease as V6 is made more positive. The "off" state current measured at V = -2.0V were small compared to the "on" state current. The "off" state current for V6 < 0 was comparable to the gate leakage current which was typically a few nA. This made it difficult to accurately determine the diode on/off rectification ratio. We therefore focus on the changes in the "on" state current of the diode, and the turn-on voltage as V6 is varied.

The insets to Figure 4(a) and (b) show the semiconductor band diagrams under specific applied voltages as indicated, and that help explain the asymmetry of the I-V curves. A comparison can be made to the band diagram shown in the inset to Figure 3 for energy level identification. The highest recorded "on" state current flows through the diode when V = +2.0V and  $V_G = +1.4V$ . Under these conditions, the Fermi level in MoS<sub>2</sub> shifts upward closer to the conduction band as indicated by the vertical up arrow in Inset (*i*). Electrons are electrostatically induced into the conduction band of MoS<sub>2</sub> resulting in accumulation mode operation. The diode is also forward biased by V which reduces the potential barrier as seen in this inset Figure. Electrons in MoS<sub>2</sub> flow into the conduction band of *p*-Si and holes in *p*-Si flow into the valence band of MoS<sub>2</sub>, resulting

in a large observed current. When  $V_G = +1.4V$  and V = -2.0V as seen in Inset (ii), the diode is reverse biased which increases the potential barrier, making it difficult for holes or electrons to flow into the corresponding valence or conduction band respectively. The current under reverse bias is therefore reduced even though the positive gate voltage maintains accumulation mode transport in MoS<sub>2</sub>. As seen in the Inset (ii), it is possible that electrons in MoS<sub>2</sub> tunneling across the junction and recombine with holes in p-Si, with the excess electrons contributing to the observed current at V = -2.0V as seen later in Figure 5(c). The barrier for hole transport from p-Si into the valence band of MoS<sub>2</sub> is too high and hole charge transport is unlikely as indicated with the red X sign. When  $V_G = -1.4V$ , the Fermi level shifts downward toward the center of the band as seen in Inset (iii) and MoS<sub>2</sub> operates in the depletion mode. The overall induced electron density in MoS<sub>2</sub> is small so that even under forward bias (V = +2.0V) the "on" state current is small. The effective barrier is also increased which results in a larger turn on voltage. Finally, the lowest currents were observed under the reverse bias condition V = -2.0 V and  $V_G = -1.4 V$  as seen in Inset (iv). The barriers for electron and hole transport into the corresponding conduction and valence bands are too large, forbidding such transport as indicated by the red X signs. Tunneling across the junction could lead to possible electron-hole recombination. The overall measured currents however are small under forward or reverse bias and are comparable to the gate leakage current in the nA range.

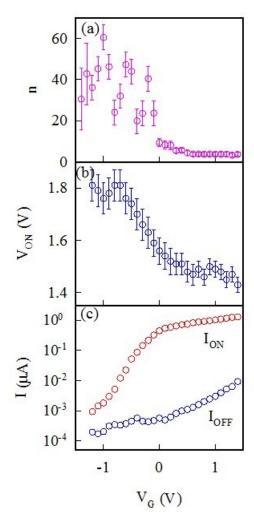

Figures 4(a), (b) and Figure S2(a) were further examined using the diode equation to better visualize the effects of  $V_G$  on diode performance. Figures 5(a), (b) and (c) show the ideality parameter, turn-on voltage, the "on" and "off" currents respectively of the diode as a function of  $V_G$ . For positive  $V_G$ , n stays relatively constant at  $\sim 3.5$  suggesting diode operation that is stable. The diode turn-on voltage decreases while the throughput current increases up to three orders of

magnitude as  $V_G$  increases. A gate tunable turn-on voltage with high throughput currents ( $\geq \sim 1 \mu A$ ) also enhances the diode functionality. A noticeable change in the slope is observed for all the curves in Figure 5 around a threshold voltage of V<sub>G</sub> ~ 0V. Since V<sub>G</sub> has no effect on charge transport in p-Si, the observed changes arise from the gate control of the charge concentration in MoS<sub>2</sub>. It is a change that is most likely associated with the Fermi energy adjustment within the MoS<sub>2</sub> band gap. Charge transport in MoS<sub>2</sub> shifts from accumulation to depletion mode as V<sub>G</sub> is reduced below a certain gate threshold. Once MoS<sub>2</sub> enters depletion mode, it presents a high series resistance in the diode circuit resulting in low throughput currents under forward and reverse bias conditions. This leads to large variations in determining the differential current necessary for calculating n. In the extreme case, V = -2V;  $V_G = -1.4V$ , there is a possibility of charge recombination that also leads to an increase in n. Above 0V however, V<sub>G</sub> does control the diode current under forward bias as seen in Figures 4(a) and (b) and the *n* values are more reliable. This is the first report of electrostatic current control over a wide range and at low operating voltages using IL<sub>gel</sub> gating in a p-Si/MoS<sub>2</sub> diode. A sensor-controlled diode is one application, where the sensing signal is applied to the gate that subsequently enhances, reduces, or completely shuts down diode operation. In addition, the multifunctionality offered by gating could transform the diode into a power saving device by sourcing the optimum current for specific applications.

### **IV. Conclusions**

We present an easy method of fabricating a p-n diode using a p-Si substrate and n-type monolayer MoS<sub>2</sub> crystals. Gating with an ionic liquid gel permitted reversible control of the diode throughput current over several decades while maintaining a relatively constant ideality parameter. The gate voltage adjusts the Fermi energy within the MoS<sub>2</sub> band gap and controlled the barrier height at the interface with p-Si. This consequently lowered the turn-on voltage and increased the

current for  $V_G > 0$  under forward bias, while suppressing diode operation for  $V_G < 0$ . Electrostatic current control at low voltages enhances the diodes' functionality making it useful in other applications besides rectification. The ease of fabrication, low operating voltages ( $< \pm 2V$ ) and moderately high throughput currents ( $\sim 1\mu A$ ) are attractive features of this diode, especially for use in sensors and power saving electronics.

# **Supplementary Material**

See the supplementary material for additional plots of the experimental results.

# Acknowledgements

This work was supported by the National Science Foundation under Grant Nos. DMR-PREM-1523463 and DMR-RUI-1800262. M.Q.Z, C.W, and A.T.C.J are supported by the NSF MRSEC DMR-1720530. The authors acknowledge the use of the Raman system supported by NSF Major Research Instrumentation Grant DMR-0923245. This work was carried out in part at the Singh Center for Nanotechnology, part of the National Nanotechnology Coordinated Infrastructure Program, which is supported by the National Science Foundation grant NNCI-1542153.

### **Data Availability**

All the data presented in this work will be made available upon request.

#### References

- [1] S.M. Sze, "Physics of Semiconductor Devices" John Wiley & Sons, 2<sup>nd</sup> Ed. Ch. 1 (1981).

- [2] E. Fortunato, P. Barquinha and R. Martins, "Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances" Adv. Mater. **24**, 2945 (2012).

- [3] D.A. Neamen, "Semiconductor Physics and Devices" McGraw Hill, 3<sup>rd</sup> Ed. Ch. 8.

- [4] B. Oregan and M. Gratzel, "A low cost, high efficiency solar cell based on dye-sensitized colloidal TiO<sub>2</sub> films, Nature **353**, 737 (1991).

- [5] S. Nakamura, "The roles of structural imperfections in InGaN-Based blue light-emitting diodes and laser diodes" Science **281**, 956 (1998).

- [6] J.H. Burroughes, D.D.C. Bradley, A.R. Brown, R.N. Marks, K. Mackay, R.H. Friend, P.L. Burns and A.B. Holmes, "Light-emitting diodes based on conjugated polymers" Nature **347**, 539 (1990).

- [7] K.S. Novoselov, A. Mishchenko, A. Carvalho and A. H. Castro Neto, "2D materials and van der Waals heterostructures" Science **353**, aac9439 (2016).

- [8] R. Ganatra and Q. Zhang, "Few-Layer MoS<sub>2</sub>: A Promising Layered Semiconductor" ACS Nano **8**, 4074 (2014).

- [9] B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti and A. Kis, "Single-layer MoS<sub>2</sub> transistors" Nat. Nanotechonology **6**, 147 (2011).

- [10] G.H. Han, N.J. Kybert, C. H. Naylor, B.S. Lee, J. Ping, J.H. Park, J. Kang, S.Y. Lee, Y.H. Lee, R. Agarwal, A. T. Charlie Johnson, Seeded growth of highly crystalline molybdenum disulphide monolayers at controlled locations, Nat. Commun., 6, 6128 (2015).

- [11] D. Jariwala, V.K. Sangwan, C.-C. Wu, P.L. Prabhumirashi, M.L. Geier, T.J. Marks, L.J. Lauhon and M.C. Hersam, "Gate-tunable carbon nanotube-MoS<sub>2</sub> heterojunction p-n diode" Proc. Nat. Aca. Sci. **110**, 18076 (2013).

- [12] Y. Deng, Z. Luo, N. J. Conrad, H. Liu, Y. Gong, S. Najmaei, P. M. Ajayan, J. Lou, X. Xu, P.D. Ye, "Black phosphorus-monolayer MoS<sub>2</sub> van der Waals heterojunction p-n diode" ACS Nano 8, 8292 (2014).

- [13] C.-H. Lee, G.-H. Lee, A. M. van der Zande, W. Chen, Y. Li, M. Han, X. Cui, G. Arefe, C. Nuckolls, T.F. Heinz, J. Guo, J. Hone, P. Kim, "Atomically thin p-n junctions with van der Waals heterointerfaces" Nat. Nanotechnology **9**, 676 (2014).

- [14] B.W.H. Baugher, H.O.H. Churchill, Y. Yang and P.J. Herrero, "Optoelectronics with electrically tunable p-n diodes in a monolayer dichalcogenide" Nat. Nanotechnology **9**, 262 (2014).

- [15] S. Lin, P. Wang, X. Li, Z. Wu, Z. Xu, S. Zhang and W. Xu, "Gate tunable monolayer MoS<sub>2</sub>/InP heterostructure solar cells", Appl. Phys. Lett. **107**, 153904 (2015).

- [16] W. Serrano, N.J. Pinto, C.H. Naylor, N.J. Kybert, and A. T. Charlie Johnson Jr., "Facile fabrication of a ultraviolet tunable MoS<sub>2</sub>/p-Si junction diode" Appl. Phys. Lett. **106**, 193504 (2015).

- [17] C. Lee, H. Yan, L.E. Brus, T.F. Heinz and J. Hone and S. Ryu, "Anomalous Lattice Vibrations of Single and Few Layer MoS<sub>2</sub>, ACS Nano 4, 2695 (2010).

- [18] J. Lee, L.G. Kaake, J.H. Cho, X.Y. Zhu, T.P. Lodge, C.D. Frisbie, "Ion gel-gated polymer

transistors: operating mechanism and characterization of gate dielectric capacitance, switching speed and stability, J. Phys. Chem. C **113**, 8972 (2009).

- [19] C.H. Kim, C.D. Frisbie, "Determination of quantum capacitance and band filling potential in graphene transistors with dual electrochemical and field effect gates" J. Phys. Chem. C 118, 21160 (2014)

- [20] D.N. Ortiz and N.J. Pinto, "Ionic liquid gel gated electro-spun poly(3,4-ethylenedioxythiophene) doped with poly(styrene sulfonic acid) nano-ribbon" Thin Solid Films **636**, 737 (2017).

- [21] J.H. Cho, J. Lee, Y. Xia, B. Kim, Y. He, M.J. Renn, T.P. Lodge and C.D. Frisbie, "Printable ion-gel gate dielectrics for low-voltage polymer thin-film transistors on plastic" Nat. Mat. 7, 900 (2008).

- [22] J.H. Cho, J. Lee, Y. He, B.S. Kim, T.P. Lodge and C.D. Frisbie, "High-Capacitance Ion Gel Gate Dielectrics with Faster Polarization Response Times for Organic Thin Film Transistors" Adv. Mater. 20, 686 (2008).

- [23] K.F. Mak, C. Lee, J. Hone, J. Shan and T.F. Heinz, "Atomically Thin MoS<sub>2</sub>: A New Direct-Gap Semiconductor" Phys. Rev. Lett. **105**, 136805 (2010).

- [24] J. Pu, Y. Yomogida, K.-K. liu, L.-J. Li, Y. Iwasa and T.Takenobu, "Highly Flexible MoS<sub>2</sub> Thin-Film Transistors with Ion Gel Dielectrics" Nano Lett. **12**, 4013 (2012).

- [25] S.M. Sze, "Physics of Semiconductor Devices" John Wiley & Sons, 2<sup>nd</sup> Ed. Ch. 2 (1981).

**Figure 1:** (a) Schematic of the p-Si/MoS<sub>2</sub> diode with external electrical connections. (b) Top view SEM image of the actual diode. The MoS<sub>2</sub> crystals lie on the top surface of the substrate, and several MoS<sub>2</sub> crystals are seen along the cleaved edge. Some MoS<sub>2</sub> crystals can also be seen along the cleaved surface, although blurry due to lack of focus. The white scale bar is 20 μm. (c) Raman spectrum of MoS<sub>2</sub> showing the characteristic peaks of monolayer crystals. (d) Top view low magnification image of (b) after an  $II_{gel}$  drop is placed at the location of the diode. The white scale bar is 500 μm.

**Figure 2:** Specific capacitance  $(C_i)$  of the ionic liquid gel  $(IL_{gel})$  as a function of frequency (f). Lower inset: Photograph of the  $Il_{gel}$  sandwiched between two parallel Au electrodes. Upper inset: Drain-source current  $(I_{DS})$  in a monolayer  $MoS_2$  field effect transistor as a function of top gate voltage  $(V_G)$ . The slope of the straight line was used to calculate the charge mobility  $(\mu)$ . The drain-source voltage  $(V_{DS})$  was fixed at 0.5V.

**Figure 3:** Current-voltage (I-V) curves of the *p*-Si/MoS<sub>2</sub> diode with no voltage applied to the IL<sub>gel</sub>. The blue and red curves represent two different external bias conditions as discussed in the text. **Lower Inset:** Energy band diagram of the *p*-Si/MoS<sub>2</sub> diode in thermal equilibrium. **E**<sub>g</sub> represents the energy band gap. The dotted line represents the Fermi energy, the energy level above and below the Fermi level correspond to the conduction and valence band respectively. The empty circles represent electrons while the filled circles represent holes. **Upper Inset:** Semi-logarithmic plot of the current vs. voltage curve under forward bias in the first quadrant. The slope of the straight line prior to diode turn-on was used to determine the ideality parameter.

**Figure 4:** I-V curves of the diode shown in Figure 1(b), where the gate voltage was changed from -1.4V to +1.4V in steps of 0.1V and plotted in two panels for clarity: (a)  $V_G$  changed from 0V to +1.4V, and (b)  $V_G$  changed from -1.4V to 0V at a few selected gate voltages as indicated near each curve. The complete run where  $V_G$  is changed from -1.4  $\rightarrow$  +1.4V  $\rightarrow$  -1.3V is shown in the supplementary section Figure S2(a) and (b). The insets represent the energy band diagram of the p-Si/MoS<sub>2</sub> diode under specific applied voltages as shown.

Figure 5: (a) Diode ideality parameter as a function of  $V_G$ . (b) Diode turn-on voltage as a function of  $V_G$ . (c) Diode on/off state currents measured at V = +/-2V respectively as a function of  $V_G$ .