LETTER

## Three-terminal magnetic tunnel junction synapse circuits showing spike-timing-dependent plasticity

To cite this article: Otitoaleke Akinola *et al* 2019 *J. Phys. D: Appl. Phys.* **52** 49LT01

View the [article online](#) for updates and enhancements.

**IOP** | **ebooks**<sup>TM</sup>

Bringing you innovative digital publishing with leading voices to create your essential collection of books in STEM research.

Start exploring the collection - download the first chapter of every title for free.

## Letter

# Three-terminal magnetic tunnel junction synapse circuits showing spike-timing-dependent plasticity

Otitoaleke Akinola<sup>1</sup> , Xuan Hu<sup>2</sup> , Christopher H Bennett<sup>3</sup> ,

Matthew Marinella<sup>3</sup>, Joseph S Friedman<sup>2</sup>  and Jean Anne C Incorvia<sup>1,4</sup>

<sup>1</sup> Electrical and Computer Engineering, University of Texas at Austin, Austin, TX,

United States of America

<sup>2</sup> Electrical and Computer Engineering, University of Texas at Dallas, Richardson, TX,

United States of America

<sup>3</sup> Sandia National Laboratory, Albuquerque, NM, United States of America

E-mail: [incorvia@austin.utexas.edu](mailto:incorvia@austin.utexas.edu)

Received 14 July 2019, revised 28 August 2019

Accepted for publication 4 September 2019

Published 23 September 2019

## Abstract

There have been recent efforts towards the development of biologically-inspired neuromorphic devices and architecture. Here, we show a synapse circuit that is designed to perform spike-timing-dependent plasticity which works with the leaky, integrate, and fire neuron in a neuromorphic computing architecture. The circuit consists of a three-terminal magnetic tunnel junction with a mobile domain wall between two low-pass filters and has been modeled in SPICE. The results show that the current flowing through the synapse is highly correlated to the timing delay between the pre-synaptic and post-synaptic neurons. Using micromagnetic simulations, we show that introducing notches along the length of the domain wall track pins the domain wall at each successive notch to properly respond to the timing between the input and output current pulses of the circuit, producing a multi-state resistance representing synaptic weights. We show in SPICE that a notch-free ideal magnetic device also shows spike-timing dependent plasticity in response to the circuit current. This work is key progress towards making more bio-realistic artificial synapses with multiple weights, which can be trained online with a promise of CMOS compatibility and energy efficiency.

Keywords: synapse, neuromorphic, magnetic tunnel junction, plasticity, domain wall

(Some figures may appear in colour only in the online journal)

## 1. Introduction

Dedicated architecture for artificial intelligence (AI) applications can overcome the limitations of the von Neumann architecture in accomplishing data-intensive tasks. Transistors are traditionally used as binary logic devices, whereas applications like perception, prediction, and decision making are

inherently non-binary tasks. The von Neumann architecture also faces a memory access bottleneck, as separation between the memory unit and the computing unit necessitates the frequent transfer of data between these two units, which results in significant delay and energy consumption [1, 2]. Due to these reasons, there has been a paradigm shift towards biologically-inspired neuromorphic computing which requires developing devices and circuits that approximate physical components of the nervous system, e.g. the neuron and synapse, and embody

<sup>4</sup> Author to whom any correspondence should be addressed.

dynamical operations such as learning and real-time adaptation (plasticity) [3].

Neurons are cells within the nervous system that receive signals from other neurons through their dendrites, perform non-linear processing on the signals in their soma, and transmit the output to the next set of neurons through their axon [4]. A synapse is a structure in the nervous system that allows a neuron to pass an electrical signal (electrical current) or a chemical signal (neurotransmitters) to another neuron or to a target effector cell [5]. Synaptic plasticity is believed to be a major contributor to memory and learning. In response to increases or decreases in specific patterns of a synapse's activity, the synapse strengthens or weakens over time. While plasticity is an ongoing topic of research in neuroscience, well-established hallmarks of plasticity operations include changes in the quantity of neurotransmitters, changes in the strength and number of receptors on the post-synaptic neuron, and changes in how rapidly the post-synaptic neuron responds to stimulation from the pre-synaptic neuron.

Spike-timing-dependent plasticity (STDP) has been identified as a key operation for learning and memory in the brain, as well as the basis for development and refinement of neural circuits during brain development. It is a biological process in which the strength of the synapse (synaptic weight) is correlated with the time differences between pre-synaptic neural signals and post-synaptic neural signals [6, 7]. This is commonly referred to as 'cells that fire together, wire together', [8] in which the synaptic connection between the neurons gets reinforced in the form of long-term potentiation (LTP) or weakened in the form of long-term depression (LTD).

Numerous types of emerging non-volatile memory devices are being studied as artificial neurons for low-power computing elements and synapses as adaptive memory elements [9]. So far, most research in this area has focused on technologies such as resistive random access memory (RRAM) [10, 11], phase change memory [9, 12], and conductive-bridge RAM (CBRAM) [13]. For example, complex plasticity effects have been physically demonstrated in CBRAM devices [14, 15] and used for nanodevice-powered learning architectures [16, 17]. Recently, there has been significant interest in fully implementing plasticity operations in magnetic random access memory (MRAM) systems based on magnetic tunnel junction (MTJ) devices. Magnetic devices have many properties similar to the neurons and synapses of the brain, such as low-energy [18] and stochastic switching [19], nonvolatility, and co-localized memory and logic [20]. Additionally, magnetic devices have been proposed to act as both synapses and neurons [21–24], providing a potential platform for monolithic neuromorphic circuits. MRAM cycle-to-cycle endurance is the highest among emerging resistive memories with over  $10^{15}$  cycles [25]; it is a particularly attractive device for building synapses, because the devices can handle the high activity factor necessary for online learning.

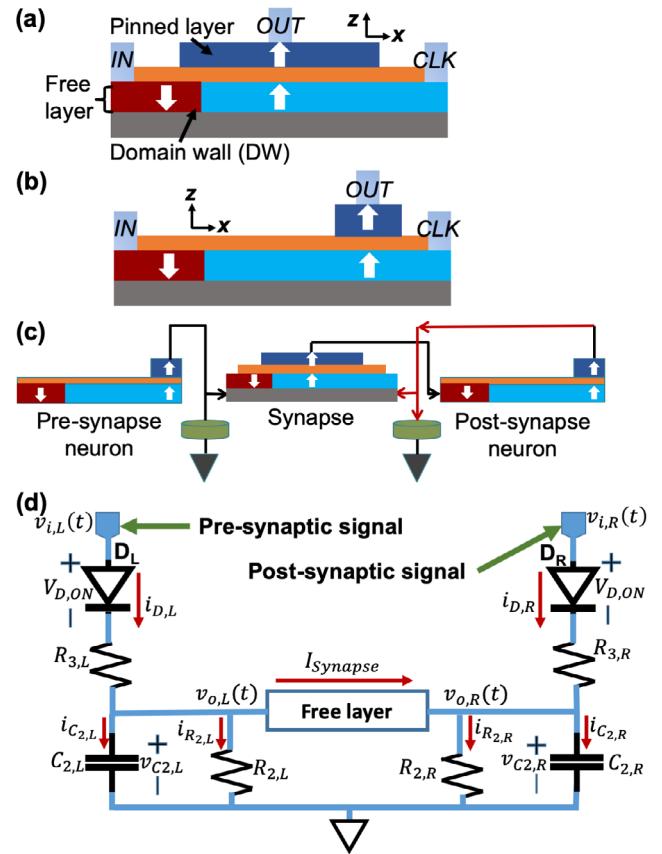

The three-terminal magnetic tunnel junction (3T-MTJ), shown in figure 1(a), is an MTJ device where the ferromagnetic free layer is separated from the ferromagnetic pinned layer by a tunneling oxide barrier and there are three terminals: two terminals on either side of the free layer (*IN* and *CLK*) and

**Figure 1.** (a) Side-view cartoon of the 3T-MTJ synapse device. The up/down arrows and blue/red color represent the magnetization vector of the ferromagnetic thin films; the orange represents the tunnel barrier. (b) Side-view cartoon of the corresponding 3T-MTJ neuron device we developed in [24]. (c) Cartoon showing the 3T-MTJ synapse integrated with the pre-synaptic neuron and post-synaptic neuron. The capacitors (green discs) are integral in timing coordination in order to move the DW. (d) The balanced synapse circuit schematic with the MTJ free layer modeled as a resistor.  $I_{Synapse}$  is the current that flows through the free layer of the MTJ and moves the DW, thereby adjusting the device weight in the form of tunneling resistance.

one terminal connecting to the top pinned layer (*OUT*). The free layer can be set up to have two oppositely magnetized regions separated by a domain wall (DW), as shown. In the synapse implementation, the pinned layer is kept long enough in  $\hat{x}$  such that the free layer magnetization can be manipulated via the DW to orient either fully parallel, antiparallel, or inbetween, relative to the magnetization of the pinned layer, which will result in multiple conductances through the center tunnel junction that can represent synaptic weights. The extra third terminal is to provide separate read/write control channels and separate control of the DW, compared to the two-terminal MTJs (2T-MTJs) in MRAM where the same channel is used as both read and write [26, 27]. Since MTJ breakdown most often happens at the tunnel barrier, separating the read and write can extend the device endurance even further for synapse applications, because during training minimal current flows through the tunnel barrier. The DW of the free layer can be displaced by spin transfer torque (STT) exerted on it by spin polarized current flowing through the free layer [28] or

by spin orbit torque (SOT) exerted by a charge current flowing through an underlying heavy metal (HM) [29–31].

The majority of the work on spintronic neuromorphic computing has focused on the implementation of neurons using 2T-MTJs [19, 22, 23, 32–34] while doing most of the synaptic weight training offline. Others have attempted to use 2T-MTJs as synapses which are limited to binary weights [35]. Some work has been done on using 3T-MTJs as neurons [26], including our recent work developing a leaky, integrate, and fire (LIF) neuron with inherent lateral inhibition [24, 36]. The 3T-MTJ LIF neuron, to contrast from the synapse, is shown in figure 1(b). A shorter (in  $\hat{x}$ ) pinned layer that is offset from the center of the free layer enables the DW motion to represent integration, and firing occurs once the DW passes the pinned layer.

Only a few efforts have used 3T-MTJs as synapses. One example is the use of a transistor circuit and a 3T-MTJ to show stochastic STDP in a binary synapse [37]. This, however, does not show a multi-state resistance or conductance weighting system that is similar to the biological synapse [38–40]. Another example is an all-spin neural network in which binary 3T-MTJ neurons are connected to binary 3T-MTJ synapses through transistor axons [26]. Although this still uses binary synapses and does not show LTP or LTD, it sought to use less CMOS-based devices, which can be beneficial for energy efficiency. However, that implementation does not allow for fine adjustments of the synaptic weights, which may be critical to implementing plasticity-based learning algorithms.

Here, we have designed and modeled a synapse circuit using 3T-MTJs that captures STDP and allows online learning. We show that there is a correlation between the current amplitude to switch the DW and the timing between the pre-synaptic signal and the post-synaptic signal, and that the response of the circuit mimics the biological neural model of potentiation and inhibition. We also show that lithographically-defined notches along the length of the DW track create controlled pinning of the DW location. This well-studied method for DW control [41–44] shows a semi-analog multiple weight state depending on the pre- and post-synaptic signals.

We first present the 3T-MTJ circuit that has been developed for STDP and provide details about its functionality. Then, we show results from the SPICE simulation of the circuit, followed by micromagnetic simulation results for current pulse timing from the circuit applied to a 3T-MTJ to achieve multiple weight states. Finally, we use a SPICE model of the 3T-MTJ that we have benchmarked against micromagnetics [45] to study the behavior of the full circuit including the current waveform and DW dynamics.

## 2. Methods

The model for the artificial synapse is shown in figure 1. To have the 3T-MTJ synapse, figure 1(a), show STDP behavior, we need the position of the DW, and therefore the resistance weight, to respond to the timing between spiking signals at both the *IN* and *CLK* terminals. What the DW position *does*

respond to is the sign of the current  $I_{Synapse}$  between the *IN* and *CLK* terminals, which if above the DW depinning current will move the DW right or left. Thus, to achieve STDP we design a circuit that converts the timing of the pre- and post- synaptic signals to a sign and magnitude change in  $I_{Synapse}$ . We keep the circuit small and as simple as possible so that it could be integrated into a dense array of the 3T-MTJ synapses with a small area overhead.

Figure 1(c) depicts the circuit, consisting of a 3T-MTJ sandwiched between two capacitor–resistor–diode networks (green disks) through which it is connected to the pre- and post-synaptic 3T-MTJ neurons. The pre-synaptic signal comes from the output of the pre-synaptic neuron; the post-synaptic signal comes from the output of the post-synaptic neuron; and the output of the synapse goes into the input of the post-synaptic neuron. Here, we focus on the synapse behavior; the details of how the neurons and synapses connect are not specified.

The details of the circuit are shown in figure 1(d). It includes minimal additional resistors and capacitors to enable STDP that could be integrated into a crossbar array. We have modeled the free layer in case of an STT device (or HM in case of an SOT device) as a patterned thin film resistance  $R_{Synapse}$  in the balanced RC circuit. The center MTJ resistance of the device is not included. Diodes are placed on both ends of the circuit to prevent back current flow. The capacitor to the left of the 3T-MTJ ( $C_{2,L}$ ) and the capacitor to the right ( $C_{2,R}$ ) have equal capacitances. The left resistor ( $R_{2,L}$ ) and right resistor ( $R_{2,R}$ ) are equal resistances. ( $R_{3,L}$ ) and ( $R_{3,R}$ ) are the sum of a resistor and the contact resistance to the left and the right of the 3T-MTJ, respectively. The dynamics of the circuit depend on the arrival times of the pre-synaptic neuron signal (voltage amplitude  $v_{i,L}(t)$ ) and the post-synaptic neuron signal (voltage amplitude  $v_{i,R}(t)$ ), the states of the diodes  $D_L$  and  $D_R$ , and the time constants of the RC networks  $R_{2,L}C_{2,L}$  and  $R_{2,R}C_{2,R}$ . These states affect the direction of flow of  $I_{Synapse}$  which will increase or decrease the conductance of the MTJ through STT or SOT switching of a DW in the free layer. The current  $i$  is labeled throughout the circuit.

For either of the diodes to be on, the input signals from the pre-synaptic or post-synaptic neurons must be such that

$$v_{i,R}(t) - v_{o,R} - i_{D,R}R_{3,R} \geq V_{D,ON} \quad (1)$$

$$v_{i,L}(t) - v_{o,L} - i_{D,L}R_{3,L} \geq V_{D,ON}. \quad (2)$$

When both diodes  $D_L$  and  $D_R$  turn on at the same time, the pre-synaptic and post-synaptic signals arrive at the same time, and assuming the voltages at the capacitors  $C_{2,L}$  and  $C_{2,R}$  are at the same value, no current flows through the free layer, i.e.

$$I_{Synapse} = 0; i_{D,L} = i_{D,R} \geq 0, v_{i,L}(t) = v_{i,R}(t). \quad (3)$$

For other conditions (when both diodes are on), the complete set of parametric equations for the circuit can be written from nodal analysis as

$$v_{i,L}(t) - v_{o,L} - i_{D,L}R_{3,L} = V_{D,ON} \quad (4)$$

$$v_{i,R}(t) - v_{o,R} - i_{D,R}R_{3,R} = V_{D,ON} \quad (5)$$

$$i_{D,L} = i_{C_{2,L}} + \frac{v_{o,L} - v_{o,R}}{R_{synapse}} + \frac{v_{o,L}}{R_{2,L}} \quad (6)$$

$$i_{D,R} = i_{C_{2,R}} - \frac{v_{o,L} - v_{o,R}}{R_{synapse}} + \frac{v_{o,R}}{R_{2,R}} \quad (7)$$

$$i_{C_{2,L}} = C_{2,L} \frac{dv_{o,L}}{dt} \quad (8)$$

$$i_{C_{2,R}} = C_{2,R} \frac{dv_{o,R}}{dt}. \quad (9)$$

Using Laplace transforms, we write the input voltages as

$$v_{i,L}(s) = V_{iL} * \left( \frac{1 - \exp(-s * t_{pw})}{s * (1 - \exp(-t_p * s))} \right) \quad (10)$$

$$v_{i,R}(s) = V_{iR} * \left( \frac{\exp(-s * t_d) - \exp(-s * (t_d + t_{pw}))}{s * (1 - \exp(-t_p * s))} \right) \quad (11)$$

where  $s$  is the Laplace frequency variable,  $V_{iL}$  and  $V_{iR}$  are the pre- and post-synaptic signal amplitudes, respectively,  $t_{pw}$  is the pulse width,  $t_d$  is the delay between the pre-synaptic signal and the post-synaptic signal, and  $t_p$  is the period of both the pre-synaptic and post-synaptic signals. The current through the MTJ synapse can then be derived as:

$$I_{Synapse} = \frac{v_{o,L} - v_{o,R}}{R_{synapse}}. \quad (12)$$

When both diodes  $D_L$  and  $D_R$  are off and assuming they turn off after a cycle of the circuit at about the same time at  $t > 0$ , the current flowing through the free layer will be a function of the difference of the voltages of  $C_{2,L}$  and  $C_{2,R}$ . And given that  $C_{2,L} = C_{2,R} = C_2$  and  $R_{2,L} = R_{2,R} = R_2$ ,  $I_{Synapse}$  can be written as:

$$I_{Synapse} = \exp \left( -\frac{t * (2 * R_2 + R_{synapse})}{C_2 * R_2 * R_{synapse}} \right) * (v_{C2,L}(t) - v_{C2,R}(t)) \quad (13)$$

where  $v_{C2,L}(t)$  and  $v_{C2,R}(t)$  are the voltages of capacitors  $C_{2,L}$  and  $C_{2,R}$ , respectively, at time  $t > 0$  when both diodes are off.

### 3. Results and discussion

#### 3.1. Circuit simulation results

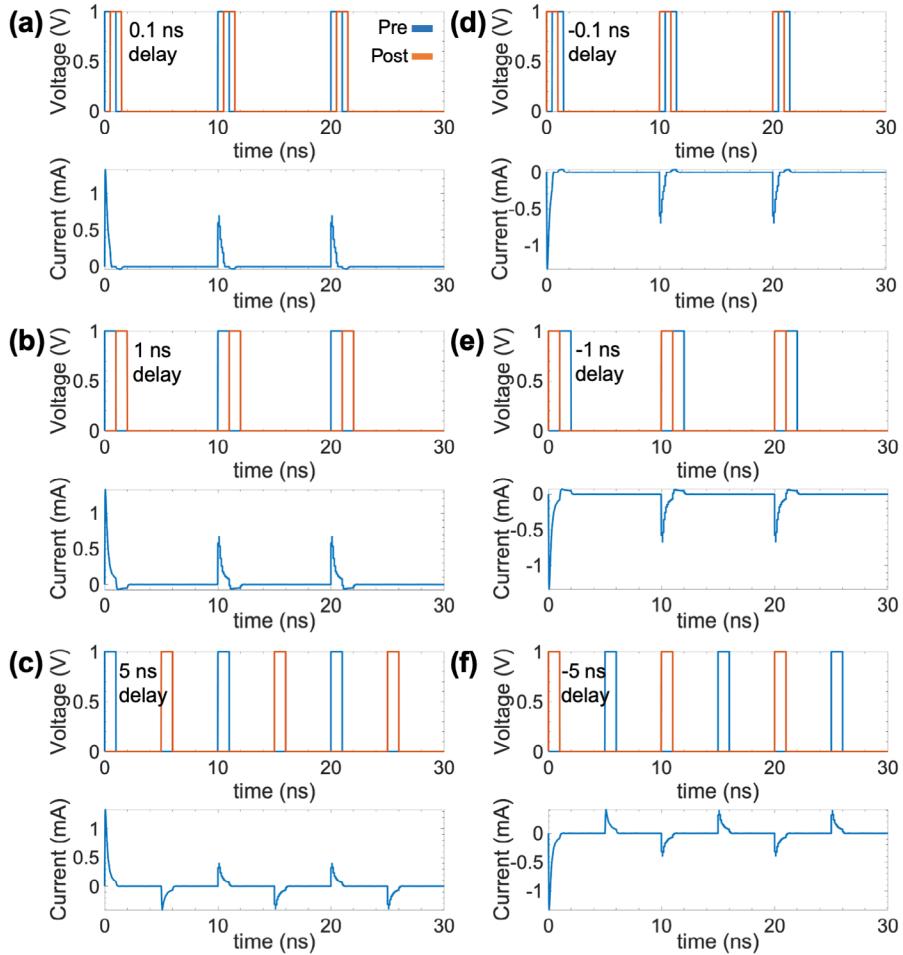

The 3T-MTJ synapse circuit is simulated in HSpice with varying delay conditions from 0.1 ns to 5 ns between onset of the pre-synaptic neuron signal  $v_{i,L}(t)$  and post-synaptic neuron signal  $v_{i,R}(t)$ . The signal pulse widths are 1 ns with a 10 ns period, and we use  $R_{2,L} = R_{2,R} = R_2 = 10 \text{ k}\Omega$ ,  $R_{Synapse}$  (resistance of the free layer) = 100  $\Omega$ ,  $R_{3,L} = R_{3,R} = R_3 = 50 \text{ }\Omega$ , and  $C_{2,L} = C_{2,R} = C_2 = 1 \times 10^{-12} \text{ F}$ . Figure 2 shows the results of the HSpice simulation, where we plot both the transient voltage pulses and current through the free layer,  $I_{Synapse}$ . It can be seen from figures 2(a) and (b) that when  $v_{i,L}(t)$  arrives before  $v_{i,R}(t)$ , a positive current flows through the 3T-MTJ synapse, which will increase the conductance of the MTJ stack. The dynamics of the circuit depend on which signal arrives first. The circuit acts as a two-port peak detector,

with RC networks on both sides of the free layer. If  $v_{i,L}(t)$  arrives before  $v_{i,R}(t)$ , then the voltage  $v_{C2,R}$  of the capacitor  $C_{2,R}$  on the post-synaptic end, which has been stored up from the previous period, is almost fully discharged. This results in a larger voltage difference across the free layer and higher current amplitude. Conversely, if within the same period there is a greater delay between the two signals, the capacitor on the post-synaptic side will still be holding some voltage stored from the previous period, resulting in a reduced voltage difference and less current. Hence, the magnitude of the current is inversely proportional to the delay between  $v_{i,L}(t)$  and  $v_{i,R}(t)$ .

Figures 2(d) and (e) show that if the post-synaptic neuron fires before the pre-synaptic neuron, there is a negative (depressing) current through the synapse, and its magnitude is also dependent on the delay between the signals. Then there are the cases shown in figures 2(c) and (f) in which the pre-synaptic neuron fires midway between the span of the post-synaptic neuron firing twice in the first case; and the post-synaptic neuron fires midway between the span of the pre-synaptic neuron firing twice in the second case. In both cases there are equal magnitudes of both positive and negative current spikes flowing through the synapse. This can lead to oscillation of the output MTJ resistance. It should be noted that in all the simulations there is an initial larger current spike, which is an artifact of the circuit starting at time  $t = 0$ .

To compare with the behavior of biological synapses, the current that passes through a chemical synaptic channel,  $I_{syn,bio}(t)$ , can be represented by [4, 46]

$$I_{syn,bio}(t) = g_{syn}(t)(u(t) - E_{syn}) \quad (14)$$

which depends on the difference between its reversal potential  $E_{syn}$  and the actual value of the membrane potential,  $u(t)$ .  $g_{syn}(t)$  is a superposition of synaptic conductances  $\bar{g}_{syn}$  with exponential decay of time constant  $\tau$  and given by

$$g_{syn}(t) = \sum_f \bar{g}_{syn} e^{-\frac{t-t^f}{\tau}} \Theta(t - t^f) \quad (15)$$

where  $t^f$  is the arrival time of a pre-synaptic action potential and  $\Theta(t - t^f)$  is a Heaviside step function.  $g_{syn}(t)$  can be simplified for a single neuron-to-neuron synaptic connection by the alpha-function [46]

$$g_{syn}(t) = \frac{t}{\tau_s} e^{-\frac{t}{\tau_s}} \quad (16)$$

where  $\tau_s$  is the time constant of the response which specifies slow or fast transmission.

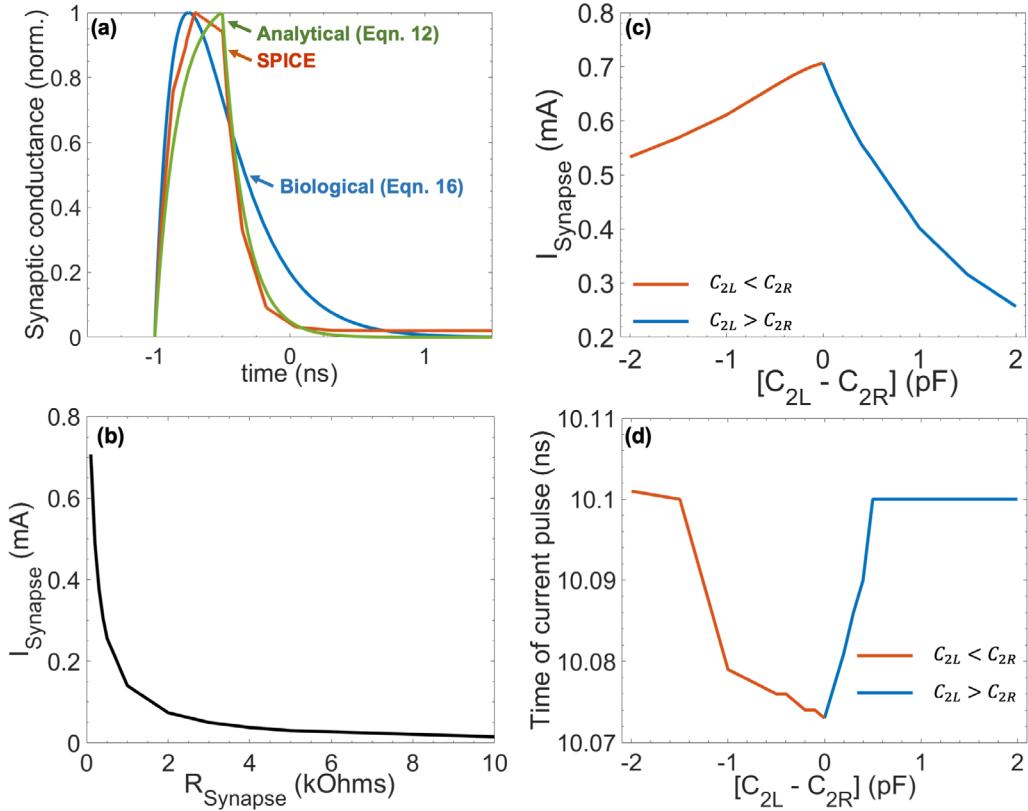

In figure 3(a), we plot  $I_{Synapse}(t)$  from the HSpice simulation for the figure 2(a) condition ('SPICE'), compared to the analytical solution equation (12), using parameters from equations (4)–(11) ('Analytical'), with  $t_{pw} = 1 \text{ ns}$ ,  $t_d = 0.2 \text{ ns}$ ,  $t_p = 10 \text{ ns}$ ,  $R_2 = 10 \text{ k}\Omega$ ,  $R_{Synapse} = 100 \text{ }\Omega$ ,  $R_3 = 50 \text{ }\Omega$ , and  $C_2 = 1 \times 10^{-12} \text{ F}$ . We also compare to the biological synapse transient current behavior using  $\tau_s = 0.1 \text{ ns}$  ('Biological'). The plots are normalized to their maximum values. It can be seen that we closely capture the biological transient behavior with the circuit, which agrees well with simulations, mathematical modeling, and analysis of biological neurons [46–54].

**Figure 2.** Spice simulation results for different delay scenarios between the pre-synaptic neuron signal and post-synaptic neuron signal. (a)–(c) The currents (lower plots) that flow through the free layer when the pre-synaptic neuron fires 0.5 ns, 1 ns, and 5 ns, respectively, before the post-synaptic neuron fires. (d)–(f) The currents (lower plots) that flow through the free layer when the pre-synaptic neuron fires 0.5 ns, 1 ns, and 5 ns, respectively, after the post-synaptic neuron fires. Both the pre- and post-synaptic firing are represented by voltage pulses of 10 ns period and 10% duty cycle as shown in the upper plots.

It can also be seen that the RC networks on both sides of the free layer also act as a low pass filter modeled in glutamate channels with N-methyl-D-aspartate receptors [4].

Figure 3(b) shows the  $I_{\text{Synapse}}(t)$  dependence on  $R_{\text{Synapse}}$ . As the resistance increases, the current decreases exponentially. This provides a design requirement for the 3T-MTJ device to keep the resistance of the bottom layers under 1–2 k $\Omega$  to have enough current to drive a DW in the free layer. This resistance value is a reasonable requirement for 3T-MTJ devices (e.g. in [20]  $R_{\text{Synapse}} = 1.2$  k $\Omega$ ), and it can be tuned by choosing the material and geometry of the bottom layers. The resistance needed depends on the required current for depinning the DW for a given device size and materials.

To calculate how much the circuit can tolerate imperfections between the matched capacitors, in figure 3(c) we plot  $I_{\text{Synapse}}$  while increasing the difference between the capacitance of  $C_{2L}$  and  $C_{2R}$  up to a factor of three mismatch. The figure shows the circuit is more tolerant of  $C_{2R} > C_{2L}$  with a 3  $\times$  mismatch producing a 25% change in  $I_{\text{Synapse}}$ . For  $C_{2R} < C_{2L}$ , the 3  $\times$  mismatch reduces the synapse current

by a larger factor up to 64%. This analysis assumes the pre-synaptic signal  $v_{i,L}$  leads the post-synaptic signal  $v_{i,R}$  by 0.1 ns. It is expected that the graph will be similar but flipped along the y-axis if the pre-synaptic signal lags the post-synaptic signal by the same amount of time (0.1 ns).

To investigate how the response time of the current through the 3T-MTJ free layer to the pre- and post-synaptic signals varies with the capacitance mismatch on either side of the MTJ, we took the onset time for signal  $I_{\text{Synapse}}$  on the second period, using a period of 10 ns and plotted it against the capacitance mismatch. The second period was used rather than the first period because of the artifact that comes with starting the simulation at  $t = 0$ . Figure 3(d) shows the timing of the current through the synapse is tolerant to capacitance mismatches with little or no difference in the current timing as the capacitance mismatch gets larger. The current pulse comes quicker on the average if  $C_{2R}$  is increased with respect to  $C_{2L}$  and saturates as the difference approaches  $-2$  pF. The reason for the small 0.3% dip in timing shown in figure 3(d) is not yet fully understood.

**Figure 3.** (a) Comparison of the transient synaptic current from the SPICE circuit to the analytical expression of the circuit from equation (12) and the biological synapse alpha-function from equation (16). The plots have been normalized to their maximum values. (b) Plot of current at the synapse versus resistance of the 3T-MTJ free layer. (c) Plot of current at the synapse and (d) current pulse timing versus difference in capacitance of the two capacitors in the circuit; orange traces correspond to  $C_{2L} < C_{2R}$  and blue traces correspond to  $C_{2L} > C_{2R}$ .

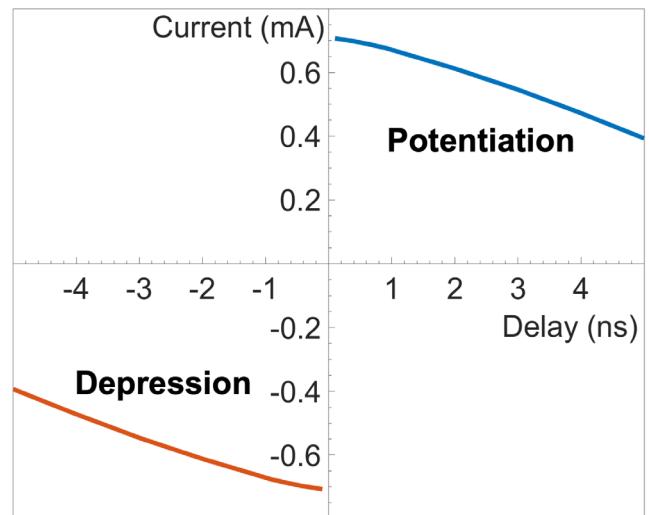

### 3.2. Spike-timing-dependent plasticity (STDP)

Taking the different current magnitudes flowing through the synapse at different timing conditions, we graph the current magnitude against time delay between the pre-synaptic neuron signal and the post-synaptic neuron signal. The plot is shown in figure 4. It is seen that the smaller the delay, the higher the current magnitude that flows through the synapse. Thus, the circuit captures both potentiation and depression, and also captures that the amplitude of the strengthening or weakening of the synapse is based on the timing between the pre- and post- signals. This has a high resemblance to the work of Bi and Poo's clinical experiment on STDP which shows LTP and LTD induced in synapses between hippocampal glutamatergic neurons [55]. Additionally, when the circuit has no correlation between the two signals, we get oscillation in time back and forth between two resistance states, maintaining the state of the synapse conductance.

### 3.3. Micromagnetic simulations

To observe how the circuit will affect the magnetic behavior of the 3T-MTJ synapse, we run the HSpice model and input the *vector direction* of the resulting  $I_{\text{Synapse}}$  into a micromagnetic simulation using MuMax3 [56] and rendered in OOMMF [57]. While 3T-MTJs have been modeled as a synapse in perfect wires [19, 26, 35, 58–61], it is a challenge in

**Figure 4.** Potentiation and depression currents from the SPICE simulation as a function of spiking delay between pre-synaptic and post-synaptic neurons.

a real device to repeatably control the distance of the DW along the free layer racetrack under the MTJ. One solution, implemented here, is to use lithographically defined notches, which are anisotropy barriers that pin the DW. We model a 1  $\mu\text{m}$  long  $\times$  32 nm wide  $\times$  4 nm thick CoFeB free layer with a discretization cell size of 1 nm  $\times$  1 nm  $\times$  1 nm, perpendicular

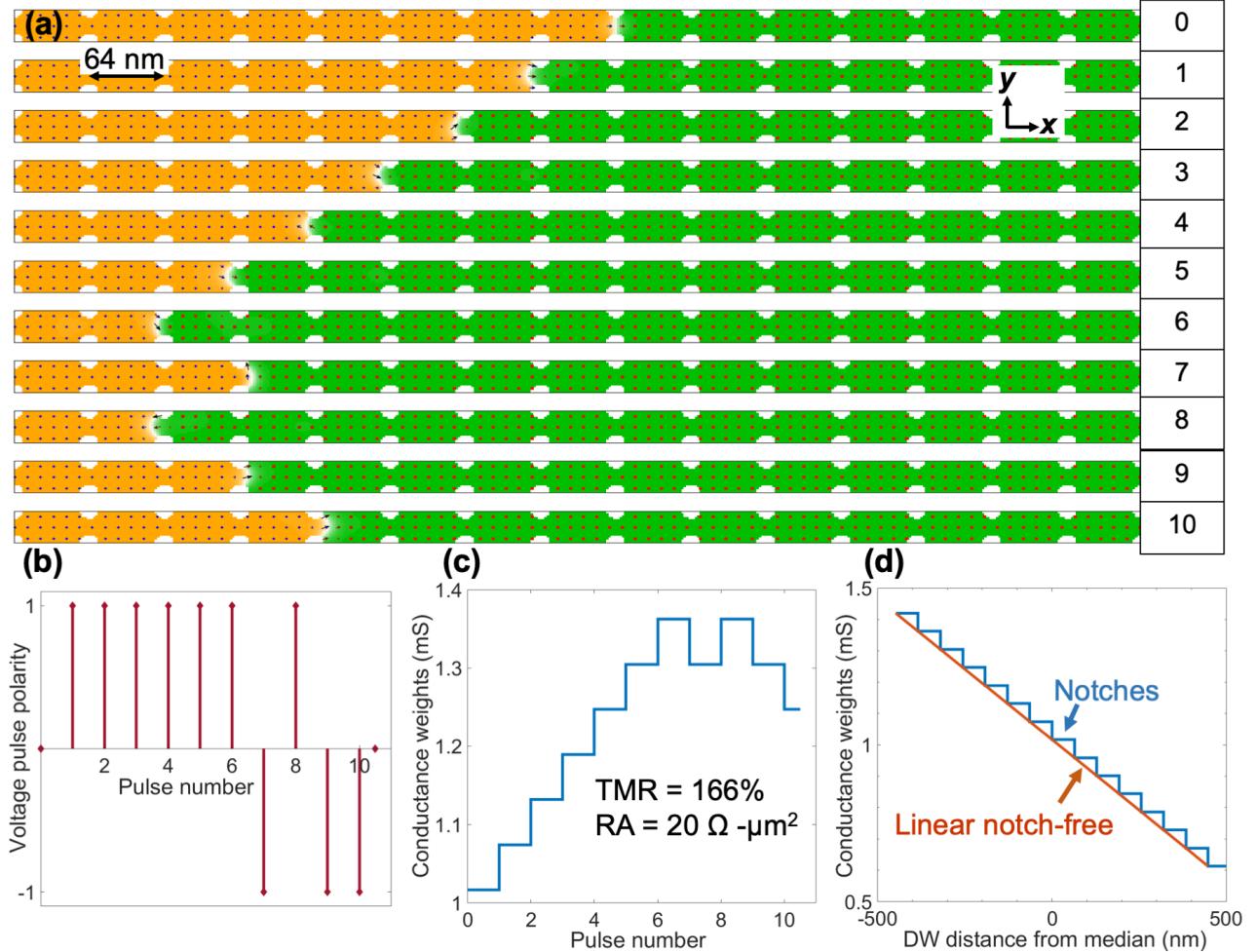

**Figure 5.** (a) Micromagnetic simulation snapshots for the current pulse train shown in (b) through a 1  $\mu\text{m}$  long  $\times$  32 nm wide  $\times$  4 nm thick CoFeB free layer. The notches introduce anisotropies which pin the DW. (c) Plot of the resulting conductance weights versus pulse number, assuming that the green-colored (right) domain is parallel to the pinned layer and the orange-colored (left) domain is anti-parallel to the pinned layer. (d) Calculated conductance of the MTJ versus DW position at each notch in the free layer (blue curve) compared to a linear fit to the conductance change assuming no DW pinning (orange).

magnetic anisotropy of  $1.5 \times 10^6 \text{ J m}^{-3}$ , exchange stiffness of  $13 \times 10^{-12} \text{ J m}^{-1}$ , damping constant of 0.02, saturation magnetization of  $1.44 \times 10^6 \text{ A m}^{-1}$ , and non-adiabatic constant of 0.02. The notches are 16 nm in diameter with a pitch of 64 nm. Using STT, we use 1 ns pulses of current density  $2 \times 10^{12} \text{ A m}^{-2}$ , where the direction of the current depends on the relative timing of the pre- and post-synaptic neurons from the circuit model. The current density was chosen such that the current across the synapse is the same order of magnitude as the peak transient current in the circuit model. The pulses have a period of 10 ns.

The results of the micromagnetic simulation are shown in figure 5(a) as snapshots of the wire magnetization after the DW motion has stopped after each current pulse (view is  $-\hat{z}$  compared to figure 1(a)). At the initial state 0 the DW is in the center of the free layer. Figure 5(b) depicts the polarity of the ten current pulses applied sequentially across the free layer.

We see that each current pulse moves the DW left or right depending on the timing delay between the pre- and post- signals. Thus, with a long MTJ placed on top of the free layer (not shown), this will controllably increase or decrease the

MTJ conductance, setting the synaptic weight. It can be seen that each positive current pulse moves the DW to the left, getting pinned at subsequent notches, while each negative current pulse moves the DW to the right, also getting pinned at subsequent notches. Positive current pulses reduce the tunneling resistance of the device and hence increase the weight of the synapse while negative current pulses do the contrary.

In figures 5(c) and (d) we use measured numbers for CoFeB MTJs fabricated in our group of 166% tunnel magnetoresistance and  $20 \Omega \cdot \mu\text{m}^2$  resistance-area (RA) product to convert the DW position to expected conductance weight. Figure 5(c) shows the expected conductance for each corresponding DW position in figure 5(a). Figure 5(d) shows the expected MTJ resistance when the DW sits at each notch (blue curve), compared to a linear fit if no notches are present (orange curve). Because the DW can be pinned at a particular notch for a long time if there is no current flowing, this gives the synapse a long-term memory effect. Also because the position of the DW along the free layer is a resultant effect of potentiation and depression over time, we can safely say that the synapse undergoes LTP and LTD.

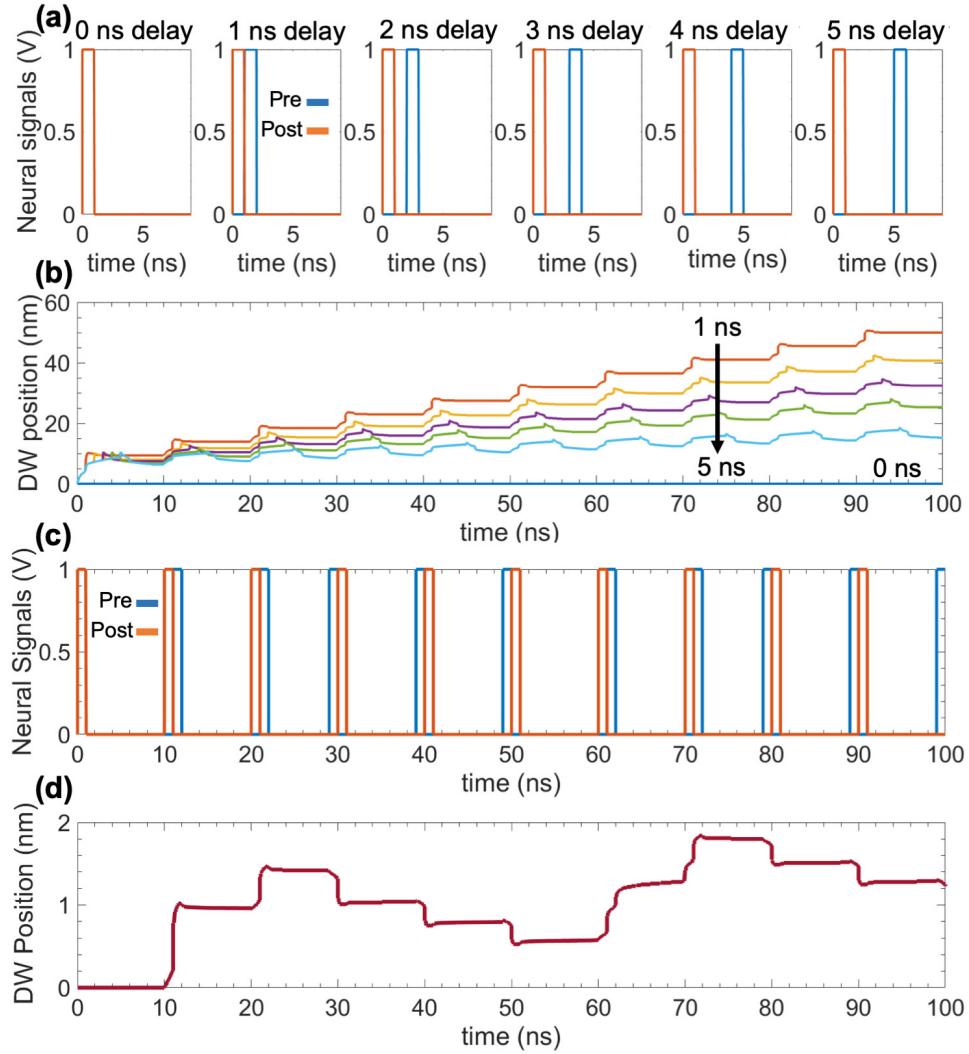

**Figure 6.** (a) Six modeled delay conditions between the pre- and post-synaptic signals, each simulated for ten cycles of 10 ns. (b) DW position output over time from the full SPICE model for the conditions in (a). Here the DW was initiated at the leftmost end of the free layer. (c) Modeled random train of delay conditions between the pre- and post-synaptic signals, with lead and lag times of 1 ns. (d) DW position output over time from the full SPICE model for the conditions in (c), showing the DW position, and therefore synaptic weight, is controlled by the timing between the signals.

The length of the MTJ compared to the length of the DW in  $\hat{x}$  determines the number of notches and hence the number of DW positions that can represent different resistance or conductance weights. In a free layer with perpendicular magnetic anisotropy, the length of the DW  $L_{\text{DW}}$  is approximately determined by the width in  $\hat{y}$  of the free layer, which is equal to the width of the MTJ,  $w_{\text{MTJ}}$ , as  $L_{\text{DW}} \approx \frac{w_{\text{MTJ}}}{4}$  [62]. This means that with a MTJ of length  $L_{\text{MTJ}}$ , the maximum number of weights ( $n_{\text{weights}}$ ) achievable will be given by the relation

$$n_{\text{weights}} \leq (L_{\text{MTJ}}/L_{\text{DW}}) \approx 4 \times L_{\text{MTJ}}/w_{\text{MTJ}}. \quad (17)$$

Depending on the number of weights needed, the length of the free layer could be shortened to create more compact circuits. The notch depth and period was chosen empirically for given materials parameters to catch the DW after each pulse [63, 64].

It should be noted that the short pulse width of 1 ns used here mitigates heating effects from the higher current density [65] and hence ensures uniform predictable behavior of the

synapse circuit. For short current pulses between 1–10 ns, the thermal diffusion length is 0.1–1  $\mu\text{m}$ , larger than the free layer thickness of 4 nm; thus, we predict Joule heating will have little effect on the DW motion [65, 66].

#### 3.4. Full SPICE simulation including domain wall dynamics

In sections 3.1–3.2, for the SPICE circuit model we used a resistor to represent the 3T-MTJ free layer. In section 3.3, to observe the effect of the circuit on the micromagnetic behavior of the 3T-MTJ synapse, we input the resulting current polarity from the circuit as a 1 ns current pulse of a fixed amplitude. Here, to capture the full dynamics of the circuit signal waveform (e.g. figure 3(a)) on the 3T-MTJ magnetic response, we implement a SPICE-only model of the full circuit that includes DW dynamics. We use a model of the 3T-MTJ for a notch-free free layer that we have previously developed with Verilog A and is benchmarked against micromagnetic simulations [45]. The 3T-MTJ model is connected via the *IN* and *CLK* terminals

**Table 1.** Head-to-head comparison of critical parameters for nanodevice and CMOS co-integrated unit cells for providing analog STDP learning (we do not consider here the comparison to probabilistic or binary schemes).

|                           | CBRAM [67]                     | Metal oxide<br>(Al <sub>2</sub> O <sub>3</sub> /TiO <sub>2-x</sub> )<br>[68] | Metal oxide<br>(BiFeO <sub>3</sub> ) [69] | Polymer<br>(PEDOT:PSS)/Ta [70] | 2T-MTJ [37]       | 3T-MTJ<br>(our approach)     |

|---------------------------|--------------------------------|------------------------------------------------------------------------------|-------------------------------------------|--------------------------------|-------------------|------------------------------|

| $R_{Synapse}$             | 5–50 kΩ                        | 10–40 kΩ                                                                     | ~1 MΩ                                     | 1–2.5 kΩ                       | 400 Ω             | 100 Ω–10 kΩ                  |

| Switching time            | 2–4 μs                         | 20 ms                                                                        | 125 μs                                    | 50 ms                          | <5 ns             | <5 ns                        |

| $V_{post/pre}$            | ±1.3 V                         | ±0.6–1.0 V                                                                   | 3.0 V+                                    | ±2.0 V                         | 1.0 V             | 1.0 V                        |

| Analog STDP<br>resolution | Intermediate<br>(~5–10 states) | High (>20<br>states)                                                         | Intermediate<br>(~10 states)              | High (>30 states)              | Low (2<br>states) | Intermediate (~10<br>states) |

to the circuit, replacing the free layer resistor in the figure 1(d) circuit schematic.

With the same capacitance and resistance values ( $R_{2,L} = R_{2,R} = R_2 = 10$  kΩ and  $C_{2,L} = C_{2,R} = C_2 = 1 \times 10^{-12}$  F) used for the simulation in figure 2, we simulate ten cycles of six constant delay conditions between onset of the pre-synaptic signal and onset of post-synaptic signal. The six delay conditions are shown in figure 6(a). The transient DW position is shown in figure 6(b). With 0 ns delay, the DW does not move. The DW responds to each spiking of the circuit by moving an incremental distance across the free layer, and it is evident that the shorter the non-zero delay, the farther the DW moves after each firing and over the ten cycles, showing STDP behavior.

In figure 6(c), we randomly vary the timing of the pre- and post-synaptic signals with 1 ns lead or lag between the signals. Figure 6(d) shows that in response to this pulse train the DW moves left or right depending on the polarity of the resulting current spikes across the 3T-MTJ free layer. These results show that including the precise waveform of the circuit corroborates the micromagnetic results. We do see some irregularities in how far and how smoothly the DW moves in response to multiple similarly-timed pulses, which shows that external pinning may be important for controlling the conductance weights.

### 3.5. Benchmarking against competing STDP implementations

The results of our micromagnetic and SPICE simulations allow us to make a comparison to other state-of-the-art proposals for nanodevice platforms for implementing online STDP learning. Specifically, we consider how our analog STDP implementation using 3T-MTJ devices compares to physically realized or proposed analog STDP building block cells using 2T-MTJs [37], CBRAM [67], metal oxide [68, 69], or polymeric [70] active switching layers. As visible in table 1, the signature advantage of our system is its extreme (nano-second range) STDP time window; the second fastest device, a CBRAM option, is over two orders of magnitude slower, and the other listed nanodevice options are slower still. Since this window serves as a speed limit for overall STDP learning, this could finally allow for online STDP learning functions in an integrated circuit co-integrated with NVM devices in an industrially-relevant context. Our proposal compares favorably in terms of required voltage, and is comparable though

not superior in terms of analog resolution provided by other nanodevices. Our proposal's major weak point relative to competing options is the relatively low resistance and on/off ratio provided by MTJ devices. However, this issue may be ameliorated by further device engineering.

## 4. Conclusions

We have successfully designed a 3T-MTJ synapse circuit that achieves STDP, LTP, and LTD, essential characteristics of biologically-inspired artificial synapses. We observe that the transient form of the current generated across the synapse corresponds to what is seen in biology, and that shorter delay between the pre- and post- neuron firing results in higher current for potentiation or depression, which shows high similarity to biological neuron behavior. We show that the circuit can achieve a semi-analog pinning of the DW along the length of the ferromagnetic free layer of a 3T-MTJ using notches, and that the DW position can be set using the concept of STDP when integrated with the circuit. Including a SPICE model for the 3T-MTJ, we see the DW responds to the transient current with LTP and LTD behavior. This is key progress towards making more bio-realistic artificial synapses with multiple weights, which can also be trained online with a promise of CMOS compatibility and energy efficiency. Future work is needed to understand the impact of the additional circuitry for STDP on scaling and circuit density. The results shown can be in the future integrated with the LIF neuron in a crossbar array fashion and used for online machine learning applications in tasks like pattern or speech recognition.

## Acknowledgments

The authors acknowledge discussions and funding from Sandia National Laboratories, managed and operated by NTESS under DOE NNSA contract DE-NA0003525, and computing resources from the Texas Advanced Computing Center (TACC) at the University of Texas at Austin ([www.tacc.utexas.edu](http://www.tacc.utexas.edu)). M Marinella and C H Bennett acknowledge support from Sandia's Laboratory-Directed Research and Development program. This paper describes objective technical results and analysis. Any subjective views or opinions that might be expressed in the paper do not necessarily represent the views of the US Department of Energy or the United States Government. Sandia National Laboratories is

a multimission laboratory managed and operated by National Technology Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International Inc., for the US Department of Energy's National Nuclear Security Administration under contract DE-NA0003525.

## ORCID iDs

Otitoaleke Akinola  <https://orcid.org/0000-0002-2505-5847>

Xuan Hu  <https://orcid.org/0000-0002-7337-6637>

Christopher H Bennett  <https://orcid.org/0000-0002-6989-292X>

Joseph S Friedman  <https://orcid.org/0000-0001-9847-4455>

Jean Anne C Incorvia  <https://orcid.org/0000-0002-4805-2112>

## References

[1] Fukami S and Ohno H 2018 Perspective: spintronic synapse for artificial neural network *J. Appl. Phys.* **124** 151904

[2] Hsu J 2014 IBM's new brain [News] *IEEE Spectrosc.* **51** 17–9

[3] Abbott L F and Regehr W G 2004 Synaptic computation *Nature* **431** 796–803

[4] Gerstner W, Kistler W M, Naud R and Paninski L 2014 *Neuronal Dynamics: From Single Neurons to Networks and Models of Cognition* (Cambridge: Cambridge University Press)

[5] Foster M and Sherrington C S 1897 *Textbook of Physiology, Part 3* (London: Macmillan)

[6] Hebb D O 1949 *The Organization of Behavior: A Neuropsychological Theory* (New York: Wiley)

[7] Konorski J 1948 *Conditioned Reflexes and Neuron Organization* (New York: Cambridge University Press)

[8] Shatz C J 1992 The developing brain *Sci. Am.* **267** 60–7

[9] Burr G W *et al* 2017 Neuromorphic computing using non-volatile memory *Adv. Phys. X* **2** 89–124

[10] Park S, Sheri A, Kim J, Noh J, Jang J, Jeon M, Lee B, Lee B R, Lee B H and Hwang H 2013 Neuromorphic speech systems using advanced ReRAM-based synapse *Technical Digest—Int. Electron Devices Meeting IEDM* pp 625–8 (<https://doi.org/10.1109/IEDM.2013.6724692>)

[11] Lee M J *et al* 2018 Reliable multivalued conductance states in  $TaO_x$  memristors through oxygen plasma-assisted electrode deposition with *in situ*-biased conductance state transmission electron microscopy analysis *ACS Appl. Mater. Interfaces* **10** 29757–65

[12] Suri M, Bichler O, Querlioz D, Cueto O, Perniola L, Sousa V, Vuillaume D, Gamrat C and DeSalvo B 2011 Phase change memory as synapse for ultra-dense neuromorphic systems: application to complex visual pattern extraction *2011 Int. Electron Devices Meeting* pp 4.4.1–4 (<https://doi.org/10.1109/IEDM.2011.6131488>)

[13] Kwon M-W, Kim S, Kim M-H, Park J, Kim H, Hwang S and Park B-G 2017 Integrate-and-fire (I&F) neuron circuit using resistive-switching random access memory (RRAM) *J. Nanosci. Nanotechnol.* **17** 3038–41

[14] Chang T, Jo S H and Lu W 2011 Short-term memory to long-term memory transition in a nanoscale memristor *ACS Nano* **5** 7669–76

[15] La Barbera S, Vuillaume D and Alibert F 2015 Filamentary switching: synaptic plasticity through device volatility *ACS Nano* **9** 941–9

[16] Bennett C H, La Barbera S, Vincent A F, Klein J O, Alibert F and Querlioz D 2016 Exploiting the short-term to long-term plasticity transition in memristive nanodevice learning architectures *Proc. Int. Joint Conf. on Neural Networks* pp 947–54

[17] Du C, Cai F, Zidan M A, Ma W, Lee S H and Lu W D 2017 Reservoir computing using dynamic memristors for temporal information processing *Nat. Commun.* **8** 2204

[18] Nikonorov D E and Young I A 2015 Benchmarking of beyond-cmos exploratory devices for logic integrated circuits *IEEE J. Explor. Solid-State Comput. Devices Circuits* **1** 3–11

[19] Zhang D, Zeng L, Qu Y, Zhang Y, Wang M, Zhao W, Tang T and Wang Y 2015 Energy-efficient neuromorphic computation based on compound spin synapse with stochastic learning *Proc.—IEEE Int. Symp. Circuits System* pp 1538–41

[20] Currihan-Incorvia J A, Siddiqui S, Dutta S, Evarts E R, Zhang J, Bono D, Ross C A and Baldo M A 2016 Logic circuit prototypes for three-terminal magnetic tunnel junctions with mobile domain walls *Nat. Commun.* **7** 10275

[21] Lequeux S, Sampaio J, Cros V, Yakushiji K, Fukushima A, Matsumoto R, Kubota H, Yuasa S and Grollier J A 2016 Magnetic synapse: multilevel spin-torque memristor with perpendicular anisotropy *Sci. Rep.* **6** 1

[22] Grollier J, Querlioz D and Stiles M D 2016 Spintronic nanodevices for bioinspired computing *Proc. IEEE* **104** 2024–39

[23] Sengupta A and Roy K 2017 Encoding neural and synaptic functionalities in electron spin: a pathway to efficient neuromorphic computing *Appl. Phys. Rev.* **4** 041105

[24] Hassan N, Hu X, Jiang-Wei L, Brigner W H, Akinola O G, Garcia-Sanchez F, Pasquale M, Bennett C H, Incorvia J A C and Friedman J S 2018 Magnetic domain wall neuron with lateral inhibition *J. Appl. Phys.* **124** 152127

[25] Chappert C, Fert A and Van Dau F N 2007 The emergence of spin electronics in data storage *Nat. Mater.* **6** 813–23

[26] Sengupta A, Shim Y and Roy K 2016 Proposal for an all-spin artificial neural network: emulating neural and synaptic functionalities through domain wall motion in ferromagnets *IEEE Trans. Biomed. Circuits Syst.* **10** 1152–60

[27] Nikonorov D E and Young I A 2013 Overview of beyond-CMOS devices and a uniform methodology for their benchmarking *Proc. IEEE* **101** 2498–533

[28] Beach G S D, Tsoi M and Erskine J L 2008 Current-induced domain wall motion *J. Magn. Magn. Mater.* **320** 1272–81

[29] Manipatruni S, Nikonorov D E, Ramesh R, Li H and Young I A 2015 Spin-orbit logic with magnetoelectric nodes: a scalable charge mediated nonvolatile spintronic logic (arXiv:1512.05428)

[30] Yu J, Qiu X, Wu Y, Yoon J, Deorani P, Besbas J M, Manchon A and Yang H 2016 Spin orbit torques and Dzyaloshinskii–Moriya interaction in dual-interfaced Co–Ni multilayers *Sci. Rep.* **6** 32629

[31] Brataas A and Hals K M D 2014 Spin-orbit torques in action *Nat. Nanotechnol.* **9** 86–8

[32] Zand R, Camsari K Y, Datta S and DeMara R F 2018 Composable probabilistic inference networks using MRAM-based stochastic neurons *ACM J. Emerg. Technol. Comput. Syst.* **15** 17

[33] Heyns M, Zografos O, Devolder T, Bultynck O, Vayset A, Doevenspeck J, Manfrini M, Radu I P, Raymenants E and Wan D 2018 Chain of magnetic tunnel junctions as a spintronic memristor *J. Appl. Phys.* **124** 152116

[34] Upadhyay N K, Jiang H, Wang Z, Asapu S, Xia Q and Joshua Yang J 2019 Emerging memory devices for neuromorphic computing *Adv. Mater. Technol.* **4** 1800589

[35] Zhang D, Zeng L, Cao K, Wang M, Peng S, Zhang Y, Zhang Y, Klein J O, Wang Y and Zhao W 2016 All spin artificial neural networks based on compound spintronic

synapse and neuron *IEEE Trans. Biomed. Circuits Syst.* **10** 828–36

[36] Brigner W H, Hu X, Hassan N, Bennett C H, Incorvia J A C, Garcia-Sanchez F and Friedman J S 2019 Graded-anisotropy-induced magnetic domain wall drift for an artificial spintronic leaky integrate-and-fire neuron *IEEE J. Explor. Solid-State Comput. Devices Circuits* **5** 19–24

[37] Srinivasan G, Sengupta A and Roy K 2016 Magnetic tunnel junction based long-term short-term stochastic synapse for a spiking neural network with on-chip STDP learning *Sci. Rep.* **6** 29545

[38] Huang Y and Amit Y 2011 Capacity analysis in multi-state synaptic models: a retrieval probability perspective *J. Comput. Neurosci.* **30** 699–720

[39] Fauth M, Wörgötter F and Tetzlaff C 2015 The formation of multi-synaptic connections by the interaction of synaptic and structural plasticity and their functional consequences *PLoS Comput. Biol.* **11** e1004031

[40] Kotasinski J H and Blackwell K T 2010 Computational neuroscience: modeling the systems biology of synaptic plasticity *Nat. Rev. Neurosci.* **11** 239–51

[41] Himeno A, Kasai S and Ono T 2005 Current-driven domain-wall motion in magnetic wires with asymmetric notches *Appl. Phys. Lett.* **87** 243108

[42] Noh S J, Miyamoto Y, Okuda M, Hayashi N and Keun Kim Y 2012 Effects of notch shape on the magnetic domain wall motion in nanowires with in-plane or perpendicular magnetic anisotropy *J. Appl. Phys.* **111** 07D123

[43] Parkin S S P, Hayashi M and Thomas L 2008 Magnetic domain wall racetrack memory *Science* **320** 190–4

[44] Hayashi M, Thomas L, Moriya R, Rettner C and Parkin S S P 2008 Current-controlled magnetic domain-wall nanowire shift register *Science* **320** 209–11

[45] Hu X, Timm A, Brigner W H, Incorvia J A C and Friedman J S 2019 SPICE-only model for spin-transfer torque domain wall MTJ logic *IEEE Trans. Electron Devices* **66** 2817–21

[46] Hennig M H 2008 Modeling synaptic transmission *N Week—ANC, Informatics, Univ. Edinburgh* vol 4 pp 1–18

[47] Sneyd J and Bertram R 2005 Mathematical biosciences Institute at the Ohio State University *Tutorials in Mathematical Biosciences II: Mathematical Modeling of Calcium Dynamics and Signal Transduction*. Springer e-books vol 1867 (Berlin: Springer)

[48] Sleiman M, Stevens D R and Rettig J 2017 Simultaneous membrane capacitance measurements and TIRF microscopy to study granule trafficking at immune synapses *The Immune Synapse: Methods and Protocols (Methods in Molecular Biology)* vol 1587 ed C T Baldari and M L Dustin (New York: Humana Press) pp 157–69

[49] Shouval H Z and Kalantzis G 2004 Stochastic properties of synaptic transmission affect the shape of spike time-dependent plasticity curves *J. Neurophysiol.* **93** 1069–73

[50] Shouval H 2010 Spike timing dependent plasticity: a consequence of more fundamental learning rules *Frontiers Comput. Neurosci.* **4** 19

[51] Frémaux N and Gerstner W 2016 Neuromodulated spike-timing-dependent plasticity, and theory of three-factor learning rules *Frontiers Neural Circuits* **9** 85

[52] Graupner M 2010 Mechanisms of induction and maintenance of spike-timing dependent plasticity in biophysical synapse models *Frontiers Comput. Neurosci.* **4** 136

[53] Porr B, Saudargiene A and Worgotter F 2004 Analytical solution of spike-timing dependent plasticity based on synaptic biophysics *Advances in Neural Information Processing Systems* vol 16, ed S Thrun, L Saul and B Scholkopf (Cambridge, MA: MIT Press) pp 1343–50

[54] Zhang X 2008 A mathematical model of a neuron with synapses based on physiology *Nat. Preced.* (<https://doi.org/10.1038/npre.2008.1703.1>)

[55] Bi G and Poo M 2002 Synaptic modification by correlated activity: Hebb's postulate revisited *Annu. Rev. Neurosci.* **24** 139–66

[56] Vansteenkiste A, Leliaert J, Dvornik M, Helsen M, Garcia-Sanchez F and Van Waeyenberge B 2014 The design and verification of MuMax3 *AIP Adv.* **4** 107133

[57] Donahue M J and Porter D G 2012 OOMMF User's Guide version 1.0 *Interagency Report NISTIR 6376* (Gaithersburg, MD: NIST) (<http://math.nist.gov/oommf/>)

[58] Sengupta A and Roy K 2018 Neuromorphic computing enabled by physics of electron spins: prospects and perspectives *Appl. Phys. Express* **11** 030101

[59] Sharad M, Augustine C, Panagopoulos G and Roy K 2012 Spin based neuron-synapse module for ultra low power programmable computational networks *Proc. Int. Joint Conf. Neural Networks* pp 10–15 (<https://doi.org/10.1109/IJCNN.2012.6252609>)

[60] Zeng L, Zhang D, Zhang Y, Gong F, Gao T, Tu S, Yu H and Zhao W 2016 Spin wave based synapse and neuron for ultra low power neuromorphic computation system *Proc.—IEEE Int. Symp. Circuits System* pp 918–21

[61] Vincent A F, Larroque J, Locatelli N, Romdhane N B, Bichler O, Gamrat C, Zhao W S, Klein J O, Galdin-Retailleau S and Querlioz D 2015 Spin-transfer torque magnetic memory as a stochastic memristive synapse for neuromorphic systems *IEEE Trans. Biomed. Circuits Syst.* **9** 166–74

[62] Currihan J A, Jang Y, Mascaro M D, Baldo M A and Ross C A 2012 Low energy magnetic domain wall logic in short, narrow, ferromagnetic wires *IEEE Magn. Lett.* **3** 3000104

[63] Dutta S, Siddiqui S A, Currihan-Incorvia J A, Ross C A and Baldo M A 2015 Micromagnetic modeling of domain wall motion in sub-100-nm-wide wires with individual and periodic edge defects *AIP Adv.* **5** 127206

[64] He J, Li Z and Zhang S 2005 Current-driven domain-wall depinning *J. Appl. Phys.* **98** 016108

[65] Ilgaz D, Kläui M, Heyne L, Boulle O, Zinser F, Krzyk S, Fonin M, Rüdiger U, Backes D and Heyderman L J 2008 Selective domain wall depinning by localized Oersted fields and Joule heating *Appl. Phys. Lett.* **93** 2006–9

[66] Curiale J, Lemière A, Faini G and Jeudy V 2010 Track heating study for current-induced domain wall motion experiments *Appl. Phys. Lett.* **97** 243505

[67] Mahalanabis D, Sivaraj M, Chen W, Shah S, Barnaby H J, Kozicki M N, Christen J B and Vrudhula S 2016 Demonstration of spike timing dependent plasticity in CBRAM devices with silicon neurons *2016 IEEE Int. Symp. Circuits System* pp 2314–7

[68] Prezioso M, Bayat F M, Hoskins B, Likharev K and Strukov D 2016 Self-adaptive spike-time-dependent plasticity of metal-oxide memristors *Sci. Rep.* **6** 21331

[69] Du N, Kiani M, Mayr C G, You T, Bürger D, Skorupka I, Schmidt O G and Schmidt H 2015 Single pairing spike-timing dependent plasticity in  $\text{BiFeO}_3$  memristors with a time window of 25 ms to 125  $\mu\text{s}$  *Frontiers Neurosci.* **9** 227

[70] Li S, Zeng F, Chen C, Liu H, Tang G, Gao S, Song C, Lin Y, Pan F and Guo D 2013 Synaptic plasticity and learning behaviours mimicked through Ag interface movement in an Ag/conducting polymer/Ta memristive system *J. Mater. Chem. C* **1** 5292–8