# Accurate Inductance Models of Mounted Two-Terminal Decoupling Capacitors

Tamar Makharashvili<sup>(D)</sup>, *Member, IEEE*, Siqi Bai<sup>(D)</sup>, *Student Member, IEEE*,

Giorgi Maghlakelidze<sup>(D)</sup>, *Student Member, IEEE*, Samuel Connor, *Senior Member, IEEE*, Albert E. Ruehli, *Life Fellow, IEEE*, Phil Berger, *Life Senior Member, IEEE*, James L. Drewniak<sup>(D)</sup>, *Fellow, IEEE*, and Daryl G. Beetner<sup>(D)</sup>, *Senior Member, IEEE*

Abstract—The inductance associated with a decoupling capacitor is typically represented with a constant equivalent series inductance (ESL). In reality, this inductance depends on how the capacitor is mounted and on coupling to closely located structures, including the traces and vias connecting the capacitor to the power and return planes. Here, a method is proposed to quickly and accurately compute the inductance associated with decoupling capacitors and their connections to the power planes. We call this equivalent inductance  $L_{above,decap}$ . It is calculated by partitioning the geometry into sub-models for the connections to the power and return planes and for the mounted capacitor and pads. The accuracy of the partitioning approach is demonstrated in simulation and experiments using two common decoupling capacitor layouts. Simulations are performed using the finite element method (FEM) and the partial element equivalent circuit (PEEC) method. The partitioning approach estimates the overall inductance associated with the decoupling capacitor and its connections to the power bus within 16% if the distance between the capacitor and reference plane (dielectric thickness) is not more than 6 mils. A simplified PEEC model was further developed which allows a user to estimate the inductance associated with the capacitor using closed-form expressions. This simplified model estimates the capacitor's inductance within 14% of the results found using FEM. The models presented in this work should help both the power distribution network tool designer as well as the design engineer to obtain more accurate inductance estimates than is possible using the manufacturer's ESL value.

*Index Terms*—Computational electromagnetics, inductance, multi-layer ceramic capacitor, power distribution network, partitioning, partial equivalent element circuit (PEEC) method, passive component modeling, signal and power integrity (SiPi).

## I. INTRODUCTION

D ECOUPLING capacitors (decaps) are a major contributor to the power distribution network (PDN) impedance [1],

Manuscript received November 9, 2019; revised March 9, 2020; accepted April 11, 2020. This work is based upon work supported in part by the National Science Foundation under Grant No. IIP-1916535. (*Corresponding author: Tamar Makharashvili.*)

Tamar Makharashvili, Siqi Bai, Giorgi Maghlakelidze, Albert E. Ruehli, Phil Berger, James L. Drewniak, and Daryl G. Beetner are with the EMC Laboratory, Missouri University of Science and Technology, Rolla, MO 65409 USA (e-mail: tm2p8@mst.edu; sb2pc@mst.edu; gmp73@mst.edu; albert.ruehli@gmail.com; bergerphi@mst.edu; drewniak@mst.edu; daryl@mst.edu).

Samuel Connor is with the IBM Corporation, Armonk, NY 10504 USA (e-mail: sconnor@us.ibm.com).

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TEMC.2020.2987995

[2]. Decoupling capacitors are used to reduce voltage ripples caused by simultaneous switching noise. Careful selection of the decoupling capacitor's value, package size, quantity and placement – as well as their connection inductance to the power and return planes - are critical for power integrity [3]. Noise in the power supply may also cause electromagnetic interference issues [4], [5]. The impedance of these capacitors is usually represented as an equivalent circuit consisting of an equivalent series capacitance (ESC), equivalent series inductance (ESL), and equivalent series resistance (ESR) [6], [7], as a distributed circuit [8], [9], or as an S-parameter block [10], [11]. However, these models often do not include the parasitic interactions between the capacitor and surrounding structures, including its mounting pads, the reference plane, and the traces and the vias connecting the capacitor to the power bus [12]. ESR and ESC values given by the manufacturer are typically correct within the specified tolerance [6], [13], but the actual inductance of the mounted capacitor can be much different than would be calculated using the ESL alone [14]. The equivalent inductance depends on the distance to the reference plane and the capacitor's inner electrode architecture [14], [15]. Hence, accurately modeling the inductance associated with decoupling capacitors can be critical to the design of the power delivery network (PDN). Unfortunately, it is often not practical to estimate the inductance of the capacitor and its connections to the PDN using computational electromagnetics (CEM) tools [16]–[18], considering the many connection configurations that are possible for the large number of decoupling capacitors that are often used in a design. However, estimations of these inductances can be made with the partial equivalent element circuit (PEEC) method using a simple representation of the decoupling capacitor [19], [20]. PEEC allows representation of electromagnetic parasitics with electrical circuit elements whose values can be calculated using closed-form expressions.

The PDN impedance is a combination of two impedances which are found to be independent from each other. Those two impedances are: the impedance of the capacitor(s) with the layout above the top return plan (pad, trace, via), and the impedance between a noise source on the IC and its connection to the power in return planes [21]. In this work, a method is proposed to estimate the inductance associated with decoupling capacitors by partitioning the total inductance into two sub-models: one for the capacitor and mounting pads, and one for the traces and

See https://www.ieee.org/publications/rights/index.html for more information.

<sup>0018-9375 © 2020</sup> IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

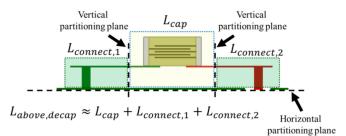

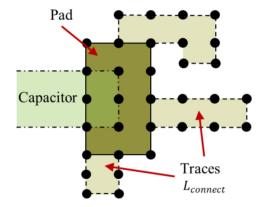

Fig. 1. Total inductance associated with a decoupling capacitor,  $L_{above,decap}$ , can be partitioned into a portion associated with the capacitor and mounting pads,  $L_{cap}$ , and a portion associated with the connecting traces and vias,  $L_{connect}$ .

vias connecting the capacitor to the power and return plane. The inductance associated with these sub-models can be found independent of one another or the rest of the PDN. Partitioning allows the inductance associated with the mounted capacitor to be established before designing the overall PDN circuit details, and allows to calculate the inductance associated with a wide variety of connections to the power and return planes separately.

The partitioning approach will be discussed in detail in this article. Two PEEC models will be presented, one of which is complex and requires numerical solution and one of which is simplified and can be solved using closed-form expressions. The internal geometrical structure of a number of commercial capacitors are analyzed in Section III, to account for variation in internal structures of the capacitors while estimating inductance. Results are presented in section IV, where estimates of the inductance of the mounted capacitor, pads, and the reference plane are measurements. Discussions and conclusions are summarized in Section V.

#### **II. PARTITIONING APPROACH**

Partitioning is used to simplify and speedup the modeling of decoupling capacitors for practical PDNs. A PDN may include hundreds of decoupling capacitors where exact modeling of all parts requires large compute times [17]. Conventional approaches do not lead to efficient solutions of the problem. The proposed method is based on horizontal and vertical partitioning planes as shown in Fig. 1. The metal plane under the capacitor in Fig. 1 is usually a ground plane. This horizontal metal plane is a good place for splitting the model of the capacitor from the rest of the PDN [3], [20], [22]. More specifically, the capacitor is typically partitioned from the rest of the PDN at the location where the power via transitions through the antipad in the ground plane. The ground plane isolates the mounted capacitor from the rest of the PDN layers, since there is minimal opportunity to couple energy through the ground plane or the via antipad. We will use this horizontal plane partition in all our models.

Here we will also use a second vertical partition for the contact connections as shown in Fig. 1 to separate the calculation of the inductance associated with the capacitor from the inductance associated with the connections to the power and return planes. The inductance associated with the connections between the capacitor and the power and ground planes will be represented by an inductance we call  $L_{connect}$ . The inductance associated

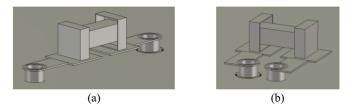

Fig. 2. Models of 100 nF 0603 capacitor mounted. (a) Straight. (b) *L*-shaped layout.

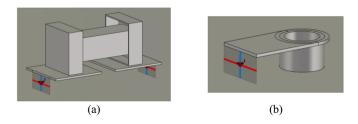

Fig. 3. Straight layout shown in Fig. 2(a) was partitioned into models. (a)  $L_{cap}$ , representing the pads, capacitor, and reference plane. (b)  $L_{connect1}$ , representing the connecting trace and via, and the reference plane.

with the capacitor, including the strong inductive coupling to the metal plane beneath it and its local environment, will be represented with  $L_{cap}$ .

Partitioning leads to two separate parts for the connections,  $L_{connect} = L_{connect,1} + L_{connect,2}$ , and for the capacitor,  $L_{cap}$ , which are weakly coupled to each other. The partition between  $L_{connect}$  and  $L_{cap}$  is located sufficiently far away from the capacitor such that only weak couplings are interrupted by the partitioning cuts. We later present a more complicated model that better accounts for this coupling. For this simple partitioning, the inductance of the overall capacitor structure,  $L_{above,decap}$ , can be computed separately as

$$L_{above,decap} = L_{connect} + L_{cap} + err \tag{1}$$

where err is the error due to the simple partitioning approach. A key advantage of this partitioning approach is that the  $L_{cap}$  inductance can be the same for a large number of capacitors in a PDN if the same decoupling capacitor type is used. In this case, the modeling of all capacitors is much simpler for a large PDN with many capacitors than if the capacitor must be modeled over and over. More details will be given below.

## A. Vertical Plane Partitioning of the Connection Between $L_{cap}$ and $L_{connect}$

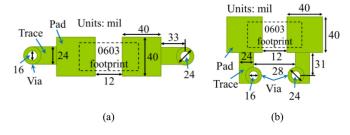

Capacitors may be connected to the PDN through a variety of connection layouts. A few of the more common layouts and their inductance are shown in Fig. 2 [23]. Layouts studied in this article are referred to as the "straight" and "L-shaped" layouts.

As shown in Fig. 1, the partitioning approach separates the inductance  $L_{connect}$  from the inductance  $L_{cap}$ . This partitioning allows the user to quickly estimate the overall inductance,  $L_{above,decap}$ , for a number of layout configurations. To illustrate this flexibility, we consider two simple cases where the connections are to the sides as well as to the front as shown in Fig. 2. Figs. 3 and 4 show these layouts partitioned into structures

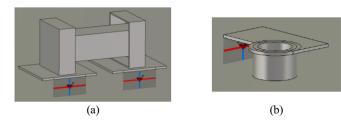

Fig. 4. *L*-shaped layout shown in Fig. 2(b) was partitioned into models. (a)  $L_{cap}$ , representing the pads, capacitor, and reference plane. (b)  $L_{connect1}$ , representing the connecting trace and via, and the reference plane.

Fig. 5. Top view of pad with a variety of connections to traces.

for  $L_{connect}$  and  $L_{cap}$ . The vertical lumped ports (highlighted with red and blue lines) in these figures were used to enable calculation of  $L_{connect}$  and  $L_{cap}$  within the Dassault Systèmes CST Studio Suite solver [24] (CST). Input impedances at the lumped port locations were obtained using CST's finite element method (FEM) solver. Inductances were calculated from input impedance values. For PEEC, we used two different models. In the simple model, we ignored the partial mutual inductances which couple  $L_{connect}$  and  $L_{cap}$ . This, of course, leads to relatively small errors and simpler, independent computations. The coupling between the sub-models for the capacitor and the traces is small unless the dielectric layer upon which the contacts are placed is far away from the ground plane. The accuracy of this approach will be shown in Section IV.

#### B. Improved Model for Connections Including Coupling

The partitioning approach presented in the last subsection leaves out the inductive couplings between  $L_{cap}$  and  $L_{connect}$ . In this section, we give an alternative approach where we show how the missing partial mutual inductances can be included to eliminate the coupling error in (1).

As shown in Fig. 3 and Fig. 4, the partition between  $L_{cap}$  and  $L_{connect}$  is made at predetermined locations close to the capacitor. Fig. 5 shows a top view of these connections, where three different connections to the  $L_{cap}$  partition are shown. In this case, we assume that only a single  $L_{cap}$  model is needed for a given capacitor package size where the  $L_{cap}$  pads of the capacitor have enough PEEC nodes to connect all possible trace configurations. In the example in Fig. 5, we chose to show only 15 nodes for the  $L_{cap}$  pad part where six of the outside nodes

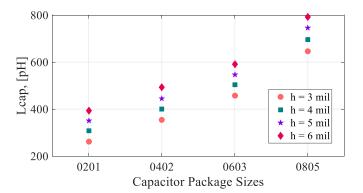

Fig. 6. Inductance associated with the capacitor as function of the distance between capacitor body and the reference plane. Values are given for typical package sizes.

are used for possible connections. Of course, all the connections and the capacitor base are located over the horizontal ground plane. In this case, the inductance  $L_{above,decap}$  is calculated numerically for each configuration without partitioning  $L_{cap}$  and  $L_{connect}$ . This will clearly lead to a more complicated model, but the model for the multiple connections can be used multiple times to avoid the construction of multiple models for  $L_{cap}$ . To eliminate the coupling error, partial mutual inductances between the  $L_{cap}$  model and the connect PEEC models in Fig. 5 must be included. The rapid decay of the coupling inductance is well known [25], which minimizes the number of partial mutual inductances needed.

## III. MODELING OF THE CAPACITOR PART, $L_{CAP}$

The value for ESL given by the manufacturer [26] does not account for the distance between the capacitor and the return plane. Fig. 6 shows the value of  $L_{cap}$  for conventional capacitor types for different distances to the return plane. As shown in this figure, capacitor mounting can significantly change  $L_{cap}$ . The following section shows the development of a highly simplified model for  $L_{cap}$  and a more complex model, which includes the internal plates of the capacitor among other features.

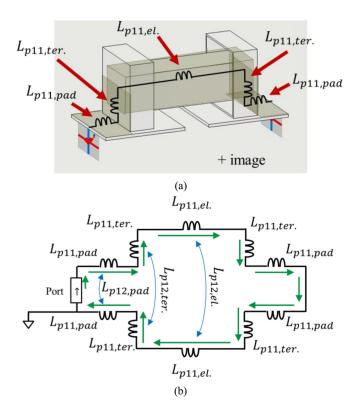

### A. Simple PEEC Model for $L_{cap}$

We first consider a PEEC model for the simplest case, as shown in Fig. 7(a), which is an orthogonal Manhattan type model with only a few partial inductances. Each structure in Fig. 7(a) is represented as a single rectangular sheet with zero thickness or with a rectangular bar. The FEM waveguide port surfaces are also included in this model. Fig. 7(a) and (b) show a PEEC equivalent circuit for the capacitor and its image in the ground plane. Because of the influence of the capacitor and its image, the solution for the equivalent circuit will result in two times  $L_{cap}$  unless the symmetry is included in the PEEC model.

Equations for the inductances shown in Fig. 7 are given in [19], in which structures are represented using conductive sheets. Using equations from [19] and the models in Fig. 7, one can estimate values for  $L_{cap}$  from closed-form expressions. This capability has the advantage that one can estimate inductance

Fig. 7. Simplified PEEC-based model of  $L_{cap}$ . (a) Structures and elements associated with the model. (b) Equivalent circuit model.

without sophisticated modeling tools, for example, using MAT-LAB, and that the simple form of the model can give intuitive insight into the primary mechanisms that lead to a particular value for  $L_{cap}$ . A more accurate model results with refined meshing and if all the partial mutual inductances between all parts of the model are included. Example results for this simple model are shown in Section IV.

## B. Detailed PEEC Model for $L_{cap}$

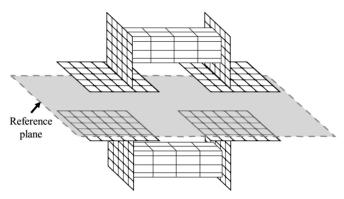

Fig. 7(a) and (b) represent a very simple equivalent circuit for the capacitor inductance. Even more sophisticated capacitor PEEC models include only a moderate number of nodes. Here, we suggest a somewhat more complex model where the cell structure is shown in Fig. 8. In fact, it is similar to the one used in [20] for a multi-terminal capacitor model. In Section IV.C, we show that the current flow in the capacitor body can be approximated by a PEEC block meshed uniformly as is indicated in Fig. 8. It is clear that this results in a major speed-up also for the FEM model. In general, the evaluation of the partial inductances takes a small fraction of a second. Even a 3D PEEC model for the capacitor does not result in many partial elements and can be computed in less than a second such that PDN models with a few hundred capacitors can be evaluated in minutes using the partitioning approach, even if the connect parts are different for most of the capacitors.

Fig. 8 shows the cells for the meshing of the  $L_{cap}$  part which shows an image to take the important ground-plane into account. The horizontal contacts at the end of the  $L_{cap}$  model pads are

Fig. 8. Cells of the mesh to compute the mounted capacitor over a reference plane, where the reference plane was replaced with an image of the capacitor.

meshed such that  $L_{connect}$  models can be applied as shown in Fig. 5. The geometrical dimensions are easily found for the external parts of the capacitor. Depending on the desired accuracy the vertical parts of the PEEC model can be modeled more accurately. However, all models in this article in Section IV used the relatively simple geometries.

The electrical PEEC modeling for the structure corresponding to Fig. 8 can be analyzed with a simple modified nodal analysis (MNA) circuit model [27]. A few observations are due to the special aspects of this model. The image cells are exact images of the PEEC model part. Thus, many partial self and mutual inductances are calculated only once. Mutual inductances between source and image cells are added to the MNA model as well. Similar to the Plane-Pair PEEC (PPP) modeling approach [19], [25], the symmetry can be used to reduce the number of variables. We observe that the voltages for the model and the image are equal and opposite resulting in half the voltages. The same is true for currents in the corresponding elements. The ground or zero volts must be at the plane in the middle shown in Fig. 8 similar to the PPP method [19].

We can observe from Fig. 7(b) that while the image current is opposite in the x, y plane cells, it is in the same direction in the vertical z-directed cells for both the model and its image. While the current is the same as in the conventional model, the image model results in twice the voltage such that the inductance is

$$L_{cap} = \frac{V_p}{2I_p} \tag{2}$$

where  $V_p$  is a port voltage,  $I_p$  is a port current. Of course, the  $L_{connect}$  results in very similar simple PEEC models as the  $L_{cap}$  model. For this reason, we do not consider the  $L_{connect}$  modeling separately [19].

#### C. Geometry of the Capacitor Plate Part

The capacitor model shown in Fig. 8 was further extended using knowledge of the capacitor's internal architecture [28]. The internal geometry of several standard capacitors was studied. The decoupling capacitor package sizes are coded as 0201, 0402, 0603, and 0805, which represent the length and width of the component in hundredths of inches. Capacitors with values of 22  $\mu$ F, 100 nF, and 1 nF and of type 0201, 0402, 0603,

MAKHARASHVILI et al.: ACCURATE INDUCTANCE MODELS OF MOUNTED TWO-TERMINAL DECOUPLING CAPACITORS

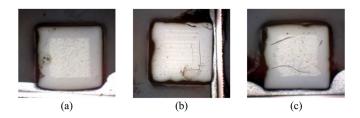

Fig. 9. Cross-section of three 0603 capacitors with 1 nF nominal capacitance produced. (a) Manufacturer A. (b) Manufacturer B. (c) Manufacturer C.

Fig. 10. Cross-sections of three 0603 capacitors with 100 nF nominal capacitance produced. (a) Manufacturer A. (b) Manufacturer B. (c) Manufacturer C.

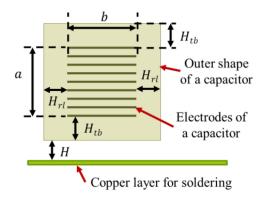

Fig. 11. Dimensions of each capacitor's internal architecture were measured under a microscope.

TABLE I22  $\mu$ F 0805 Capacitor Internal Geometry

|         | a [mil] | <i>b</i> [mil] | $H_{tb}$ [mil] | $H_{rl}$ [mil] | <i>H</i> [mil] |

|---------|---------|----------------|----------------|----------------|----------------|

| Minimum | 38      | 27             | 1.6            | 3.5            | 1              |

| Average | 41      | 35             | 3              | 3.7            | 2              |

| Maximum | 44      | 44             | 4.5            | 4              | 4              |

TABLE II

1 NF 0603 CAPACITOR INTERNAL GEOMETRY

|         | a [mil] | <i>b</i> [mil] | $H_{tb}$ [mil] | $H_{rl}$ [mil] | <i>H</i> [mil] |

|---------|---------|----------------|----------------|----------------|----------------|

| Minimum | 16      | 13             | 4.8            | 4              | 1              |

| Average | 18      | 18             | 6              | 6              | 2              |

| Maximum | 20      | 20             | 7.7            | 12             | 4              |

and 0805 sizes were considered because they are commonly used in PDN designs. To measure the internal dimensions of these capacitors, the capacitors were cut and viewed under a microscope. Cross-sections of two 0603 capacitors with values of 1 and 100 nF are shown in Fig. 9 and Fig. 10, respectively. The dimensions measured, besides the capacitor length, are shown in Fig. 11 and their values are shown in Tables I–V. The tables show the average, minimum and maximum dimensions from

TABLE III 100 NF 0603 CAPACITOR INTERNAL GEOMETRY

|         | <i>a</i> [mil] | <i>b</i> [mil] | $H_{tb}$ [mil] | $H_{rl}$ [mil] | H [mil] |

|---------|----------------|----------------|----------------|----------------|---------|

| Minimum | 17.6           | 17.6           | 2.3            | 4.1            | 1       |

| Average | 19             | 19             | 5              | 5              | 2       |

| Maximum | 25             | 25             | 6.3            | 7              | 4       |

TABLE IV

100 NF 0402 CAPACITOR INTERNAL GEOMETRY

|         | a [mil] | <i>b</i> [mil] | $H_{tb}$ [mil] | $H_{rl}$ [mil] | H [mil] |

|---------|---------|----------------|----------------|----------------|---------|

| Minimum | 13.8    | 7.7            | 2.4            | 3.5            | 1       |

| Average | 13      | 11             | 3.5            | 4.5            | 2       |

| Maximum | 9.7     | 11.1           | 4.4            | 6.2            | 4       |

TABLE V 1 NF 0201 CAPACITOR INTERNAL GEOMETRY

|         | <i>a</i> [mil] | b [mil] | $H_{tb}$ [mil] | $H_{rl}$ [mil] | <i>H</i> [mil] |

|---------|----------------|---------|----------------|----------------|----------------|

| Average | 12.6           | 10      | 3              | 3.5            | 2              |

|         |                |         |                |                |                |

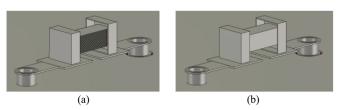

Fig. 12. (a) Simulation models of a detailed capacitor with 54 electrode plates. (b) Approximated capacitor where the plates are replaced with a solid PEEC conductive block.

capacitors of the same size and capacitance from five different manufacturers. Further, the results show that there are significant differences in the geometrical data for the same capacitors by different manufacturers. Unfortunately, this issue complicates the exact calculation of inductance.

## **IV. RESULTS**

Estimates of  $L_{connect,decap}$  were validated using FEM simulations in CST and using measurements. CST was chosen due to its flexible and easy to use graphical user interface. A simplified model of the capacitor, which replaces the internal electrode stack with a solid conductor, is first evaluated to demonstrate that the gains in compute time achieved with this simpler model do not sacrifice accuracy. Simulated values of inductance for the simplified capacitor model are then compared with measurements. Finally, results found using FEM and using the simplified and complex PEEC models are compared below.

#### A. Model of Mounted Capacitor

While modeling the entire electrode stack might lead to improved accuracy, modeling the many conductors in the electrode stack significantly increases the computational effort [20], [29], [30]. To demonstrate the impact of using a PEEC block model, simulations of FEM models for an 0603 100 nF capacitor and its straight connections were conducted where all 54 electrode plates were included in the model and where the electrode plates were replaced with a solid conductor. Fig. 12(a) shows the model

Fig. 13. Dimensions of the (a) straight; (b) *L*-shaped layouts [31].

which includes the electrode plates and Fig. 12(b) shows the model where the electrodes are approximated as a solid conductive block. Both models were solved using FEM and were built using the average geometric information in Table III. Geometric information for the pads is given in Fig. 13. The vias, pads, traces, and capacitor body were discretized using tetrahedral meshing with a maximum 3 mil mesh step width. Experiments were performed to demonstrate acceptable convergence for this discretization density. The loop inductance,  $L_{above,decap}$ , for the detailed capacitor model in Fig. 12(a) was 1092 pH, and was 1179 pH for the approximated body model in Fig. 12(b). The 87 pH (7%) difference between the models is small considering the large difference in compute time.

#### B. Measurements

In this section, we compare values for the inductance of a 0603 capacitor found through simulation of the FEM model and found through measurements. Results are found for both the straight and L-shaped contact layouts shown in Fig. 13. For the measurements, the decoupling capacitors were mounted on a fixture consisting of a standard 4-layer PCB, with two SMA ports connected to the plane below the two ground planes [32]. To obtain  $L_{above,decap}$ , a measurement of the transfer impedance between the two ports was used to measure the inductance,  $L_1$ , into the PDN including the capacitor, pads, vias, and the ground plane. The inductance of the PCB layers and vias,  $L_2$ , was also measured, where the decoupling capacitor inductance is eliminated from the measurement by shorting the via to the return plane [32]. The inductance  $L_{above,decap}$  was found by subtracting the two measured inductances, i.e.,

$$L_{above,decap} = L_1 - L_2 \tag{3}$$

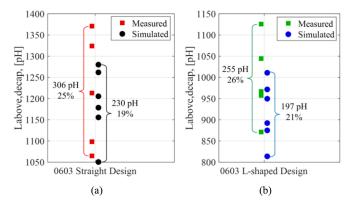

The inductance for the mounted capacitor varies between manufacturers and between tests depending on the internal structure of the capacitor [23] and on the soldering details, which can cause variations in the distance between the capacitor and return plane or position of the capacitor on the pads. Since the precise geometries associated with the measured capacitors were not known, measurements of inductance were made using five 0603 100 nF capacitors of the same capacitance but from different manufacturers. An attempt was made to minimize the amount of solder on the pad and thus the variation in the height of the capacitor above the return plane with solder thickness. Measurements were made for both straight and for L-shaped connections as shown in Fig. 2. FEM models were built using the geometric

Fig. 14. Variation of measured and simulated values of  $L_{above,decap}$  while changing the 0603 capacitor's geometry and placement. (a) Straight. (b) *L*-shaped layout designs.

TABLE VI Average Values of  $L_{ABOVE, DECAP}$

|                    | Straight Layout [pH] | L-shaped Layout [pH] |

|--------------------|----------------------|----------------------|

| Simulated (Fig. 2) | 1188                 | 919                  |

| Measured           | 1214                 | 993                  |

| Difference         | 2%                   | 8%                   |

information in Table III while modeling the electrode plates as a solid conductive block as shown in Fig. 2.

The measured results are compared in Fig. 14 to results found using FEM, and are summarized in Table VI. The measured values of inductance vary by about 26% for the straight and L-shaped connection layouts. As expected, the inductance for the straight layout was higher than for the L-shaped layout. Variations in the values of inductance closely matched the measurement. As shown in Table VI, the difference between the average inductance found with the FEM solver and the measurement was within 8%, providing confidence in the methods used to determine  $L_{above,decap}$ .

The slightly higher inductance values in the measurements compared to the FEM results can be attributed to solder tilting or a small rotation of the capacitor in the measurement setup above the return plane. These changes in placement of the decoupling capacitors have not been included in the FEM modeling.

#### C. Results for Simple Partitioning of Labove.decap FEM Model

As introduced in Fig. 1, the vertical partitioning approach separates the inductance  $L_{above,decap}$  into a part associated with the traces and vias,  $L_{connect}$ , and a portion associated with the capacitor and its pads,  $L_{cap}$ . In this section, we evaluate the error resulting from using this partitioning. Fig. 2(a) and Fig. 2(b) show the models for the straight and L-shaped layout without partitioning, and Fig. 3 and Fig. 4 show the models with partition between the trace and pads for this study. The inductance values for  $L_{cap}$ ,  $L_{connect}$  were computed using the presented partitioning approach and then used to estimate  $L_{above,decap}$ . The estimates for  $L_{above,decap}$  are compared to values found by

| TABLE VII                                                 |

|-----------------------------------------------------------|

| INDUCTANCE ESTIMATED WITH PARTITIONING APPROACH USING FEM |

|                       | Straight Design              |                          |                                                      |                                  |       |  |  |

|-----------------------|------------------------------|--------------------------|------------------------------------------------------|----------------------------------|-------|--|--|

|                       | P                            | Partitioning Approach    |                                                      |                                  |       |  |  |

| Height,<br>h, [mil]   | L <sub>connect</sub><br>[pH] | L <sub>cap</sub><br>[pH] | $L_{above,decap} \approx L_{connect} + L_{cap}$ [PH] | L <sub>above,decap</sub><br>[pH] | error |  |  |

| 3                     | 158                          | 457                      | 615                                                  | 622                              | 2%    |  |  |

| 5                     | 246                          | 547                      | 793                                                  | 769                              | 3%    |  |  |

| 6                     | 286                          | 590                      | 876                                                  | 836                              | 5%    |  |  |

| 8                     | 362                          | 671                      | 1033                                                 | 960                              | 8%    |  |  |

| 10                    | 438                          | 748                      | 1186                                                 | 1073                             | 11%   |  |  |

| 12                    | 510                          | 823                      | 1333                                                 | 1179                             | 13%   |  |  |

|                       | L-shaped Design              |                          |                                                      |                                  |       |  |  |

| Partitioning Approach |                              |                          |                                                      | Direct Sim.                      |       |  |  |

| Height,<br>h, [mil]   | L <sub>connect</sub><br>[pH] | L <sub>cap</sub><br>[pH] | $L_{above,decap} \approx L_{connect} + L_{cap}$ [PH] | L <sub>above,decap</sub><br>[pH] | error |  |  |

| 3                     | 160                          | 416                      | 576                                                  | 547                              | 5%    |  |  |

| 5                     | 246                          | 481                      | 727                                                  | 645                              | 13%   |  |  |

| 6                     | 286                          | 513                      | 767                                                  | 687                              | 16%   |  |  |

| 8                     | 364                          | 572                      | 936                                                  | 759                              | 23%   |  |  |

| 10                    | 436                          | 629                      | 1065                                                 | 820                              | 29%   |  |  |

| 12                    | 508                          | 684                      | 1192                                                 | 875                              | 36%   |  |  |

simulating the entire structure in Table VII. While the capacitor and pad geometries did not change for the straight and L-shaped layouts, the values for  $L_{cap}$  differ between the designs because of the port locations. Results shown in Table VII were obtained using FEM simulations to validate the partitioning approach.

As shown in Table VII, the accuracy of the simple partitioning approach is a function of the thickness of the dielectric spacing under the capacitor. This error is due to the missing mutual inductive coupling between  $L_{cap}$  and  $L_{connect}$ . It is not surprising that the error increases with the distance of the connections from the return plane. Dielectric thickness in high-speed, multilayer PCBs, however, does not exceed 6 mil, which suggests the error should not exceed 16% in these applications. The general connection model with mutual inductances in Section II.B can be used to eliminate this error, which is accomplished by adding the partial mutual inductances between the existing  $L_{connect}$  and  $L_{cap}$  PEEC models and by solving the combined PEEC model with these mutual inductances.

## D. PEEC Inductance Model for Labove, decap

In this section, we compare estimates of the inductance between PEEC and FEM. First, we consider the  $L_{cap}$  inductance for an 0603 capacitor using both approaches. Values in this table were calculated using the average 0603 dimensions shown in Table III, using the pads dimensions shown in Fig. 13 and using a capacitor height, h, of 5 mils. Results were found both for a detailed PEEC model, using a complex 3D model of the structure, with hundreds of mesh cells as shown in Fig. 8, and for a simplified PEEC model, using a few tens of mesh cells as shown in Fig. 7. The simplified PEEC model can simply be solved using analytical equations as discussed in Section III.A. The results for both the simplified and the detailed  $L_{cap}$  models are shown in Table VIII. No results are shown for the simplified

TABLE VIII  $L_{CAP}$  Found Using PEEC and FEM (100 NF 0603 Capacitor)

| Design                                                   | FEM | Detailed<br>PEEC | Simplified<br>PEEC |

|----------------------------------------------------------|-----|------------------|--------------------|

| L <sub>cap</sub> for straight layout<br>(Fig. 3(a)) [PH] | 547 | 607              | 473                |

| L <sub>cap</sub> for L-shaped layout<br>(Fig. 4(a)) [PH] | 481 | 550              | N/A                |

TABLE IX Self and Mutual Inductances for Circuit Elements Shown in Fig. 7

| $L_{p11,pad}$ [pH]                              | 57.7 | $L_{p12,pad}$ [pH]                             | 29.7  |

|-------------------------------------------------|------|------------------------------------------------|-------|

| <i>L</i> <sub><i>p</i>11,<i>ter</i>. [pH]</sub> | 81.7 | $L_{p11,el.}$ [pH]                             | 569.9 |

| <i>L</i> <sub>p12,ter.</sub> [pH]               | 23.3 | <i>L</i> <sub><i>p</i>12,<i>el</i>.</sub> [pH] | 279.9 |

PEEC model for the L-shaped layout, since this model was only solved for the straight layout. The detailed and simplified PEEC models differed from the FEM model by 11% to 14%. These values are typically within the acceptable range of errors. The modestly larger values estimated by the detailed PEEC model may have resulted because the pads and terminals are approximated with zero thickness conductors. Importantly, the PEEC model required less than a minute to calculate the inductance of the capacitor, which illustrates the significant benefit of the PEEC models in comparison to the FEM model.

The partial self- and mutual inductances calculated by the simple PEEC model for an 0603 capacitor are shown in Table IX [19]. Mutual inductances in the table are given with respect to a structure's image in the return plane, as shown in Fig. 7(b) [19]. Other mutual inductances were ignored. Using these values, the total equivalent inductance,  $L_{cap}$ , for the capacitor model in Fig. 7 can be found as:

$L_{cap} = \frac{L_{p11} - L_{p12}}{2}$

where

$$L_{p11} = 2\left(2L_{p11,pad} + 2L_{p11,ter.} + L_{p11,el.}\right) \tag{5}$$

$$L_{p12} = 2\left(2L_{p12,pad} + 2L_{p12,ter.} + L_{p12,el.}\right) \tag{6}$$

Analyzing the circuit elements in Table IX demonstrates that the conductor associated with the capacitor's electrodes is responsible for nearly 60% of the value of  $L_{cap}$ . The mutual coupling ( $L_{p12,el}$ .) between the capacitor and its image in the reference plane contributes substantially to the overall value of  $L_{cap}$  as well. In this case, the partial mutual inductance to the image is almost half the partial self-inductance of each component. The large contribution of this mutual inductance helps demonstrate the importance of considering the reference plane distance in the  $L_{cap}$  calculations.

#### V. DISCUSSION AND CONCLUSIONS

The main aim of this article is the efficient, accurate computation of decoupling capacitor inductances. They can contribute a fraction of the overall PDN system inductance which is important for high performance systems. Unfortunately, the single

(4)

ESL inductance value for the decoupling capacitor provided by the manufacturers is not an accurate value because it fails to account for the inductive coupling to the reference plane and other local physical parameters.

Determining the inductance associated with each decoupling capacitor layout in a VLSI package design is expensive using commercial CEM tools. Using the presented approaches to compute the values for a large number of decaps is time consuming. Further, some layout tools physically short the pads under the part as an approximation. This interferes with the strong coupling under the capacitor observed in this work, which we call the inductive coupling sandwich.

The partitioning techniques presented in this article result in the separation of the decap into several parts which are faster to evaluate. The partitioning is implemented with a horizontal part which separates the decap from the PDN circuit computation. Two vertical partitions are presented which allow the separate evaluation of the connection paths from the capacitor body parts. This is important, since the connection parts can assume different shapes. This allows multiple uses for the PEEC model parts. In the simpler approach, couplings are ignored if the pad-to-ground spacing is sufficiently small. This is the case for higher performance designs.

The simpler PEEC models developed here allow users to compute the equivalent inductance associated with the capacitor and pads without the use of extensive modeling tool. We give an example where a closed-form expression associated with this model estimated the inductance of a 0603 capacitor within 14% of the overall inductance.

An important simplification of the modeling is accomplished by replacing the detailed multiple plate internal model with a PEEC conductor block resulting in close inductance values. It is shown in this work that additional information on the physical measurements of the capacitors are required for accurate decap inductance models. Unfortunately, differences in physical details for different manufacturers were observed even for specific models.

Our results using the partitioning approach are useful to speed-up the computation of inductances for a large number of decaps in larger designs. Also, more accuracy of the decap elements can be helpful for the recently introduced machine learning model designs, which can be evaluated with the models presented.

#### ACKNOWLEDGMENT

The authors would like to thank D. Becker from the IBM Corporation for his contribution to this project.

#### REFERENCES

- [1] J. Kim, Y. Takita, K. Araki, and J. Fan, "Improved target impedance for power distribution network design with power traces based on rigorous transient analysis in a handheld device," *IEEE Trans. Compon., Packag. Manuf. Technol.*, vol. 3, no. 9, pp. 1554–1563, Sep. 2013.

- [2] K. Koo, L. G. Romo, T. Wang, T. Michalka, and J. Drewniak, "Fast decap assignment algorithm for optimization of power distribution networks," in *Proc. IEEE Int. Symp. Electromagn. Compat. Signal/Power Integrity*, Washington, DC, USA, 2017, pp. 573–578.

- [3] K. Shringarpure *et al.*, "On finding the optimal number of decoupling capacitors by minimizing the equivalent inductance of the PCB PDN," in *Proc. IEEE Int. Symp. Electromagn. Compat.*, Raleigh, NC, USA, 2014, pp. 218–223.

- [4] Y. Araga, M. Nagata, N. Miura, H. Ikeda, and K. Kikuchi, "EMI performance of power delivery networks in 3D TSV integration," in *Proc. IEEE Int. Symp. Electromagn. Compat.*, Wroclaw, Poland, 2016, pp. 428–433.

- [5] J. Lee, H. Kim, and J. Kim, "Broadband suppression of SSN and radiated emissions using high-DK thin film EBG power distribution network for high-speed digital PCB applications," in *Proc. IEEE Int. Symp. Electromagn. Compat.*, Chicago, IL, USA, 2005, vol. 3, pp. 967–970.

- [6] M. Togashi and C. Burket, "ESR controlled MLCCs and decoupling capacitor network design," in *Proc. DesignCon*, 2007, pp. 14–27.

- [7] D. Tanaka et al., "Interposer design and measurement with various capacitors for reducing total system PDN impedance," in Proc. Int. Conf. Electron. Packag. iMAPS Asia Conf., Kyoto, Japan, 2015, pp. 767–770.

- [8] C. R. Sullivan, Y. Sun, and A. M. Kern, "Improved distributed model for capacitors in high-performance packages," in *Proc. IEEE Ind. Appl. Soc. Annu. Meeting*, Oct. 2002, pp. 969–976.

- [9] J. M. Hock, J. D. Prymak, S. Weir, M. Alexander, and I. Novak, "Inductance of bypass capacitors how to define, how to measure, how to simulate," in *Proc. DesignCon*, 2005, pp. 1–46.

- [10] J. A Lee, D. Kim, and Y. Eo, "Circuit modeling of multi-layer ceramic capacitors using S-parameter measurements," in *Proc. Int. SoC. Des. Conf.*, Busan, South Korea, 2008, pp. I-358–I-361.

- [11] K. Yamanaga, T. Sato, and K. Masu, "Accurate parasitic inductance determination of a ceramic capacitor through 2-port measurements," in *Proc. IEEE Elect. Perform. Electron. Packag.*, San Jose, CA, USA, 2008, pp. 119–122.

- [12] Application manual for power supply noise suppression and decoupling for digital ICs, Murata Manufacturing Co., Ltd., 2010. [Online]. Available: https://www.murata.com/~/media/webrenewal/support/ library/catalog/products/emc/emifil/c39e.ashx Accessed: Oct. 1, 2019.

- [13] I. Novak, "How much capacitance do we really get?," in Proc. Signal Integrity J., 2017, pp. 56–58.

- [14] Y. L Li, T. G. Yew, C. Y. Chung, and D. G. Fugueroa, "Design and performance evaluation of microprocessor packaging capacitors using integrated capacitor-via-plane model," *IEEE Trans. Adv. Packag.*, vol. 23, no. 3, pp. 361–367, Aug. 2000.

- [15] M. Stewart and D. Linton, "Multi-layer ceramic capacitor (MLCC) termination height-effect on electrical performance," in *Proc. High Freq. Postgraduate Student Colloquium*, Belfast, Ireland, 2003, pp. 124–127.

- [16] J. Cho et al., "Modeling and analysis of package PDN for computing system based on cavity model," in Proc. IEEE Int. Symp. Electromagn. Compat. Signal/Power Integrity, Washington, DC, USA, 2017, pp. 213–218.

- [17] G. Han, "Simple and fast method of on-board decoupling capacitor selection and placement," in *Proc. IEEE Elect. Des. Adv. Packag. Syst. Symp.*, Haining, China, 2017, pp. 1–3.

- [18] R. Fizeşan and O. Pop, "A MATLAB tool to optimize the selection of the decoupling capacitors in a PDN," in *Proc. IEEE 18th Int. Symp. Des. Technol. Electron. Packag.*, Alba Iulia, 2012, pp. 223–226.

- [19] A. Ruehli, G. Antonini, and L. Jiang, *Circuit Oriented Electromagnetic Modeling Using the PEEC Techniques*. Hoboken, NJ, USA: Wiley, 2017.

- [20] T. Makharashvili, S. Bai, S. Connor, A. E. Ruehli, P. Berger, J. L. Drewniak, and D. G. Beetner, "Circuit models for the inductance of eight-terminal decoupling capacitors," *IEEE Trans. Compon., Packag. Manuf. Technol.*, vol. 10, no. 1, pp. 142–150, Jan. 2020.

- [21] L. Ren et al., "Prediction of power supply noise from switching activity in an FPGA," *IEEE Trans. Electromagn. Compat.*, vol. 56, no. 3, pp. 699–706, Jun. 2014.

- [22] K. Shringarpure *et al.*, "Sensitivity analysis of a circuit model for power distribution network in a multilayered printed circuit board," *IEEE Trans. Electromagn. Compat.*, vol. 59, no. 6, pp. 1993–2001, Dec. 2017.

- [23] L. D. Smith, R. E. Anderson, D. W. Forehand, T. J. Pelc, and T. Roy, "Power distribution system design methodology and capacitor selection for modern CMOS technology," *IEEE Trans. Adv. Packag.*, vol. 22, no. 3, pp. 284–291, Aug. 1999.

- [24] CST Studio Suite Electromagnetic Field Simulation Software, Dassault Systèmes, 2019. [Online]. Available: https://www.3ds.com/productsservices/simulia/products/cst-studio-suite/, Accessed: Oct. 1, 2019.

- [25] L. Wei, K. Shringarpure, A. Ruehli, E. Wheeler, and J. Drewniak, "Planepair PEEC models for PDN using sub-meshing," in *Proc. IEEE 23rd Conf. Elect. Perform. Electron. Packag. Syst.*, Portland, OR, USA, 2014, pp. 159– 162.

- [26] Y. Chase, "Introduction to choosing MLC capacitors for bypass/ decoupling applications," Technical Information, AVX Corporation, 2001. [Online]. Available: http://www.avx.com/docs/techinfo/ DecouplingLowInductance/mlcbypas.pdf, Accessed: Oct. 1, 2019.

- [27] C. W. Ho, A. Ruehli, and P. Brennan, "The modified nodal approach to network analysis," *IEEE Trans. Circuits Syst.*, vol. 22, no. 6, pp. 504–509, Jun. 1975.

- [28] I. Novak and J. R. Miller, "Frequency-dependent characterization of bulk and ceramic bypass capacitors," in *Proc. Elect. Perform. Elect. Packag.*, Princeton, NJ, USA, 2003, pp. 101–104.

- [29] H. C. Kwak, "Investigation of techniques for reducing unintentional electromagnetic emissions from electronic circuits and systems," Ph.D. dissertation, Clemson Univ., Clemson, SC, USA, Electrical and Computer Engineering, 2011.

- [30] T. Makharashvili *et al.*, "Inductance models of 8-terminal decoupling capacitors," in *Proc. IEEE 27th Conf. Elect. Perform. Electron. Packag. Syst.*, San Jose, CA, USA, 2018, pp. 245–247.

- [31] T. Makharashvili, Y. S. Cao, A. E. Ruehli, J. Drewniak, and D. G. Beetner, "Inductance model of decoupling capacitors including the local environment," in *Proc. IEEE 26th Conf. Elect. Perform. Electron. Packag. Syst.*, San Jose, CA, USA, 2017, pp. 1–3.

- [32] Y. S. Cao et al., "Inductance extraction for PCB prelayout power integrity using PMSR method," *IEEE Trans. Electromagn. Compat.*, vol. 59, no. 4, pp. 1339–1346, Aug. 2017.

Tamar Makharashvili (Member, IEEE) received the B.S. degree in electrical and electronics engineering from Tbilisi State University, Tbilisi, Georgia, in 2013. She received M.S. and Ph.D. degrees in electrical engineering at Missouri University of Science and Technology, Rolla, MO, USA, in 2015, and 2019, respectively.

She was a Graduate Research Assistant at the Electromagnetic Compatibility Laboratory at Missouri University of Science and Technology from 2014 to 2019. She is currently a Hardware Engineer at Google

LLC. Her research areas included numerical electromagnetic analysis, systemlevel electromagnetic compatibility modeling and measurements methods, and power integrity design.

**Siqi Bai** (Student Member, IEEE) received the B.S. degree in optoelectronic information engineering from the Huazhong University of Science and Technology, Wuhan, China, in 2015, and the M.S. degree in electrical engineering from the Missouri University of Science and Technology, Rolla, MO, USA, in 2018, where he is currently pursuing the Ph.D. degree with the EMC Laboratory.

His research interests include power distribution network modeling and design, signal integrity, and automotive EMI.

**Giorgi Maghlakelidze** (Student Member, IEEE) received the B.S. degree in electrical engineering from Tbilisi State University, Tbilisi, Georgia, in 2013. He is currently working toward the Ph.D. degree in electrical engineering at the EMC Laboratory, Missouri University of Science and Technology, Rolla, MO, USA.

From 2011 to 2013, he worked on numerical methods in EM as a Junior Scientist in EMCoS Ltd. In 2016, he was an Intern with the Signal Integrity Design Group, Cisco Systems, San Jose, CA, USA.

His research interests include electrostatic discharge, ESD soft failure characterization, signal integrity, and EMI design.

Samuel Connor (Senior Member, IEEE) received the B.S.E.E. degree from the University of Notre Dame, Notre Dame, IN, USA, in 1994, and the M.S.E.E. degree from Purdue University, West Lafayette, IN, USA, in 2017.

He works for IBM, Research Triangle Park, NC, USA, where he is currently a Senior Technical Staff Member responsible for EMC design strategy and the development of EMC analysis tools. He has coauthored numerous articles in the areas of power distribution network design, common-mode filter de-

sign, and high-speed signaling issues in PCB designs.

Mr. Connor is the Past Chair of the TC-9 and the Eastern North Carolina Chapter of the EMC Society and a Former Distinguished Lecturer of the EMC Society.

Albert E. Ruehli (Life Fellow, IEEE) received his Ph.D. in electrical engineering, in 1972 from the University of Vermont, and an honorary Doctorate, in 2007 from Lulea University, Sweden.

He has been a member of various projects with IBM including interconnect tools and modeling and Manager of both the VLSI design and CAD group. From 1972 to 2009, he was with IBM's T.J. Watson Research Center. Currently, he is an Adjunct Professor at the Missouri University of S&T. He is the editor of two books and author/coauthor of another book and over 250 technical papers. He received five IBM Awards, the Guillemin-Cauer Prize, in 1982, and the Golden Jubilee Medal from the IEEE CAS Society, in 1999. He also received a Certificate of Achievement from the IEEE EMC Society, in 2001, the 2005 Richard R Stoddart Award, and in 2007 he received the Honorary Life Member Award from the IEEE EMC Society. He is a Life Fellow of the IEEE and a member of Society for Industrial and Applied Mathematics (SIAM).

**Phil Berger** (Life Senior Member, IEEE) received the B.S.E.E. degree in electrical engineering from The University of Utah, Salt Lake City, UT, USA, in 1971.

He is currently a Research Associate with the Missouri University of Science and Technology, Rolla, MO, USA.

Mr. Berger is a Senior Life Member of the IEEE EMC Society and a member of the Society of Automotive Engineers (SAE) for 18 years, where he participates in the SAE EMC Standards Committee. He is also the Past Chair of the Technical Committee #4. He is also the Vice Chair of the Cedar Rapids Iowa Section IEEE EMC Society.

James L. Drewniak (Fellow, IEEE) received the B.S., M.S., and Ph.D. degrees in electrical engineering from the University of Illinois at Urbana–Champaign, Urbana, IL, USA, in 1985, 1987, and 1991, respectively.

He is currently with the Electromagnetic Compatibility Laboratory, Department of Electrical and Computer Engineering, Missouri University of Science and Technology, Rolla, MO, USA.

His current research interests include electro-magnetic compatibility, signal and power integrity, and electronic packaging.

**Daryl G. Beetner** (Senior Member, IEEE) received the B.S. degree from Southern Illinois University, Edwardsville, IL, USA, in 1990, and the M.S. and D.Sc. degrees from Washington University, St. Louis, MO, USA, in 1994 and 1997, respectively, all in electrical engineering.

He is currently a Professor and the Chair of Electrical and Computer Engineering with Missouri University of Science and Technology (formerly the University of Missouri-Rolla), Rolla, MO, USA, where he conducts research with the Electromagnetic Compatibility Laboratory on electromagnetic immunity and emissions from the integrated circuit to the system level.