# SrSnO<sub>3</sub> Metal-Semiconductor Field-Effect Transistor with GHz Operation

Jiaxuan Wen, V. R. Saran Kumar Chaganti, Tristan K. Truttmann, Fengdeng Liu, Bharat Jalan, and Steven J. Koester, *IEEE Fellow*

**Abstract**—A SrSnO<sub>3</sub> high-frequency field-effect transistor (FET) is demonstrated. The device structure consists of a recessed Schottky-gate FET with a heavily doped cap layer. DC measurements on devices with 0.5- $\mu$ m gate length and 4- $\mu$ m source/drain spacing show a maximum drain current of 53 mA/mm and a maximum transconductance of 43.2 mS/mm. Radio frequency (RF) characterization reveals a cut-off frequency,  $f_t$ , of 1.31 GHz (0.97 GHz) and a maximum oscillation frequency,  $f_{max}$ , of 3.25 (3.25) GHz, after (before) de-embedding. These results represent an important advancement in developing perovskite materials for RF applications.

**Index Terms**—MESFET, Perovskite, Stannate, SrSnO<sub>3</sub>, RF

## I. INTRODUCTION

Perovskite-structured ABO<sub>3</sub> oxides are promising multi-functional materials with interesting physical properties such as thermoelectricity, superconductivity, and ferromagnetism, among others [1-4]. Using perovskites as channel materials for electronic devices makes use of their relatively wide bandgap and at the same time opens up the possibility of integration with other functional perovskite oxides with interesting properties. SrSnO<sub>3</sub> (SSO) has emerged recently as a particularly interesting perovskite material for use in field-effect transistors (FETs) due to its combination of large bandgap of 4-5 eV [5-7] and high room-temperature electron mobility up to 70 cm<sup>2</sup>/Vs [8-12], which is roughly 10 $\times$  higher than d-band perovskites such as SrTiO<sub>3</sub> (< 10 cm<sup>2</sup>/Vs) [13].

An early demonstration of an SSO FET was reported in 2018 [14]. This device, configured in a metal-semiconductor FET (MESFET) geometry, achieved a drive current of 36 mA/mm and a peak extrinsic transconductance,  $g_{mext}$ , of 17 mS/mm with a gate length of 3  $\mu$ m and a source/drain (S/D) spacing of 9  $\mu$ m. Subsequent optimization of the device geometry using a recessed-gate structure to decrease access resistance resulted in a peak transconductance of 73 mS/mm in a 0.5- $\mu$ m gate-length device [15]. This performance is comparable to the best FETs made from BaSnO<sub>3</sub> [16], another high-mobility perovskite with a lower bandgap, and roughly 15 $\times$  higher transconductance than comparable FETs made from SrTiO<sub>3</sub> [17]. This performance

suggests that SSO devices might be suitable for operation at RF frequencies, yet the high-frequency performance of SSO FETs has yet to be studied. In fact, to our knowledge, only one study of RF performance on perovskite-based FETs has been reported in the literature to date. In that work [18], the frequency performance of all-oxide FETs on LaAlO<sub>3</sub>/SrTiO<sub>3</sub> channels was reported. Those devices had extrinsic cut-off frequency,  $f_t$ , and maximum oscillation frequency,  $f_{max}$ , of 13.5 MHz and 28.8 MHz, respectively. These modest values are a result of the low mobility in SrTiO<sub>3</sub>, as well as the relatively long gate length of 4  $\mu$ m.

In this work, we fabricate and demonstrate RF SSO MESFETs with bi-layer SSO films grown by radical-based hybrid molecular beam epitaxy (MBE) with GHz-level performance. We utilize the same recessed-gate structure

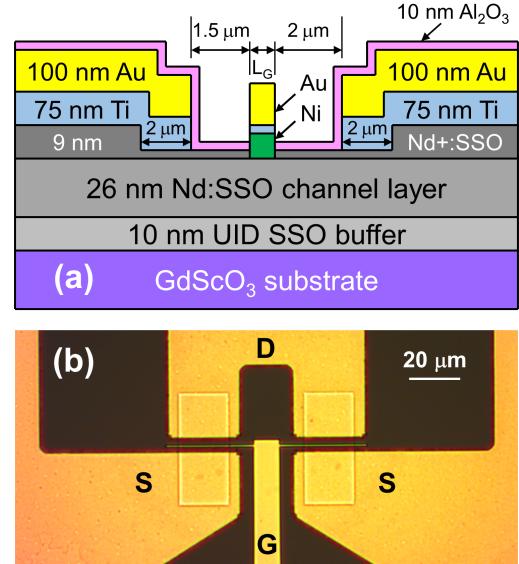

FIG 1. (a) Cross-sectional schematic of the SSO MESFET after fabrication. The relevant lateral dimensions are depicted, where the source (drain) is on the left (right) side. (b) Optical image of the RF SSO MESFET with  $L_g$  = 0.5  $\mu$ m,  $L_{ds}$  = 4  $\mu$ m and  $W_g$  = 2  $\times$  20  $\mu$ m in a GSG configuration.

Manuscript received October 17, 2020. This work was primarily supported by the Air Force Office of Scientific Research through Award Number FA9550-19-1-0245, in part by the National Science Foundation (NSF) through the University of Minnesota MRSEC under Award Number DMR-2011401, and in part by the NSF through Award Number DMR-1741801. Portions of this work were conducted in the Minnesota Nano Center, which is supported by the NSF through the National Nanotechnology Coordinated Infrastructure (NNCI) under Award Number ECCS-2025124.

J. Wen, V. R. S. K. Chaganti and S. J. Koester are with the Department of Electrical and Computer Engineering, University of Minnesota, Minneapolis, MN 55455 USA (e-mail: skoester@umn.edu).

T. K. Truttmann, F. Liu, and B. Jalan are with the Department of Chemical Engineering and Materials Science, University of Minnesota, Minneapolis, MN 55455 USA.

described in [15], but utilize devices configured in a ground-signal-ground (GSG) geometry for the purpose of RF characterization. These devices, with gate length,  $L_G$ , of 0.5  $\mu\text{m}$  and a S/D spacing of 4  $\mu\text{m}$ , have  $f_T = 1.31$  GHz and  $f_{\max} = 3.25$  GHz after de-embedding.

## II. DEVICE FABRICATION

The thin-film growth process is the same as that used in [15]. The epitaxial SSO films used in this work consisted of a 10 nm unintentionally-doped (UID) SSO, a 26 nm Nd:SSO channel layer and a 9 nm Nd<sup>+</sup>:SSO cap layer grown on the top of a highly insulating GdScO<sub>3</sub> substrate by radical-based hybrid MBE technique [9],[19]. The channel layer has an effective doping concentration of  $2.3 \times 10^{19} \text{ cm}^{-3}$  and mobility of 28  $\text{cm}^2/\text{Vs}$  according to separate van der Pauw measurements performed on a 26 nm single layer SSO sample grown under the same Nd source temperature. The same measurement was not directly performed on the heavily doped cap layer, however, the doping concentration is expected to be  $> 10^{20} \text{ cm}^{-3}$ .

The MESFETs fabrication also followed the procedure in [15]. After mesa isolation, the devices underwent an initial recess process, where a portion of the heavily doped cap layer, 2  $\mu\text{m}$  larger than the source and drain spacing on each side, was partially etched by reactive ion etching (RIE). Ti (75 nm) / Au (100 nm) metallization was then evaporated and lifted off to form source and drain contacts. Next, a 10-nm Al<sub>2</sub>O<sub>3</sub> passivation layer was deposited using atomic layer deposition, followed by the gate lithography, a wet-etch to remove the Al<sub>2</sub>O<sub>3</sub>, and a second RIE to remove the remaining  $\sim 3$  nm heavily doped layer under the gate. Finally, the gate metal consisting of Ni (65 nm) / Ti (10 nm) / Au (80 nm) was evaporated and lifted off. The separation of the S/D Ohmic contacts,  $L_{DS}$ , was 4  $\mu\text{m}$ , and  $L_G$  was 0.5  $\mu\text{m}$ , where the gate was offset by 0.25  $\mu\text{m}$  closer to the source, to decrease the parasitic source resistance. The device was arranged in a GSG configuration for RF characterization and had a total gate width 40  $\mu\text{m}$  ( $2 \times 20 \mu\text{m}$ ). A schematic cross-sectional diagram and top-view micrograph of the completed device are shown in Figs. 1(a) and 1(b), respectively.

## III. RESULTS

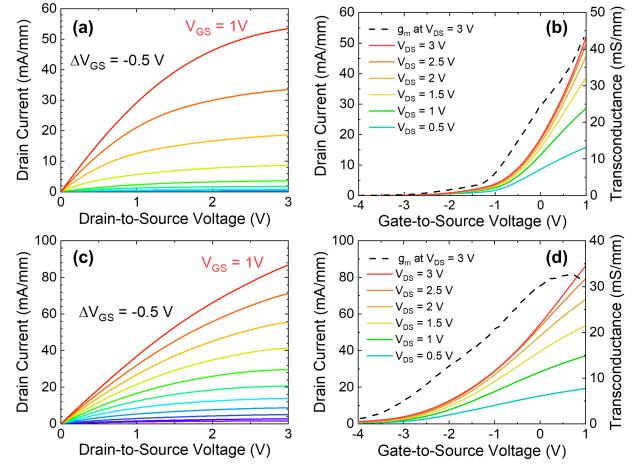

The DC measurements were performed in vacuum at room temperature using a Keysight B1500A semiconductor parameter analyzer. Two sets of DC measurements, one right before and one immediately after RF measurement, were performed and the results are shown in Fig. 2. Prior to RF characterization, the SSO MESFET showed good saturation in its output characteristic with peak drive current of 53 mA/mm and a low output conductance,  $g_o$ , of 4.2 mS/mm. The transfer characteristic showed slightly depletion-mode behavior, with a threshold voltage of  $-0.9$  V. While a peak in  $g_{\text{next}}$  is not obtained,  $g_{\text{next}}$  reached a maximum value of 43.2 mS/mm at  $V_{GS} = +1$  V and  $V_{DS} = +3$  V. Compared to the results above, the DC measurements performed after the RF measurements had a more negative threshold of  $-2.7$  V, along with a softer turn-off behavior. The maximum drive current was 87 mA/mm, with the

FIG 2. (a) Output characteristic and (b) transfer characteristic for the SSO MESFET with  $L_G = 0.5 \mu\text{m}$  and  $L_{DS} = 4 \mu\text{m}$  before RF measurements; (c) Output characteristic and (d) transfer characteristic for the same device after RF measurements.

peak  $g_{\text{next}}$  32.6 mS/mm.

While the results in Fig. 2 show that the device has some degree of threshold instability, they provide a general guide for understanding the RF measurement results. We believe the DC measurements performed prior to the RF characterization shown in Figs. 2 (a)-(b) are more reflective of the device state during RF characterization, as we will show later. While previous devices with Ni gates showed good threshold stability when measured at relatively low  $V_{DS}$  values [15], the devices reported here showed a higher degree of drift, similar to the Pt-gate devices reported in [15]. While the origin of this phenomenon requires further study, we do note that the devices in Fig. 2 had been exposed to air for an extended period between fabrication and measurement.

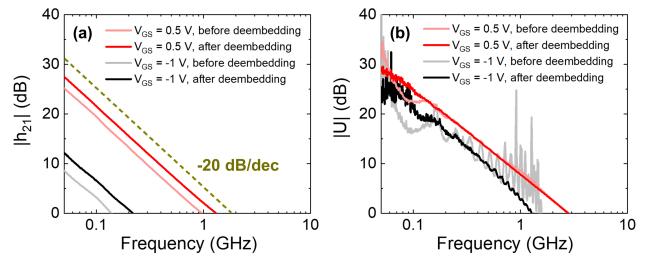

Two-port RF characterization was performed in air at room temperature using a Keysight E5063A vector network analyzer (VNA) with frequency ranging from 100 kHz to 18 GHz. The two ports on the VNA were to the gate and drain terminals. A bias tee was employed to mix the DC bias and RF input on each port. The VNA was calibrated using on-wafer open-short-load-thru structures on an impedance-standard substrate. In order to deembed extrinsic elements, s-parameter measurements on dummy open and short pad structures was performed. The short-circuit current gain ( $h_{21}$ ) and Mason's unilateral gain ( $U$ ) vs. frequency at  $V_{DS} = +3$  V and two different  $V_{GS}$  values are

FIG 3. (a)  $|h_{21}|$  and (b)  $|U|$  vs. frequency before and after deembedding at  $V_{DS} = +3$  V and two different  $V_{GS}$ . Note that at  $V_{DS} = +3$  V and  $V_{GS} = +0.5$  V the device shows maximum intrinsic  $f_T$  of 1.31 GHz. Deembedding minimizes the reflections in the  $|U|$  plot, especially for lower  $V_{GS}$ .

shown in Fig. 3 as an example. Results before and after deembedding are shown. The low-frequency reflections on the  $|U|$  vs.  $f$  plot are minimized after deembedding. We note that the extracted  $f_{\max}$  does not change much after deembedding, while  $f_T$  has a slight increase, a phenomenon that happens for all bias conditions. The relatively small change in  $f_T$  and  $f_{\max}$  is expected considering the relatively large device dimensions and the insulating nature of the  $\text{GdScO}_3$  substrate.

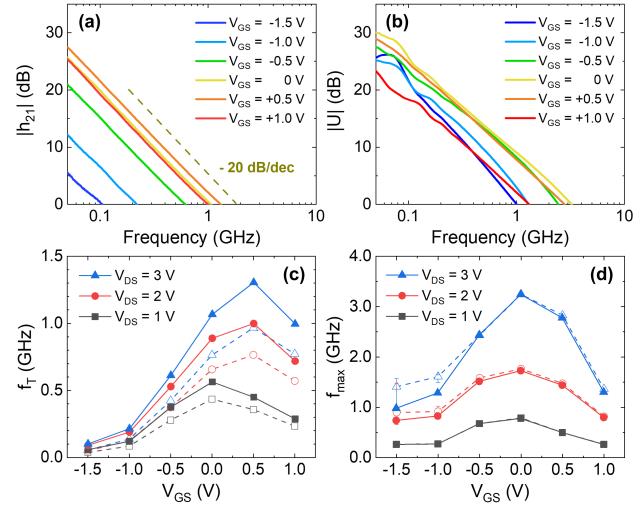

The deembedded  $|h_{21}|$  and  $|U|$  values at  $V_{DS} = +3$  V are plotted vs. frequency in Figs. 4(a) and 4(b), respectively. The current gain rolls off close to  $-20$  dB/decade, as expected. The extracted  $f_T$  and  $f_{\max}$  under different values of  $V_{DS}$ , before and after deembedding, are plotted vs.  $V_{GS}$  in Figs. 4(c) and 4(d), respectively. The degradation of  $f_T$  with decreasing  $V_{GS}$  is consistent with the  $g_{\text{mext}}$  trend from the pre-RF DC data (Fig. 2(b)), supporting our earlier statement that the DC measurements taken prior to RF characterization more closely reflect the device state during the RF measurements.

We also extracted the total gate capacitance,  $C_{\text{gg}}$ , and the high-frequency intrinsic  $g_{\text{m}}$ , using the (deembedded)  $s$ -parameter data. These results, shown in Table I below, provide a clearer explanation for trends in Fig. 4. The degradation of  $f_T$  at strong forward bias results from  $C_{\text{gg}}$  increasing faster than  $g_{\text{m}}$ , while the decrease in  $f_T$  at negative  $V_{GS}$ , is due to the rapid decrease in  $g_{\text{m}}$ , which cannot be offset by the lower gate capacitance.

Table I. Extracted intrinsic transconductance,  $g_{\text{m}}$ , and total gate capacitance,  $C_{\text{gg}}$ , from  $s$ -parameters at  $V_{DS} = +3$  V.

| $V_{GS}$ (V) | $g_{\text{m}}$ (mS) | $C_{\text{gg}}$ (fF) |

|--------------|---------------------|----------------------|

| +1.0         | 1.60                | 169                  |

| +0.5         | 1.31                | 124                  |

| 0.0          | 0.94                | 105                  |

| -0.5         | 0.44                | 85.0                 |

| -1.0         | 0.11                | 47.9                 |

| -1.5         | 0.038               | 34.1                 |

Both  $f_T$  and  $f_{\max}$  increase with increasing  $V_{DS}$  which is likely due to the higher electron velocity under larger electric field.  $f_T$  and  $f_{\max}$  generally increase with increasing  $V_{GS}$ , except at more positive values, where the increased gate capacitance causes  $f_T$  and  $f_{\max}$  to decrease. At  $V_{DS} = +3$  V, the device shows maximum  $f_T$  of 1.31 GHz (0.97 GHz) at  $V_{GS} = +0.5$  V, while the maximum  $f_{\max}$  of 3.25 GHz occurs at  $V_{GS} = 0$  V. The lower  $V_{GS}$  value for the peak  $f_{\max}$  compared to  $f_T$  can be attribute to the  $V_{GS}$  dependence of  $g_o$  and is consistent with the increased  $g_{\text{m}}/g_o$  ratio of 19 at  $V_{GS} = 0$  V compared to  $g_{\text{m}}/g_o = 17$  at  $V_{GS} = +0.5$  V (taken from first DC measurement). Similarly,  $f_{\max}$  also shows a  $V_{DS}$  dependence that is stronger than  $f_T$ , a trend that can be linked to the improved  $g_{\text{m}}/g_o$  ratio at higher  $V_{DS}$ .

While these results far exceed the best reported values for perovskites FETs in the literature, they still are lower than state-of-the-art  $\beta\text{-Ga}_2\text{O}_3$  [20],[21] and GaN [22] FETs. However, several design improvements are possible. These include reducing the gate length, utilizing a T-gate structure to minimize gate resistance, and improving the recessed gate design to improve robustness to degradation. This later point will enable operation at high values of  $V_{DS}$ , which is limited in

FIG 4. (a)-(b) Deembedded (a) short circuit current gain and (b) Mason's unilateral power gain vs. frequency at  $V_{DS} = +3$  V and various  $V_{GS}$ . (c)-(d) Extracted (c) cut-off frequency and (d) maximum oscillation frequency vs.  $V_{GS}$  at various  $V_{DS}$  values before (dashed line) and after (solid line) deembedding.

our current device design.

#### IV. CONCLUSION

In conclusion, we have performed RF measurements on high-mobility SSO MESFET demonstrating GHz performance. Devices with 0.5- $\mu\text{m}$  gate length achieve  $f_T$  of 1.31 GHz and  $f_{\max}$  of 3.25 GHz after de-embedding. This work provides insight into the potential of high-mobility perovskites for use in RF applications. Several design improvements should be possible to push the performance to even higher frequencies. In the future, the high-frequency ability can be integrated with other attractive properties of SSO such as its optical transparency and integration capability with ferroelectrics to realize novel high-speed device applications.

#### REFERENCES

- [1] D. D. Fong, G. B. Stephenson, S. K. Streiffer, J. A. Eastman, O. Auciello, P. H. Fuoss, and C. Thompson, "Ferroelectricity in ultrathin perovskite films," *Science*, vol. 304, pp. 1650-1653, 2004. doi: 10.1126/science.1098252.

- [2] H. Y. Hwang, Y. Iwasa, M. Kawasaki, B. Keimer, N. Nagaosa, and Y. Tokura, "Emergent phenomena at oxide interfaces," *Nat. Mater.*, vol. 11, pp. 103-113, 2012. doi: 10.1038/nmat3509.

- [3] T. Okuda, K. Nakanishi, S. Miyasaka, and Y. Tokura, "Large thermoelectric response of metallic perovskites:  $\text{Sr}_{1-x}\text{La}_x\text{TiO}_3$  ( $0 \leq x \leq 0.1$ )," *Phys. Rev. B*, vol. 63, 113104, 2001. doi: 10.1103/physrevb.63.113104.

- [4] T. Wolfram, S. Ellalioglu, "Electronic and optical properties of d-band perovskites," (Cambridge Univ. Press, 2006).

- [5] E. Baba, D. Kan, Y. Yamada, M. Haruta, H. Kurata, Y. Kanemitsu, and Y. Shimakawa, "Optical and transport properties of transparent conducting La-doped  $\text{SrSnO}_3$  thin films," *J. Phys. D Appl. Phys.*, vol. 48, 455106, 2015. doi: 10.1088/0022-3727/48/45/455106.

- [6] M. Wei, A. V. Sanchela, B. Feng, Y. Ikuhara, H. J. Cho, and H. Ohta, "High electrical conducting deep-ultraviolet-transparent oxide semiconductor La-doped  $\text{SrSnO}_3$  exceeding  $\sim 3000 \text{ S cm}^{-1}$ ," *Appl. Phys. Lett.*, vol. 116, 022103, 2020. doi: 10.1063/1.5128410.

- [7] H. Mizoguchi, H. W. Eng, and P. M. Woodward, "Probing the electronic structures of ternary perovskite and pyrochlore oxides containing  $\text{Sn}^{4+}$  or  $\text{Sb}^{5+}$ ," *Inorg. Chem.*, vol. 43, pp. 1667-1680, 2004. doi: 10.1021/ic034551c.

- [8] H. R. Liu, J. H. Yang, H. J. Xiang, X. G. Gong, and S. H. Wei, "Origin of the superior conductivity of perovskite Ba(Sr)SnO<sub>3</sub>," *Appl. Phys. Lett.*, vol. 102, 112109, 2013. doi: 10.1063/1.4798325.

- [9] T. Truttmann, A. Prakash, J. Yue, T. IE. Mates and B. Jalan, "Dopant solubility and charge compensation in La-doped SrSnO<sub>3</sub> films," *Appl. Phys. Lett.*, vol. 115, 152103, Jul. 2019. doi: 10.1063/1.5119272.

- [10] T. Wang, A. Prakash, Y. Dong, T. Truttmann, A. Bucsek, R. James, D. D. Fong, J. W. Kim, P. J. Ryan, H. Zhou, T. Birol, and B. Jalan, "Engineering SrSnO<sub>3</sub> phases and electron mobility at room temperature using epitaxial strain," *ACS Appl. Mater. & Inter.*, vol. 10, pp. 43802-43808, 2018. doi: 10.1021/acsami.8b16592.

- [11] T. Wang, L. R. Thoutam, A. Prakash, W. Nunn, G. Haugstad, and B. Jalan, "Defect-driven localization crossovers in MBE-grown La-doped SrSnO<sub>3</sub> films," *Phys. Rev. Mat.*, vol. 1, 061601, 2017. doi: 10.1103/PhysRevMaterials.1.061601.

- [12] A. Prakash, and B. Jalan, "Wide bandgap perovskite oxides with high room-temperature electron mobility," *Adv. Mater. Inter.*, vol. 6, 1900479, 2019. doi: 10.1002/admi.201900479.

- [13] E. Mikheev, B. Himmelotglu, A. P. Kajdos, P. Moetakef, T. A. Cain, C. G. Van de Walle, and S. Stemmer, "Limitations to the room temperature mobility of two- and three-dimensional electron liquids in SrTiO<sub>3</sub>," *Appl. Phys. Lett.*, vol. 106, 062102, 2015. doi: 10.1063/1.4907888.

- [14] V. R. S. K. Chaganti, A. Prakash, J. Yue, B. Jalan, and S. J. Koester, "Demonstration of a Depletion-Mode SrSnO<sub>3</sub> n-Channel MESFET," *IEEE Elect. Dev. Lett.*, vol. 39, pp. 1381-1384, Sep. 2018. doi: 10.1109/LED.2018.2861320.

- [15] V. S. K. Chaganti, T. K. Truttmann, F. Liu, B. Jalan, and S. J. Koester, "SrSnO<sub>3</sub> field-effect transistors with recessed gate electrodes," *IEEE Elect. Dev. Lett.*, vol. 41, pp. 1428-1431, Sep. 2020. doi: 10.1109/led.2020.3011058.

- [16] J. Cheng, H. Yang, C. Wang, N. Combs, C. Freeze, O. Shoron, W. Wu, N. K. Kalarickal, H. Chandrasekar, S. Stemmer, S. Rajan, and W. Lu, "Nanoscale etching of perovskite oxides for field effect transistor applications," *J. Vac. Sci. Technol. B*, vol. 38, 012201, 2020. doi: 10.1116/1.5122667.

- [17] A. Verma, S. Raghavan, S. Stemmer, and D. Jena, "Au-gated SrTiO<sub>3</sub> field-effect transistors with large electron concentration and current modulation," *Appl. Phys. Lett.*, vol. 105, 113512, 2014, doi: 10.1063/1.4896275.

- [18] Q. Liu, L. Dong, Y. Liu, R. Gordon, P. D. Ye, P. Fay, and A. Seabaugh, "Frequency response of LaAlO<sub>3</sub>/SrTiO<sub>3</sub> all-oxide field-effect transistors," *Solid-State Electron.*, vol. 76, pp. 1-4, Oct. 2012, doi: 10.1016/j.sse.2012.05.044.

- [19] A. Prakash, J. Dewey, H. Yun, J. S. Jeong, K. A. Mkhoyan, B. Jalan, "Hybrid molecular beam epitaxy for the growth of stoichiometric BaSnO<sub>3</sub>," *J. Vac. Sci. Technol. A*, vol. 33, 060608, Oct. 2015. doi: 10.1116/1.4933401.

- [20] A. J. Green, K. D. Chabak, M. Baldini, N. Moser, R. Gilbert, R. C. Fitch, G. Wagner, Z. Galazka, J. McCandless, A. Crespo, K. Leedy, and G. H. Jessen, "β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs for Radio Frequency Operation," *IEEE Electron Device Lett.*, vol. 38, pp. 790-793, Jun. 2017. doi: 10.1109/LED.2017.2694805.

- [21] Z. Xia, H. Xue, C. Joishi, J. McGlone, N. K. Kalarickal, S. H. Sohel, M. Brenner, A. Arehart, S. Ringel, S. Lodha, W. Lu, and S. Rajan, "β-Ga<sub>2</sub>O<sub>3</sub> Delta-Doped Field-Effect Transistors With Current Gain Cutoff Frequency of 27 GHz," *IEEE Elect. Dev. Lett.*, vol. 40, pp. 1052-1055, Jul. 2019. doi: 10.1109/LED.2019.2920366.

- [22] Y. Tang, K. Shinohara, D. Regan, A. Corrion, D. Brown, J. Wong, A. Schmitz, H. Fung, S. Kim, and M. Micovic, "Ultrahigh-Speed GaN High-Electron-Mobility Transistors with  $f_T/f_{max}$  of 454/444 GHz," *IEEE Elect. Dev. Lett.*, vol. 36, pp. 594-551, Jun. 2015. doi: 10.1109/LED.2015.2421311.