#### **PAPER**

# Fabrication and non-destructive characterization of through-plastic-via (TPV) in flexible hybrid electronics

To cite this article: Kartik Sondhi et al 2021 Flex. Print. Electron. 6 025001

View the article online for updates and enhancements.

240th ECS Meeting ORLANDO, FL

Orange County Convention Center Oct 10-14, 2021

Abstract submission deadline extended: April 23rd

**SUBMIT NOW**

# Flexible and Printed Electronics

#### RECEIVED

5 December 2020

#### REVISED

9 February 2021

ACCEPTED FOR PUBLICATION 2 March 2021

PUBLISHED

25 March 2021

#### **PAPER**

# Fabrication and non-destructive characterization of through-plastic-via (TPV) in flexible hybrid electronics

Kartik Sondhi<sup>1</sup>, Sai Guruva Reddy Avuthu<sup>2</sup>, Jörg Richstein<sup>2</sup>, Z Hugh Fan<sup>3,4</sup> and Toshikazu Nishida<sup>1</sup>

- <sup>1</sup> Interdisciplinary Microsystems Group, Department of Electrical and Computer Engineering, University of Florida, Gainesville, FL, United States of America

- Jabil Inc., St. Petersburg, FL, United States of America

- Interdisciplinary Microsystems Group, Department of Mechanical and Aerospace Engineering, University of Florida, Gainesville, FL, United States of America

- <sup>4</sup> J Crayton Pruitt Family Department of Biomedical Engineering, University of Florida, Gainesville, FL, United States of America

E-mail: nishida@ufl.edu

Keywords: flexible hybrid electronics, via fabrication, via filling, via stresses

Supplementary material for this article is available online

#### Abstract

Flexible hybrid electronics (FHE) have been gaining interest in recent years as this technology has the potential to become a low-cost, mechanically pliable sister technology for multilayer printed circuit boards (PCBs). One of the limitations of rigid PCB is low endurance to mechanical bending, this limitation poses a threat to the efficacy for wearable applications. During bending, a substrate experiences both compressive and tensile stress. These stresses are similar in magnitude but opposite in direction. This difference in directionality creates a non-linear stress gradient in a via which impacts the structural integrity, endurance and bending reliability of a circuit during its operation. Additionally, as flexible substrates can be bent to a higher bending radius, the magnitude of maximum extrinsic stresses observed on flexible substrates could be higher than the stress observed on rigid substrates. Hence, the reliability and mechanical compliance of through-hole-plastic-vias for reliable flexible circuits need to be understood. In this study, we have developed a process to create vias on flexible substrates using a rapid commercial laser (Nd-YaG laser) to study the effects on via resistance due to three different variables—bending stresses, via diameter and via length. A novel non-destructive approach (CT-scanner) was used to scan the via structures and determine the filling for all via diameters from 50 to 450  $\mu$ m and via lengths of 7, 10 mils. Two different configurations of vias were used to measure and analyze the effect of mechanical cycling on via resistance and via filling. This demonstration of electrical and mechanical testing of vias and novel methodologies for via filling, and via electrical resistance can contribute to better design and fabrication guidelines of multi-layer FHE circuits.

# 1. Introduction

The development of complex flexible hybrid electronics (FHE) devices can include multiple conductive and insulating layers and is driven by demands for multi-functional wearable and conformable applications [1, 2]. While the essential feature of a via is the same as that used in rigid multi-layer printed circuit boards (PCBs) [3], there are additional design considerations to support flexibility required in FHE applications. Even in rigid/flexible traditional PCBs, vias have been identified as one of the primary failure node of devices when exposed to external [4] and/or

intrinsic stresses during normal operation. Furthermore, traditional FR-4 substrates used in PCBs have not been designed for bending. However, one of the primary objective of substrates for FHE is endurance to high bending radii. Therefore, it is important to investigate models and perform studies that are more relevant for flexible substrates. This understanding of the effects of bending on flexible substrates with through-plastic vias (TPV) can enable more reliable devices for IOT and wearable electronics.

Conductive via fabrication includes the construction of a via hole and hole filling/lining with conductive material. Typical methods of via hole fabrication

include: (a) punching [5, 6], (b) laser micromachining [7, 8], and (c) laser drilling [8]. All these methods have been employed for fabricating through-holes in PCBs and in flexible substrates with modified parameters [9-12]. One of the modified parameters is a lower laser power used for laser drilling through softer flexible substrates than the rigid PCBs [10]. Commonly used substrates for FHE include organic polymers such as polyethylene terephthalate (PET, Young's modulus = 2 GPa) [2, 13] and polyimide (PI, Young's modulus, cross linked PI polymers have Young's moduli ranging from 2.8 to 10 GPa) [14, 15]. In contrast, the substrate frequently used in rigid PCBs, known as FR-4 and related classifications, has a Young's modulus  $\sim$ 21–24 GPa and consists of fiberglass-reinforced epoxy laminates [16].

For FHE, conductive TPVs are typically filled while screen printing the conductive traces. Therefore, the via filling for TPV is dependent on multiple material parameters including the (a) surface energy of substrate, (b) surface tension of ink, and (c) ink viscosity, and geometrical parameters such as (d) via diameter and (e) via aspect ratio = height/diameter. As the aspect ratio increases, it becomes more difficult to fill the via. Techniques used to increase the ink throughput include (a) increasing the ink temperature [17], (b) vibrating the squeegee used in screen printing [18], and (c) modifying the squeegee parameters [19]. Additional techniques include a combination of electroless and electroplating similar to plated through-hole filling in PCBs [20]. These techniques can also be applied for FHE fabrication, however these methods add additional steps which makes the process cumbersome and expensive from the perspective of high-volume device manufacturing.

Traditionally, via filling inspection has been performed using scanning electron microscopy (SEM) [21, 22]. This inspection filling provides a qualitative estimate into via's mechanical and electrical performance such as current carrying capacity [23], crosstalk [24], and localized heating [25]. Via filling can be calculated through the ratio of volume of material filled inside the via to the total volume of the cylindrical via. Sample preparation for SEM includes sectioning and potting of the via [26]. This sectioning could be performed using focused ion beam [27] and/or sample milling. One of the disadvantages of using these methods is the cracks caused by localized heating [27] which may lead to loss of filled material. Hence, non-destructive approaches are preferred for via filling inspection. Approaches such as computed tomography (CT), uses the principle of x-ray imaging and restoration for examining different substrate layers and components, do not require sectioning and are thus more suitable for vias on flexible substrate.

Stress factors such as bending can severely impact the performance of a via and resultantly impact the connected circuits reliability. Industry standards on reliability testing of PCBs include (a) temperature and (b) humidity cycling [28, 29]. These stress factors can also affect the reliability of TPV. In addition to these, another limitation to FHE device reliability is the extrinsic stress induced due to bending. Bending stress on PCB can be damaging for substrate and resultantly the circuit reliability. Modeling of such stresses has been investigated for PCB and similar investigations on FHE substrates becomes complex because of the non-linearity in visco-elastic properties [30]. Therefore, the bending stress models available for PCBs cannot be applied implicitly for FHE. As reported by Jonnalagadda et al [31], in PCBs the elastic modulus and volume of the material filled in the via are factors that impact the stress observed on a via and can lead to via delamination. Therefore, it can be inferred, there could be a direct relationship between the bending stress and volume of the material in TPV via. Additionally, bending stress induces a strain on the via. This strain can be either a negative strain (concave/compressive side) or a positive strain (convex/tensile). As described by Jonnalagadda et al [31] the stress inside a via follows a non-linear behavior. The stress is compressive on concave plane, tensile on the convex plane and inside the via it transitions from compressive to tensile. Therefore, directly relating the strain to the via resistance requires extensive calculations using non-linear finite element modeling. Hence, investigation of parameters that control the volume of material filled inside the via can provide a simplistic insight in reliability of TPVs.

In this study, the effects of via diameter, substrate lengths and via filling were used to evaluate the mechanical and electrical reliability of through plastic vias. Quantity and quality of via filling were evaluated for different vias using a CT-Scanner. Cyclic strain tests were studied to evaluate the effect of bending stress on vias with different fillings. These investigations present a detailed effect of factors that cause a change in via performance based on via parameters such as via filling and aspect ratio. This study was also extended to compare the via performance for 100% filled vias and a similar trend of via reliability was observed. These demonstrations of via filling calculation, testing methodologies and, bending analysis help provide design guidelines of FHE circuits and devices.

# 2. Experimental procedures and methods

# 2.1. Screen printing, inks and substrates

Screen printing was done using an automatic screen printer (Model No: 293111, DEK Horizon 03i, USA). Constant squeegee speed, squeegee pressure and substrate plate's vacuum were used for printing the flexible silver ink and comparing the filling of all the vias. Print/flood mode was used for printing with a constant print speed of 10 mm s<sup>-1</sup>. Screen printing was performed on different substrates using squeegee pressure of 4.5 N. Printing process conditions that were studied have been

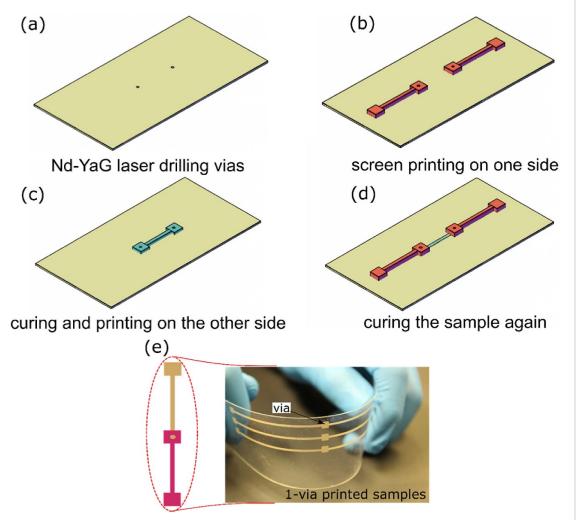

**Figure 1.** Fabrication process for via fabrication, (a) laser drilling vias, (b) screen printing silver ink on one side, (c) curing and printing on the other side of the substrate, (d) printing on the other side to make a contact between the two vias. Images of samples with (e) one via.

shown in supplementary section (available online at stacks.iop.org/FPE/6/025001/mmedia). Each print run was done using the print/print mode where each run corresponds to two successive screen prints in a back-and-forth motion. This method was chosen because it maximizes the ink volume that can pass through the screen in a single run.

The silver ink used in this study has 66% particle content and a surface tension of 25 N cm<sup>-1</sup>, the particle size of the silver in the ink ranges from 1 to 5  $\mu$ m. The silver ink is cured at 112 °C for 20 min. Flexible PET substrates with two different thickness, 7 mil ( $\sim$ 178  $\mu$ m) and 10 mil ( $\sim$ 254  $\mu$ m), were used in this study. Both substrates have a surface energy of 28  $\pm$  2 mN m<sup>-1</sup>, measured using a contact-angle goniometer (Model No. 250, Rame-Hart Instrument Co., USA). Other characteristics of the substrate used are high crease resistance and reworkability of the substrate.

Figure 1 shows the protocol used for printing and depositing the test sample. Figures 1(a)–(d) show the four steps used in the fabrication of the test structure. The detailed process steps are discussed below.

#### 2.2. Via fabrication

2.2.1. Via hole fabrication

Hole construction on PET substrate is performed using a laser ablation tool (figure 1(a)). Via holes were laser drilled with a picosecond Nd-YaG laser (Oxford Lasers, UK). Drilling using a laser requires control of two parameters, (a) number of passes/steps down and (b) laser power. Effective control of these parameters results in a well-defined hole for the via and less possibility of excessive heating and burning. Table 1 shows the different values of number of passes and laser power that were tested for the two PET thicknesses. In this study, the number of passes corresponds to the number of times the laser cuts the circular surface of the hole at a fixed height. The step down is the incremental step height used to cut the hole after the fixed number of cut passes are complete. The samples are then washed with IPA and dried post-drilling since the laser may cause burning and result in carbon residue. Screen printing and subsequent curing of silver ink is done on both sides of the vias (figures 1(b) and (c)).

| Table 1. Results for | different attem | nots for cutting | precise via | holes in PET sheet. |

|----------------------|-----------------|------------------|-------------|---------------------|

|                      |                 |                  |             |                     |

| Run# | Number of passes/step down (µm) | Laser power % (total power = 3.25 W) | Expected hole diameter ( $\mu$ m) | Observed mean hole diameter $(\mu m)$ /Shape of hole (circular/non-circular) | Burning? |

|------|---------------------------------|--------------------------------------|-----------------------------------|------------------------------------------------------------------------------|----------|

| 1    | 100/50                          | 1                                    | 250                               | 247/circular                                                                 | No       |

| 2    | 100/50                          | 1                                    | 50                                | 42/circular                                                                  | No       |

| 3    | 50/50                           | 1                                    | 250                               | 240/non-circular                                                             | No       |

| 4    | 50/50                           | 1                                    | 50                                | 39/non-circular                                                              | No       |

| 5    | 100/50                          | 5                                    | 250                               | 249/circular                                                                 | No       |

| 6    | 100/50                          | 5                                    | 50                                | 51/circular                                                                  | No       |

| 7    | 50/50                           | 5                                    | 250                               | 248/circular                                                                 | No       |

| 8    | 50/50                           | 5                                    | 50                                | 49/circular                                                                  | No       |

| 9    | 100/50                          | 7.5                                  | 250                               | 252/circular                                                                 | Yes      |

| 10   | 100/50                          | 7.5                                  | 50                                | 56/circular                                                                  | Yes      |

| 11   | 50/50                           | 7.5                                  | 250                               | 250/circular                                                                 | Yes      |

| 12   | 50/50                           | 7.5                                  | 50                                | 54/circular                                                                  | Yes      |

Table 1 shows the number of passes and laser power that were used for cutting the vias. Drilling was performed below 7.5% laser power to avoid burning in PET. The final drilling configuration used for cutting the via hole was 100/50 (number of passes/step down ( $\mu$ m)) and 5% power. These values were chosen because they provided the best cutting profiles using the Nd-YaG laser.

#### 2.2.2. Via hole filling

Via hole filling was done using screen printing in the print/flood mode using the screen layout described in section 2.1 (figures 1(b)–(d)). A constant squeegee pressure was applied on the screen and maintained by the screen printer. This allowed consistent volumes of ink to pass through the screen in each 'print' pass. Maintaining the squeegee speed and pressure are essential for maintaining repeatable filling in vias. Different industry best practices were followed for printing these vias, therefore all the relevant parameters were optimized before printing.

Syringe filling was used to fill via holes completely irrespective of geometry to obtain a baseline for electrical and mechanical measurements. In this method, a syringe was filled with a conductive ink and a constant pressure of 2.5 bar for 10 s was used to fill the holes individually.

Figure 1(d) shows the final test structure with two vias. The test patterns were also designed for a single via (figure 1(e)). The one-via sample was used for calculation of fill ratio, while the two-via samples were used for via resistance measurement and averaging.

#### 2.3. Via analysis and via filling estimation

Non-contact via analysis was performed using a CT Scanner (CT-Scanner GE Model no.: V|TOME|X M 240). A diamond x-ray generator tube with 240 kV microfocus was used for via filling inspection and analysis. The software VG Studio max was used for CT scan reconstruction and characterization of silver volume and via filling. The latter is accomplished

from the reconstructed 3D profile of the via which contains a set of multiple 2D equidistant slices of the whole via. The via filling is calculated using a central 2D slice of the 3D reconstructed CT-scanned via. ImageJ is used to extract the x and y coordinates of the silver edges. These (x, y) coordinates are then converted into coordinates which are fitted into a parabolic equation (f(x)). The silver volume,  $V_{\rm silver}$ , is then calculated using equation (1),

$$V_{\text{silver}} = \int f(x)^2 \tag{1}$$

and the via filling, vf, is determined from the ratio of the silver volume to the via volume,

$$vf = \frac{V_{\text{silver}}}{\pi r^2 l} \tag{2}$$

where r is the via radii, l is the via length.

# 2.4. Mechanical cycling and resistance measurements

Mechanical cycling was performed using the universal testing machine, Mark-10 (Model No. ESM303, Mark-10, USA). The cycling was controlled using a MATLAB code, and the cycling frequency, *f*, was kept constant at 0.0833 cycles s<sup>-1</sup> for all the measurements.

The via resistance was extracted from the net trace resistance using a four-wire method on a two-via test sample as shown in figure 2. Each resistance was measured using an Agilent 34970 A using the four-wire method to eliminate the parasitic resistance of the cables. During cycling, the resistance was measured at a frequency of f/4. The via resistance is calculated using equation (3)

$$R_{\text{vias}} = \frac{R_{\text{P6}-\text{P1}} - (R_{\text{P1}-\text{P2}} + R_{\text{P3}-\text{P4}} + R_{\text{P5}-\text{P6}})}{2}. \quad (3)$$

where the resistance between ports P1 and P2, P5 and P6, and P3 and P4 are simultaneously measured in a four-wire configuration using the Agilent 34 970 A.

Figure 2. Via resistance extraction method to extract via resistance from net trace resistance using four-wire method, (a) two-via printed sample and (b) measurement schematic.

#### 3. Results and discussion

# 3.1. Characterization of via filling

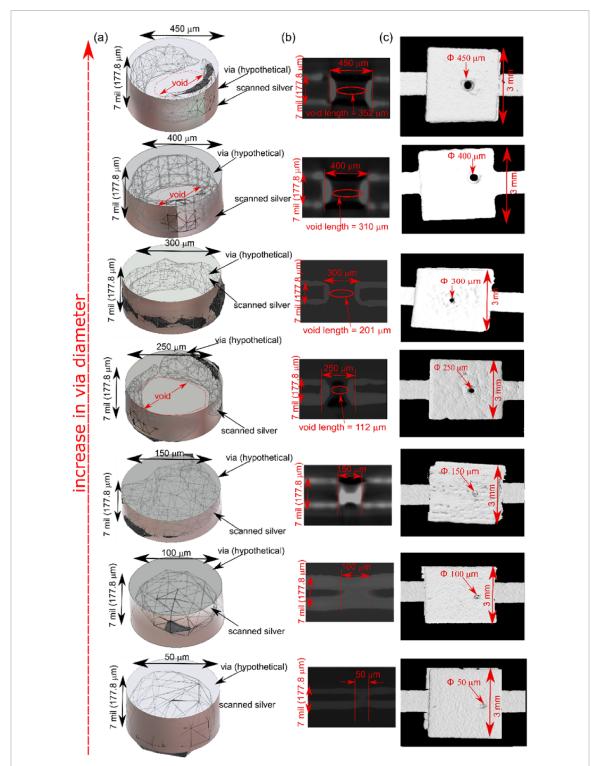

Three different views of TPV fabricated using the process flow given in figure 1 are shown in figure 2. The views include seven different via diameters ranging from the 450  $\mu$ m to 50  $\mu$ m. The 3D wire mesh representations of CT-scans are shown in figure 3(a) superimposed on the equivalent cylinder of each via diameter. For visibility of the wire mesh, the scale of all vias are normalized to diameter. Figure 3(b) shows a 2D slice of the 3D mesh taken at the geometric center of the via. All the via images shown in figure 3(b) were processed to increase the brightness by 51%. Note: A few images exhibit shaded regions in the background which is an artifact of CT-scanning (beam hardening) [32]. Additional post-processed CT scan images are included in supplementary materials that have higher brightness and contrast. An optical image of the sample is shown in figure 3(c).

CT-scanning provides details into via morphology. Figures 3(a) and (b) show the discontinuities and surface topology in the vias after fabrication and before bending. Images were also taken for vias after bending (not shown), and no significant change was observed. The resolution limit of the CT Scanner is  $\sim 1 \ \mu m$  As shown in these figures, the three smallest diameter vias do not have any central void while the four largest diameters have a void. Possible causes of the voids include removal of volatile matter, low adhesion between ink and substrate, or ink falling off from the via due to insufficient via hole wetting. A previously published study by Kujala et al [33] presented a similar observation of screen-printed inks residing only in the walls for vias >150  $\mu$ m. According to the ink manufacturer, the adhesion of the ink to the PET substrate is high. Since the percentage of volatile solvent is less than 10%, the voids in the larger diameter vias may be primarily caused by the ink flow profile during printing. The void diameter shown in figure 3(b) can also be seen in the figure 3(c). Furthermore, each figure shown in figures 3(a)–(c) is essential for understanding the via morphology from a different perspective. The different morphology can be understood using 450  $\mu$ m via diameter as an example. As shown in figures 3(b) and (c), the filling in the 450  $\mu$ m via diameter can be claimed to be symmetric. However, this claim cannot be substantiated when observing figure 3(a). Slight irregularities of silver observed in the edges are present. Hence, each figure individually is essential for a complete via filling and via morphology analysis.

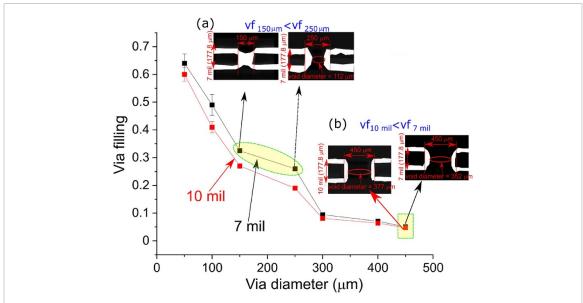

Both aspect ratio and print parameters (squeegee pressure and print speed) affect via filling. Figure 4 shows the data for via filling for different substrate lengths and diameters. The largest via filling (0.6) is observed for smallest diameter via (50  $\mu$ m) and smaller substrate thickness (7 mil). The inset images shown in figures 4(a) and (b) are the 2D side CT-scanned images that are shown in figure 3.

Aspect ratio of the via play an important role for governing via filling. Additionally, the material properties of the ink such as viscosity, and surface energy of substrate. The ink thickness after printing was observed to be  $\sim$ 12  $\pm$  5  $\mu$ m and  $\sim$ 9  $\pm$  2  $\mu$ m after curing. After each pass, the ink transfers into the via and deposits on the sidewalls. Since the dry/cured ink thickness is 18% of the smallest 50  $\mu$ m diameter via, it follows that the ink settles on the sides of the via instead of plugging the whole via. As expected, via filling is largest for the smallest diameter and decreases with increasing diameter. After two squeegee passes on top and bottom, the via filling is 0.6 for 50  $\mu m$  diameter via on 7 mil thick substrate. It also depends on the volume of the fluid, with each squeegee pass only a fixed volume of ink passes through the screen and settles onto the substrate after curing. Therefore, for the same ink volume passing through a via, the via filling will be higher for a smaller diameter via (vf<sub>150  $\mu$ m</sub> < vf<sub>250  $\mu$ m</sub>, for vias with the same length), as the curing conditions are maintained same. This discussion can also be extended to compare the filling of vias for different via lengths. For a longer via, the ink will spread and settle more along the length. This will reduce the thickness of the conductive ink inside the via, causing a reduction in filling for a longer via (vf $_{10\;mil}$  > vf $_{7\;mil}$ ). The aspect ratio defined as via length/via diameter is an important geometrical

**Figure 3.** Images obtained from CT-Scanner with seven different diameters. (a) 3D images of scanned silver, (b) 2D side view images of the scanned silver and (c) silver pads. These images are of vias after printing and curing.

parameter, which is dependent on both via diameter and length. The aspect ratio also assists in simplifying the data representation and analysis by combining the two geometrical variables that affect via filling.

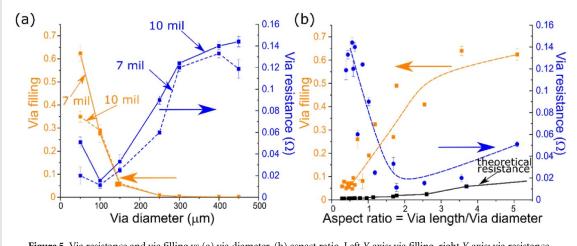

# 3.2. Experimental via resistances

Besides estimation of via filling, the resistance of the partially filled via is an important operational parameter. The via resistance and via filling are plotted versus via diameter in figure 5(a) for two different substrate thicknesses (via lengths) and with respect to the aspect ratio (via length/via diameter) in figure 5(b). The theoretical resistance for a completely filled via is also shown. If the vias are completely filled, the via resistance would be smallest for the shortest length/largest diameters (smallest aspect ratio). However, as noted above, these smallest aspect ratio vias also have the least via filling. Hence, the deviation of the theoretical resistance from the measured via resistance is largest for these small aspect

Figure 4. Via filling for different diameter and substrate lengths. Insets: 2D side view images to compare the effect of (a) different via diameter (a smaller diameter will have lower via filling), and (b) different via length (a larger length will have lower via filling).

Figure 5. Via resistance and via filling vs (a) via diameter, (b) aspect ratio. Left Y axis: via filling, right Y axis: via resistance.

ratio vias. In fact, the measured via resistance diverges from the theoretical resistance fairly closely below an aspect ratio of about 2. When the number of squeegee passes is increased, more ink fills inside the via, and the agreement between measured and theoretical resistance improves correspondingly. However, in this study we have used the same two squeegee passes for all via diameters. Hence, all vias being compared were printed using the same print parameter. The experimental via resistance will be dependent on the via filling and geometrical parameters while the theoretical via resistance is dependent only on the geometrical parameters (assuming 100% filling).

# 3.3. Cyclic resistance measurements

As reported by Hicks *et al* [34], cyclic bending causes a prolonged interfacial stress and can lead to formation of cracks within the via and subsequent crack propagation on interfaces [35]. In the aforementioned study, completely filled vias were

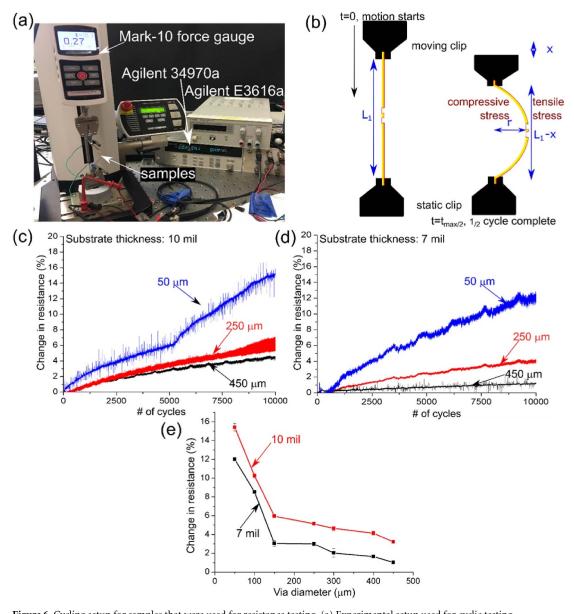

used. In this study, the effect of cycling bending on via resistance was investigated as a function of via filling. Figure 6(a) shows the test structure that was used for via cycling measurements. Figure 6(b) illustrates the bent and unbent substrate containing vias. Figures 6(c) and (d) show the percent change in resistance due to cyclic bending for three different via diameters. The increase in resistance shown in figures 6(c) and (d) is the raw data that was observed during cycling of the test structure for 10 000 cycles. Figure 6(e) summarizes the change in resistance for different via diameters after 10 000 cycles. It is observed that smaller diameter vias exhibited higher percentage change in resistance compared to the larger diameter vias. To understand possible reasons, it is noted that the smaller diameter vias had the highest via filling values.

As shown by Vasu *et al* [36], the stress profile on a structure such as the via in a flexible substrate is dependent on its orientation to the bending force.

**Figure 6.** Cycling setup for samples that were used for resistance testing. (a) Experimental setup used for cyclic testing, (b) schematic of setup showing the effect on via bending. Change in via resistance for (a) 10 mil PET and (b) 7 mil PET. (e) Change in via resistance for different via diameters after 10 000 bending cycles.

The concave side experiences a tensile stress while the convex side experiences a compressive stress. Since a via spans the two sides of the flexible substrate, the stress on each side creates a stress gradient across the via length. Furthermore, the amount of filling of the via affects the effective stiffness of the via. The above CT-Scan images showed that the 50  $\mu$ m via had much higher filling than the 450  $\mu$ m vias. Hence, the 50  $\mu$ m via is stiffer than the 450  $\mu$ m via. As indicated computationally, there is a higher stress concentration at the junction of the metal trace and 50  $\mu$ m via. The higher stress may lead to micro-cracks [35]. Hence, with cycling, the 50  $\mu$ m via would incur a larger increase in resistance compared to the 450  $\mu$ m via as seen in figure 5(e). Therefore, from the perspective of mechanical reliability, a lower via filling is a preferable condition for circuits that will be exposed to a cyclic bending

stress. Furthermore, as via filling is directly dependent on the aspect ratio, the latter can also be used to define the preferable condition for high mechanical endurance.

Another geometrical parameter that can affect via reliability is the curvature (=1/bending radii) induced due to the bending stress. As the bending tool used in this study (Mark-10) can be only used to control the motion in z-direction, the bending radii (1/curvature) is calculated using equation (3). The displacement of the moving clip has been represented through a variable z and has been shown in figure 5(b).

$$r = \frac{3\pi \left(\frac{l-z}{2}\right)^2}{\left(3l - 2\pi \left(\frac{l-z}{2}\right) + \sqrt{3l^2 + 6\pi l \left(\frac{l-z}{2}\right) - 5\left(\frac{\pi(l-z)}{2}\right)^2}\right)}$$

(4)

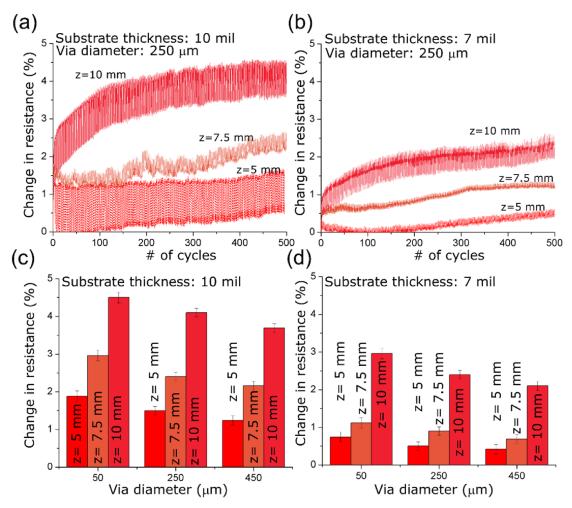

**Figure 7.** Change in resistance for vias for different values of z and 250  $\mu$ m via diameter with substrate thickness of (a) 10 mil PET, (b) 7 mil PET. Change in via resistance for different via diameters for (a) 10 mil PET and (b) 7 mil PET. All this data is for 500 cycles.

where r is the bending radii, and l is the substrate length. Ramanujan's approximation [37] was used for derivation of r. It is observed from equation (4) that an increase in the value of z leads to a decrease in bending radius. This reduction of bending radii will lead to a higher stress on the vias. Figures 7(a) and (b) shows the effect of bending stress on experimental via resistance for vias with a diameter of 250  $\mu$ m and length of 7 and 10 mils. As shown in equation (4), substrate length (L) also impacts the bending radii, hence the substrate length was kept constant for a consistent comparison between the via diameters. Figures 7(c) and (d) show the cumulative results for change in resistance for 50, 250 and 450  $\mu$ m via diameters after 500 cycles for 10 and 7 mils PET respectively. Three different values of z (5, 7.5 and 10 mm) were chosen for testing the effect of curvature.

As shown in figures 7(a) and (b), a higher increase of resistance is observed for smaller radii of curvature. As described by Moon *et al* [38], cyclic bending causes a corresponding cyclic change in resistance. This cyclic change in resistance has been shown in figures 7(a) and (b). The smallest radii of bending (z = 10 mm)

(radius = 3.29 mm)) shows the highest increase in resistance compared to 7.5 mm (radius = 6.02 mm) and z = 5 mm (radius = 10.98 mm). In figures 6(c)and (d), a higher change of resistance is observed for a lower bending radii. In figures 7(c) and (d), a higher change of resistance is observed for a lower bending radii. In another application, the effect of bending radii induced stress on flexible conducting traces was observed in a previous study published by our group [35]. It can also be observed from figures 7(c) and (d) that a higher substrate thickness/via lengths causes a higher change in resistance. This behavior has been reported in previous studies and is attributed to additional stresses imposed by the substrate-silver interface. A similar behavior was observed in figures 6(c)and (d), where the thicker substrate induced a higher bending stress and resulted in a higher increase of resistance.

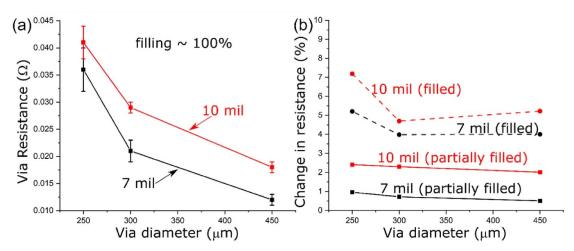

To further investigate the impact of filling on via bending, all the unfilled vias were subsequently filled using a syringe. Comparison of the via resistance for the two substrate thicknesses/via lengths is shown in figure 7(a) for the filled vias. Comparison of the via

**Figure 8.** (a) Via resistance for filled vias and (b) change in the calculated via resistance for different diameters vias after 500 cycles of bending with z = 10 mm.

resistance data shown in figures 8(a) and 5 shows that the via resistance for the filled vias is lower than the unfilled vias as expected. The resistance of a 100% filled condition can be modeled by the resistance of a solid cylinder. In a solid conductive cylinder, the resistance is inversely proportional to the diameter squared and directly proportional to the length. Next, the change in resistance of these filled vias of different diameters due to cyclic bending stress was evaluated.

The filled vs. unfilled via cycling bending comparison test illustrated in figure 8(b) was designed to further test the inference made from the cyclic bend test of the unfilled vias (figure 5). Figure 8(b) shows the change in resistance for both substrate thicknesses and the two filling conditions (filled and unfilled). It is observed that the change in resistance for unfilled (7 and 10 mil) vias is lower than their filled via counterparts. This suggests that a completely filled via inadvertently results in greater susceptibility to bending induced increase in the resistance. An increase in resistance with cyclic bending of filled vias on rigid PCBs has been observed and is attributed to formation of micro-cracks [39]. It was also seen that crack propagation increased with the number of cycles, resulting in an increase in resistance [39]. An increase in via resistance with bending cycling is shown in figure 8(b) and is attributed to crack propagation. An increase of  $\sim 1.2 \times$  in via resistance is observed for filled 250 vias on 10 mil substrate and a  $\sim$ 1.6× increase for 7 mil substrates. Therefore, a higher change in resistance was observed for 7 and 10 mil filled vias than unfilled vias (figure 8(b)), suggesting a model of greater formation and propagation of micro-cracks in the filled vias.

#### 4. Conclusion

In this work, the reliability of vias on a flexible substrate was evaluated using three different bending radii, two different substrate thicknesses, and seven different via diameters. The ASTM bend test (F2749) was used as the primary test to investigate the via reliability. Electrical and optical results were used to analyze the effect of bending stress and bending cycles on all the vias. It was observed that vias with lower filling not only showed a better mechanical pliability but also showed a lower change in resistance after 10 000 cycles of bending. It was also observed that the resistance change was high for completely filled vias, suggesting a mechanism of an increased crack formation and propagation for high via filling conditions. All via filling estimates were obtained using a noncontact CT-scanning approach. This non-destructive method assisted in increasing the repeatability of the via filling measurements and overcame the drawbacks that are associated with traditional methods such as cutting cross-sections and imaging with SEM. This understanding and discussion of the effect of bending on the electrical and mechanical reliability of TPVs could assist the design of reliable multilayer flexible printed circuits.

#### Data availability statement

The data generated and/or analysed during the current study are not publicly available for legal/ethical reasons but are available from the corresponding author on reasonable request.

# Acknowledgments

This work is partially supported by US National Science Foundation (NSF#1439644 and NSF#1939009) and the University of Florida (UF). We thank Dr Mark Sheplak and Austin Vera of UF for the access of the Nd-YAG laser. We would also like to thank Gary Scheiffele from the Nanoscale Research Facility,

RSC at UF for helping us with the analysis of CT-scanner data. Finally, we would also like to acknowledge the help and support of interns at Jabil: Samantha Stevens, Shannon Griffin and Patrick Alfonso.

#### **ORCID iDs**

Kartik Sondhi https://orcid.org/0000-0001-7954-7321

Sai Guruva Reddy Avuthu https://orcid.org/0000-0003-1443-0098

Z Hugh Fan https://orcid.org/0000-0002-1812-8016

Toshikazu Nishida 6 https://orcid.org/0000-0002-7148-2102

# References

- Kwon K, Jin Jo Y and Kim T 2009 Flexible Electronics ed W S Wong and A Salleo (Boston, MA: Springer) 462

- [2] Sondhi K, Garraud N, Alabi D, Arnold D P, Garraud A, Avuthu S G R, Fan Z H and Nishida T 2019 Flexible screen-printed coils for wireless power transfer using low-frequency magnetic fields J. Micromech. Microeng. 29 084006

- [3] Kwon J H, Pode R, Kim H D and Chung H K 2013 Applications of Organic and Printed Electronics vol 55 (Boston, MA: Springer)

- [4] Suganuma K 2014 Introduction to Printed Electronics vol 74 (New York, NY: Springer)

- [5] Joo B Y, Rhim S H and Oh S I 2005 Micro-hole fabrication by mechanical punching process *J. Mater. Process. Technol.* 170 593–601

- [6] Hagen G and Rebenklau L 2006 Fabrication of smallest vias in LTCC tape 1 pp 642–7

- [7] Chu D and Miller W D 1995 Laser micromachining of through via interconnects in active die for 3D multichip module pp 120–6

- [8] Gower M C 2000 Industrial applications of laser micromachining Opt. Express 7 56

- [9] Kawase T, Sirringhaus H, Friend R H and Shimoda T 2001 Inkjet printed via-hole interconnections and resistors for all-polymer transistor circuits Adv. Mater. 13 1601–5

- [10] Weremczuk J, Jachowicz R, Shan X, Tarapata G, Hui H T and Shi C W P 2010 Fabrication of wireless sensors on flexible film using screen printing and via filling *Microsyst. Technol.* 17 661–7

- [11] Sirringhaus H, Kawase T, Friend R H, Shimoda T, Inbasekaran M, Wu W and Woo E P 2000 High-resolution inkjet printing of all-polymer transistor circuits *Science* 290 2123–6

- [12] Paul G, Torah R, Beeby S and Tudor J 2017 A printed, dry electrode Frank configuration vest for ambulatory vectorcardiographic monitoring Smart Mater. Struct. 26 025029

- [13] Amontree J, Sondhi K, Hwangbo S, Reddy Avuthu S G, Yoon Y K, Nishida T and Fan Z H 2019 Reliability of passive printed dipole antennas under extreme environments 2018 6th IEEE Int. Conf. on Wireless for Space and Extreme Environments, WiSEE 2018 (IEEE) pp 119–24

- [14] Li X, Andersson H, Sidén J and Schön T 2018 Soldering surface mount components on screen-printed Ag patterns on paper and polyimide substrates for hybrid printed electronics Flex. Print. Electron. 3

- [15] Siegel A C, Phillips S T, Dickey M D, Lu N, Suo Z and Whitesides G M 2010 Foldable printed circuit boards on paper substrates Adv. Funct. Mater. 20 28–35

- [16] Alam M A and Kumar S 2016 Flexible electronics Encyclopedia of Nanotechnology (Electronic Materials: Science

- & Technology vol 11) ed W S Wong and A Salleo (Dordrecht: Springer) pp 1223–9

- [17] Munehiro N, Nagato K, Higashisaka T, Murakami M and Nakao M 2019 Heat-assisted screen printing of high-aspect-ratio microstructures IEEE Trans. Compon. Packag. Manuf. Technol. 9 10

- [18] Ekere N N and He D 1996 The performance of vibrating squeegee in the stencil printing of solder pastes *J. Electron. Manuf.* 6 261–70

- [19] Mohanty R, Claiborne B and Andres F 2010 Effect of squeegee blade on solder paste print quality IPC APEX EXPO Technical Conf. 2010 vol 4 pp 2664–70

- [20] Wang F, Zhao Z, Nie N, Wang F and Zhu W 2017 Dynamic through-silicon-via filling process using copper electrochemical deposition at different current densities *Sci. Rep.* 7 46639

- [21] Dow W P, Huang H S and Lin Z 2003 Interactions between brightener and chloride ions on copper electroplating for laser-drilled via-hole filling *Electrochem. Solid-State Lett.* 6

- [22] Dow W P and Huang H S 2005 Roles of chloride ion in microvia filling by copper electrodeposition I. Studies using SEM and optical microscope J. Electrochem. Soc. 152

- [23] Beart K, Ortolino D, Wurm R, Moos R, Pletsch A, Kleinewig S and Kita J 2015 Failure of electrical vias manufactured in thick-film technology when loaded with short high current pulses *Microelectron. Reliab.* 56 121–8

- [24] Engin A E and Narasimhan S R 2013 Modeling of crosstalk in through silicon vias *IEEE Trans. Electromagn. Compat.* 55 149–58

- [25] Aga R S, Kreit E B, Dooley S R, Devlin C L, Bartsch C M and Heckman E M 2016 *In situ* study of current-induced thermal expansion in printed conductors using stylus profilometry *Flex. Print. Electron.* 1

- [26] Mokhtari Amirmajdi O, Ashyer-Soltani R, Clode M P, Mannan S H, Wang Y, Cabruja E and Pellegrini G 2009 Cross-section preparation for solder joints and MEMS device using argon ion beam milling *IEEE Trans. Electron.* Packag. Manuf. 32 265–71

- [27] Bassim N D, De Gregorio B T, Kilcoyne A L D, Scott K, Chou T, Wirick S, Cody G and Stroud R M 2012 Minimizing damage during FIB sample preparation of soft materials J. Microsc. 245 288–301

- [28] Ruzzu A, Fromhein O and Haller D 2002 Electrical bottom side contacting of electromechanical LIGA-structures by vias and screen printing *Microsyst. Technol.* 8 113–5

- [29] Zhang T, Asher E and Yang J 2018 A new printed electronics approach eliminating redundant fabrication process of vertical interconnect accesses: building multilayered circuits in porous materials Adv. Mater. Technol. 3 1700346

- [30] Arruda L, Chen Q and Quintero J 2009 Failure evaluation of flexible-rigid PCBs by thermo-mechanical simulation 2009 Int. Conf. on Electronic Packaging Technology and High Density Packaging, ICEPT-HDP 2009 pp 1201–5

- [31] Jonnalagadda K 2002 Reliability of via-in-pad structures in mechanical cycling fatigue Microelectron. Reliab. 42 253–8

- [32] Barrett J F and Keat N 2004 Artifacts in CT: recognition and avoidance RadioGraphics 24 1679–91

- [33] Kujala M, Kololuoma T, Keskinen J, Lupo D, Mäntysalo M and Kraft T M 2020 Bending reliability of screen-printed vias for a flexible energy module *npj Flex. Electron* 4 24

- [34] Hicks W, Allington T and Johnson V 1980 Membrane touch switches: thick-film materials systems and processing options IEEE Trans. Compon. Hybrids Manuf. Technol. 3 518–24

- [35] Sondhi K, Avuthu S G R, Richstein J, Fan Z H and Nishida T 2020 Characterization of bending, crease, aging, and immersion effects on flexible screen-printed silver traces IEEE Trans. Compon. Packag. Manuf. Technol. 10 444–56

- [36] Vasu A and Grandhi R V 2013 Effects of curved geometry on residual stress in laser peening Surf. Coat. Technol. 218 71–79

- [37] Borwein J M, Borwein P B and Bailey D H 1989 Ramanujan, modular equations, and approximations to Pi or how to compute one billion digits of Pi Am. Math. Mon. 96 201

- [38] Moon H, Lee H, Kwon J, Suh Y D, Kim D K, Ha I, Yeo J, Hong S and Ko S H 2017 Ag/Au/polypyrrole core-shell nanowire network for transparent, stretchable and flexible supercapacitor in wearable energy devices Sci. Rep. 7 41981

- [39] Atli-Veltin B, Ling H, Zhao S, Noijen S, Caers J, Liu W, Gao F and Ye Y 2012 Thermo-mechanical investigation of the

reliability of embedded components in PCBs during processing and under bending loading 2012 13th Int. Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems, EuroSimE 2012 (https://doi.org/10.1109/ESimE.2012.6191742)