# Wireless NoCs using Directional and Substrate Propagation Antennas

Vasil Pano\*, Yuqiao Liu\*, Isikcan Yilmaz\*, Ankit More†, Baris Taskin\*, and Kapil Dandekar\*

\*Electrical and Computer Engineering, Drexel University, Philadelphia, PA 19104, USA

E-mail: vasilpano@gmail.com, ting.yuqiao@gmail.com, taskin@coe.drexel.edu, dandekar@coe.drexel.edu

†Intel Corporation, Hillsboro, OR, 97124, USA

E-mail: ankitmore@gmail.com

**Abstract**—Wireless Network-on-Chip (WNOCs) are introduced to improve the performance for long distance communication within a chip. The on-chip antennas utilized in these WNOCs can be omni-directional or bi-directional, broadcasting to every receiving antenna or directional only in a specific pairing, respectively. There are positives and negatives for both types of antennas, although bi-directional antennas that do not cross paths have the added benefit of decreasing the possibility of interference. This work analyzes the performance of a WNOC with bi-directional antennas that uses an innovative substrate propagation technique recently introduced in literature. Antennas that use substrate propagation are capable of longer distance communication compared to typical on-chip antennas that use surface propagation. It is shown that by using the substrate propagation technique, wireless NoCs with minimal bi-directional antennas can reduce the number of wireless nodes by 66% while achieving similar performance of within  $\pm 5\%$  of throughput.

## I. INTRODUCTION

Most current NoC designs employ a traditional flat-mesh topology that offer an improvement over the typical crossbar infrastructure [1]. The flat-mesh topology is not scalable for larger CMPs or Multi-Processor System-on-Chip (MPSoCs) due to the overall increase in area, which results in increased hop count (the number of nodes traversed by the packet to reach its destination). This in turn results in increased latency and power consumption. These NoC flat-mesh limitation have been countered in literature by employing hierarchical topologies [2–4], which separate the mesh into smaller subnets of cores and connect them at the top level network topology.

Innovative interconnection media such as inductive coupling, nano-photonics, and on-chip antennas are introduced to improve the performance and energy-efficiency of NoCs [5–8]. In particular, wireless on-chip antennas have shown great promise to combat the long wire-based multi-hop distances a packet needs to travel when reaching its destination (even on a hierarchical NoC). Most literature particularly investigates the performance benefits of broadcasting, or omni-directional, antennas that are capable of transmitting to a shared wireless channel across the NoC. This is in stark contrast to bi-

directional antennas which can transmit and receive to only specific pairs.

The main benefit of bi-directional antennas, as opposed to omni-directional antennas, is the ability to transmit simultaneously across multiple wireless channels (with limited wireless destinations) instead of being limited to only one transmission on one wireless channel (but having access to all wireless antennas). A wireless NoC using bi-directional antennas thus has increased throughput and energy-efficiency; although current antenna technology [9–12] has limited the available design space possible for wireless NoCs.

This work analyzes the impact of a recent substrate propagation technique for on-chip communication [13] on a wireless NoC equipped with multiple non-overlapping bi-directional antennas. This technique has a dominant substrate propagation path underneath the surface using an un-doped silicon layer. The propagation path differs greatly from the typical surface propagation in previous literature but it is compliant with current CMOS manufacturing. When the technique is applied to a wireless NoC with bi-directional on-chip antennas, long-range transmission to a specific paired antenna is improved; thus increasing the overall transmission reach within the NoC.

An overview of the substrate propagation mechanism and related works are presented in Section II. The proposed wireless Network-on-Chip with bi-directional antennas is presented in Section III. Performance metrics and experimental setup of the wireless NoC are presented in Section IV. Simulation results of the wireless NoC with bi-directional antennas are discussed in Section V. Finally, the conclusions of this work are presented in Section VI.

## II. RELATED WORKS

The recently proposed antenna with the substrate based propagation technique is briefed in Section II-A. The wireless NoC literature relevant to this work is analyzed in Section II-B.

### A. Antennas in Wireless Network-on-Chip

On-chip wireless interconnections using microwave or millimeter wave are first introduced by Kim and O, who studied the feasibility of integrating the antennas in ICs and demonstrated that wireless communication within silicon ICs is possible [14]. Integrated antennas are combined with a guidance medium to improve the system performance [9, 15]. However, due to low resistivity (typically 10–20  $\Omega\text{-cm}$ ) of the

This material is based upon work supported by the National Science Foundation under Grant No. CNS-1305350 and ECCS-1232164. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the National Science Foundation.

silicon substrate, the radiation efficiency and transmission gain of the integrated on-chip antenna is very low. The efficiency and gain are approximately 3% and -40 dB respectively at relatively low frequency (15 GHz) at 5 mm distance when standard 10-cm resistivity silicon substrate is used.

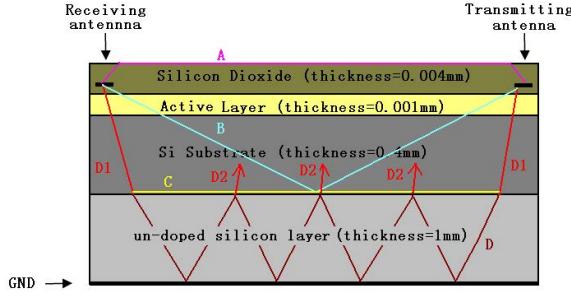

Fig. 1. Typical ray path for on-chip antenna pair. [13]

The typical structure of the CMOS process is shown in Fig. 1. Antennas are inside the silicon dioxide ( $\text{SiO}_2$ ) layer on top of the wafer. A highly doped active layer is below the  $\text{SiO}_2$  layer, followed by a slightly doped Si substrate and then an un-doped silicon layer. Four primary propagation paths that the signal can take are shown in Fig. 1. Ray path A is the surface wave path. Ray path B is the wave propagating in the Si substrate. Ray path C is the surface wave path along the interface of Si substrate and the bottom layer (BL). Ray path D is the guided wave in the BL. Some of the energy is leaking to the Si substrate from the BL and then is attenuated as shown on D2 path; some of the energy is being attenuated before entering BL (D1 path). As a result the radiation efficiency is low, though D is the dominant propagating path.

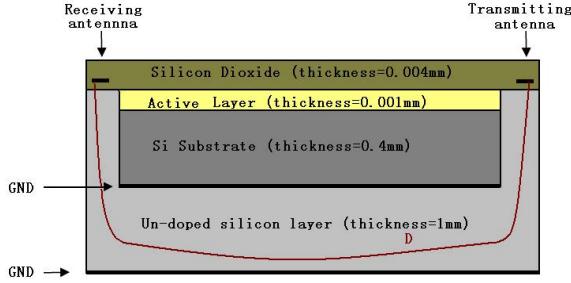

Fig. 2. Dominant ray path after inserting a ground layer between Si substrate and un-doped silicon layer. [13]

A propagation mechanism through the substrate for on-chip wireless communication is introduced by the authors in [13]. A metallic layer (ground plane) between Si substrate and bottom layer is added to increase the transmission gain and radiation efficiency. The metal under the antenna area is removed in order to direct the wave down to the bottom layer without reflection. The bottom layer does not have to be high dielectric material, so conventional CMOS processes are used.

The structure and dominant propagation path of this novel propagation technique is shown in Figure 2. The bottom layer with two metallic layers on the top and bottom acts like half metallic wave guide (vertical direction) and half dielectric wave guide (horizontal). By optimizing the antenna length and chip dimensions [13], the maximum transmission

coefficient ( $S_{21}$ ) and antenna efficiency can reach -15 dB and 28%, respectively.

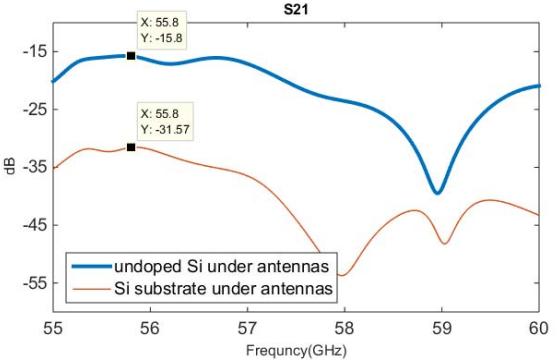

Fig. 3. Transmission coefficient ( $S_{21}$ ) when Si substrate is not replaced by un-doped Si (red, bottom); Transmission coefficient ( $S_{21}$ ) when Si substrate is replaced by un-doped Si (blue, top). [13]

In [13], it is observed that the un-doped silicon layer acts as a waveguide and provides a nearly zero conductive loss path due to nearly zero conductivity with only relatively little dielectric loss. Therefore, the transmission coefficient ( $S_{21}$ ) is greatly improved as shown in Fig. 3, from -30 dB to -15 dB.

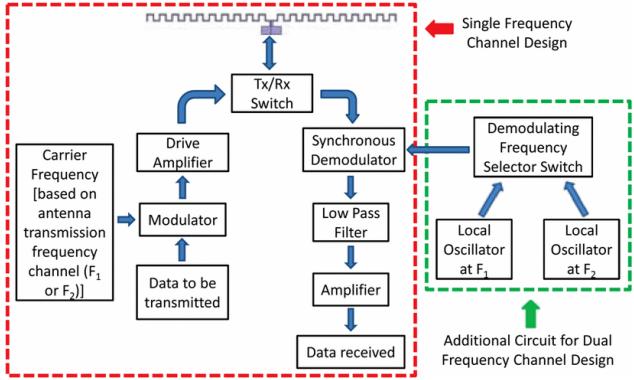

The transceiver design used for circuit simulation is shown in Fig. 4. This is identical to the one proposed in [16], with a transmitter and receiver operating at a single frequency.

Fig. 4. Transceiver block diagram for the WNoC. [16]

These improvements in transmission gain and antenna efficiency can directly benefit wireless NoCs with bi-directional antennas to improve throughput and the overall energy-delay product (EDP) of the system.

#### B. WNoCs Literature Review for Omni- vs Bi-Directional Antennas

A literature review regarding wireless NoCs showcases an array of different architectures that leverage the capabilities of on-chip antennas to improve overall performance. Multiple overviews of wireless NoCs are presented in [8, 12, 17].

Deb et al. [8, 12, 18] describe at length the various challenges and solutions regarding wireless NoCs and designing an efficient and reliable architecture. These studies focus on NoCs

with omni-directional antennas as opposed to bi-directional antennas, therefore the authors had to evaluate the issues of interference and channel availability when considering the overall architecture of their WNoCs.

Mineo et al. [19] and Mondal et al. [20] propose multiple NoC architectures that analyze and implement bi-directional antennas. The impact of the antennas orientation on the energy profile of a wireless NoC is studied in [19]. An in-depth design space exploration is also performed to determine the optimal orientation of the antennas to minimize the energy consumption. Mondal et al. [20] introduce a placement algorithm for directional antennas that minimizes interference and enables operation of multiple wireless links concurrently.

Zhang et al. [21] performed an in-depth analysis of the propagation mechanisms of radio waves over intra-chip channels using on-chip antennas. It is concluded that the propagation of radio waves is mainly realized with surface wave rather than space wave; further sources of interference were also investigated.

### III. PROPOSED WNoC WITH BI-DIRECTIONAL ANTENNAS

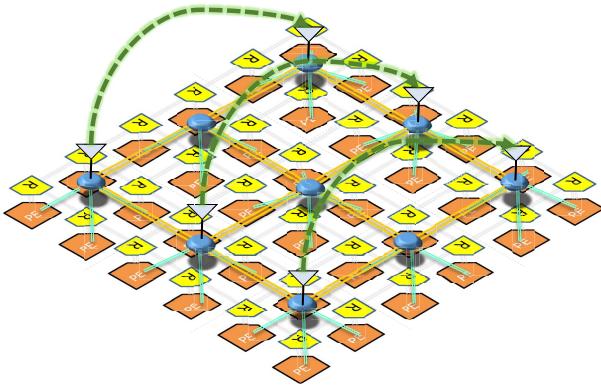

The proposed wireless NoC with bi-directional antennas is depicted in Figure 5. On the base layer of the topology, routers and processing elements are interconnected in a mesh-like topology. Extensions to non-mesh topologies in the base-layer are straightforward. The upper layer is comprised of hubs and hybrid-hubs (capable of wireless communication) that are used to group processing elements (PEs) together in clusters of PEs per “subnet”. This essentially creates a hierarchy in the NoC design that forces packets to be routed to the upper layer if the destination address is outside the bounds of the subnet. In this particular study, the subnets are arbitrarily defined by four routers and PEs.

Fig. 5. The wireless NoC with bi-directional antennas (scaled down from 560 PEs to 36 PEs for demonstration purposes. ).

The routing algorithm is updated to route packets wirelessly if the source hub is in close proximity (in this example, up to two hops distance) to hybrid-hubs capable of wireless transmission. This change to the typical XY-routing minimizes the distance a packet has to travel through normal hubs and

increases the hybrid-hubs utilization. The inclusion of multiple virtual channels guarantees deadlock and livelock avoidance.

The wireless antennas are displayed as small triangles on top of their particular hybrid hub. These antennas are bi-directional in communication channels, only capable of exchanging information in pairs (depicted with green dashed arrows in Figure 5) instead of broadcasting at a particular frequency. This design choice further facilitates comparisons between different topologies due to the available option of increasing the number of hops needed to transmit a packet or a flit wirelessly.

TABLE I. WIRELESS NOC TOPOLOGY OVERVIEW

| Topology                  | Design Point Chosen |

|---------------------------|---------------------|

| # of PEs in Subnets       | 4 PEs (2x2)         |

| # of Subnets              | 140 (10x14)         |

| Total # of PEs            | 560 PEs             |

| # of Wireless Antennas    | Variable 0 – 24     |

| # of Virtual Channels     | 4 VCs               |

| # of Input/Output Buffers | 4 flits             |

| # of Antenna Buffer Depth | 8 flits             |

| Fixed Packet Size         | 10 flits            |

The design choices used in this work for the wireless NoC with bi-directional antennas are detailed in Table I. In addition to the performance analysis of the proposed WNoC built with these design choices, the variability in the number of wireless antennas is also discussed in the experimental results section of Section IV.

### IV. WNoC PERFORMANCE EVALUATION OF SUBSTRATE-PROPAGATION ANTENNAS

An overview of the performance metrics and traffic patterns used to evaluate the wireless NoC are presented in Section IV-A. The experimental setup for the wireless NoC with *bi-directional* antennas is detailed in Section IV-B, including the analysis of varying the number of wireless nodes. The results of the multiple test scenarios on the NoC performance are discussed quantitatively in Section V.

#### A. Performance Metric and Traffic Patterns Overview

The performance metrics used for evaluating the wireless NoC with bi-directional antennas are as follows:

- 1) saturation throughput (flits/cycle/PE),

- 2) average energy per flit at saturation (pJ/flit),

- 3) normalized average latency at saturation (normalized to baseline NoC with no antennas), and

- 4) normalized energy-delay per flit at saturation (normalized to baseline NoC with no antennas),

*Saturation throughput* is important to investigate whether there is a need for the additional wireless nodes or if the throughput will not be impacted severely without additional wireless nodes. If the saturation throughput remains similar throughout the different configurations with varying traffic patterns then it can safely be assumed that additional antennas are not necessary. The main point to observe when analyzing the *normalized average latency at saturation* is whether the additional wireless hops would drastically increase/decrease the latency of packet delivery or if the latency difference is negligible. *Normalized energy-delay per flit at saturation* is used to quantify the relation between energy consumption and

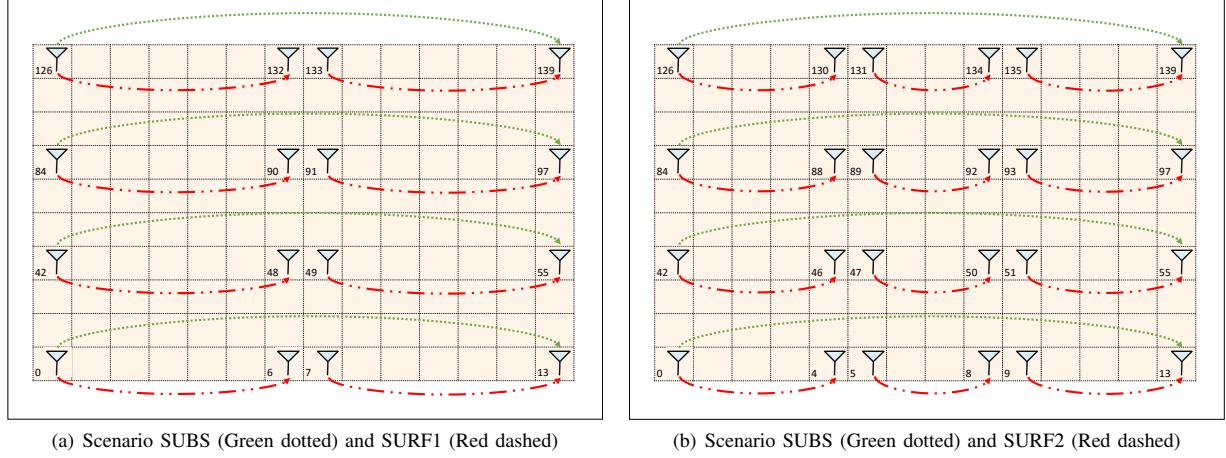

Fig. 6. Antenna placement on the hybrid hierarchical Network-on-Chip (each tile represents a subnet).

the delay of a packet delivery. Energy-delay product (EDP) shows how efficiently energy is being used in relation to packet delivery delay.

The traffic patterns used during simulation runtime are:

- 1) *uniform* traffic,

- 2) *butterfly* traffic, and

- 3) *localization degree of 0.05–0.5* traffic.

*Uniform random* traffic is a good estimate for future exascale workloads that are increasingly non-localized and utilize most of the processing elements uniformly [22]. The *butterfly* traffic pattern specifies destination addresses increasingly further away from the source PE, thus the benefits of across-the-chip wireless links may not be evident in this particular traffic pattern. *Degree of localization* traffic decides destination PEs based on a preset probability of subnet localization; if the localization degree is 5% then most of the traffic generates is outside the subnet of the source PE. These traffic patterns provide a good estimate of the typical (but diverse) applications that are generally seen on a Network-on-Chip.

#### B. Wireless NoC with Bi-Directional Antennas

The simulation framework consists of an in-house cycle-accurate Network-on-chip SystemC simulator with built-in Orion [23] power and area model. The energy consumed by the wireless scheme is taken from [16] and implemented as a energy-per-flit parameter into the SystemC simulator. Further improvements to process technology should improve on the overall energy profile of the Wireless NoC, although it is left out for future work due to space considerations. The analysis and trade-offs between omni-directional and bi-directional antennas are well studied in literature as discussed in Section II-B. For this reason, the analysis in this paper is focused exclusively on bi-directional antennas. The goal is to investigate how the substrate propagation antennas impact the performance metrics discussed in Section IV-A on WNoCs with bi-directional antennas.

Four scenarios are formulated to aid in the investigation: The baseline, SUBS, SURF1 and SURF 2.

The “Baseline” test scenario consists of the same hierarchical NoC but without any antennas. Test scenario “SUBS” is the wireless NoC with bi-directional antennas that utilizes the substrate propagation. Test scenarios “SURF1” and “SURF2” are wireless NoCs with bi-directional antennas that utilize the typical surface propagation but with varying distance of communication. Both SURF1 and SURF2 have shorter communication distance compared to SUBS. In effect these three scenarios in SUBS, SURF1 and SURF2 provide different (i.e. decreasing, in order) strengths of communication distance for directional antennas, providing for multiple data points in the analysis.

Test scenarios SUBS and SURF1 provide the first direct comparison of antenna placement and pairing used. Scenario SUBS consists of 8 antennas (therefore 4 pairs) placed in subnet #0, 42, 84, 126 on the left and #13, 55, 97, 139 on the right, as shown in Figure 6(a) in green dotted. These antennas utilize the *substrate wave propagation* and are able to communicate. Scenario SURF1 instead has 16 antennas (8 total pairs compared to the 4 pairs in SUBS), placed in subnets #6, 7, 48, 49, 90, 91, 132 and 133 as shown in Figure 6(a) in red dashed. These antennas utilize the typical surface wave propagation, and for the purposes of the experimental setup, can only communicate 6 grid lengths across the chip. This first comparison and the subsequent one shown in Figure 6(b) consist of determining the impact that intermediate antennas have on the overall performance of the system.

#### V. SIMULATION RESULTS FOR WNoC WITH BI-DIRECTIONAL ANTENNAS

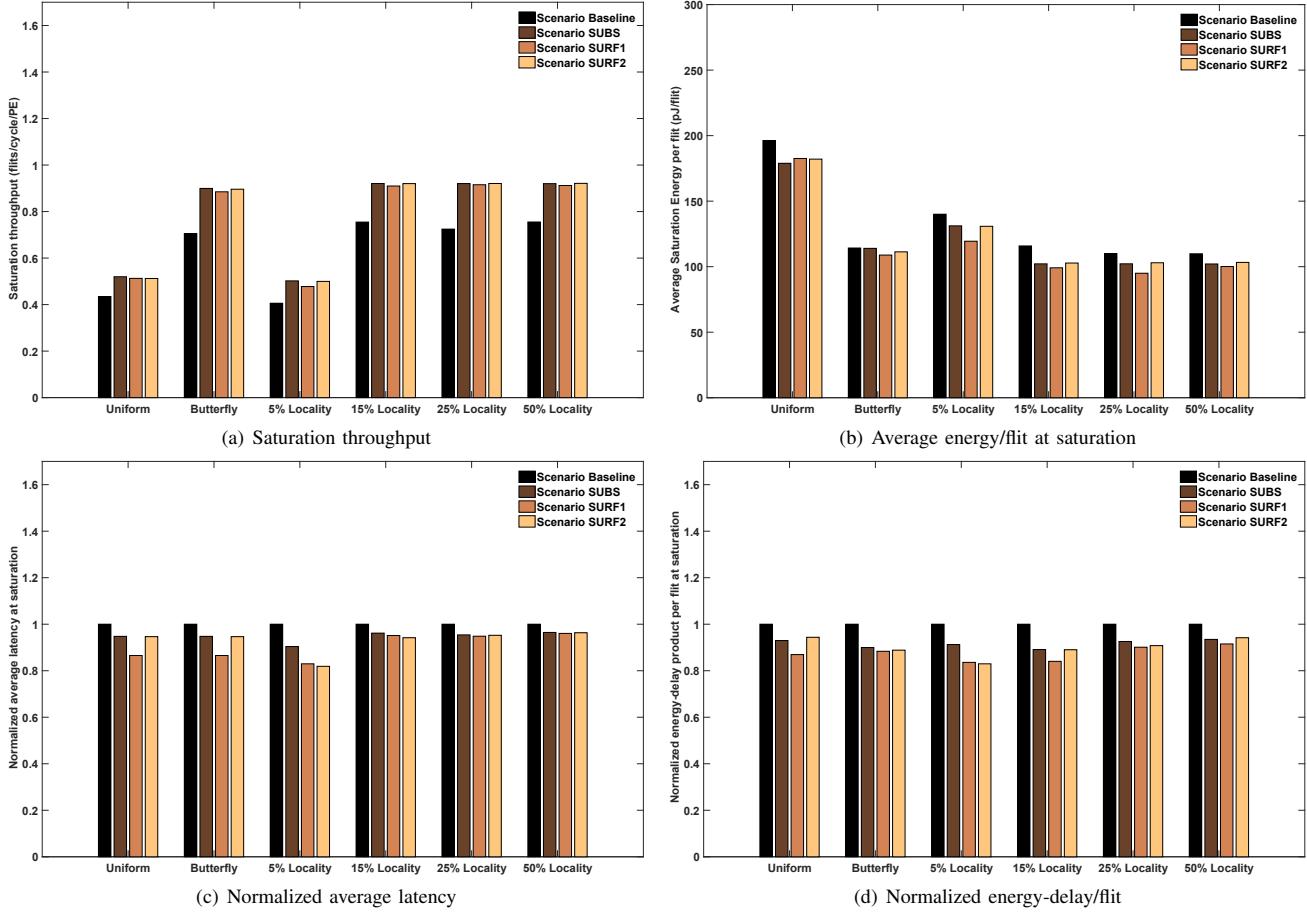

Simulation results in Figure 7 show that the overall performance difference of the WNoC with varying antenna placement and traffic patterns varies between 15% to 27%. The increase in performance can be attributed to the substrate propagation technique discussed in Section II-A. This added ability to deliver packets across the NoC increases the overall throughput of the NoC and improves the EDP considerably.

i. *Saturation throughput* results in Figure 7(a) show the impact on throughput from the baseline NoC to various antenna configuration is substantial enough to warrant the

Fig. 7. Experimental results for WNoC with Bi-Directional Antennas with varying synthetic traffic patterns.

implementation of wireless links throughout the topology. The improvement ranges from 15% as observed in the butterfly traffic pattern, up to 27% as observed in the 25% localized traffic pattern. Although throughput is definitely improved, it can be observed that throughput improvement saturates with the increase of wireless links, keeping the improvement to around 18% in uniform random traffic pattern. Scenarios SUBS and SURF1 offer a good discussion of antenna placement compared to throughput saturation: scenario SUBS displays the best throughput compared to the others scenarios which show a steady decrease in throughput. When compared to scenario SURF1 we can observe a decrease in throughput from SUBS mainly because the additional hops that are required to jump from the two distanced antennas. This further verifies that in certain cases additional antennas do not always infer better performance. Scenario SUBS and SURF2 are very similar throughput wise, reaching a saturation of around 23% improvement over the baseline NoC. This trend line is more visible in the localized traffic that have a lower probability of packet destinations being from within the same subnet as the source of the packet.

ii. Results for *Average energy/flit at saturation* in Figure 7(b) help form a better understanding of antenna impact on the NoC. When comparing the baseline NoC to scenario

SUBS, the average energy per flit is improved from 7% up to 15% in some particular cases. An increase in energy per flit of 7% is seen from scenario SURF1 to SURF2 in the 5% and 25% localized traffic. Scenarios SUBS and SURF2 display minimal change of  $\pm 3\%$  in energy per flit. It can be observed that the configurations achieve similar throughput in Figure 7(a) but with increasingly higher energy per flit.

iii. Results for *Normalized average latency* detailed in Figure 7(c) show a decreased latency up to 18% from the baseline NoC to configurations with additional antennas. Scenarios SUBS and SURF1 show a linear decrease in latency with the increase of antennas throughout most types of traffic. This can be attributed to the additional wireless links in the middle portion of the wireless NoC that can act as destination points for traffic forwarded to the center. Scenarios SUBS and SURF2 display a different trend: latency remains similar with the addition of antennas when analyzing uniform random, 25-50% locality, and butterfly traffic. Traffic localization of 5% shows that latency is decreased by nearly 10% when compared to scenario SUBS due to the high probability that most of the traffic is not localized to the origin subnet. Although, 5% and 15% localization patterns have improved latency from scenario SUBS to SURF2, 25% and 50% localization show nearly identical latency with increased number of antennas.

iv. Results for *Normalized energy-delay/fit* show very similar behavior to average latency. An improvement of up to 17% in EDP is observed from the baseline NoC to the addition of hybrid hubs capable of wireless transmission. Scenario SUBS displays the highest EDP compared to SURF, a similar behavior to latency due to not having the additional center jumps (42–48 and 49–55 for example) that otherwise would improve performance marginally. Scenarios SUBS and SURF2 display an decrease in EDP in the 5% and 15% localized traffic (most likely attributed to the additional links available to reach destinations in the center of the NoC). If the traffic is localized (25% or 50%) the EDP difference between SUBS and SURF2 is negligible.

## VI. CONCLUSIONS

The potential benefits of a propagation technique that is capable of achieving a high transmission gain and increased antenna efficiency on bi-directional WNoCs are explored in this work. A WNoC with bi-directional antennas is chosen as the primary evaluation platform due to the increased benefits that the propagation technique facilitate. Multiple scenarios are compared, across different traffic patterns and with a packet injection rate that saturate the network. The experimental results show an increase of 27% in throughput and an improvement of 17% in the energy-delay product (EDP) when adding long distance bi-directional antennas to the NoC.

The effects of adding additional antennas to have an increased wireless coverage is also evaluated; it is shown that the additional antennas do not provide a substantial difference in performance when compared to the the minimum number of antennas. The innovative substrate propagation technique makes it unnecessary to include additional antennas in the NoC. Performance benefits within  $\pm 5\%$  can be achieved with the minimum 8 number of antennas in the experimental setup discussed in Section V. In comparison to the WNoC with 16 additional antennas (scenario SURF2), antenna overhead is reduced by 66% in the WNoC with substrate propagation. This is a step forward to minimizing the overhead of on-chip antennas in WNoCs, which has historically been seen as a major challenge for the widespread use of WNoCs. Overall, the usage of long distance bi-directional antennas is favored, the avoidance of interference and the capability of reaching across the NoC with novel propagation techniques, strongly indicates that NoCs equipped with bi-directional antennas are a viable alternative to ones with omni-directional antennas.

## REFERENCES

- [1] R. Marculescu, U. Y. Ogras, L. S. Peh, N. E. Jerger, and Y. Hoskote, "Outstanding research problems in noc design: System, microarchitecture, and circuit perspectives," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)*, vol. 28, pp. 3–21, January 2009.

- [2] S. Bourduas and Z. Zilic, "A hybrid ring/mesh interconnect for network-on-chip using hierarchical rings for global routing," in *Proceedings of the IEEE/ACM International Symposium on Networks-on-Chip (NoCS)*, pp. 195–204, May 2007.

- [3] D. Park *et al.*, "Mira: A multi-layered on-chip interconnect router architecture," in *Proceedings of the IEEE International Symposium on Computer Architecture (ISCA)*, pp. 251–261, June 2008.

- [4] R. Das, S. Eachempati, A. K. Mishra, V. Narayanan, and C. R. Das, "Design and evaluation of a hierarchical on-chip interconnect for next-generation cmps," in *Proceedings of the IEEE International Symposium on High Performance Computer Architecture (HPCA)*, pp. 175–186, February 2009.

- [5] H. Matsutani, P. Bogdan, R. Marculescu, Y. Take, D. Sasaki, H. Zhang, M. Koibuchi, T. Kuroda, and H. Amano, "A case for wireless 3d nocs for cmps," in *Proceedings of the IEEE/ACM Design Automation Conference (DAC)*, pp. 23–28, January 2013.

- [6] Y. Take, H. Matsutani, D. Sasaki, M. Koibuchi, T. Kuroda, and H. Amano, "3d noc with inductive-coupling links for building-block sips," *IEEE Transactions on Computers*, vol. 63, pp. 748–763, March 2014.

- [7] A. Shacham, K. Bergman, and L. P. Carloni, "Photonic networks-on-chip for future generations of chip multiprocessors," *IEEE Transactions on Computers*, vol. 57, pp. 1246–1260, September 2008.

- [8] S. Deb, A. Ganguly, P. P. Pande, B. Belzer, and D. Heo, "Wireless noc as interconnection backbone for multicore chips: Promises and challenges," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 2, pp. 228–239, June 2012.

- [9] K. K. O, K. Kim, *et al.*, "The feasibility of on-chip interconnection using antennas," in *Proceedings of the IEEE/ACM International Conference on Computer-Aided Design (ICCAD)*, pp. 979–984, November 2005.

- [10] J. J. Lin *et al.*, "Communication using antennas fabricated in silicon integrated circuits," *IEEE Journal of Solid-State Circuits*, vol. 42, pp. 1678–1687, August 2007.

- [11] A. More and B. Taskin, "Leakage current analysis for intra-chip wireless interconnects," in *Proceedings of the IEEE International Symposium on Quality Electronic Design (ISQED)*, pp. 49–53, March 2010.

- [12] S. Deb *et al.*, "Design of an energy-efficient cmos-compatible noc architecture with millimeter-wave wireless interconnects," *IEEE Transactions on Computers*, vol. 62, pp. 2382–2396, December 2013.

- [13] Y. Liu, V. Pano, D. Patron, K. Dandekar, and B. Taskin, "Innovative propagation mechanism for inter-chip and intra-chip communication," in *Proceedings of the IEEE Wireless and Microwave Technology Conference (WAMICON)*, pp. 1–6, April 2015.

- [14] K. Kim and K. Ko, "Integrated dipole antennas on silicon substrates for intra-chip communication," in *Proceedings of the IEEE International Symposium on Antennas and Propagation Society (AP-S)*, pp. 1582–1585, July 1999.

- [15] K. Kim and K. Ko, "A plane wave model approach to understanding propagation in an intra-chip communication system," in *Proceedings of the IEEE International Symposium on Antennas and Propagation Society (AP-S)*, pp. 166–169, July 2001.

- [16] A. More and B. Taskin, "Em and circuit co-simulation of a reconfigurable hybrid wireless noc on 2d ics," in *Proceedings of IEEE International Conference on Computer Design (ICCD)*, pp. 19–24, October 2011.

- [17] P. P. Pande, A. Ganguly, K. Chang, and C. Teuscher, "Hybrid wireless network on chip: A new paradigm in multi-core design," in *Proceedings of the ACM International Workshop on Network on Chip Architectures (NoCArc)*, pp. 71–76, December 2009.

- [18] S. Deb *et al.*, "Cmos compatible many-core noc architectures with multi-channel millimeter-wave wireless links," in *Proceedings of the ACM/IEEE Great Lakes Symposium on VLSI*, pp. 165–170, May 2012.

- [19] A. Mineo, M. Palesi, G. Asciano, and V. Catania, "Exploiting antenna directivity in wireless noc architectures," *Microprocessors and Microsystems*, vol. 43, pp. 59–66, June 2016.

- [20] H. Mondal, S. Gade, M. Shamim, S. Deb, and A. Ganguly, "Interference-aware wireless network-on-chip architecture using directional antennas," *IEEE Transactions on Multi-Scale Computing Systems*, vol. PP, pp. 1–1, July 2016.

- [21] Y. P. Zhang, Z. M. Chen, and M. Sun, "Propagation mechanisms of radio waves over intra-chip channels with integrated antennas: Frequency-domain measurements and time-domain analysis," *IEEE Transactions on Antennas and Propagation*, vol. 55, pp. 2900–2906, October 2007.

- [22] P. Kogge, K. Bergman, S. Borkar, *et al.*, "Exascale computing study: Technology challenges in achieving exascale systems," tech. rep., Defense Advanced Research Projects Agency Information Processing Techniques Office (DARPA IPTO), 2008.

- [23] A. B. Kahng, B. Li, L. S. Peh, and K. Samadi, "Orion 2.0: A fast and accurate noc power and area model for early-stage design space exploration," in *Proceedings of the ACM/IEEE Design, Automation Test in Europe Conference Exhibition (DATE)*, pp. 423–428, December 2009.