Research Article www.acsami.org

# Role of ALD Al<sub>2</sub>O<sub>3</sub> Surface Passivation on the Performance of p-Type Cu<sub>2</sub>O Thin Film Transistors

Mari Napari,\* Tahmida N. Huq, David J. Meeth, Mikko J. Heikkilä, Kham M. Niang, Han Wang, Tomi Iivonen, Haiyan Wang, Markku Leskelä, Mikko Ritala, Andrew J. Flewitt, Robert L. Z. Hoye, and Judith L. MacManus-Driscoll

Cite This: ACS Appl. Mater. Interfaces 2021, 13, 4156-4164

**ACCESS**

III Metrics & More

Article Recommendations

Supporting Information

ABSTRACT: High-performance p-type oxide thin film transistors (TFTs) have great potential for many semiconductor applications. However, these devices typically suffer from low hole mobility and high off-state currents. We fabricated p-type TFTs with a phasepure polycrystalline Cu<sub>2</sub>O semiconductor channel grown by atomic layer deposition (ALD). The TFT switching characteristics were improved by applying a thin ALD Al<sub>2</sub>O<sub>3</sub> passivation layer on the Cu<sub>2</sub>O channel, followed by vacuum annealing at 300 °C. Detailed characterization by transmission electron microscopy-energy dispersive X-ray analysis and X-ray photoelectron spectroscopy shows that the surface of Cu<sub>2</sub>O is reduced following Al<sub>2</sub>O<sub>3</sub> deposition and indicates the formation of a 1-2 nm thick CuAlO<sub>2</sub> interfacial layer. This, together with field-effect passivation

caused by the high negative fixed charge of the ALD Al<sub>2</sub>O<sub>3</sub>, leads to an improvement in the TFT performance by reducing the density of deep trap states as well as by reducing the accumulation of electrons in the semiconducting layer in the device off-state.

KEYWORDS: thin film transistors, oxide thin films, passivation, copper oxide, atomic layer deposition

## INTRODUCTION

Metal-oxide thin film transistors (TFTs) have attracted increasing interest especially in display technologies owing to their optical transparency and high mobility, low processing temperatures and material costs, and mechanical flexibility. This has led to the development of high-performance n-type semiconducting oxide materials, such as amorphous indiumgallium-zinc-oxide (IGZO) with electron mobility of several tens of cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. However, the full utilization of oxides in p-n junction-based electronics and complementary metal oxide semiconductor (CMOS) integrated circuits is still hindered by the lack of high performance p-type oxides. The reason for the challenges in achieving feasible hole conductivity is the differences in the electronic structures of the n- and ptype oxides.<sup>3</sup> The transport path of holes in p-type oxides and valence band maximum (VBM) consists typically of localized anisotropic oxygen 2p orbitals, which results in large hole effective mass and low mobility. In addition, the concentration of holes in oxides is often limited by the high formation energy of the cation vacancies as well as the annihilation of holes due to the low formation energy of the oxygen vacancies.<sup>3</sup> In case of cuprous oxide Cu<sub>2</sub>O, however, the valence band is formed by the hybridization of the O 2p and Cu 3d orbitals, resulting in a less localized VBM and pathway for hole transportation for holes formed via copper vacancies (V<sub>Cu</sub>) as acceptor states.

Such special configuration and high hole mobility have made Cu<sub>2</sub>O an extensively studied p-type oxide for TFTs,<sup>5</sup> and due to its other advantageous properties, such as material abundance and solar absorbance, it has also been investigated as a potential candidate for multiple device applications ranging from photovoltaics to sensors.

Cu<sub>2</sub>O layers for TFTs are traditionally fabricated by physical vapor deposition (PVD) methods, such as pulsed lased deposition (PLD)<sup>7-9</sup> and sputtering. 10-12 Solution-based processing methods have also been used, such as spin coating, 13,14 electrodeposition, 15 and inkjet printing. 16 For scalable device applications, it is crucial to be able to deposit films with uniform and controllable thickness and composition over large areas, preferably at low or moderate temperatures. Atomic layer deposition (ALD) has been proven invaluable for the fabrication of modern microelectronics, where it is used to produce ultrathin high-quality dielectric films for devices

Received: October 21, 2020 Accepted: January 5, 2021 Published: January 14, 2021

including metal-oxide semiconductor field effect transistors and dynamic random access memories. ALD has the potential to be extended in production of active device layers. It has already shown to be capable of depositing n-type semiconducting films, such as IGZO, <sup>17</sup> with properties compatible with what has been achieved by PVD techniques.<sup>2,17</sup> The successful application of ALD-grown n-type semiconducting oxides in TFTs has been demonstrated both on rigid and flexible substrates. 18,19 Development of ALD processes for ptype materials (NiO, CuO<sub>x</sub>, and SnO) has been mostly of interest for photovoltaics, especially in perovskite and tandem solar cells, where they can be used as electron-blocking and hole transport layers.<sup>20</sup> However, some examples of other electronics applications, such as p-type TFTs with ALD-grown semiconductor channels, have been published. 18,21,22 For example, high performing TFTs with ALD-grown CuO<sub>x</sub> films (consisting of both Cu<sub>2</sub>O and CuO phases) have been reported by Maeng et al.<sup>21</sup> Their devices showed an unusually high field effect mobility of  $\mu_{FE} = 5.6 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ , which is higher than the  $\mu_{\mathrm{FE}}$  of any reported  $\mathrm{CuO}_x$  device in the literature. Unfortunately, to our best knowledge, these results have not yet been consistently reproduced nor are there other reports of the use of ALD Cu2O in TFTs. However, ALD was used to demonstrate high-performance p-type TFTs with the SnO channel.<sup>22</sup> There it was observed that applying Al<sub>2</sub>O<sub>3</sub> channel passivation significantly improves the TFT performance via the reduction of trap states at the interface.

Here, we investigate the influence of an ALD  $Al_2O_3$  passivation layer on the performance of p-type TFTs with an ALD-grown  $Cu_2O$  channel. We show that passivation and subsequent vacuum annealing improve the transistor performance metrics. In addition to device measurements, the  $Al_2O_3/Cu_2O$  interface was characterized in detail by using X-ray photoelectron spectroscopy (XPS) and transmission electron microscopy (TEM) to obtain more information of the interface modification taking place during the deposition of  $Al_2O_3$  on  $Cu_2O$ . Furthermore, we discuss the significance of the interface formation and other passivation mechanisms of the ALD  $Al_2O_3$  film, such as the effect of the high fixed charge, on the improved performance of the  $Cu_2O$  p-channel TFTs.

## ■ RESULTS AND DISCUSSION

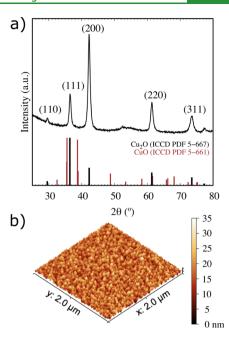

Cu<sub>2</sub>O Film Characterization. The X-ray diffraction pattern of a 40 nm thick Cu<sub>2</sub>O film is presented in Figure 1a. The grazing incidence X-ray diffraction (GIXRD) revealed that the films were polycrystalline Cu<sub>2</sub>O, with the most intense reflections associated to the (200), (111), and (220) planes of the cubic Cu<sub>2</sub>O. No trace of CuO or Cu was detected, indicating that the films were phase-pure Cu2O, with a crystallite size of ca. 30 nm. The crystalline structure of the films was visible also by atomic force microscopy (AFM) (see example Figure 1b) showing the films to have distinct grains in the morphology with a high surface roughness of ca. 4.5 nm root mean square (rms). Despite the high film roughness, we can assume the films to be continuous, based on the detailed growth analysis of corresponding ALD Cu<sub>2</sub>O films reported by livonen et al. in ref 23. Hall effect measurements confirmed the p-type conductivity of the films, with a resistivity of  $\rho = 300$  $\Omega$ cm, hole density of  $N=10^{16}~{

m cm}^{-3}$ , and Hall mobility  $\mu_{

m H}=$ 0.6 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The Hall hole mobility is somewhat lower than what has been reported earlier for Cu<sub>2</sub>O films. However, as-deposited films processed at lower temperatures generally pose a lower hole mobility, in the order of few cm<sup>2</sup> V<sup>-1</sup>

**Figure 1.** (a) XRD pattern of the as-deposited, phase-pure polycrystalline  $Cu_2O$  film and the ICCD cards for both  $Cu_2O$  and CuO, used for indexing. (b) 3D AFM image of 2  $\mu$ m  $\times$  2  $\mu$ m area of the corresponding film. The film roughness (rms) is 4.5 nm.

$s^{-15,10,12,24,25}$  as a maximum, than films deposited and/or treated at high temperatures, in which the mobility can reach tens of cm² V⁻¹ s⁻¹³,7 but the variation between different reports is vast. In our case, the low hole mobility may be due to low film thickness, which, combined with small grain size and high surface roughness, limits the conduction. Han and Flewitt have investigated the role of the Cu²O film morphology on the charge carrier characteristics, and they concluded that the nanocrystalline structure of thin Cu²O films can suggest the presence of potential energy barriers at grain boundaries, leading to effects such as grain boundary scattering, which hinders the hole transport in the thin films.²6 This is further enhanced by the formation of a conductive CuO layer onto the grain surfaces.²7

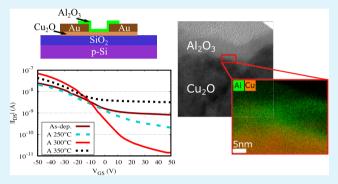

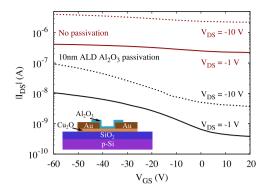

TFT Performance. The Cu<sub>2</sub>O films were tested as pchannels in simple bottom-gate TFT devices with an Au source and drain electrodes and a p-Si substrate acting as a common gate (see inset in Figure 2). The switching characteristics of the as-deposited films without the Al<sub>2</sub>O<sub>3</sub> passivation layer were negligible as shown in Figure 2. With a 10 nm Al<sub>2</sub>O<sub>3</sub> layer deposited on the Cu2O channel, the off-state drain current (I  $I_{\mathrm{DS}}$ I) at positive gate voltage  $V_{\mathrm{GS}}$  decreased by 3 orders of magnitude and switching with  $I_{\rm on}/I_{\rm off}\approx 30$  was measured. It has been shown that the gap state density in oxide semiconductor TFTs can be affected by the ambient moisture and oxygen adsorption on the top channel surface, which can be suppressed by the passivation layer.<sup>28</sup> However, for this effect, the type or fabrication method of the passivation layer seems not to be critical, as improvements in the performance of n- and p-type TFTs have been reported with different ALD and solution-processed oxide films as well as with organic passivation layers. 22,29-31

To further improve TFT performance, the devices were annealed for 10 min in 1.5 mbar  $N_2$  directly after  $Al_2O_3$  deposition. A low vacuum environment was chosen to prevent phase transitions of the  $Cu_2O$  layer into CuO or Cu. As seen in

Figure 2. Gate transfer characteristics of a TFT device with 40 nm ALD  $\mathrm{Cu_2O}$  p-channel, with and without  $\mathrm{Al_2O_3}$  passivation, shown as black and dark-red curves, respectively. In both cases, the device is measured with drain voltages  $(V_{\mathrm{DS}})$  of  $-10.0~\mathrm{V}$  (dashed lines) and  $-1.0~\mathrm{V}$  (solid lines). The inset shows the schematic of the TFT device with the  $\mathrm{Al_2O_3}$  passivation layer.

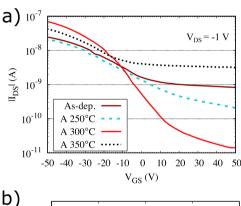

Figure 3a, the transfer characteristics of the devices started to improve after annealing at 250 °C, but the most significant

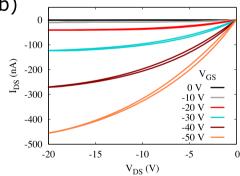

**Figure 3.** (a) Transfer characteristics of the Cu<sub>2</sub>O TFTs with  ${\rm Al_2O_3}$  passivation, annealed in low-vacuum at different temperatures. Measured with  $V_{\rm DS}=-1.0~{\rm V.}$  (b) Output characteristics of a device annealed at 300 °C.

effect was gained at 300 °C, with output characteristics shown in Figure 3b. At higher annealing temperatures, transfer characteristics begun to deteriorate. In the devices annealed at 400 °C, no switching was observed, and a positive  $I_{\rm DS}$  was recorded (data not shown). In the unpatterned  ${\rm Al_2O_3/Cu_2O}$  film reference sample on glass, the 400 °C annealing caused color changes visible to the naked eye, potentially indicating a partial reduction into metallic Cu. The same effect was observed also when the annealing was performed in 1 atm Ar atmosphere at the same temperature.

Despite the increase in the switching ratio of up to  $I_{\rm on}/I_{\rm off}=5\times10^3$  in the sample annealed at 300 °C, the carrier mobility remained low, with field-effect mobility for the as-deposited and annealed devices being  $\mu_{\rm FE}\approx1.5\times10^{-3}~{\rm cm^2~V^{-1}~s^{-1}}$ , which was calculated as  $\mu_{\rm FE}=(g_{\rm m}L)/(WC_{\rm ox}V_{\rm DS})$ , where  $g_{\rm m}$  is the transconductance  $(g_{\rm m}=\delta I_{\rm DS}/\delta V_{\rm GS})$ , L and W the channel length and width, respectively,  $(L=50~\mu{\rm m},~W=1000~\mu{\rm m})$ , and  $C_{\rm ox}$  the gate dielectric capacitance per unit area, calculated using a dielectric constant of 3.9 for SiO $_2$  gate oxide. Additionally, high operating voltages were required for switching, even for devices with enhanced characteristics, with a threshold voltage  $V_{\rm TH}$  and subthreshold swing SS of  $-19.8~{\rm V}$  and  $11.5~{\rm V}~{\rm dec}^{-1}$ , respectively. The corresponding  $V_{\rm TH}$  and SS of the as-deposited device with Al $_2$ O $_3$  passivation were  $-13.0~{\rm and}~29.2~{\rm V}~{\rm dec}^{-1}$ , respectively.

The characteristics of the TFTs without the Al<sub>2</sub>O<sub>3</sub> layer were not improved upon annealing, and Hall effect measurements showed there to be no change in the carrier mobility of the annealed Cu<sub>2</sub>O samples (Figure S1 in the Supporting Information). Therefore, it can be concluded that the Al<sub>2</sub>O<sub>3</sub> passivation is the reason for the improved performance. Similar effects have been reported for p-type TFTs with passivated SnO channels.<sup>22,32</sup> Kim et al. showed an improvement in devices with the ALD SnO channel passivated with ALD Al<sub>2</sub>O<sub>3</sub>, which was further enhanced by subsequent annealing. Similar observations were made by Qu et al., who passivated sputtered SnO channels by ALD Al<sub>2</sub>O<sub>3</sub> as well as with organic coatings.<sup>32</sup> Our results are consistent with these findings, both reporting an increase in the  $I_{\rm on}/I_{\rm off}$  ratio and a decrease in SS upon ALD Al<sub>2</sub>O<sub>3</sub> passivation. These changes can be associated with a reduction in the trap state density at the channel surface. It seems that the ALD Al<sub>2</sub>O<sub>3</sub> passivation has more impact on reducing the deep trap state density, both in Cu<sub>2</sub>O and SnO, indicated by the reduction in the SS. On the other hand, the shallow traps (tail states near the valence band), are less affected, as the carrier mobility does not increase significantly.<sup>32</sup> Interestingly, it has been reported<sup>29</sup> that passivation of n-type oxide TFTs by ALD Al<sub>2</sub>O<sub>3</sub> increases the mobility and SS which is opposite to what has been observed for the p-type devices.

The low field-effect mobility in the order of  $\mu_{\text{FE}} = 10^{-3}$  – 10<sup>-2</sup> cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> is typical for Cu<sub>2</sub>O TFTs processed at low/ moderate temperatures and with a thin channel layer of few tens of nm, regardless of the deposition technique. 3,10,14 However, there are some reports where orders of magnitude higher  $\mu_{FE}$  values, up to 6 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, have been achieved, even with a room-temperature processing and mixed phase Cu<sub>2</sub>O-CuO films. <sup>21,33</sup> The limited mobility in Cu<sub>2</sub>O thin films is typically associated with the high density of subgap trap states and grain boundary scattering.<sup>3,26</sup> Additionally, it has been shown that a CuO layer can form at the Cu<sub>2</sub>O/SiO<sub>2</sub> interface already at 300 °C, which further increases the trap density and, hence, has a negative impact on the transfer characteristics. Therefore, it has been suggested that replacing SiO<sub>2</sub> with high-k dielectric may result in better performance.8,34

We also tested devices with a 75 nm thick ALD  $\rm Al_2O_3$  gate oxide and observed switching in the devices with a decreased SS (7.5 V dec<sup>-1</sup>) and a  $V_{\rm TH}$  of 10.6 V (see Figure S2), indeed indicating a reduction in the trap states at the dielectric/semiconductor interface. However, in this case, the  $\rm Al_2O_3$  gate oxide had a lower breakdown voltage than 100 nm SiO<sub>2</sub>, which means that the channel was not yet fully depleted when the

gate modulation was lost, limiting both the  $I_{\rm on}/I_{\rm off}$  ratio and the mobility.

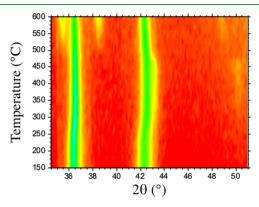

To investigate the effect of annealing on the  $Al_2O_3/Cu_2O$  stack in detail, a high-temperature GIXRD measurement was performed. 10 nm  $Al_2O_3$  was deposited on a 40 nm  $Cu_2O$  sample, and the diffraction patterns were collected at 150–600 °C in 20 mbar  $N_2$  (Figure 4). It was observed that at 250 °C,

**Figure 4.** 2D high-temperature GIXRD pattern of the 10 nm  $Al_2O_3/40$  nm  $Cu_2O$  stack annealed to 150–600 °C in 20 mbar  $N_2$ . High intensity lines correspond to the  $Cu_2O$  (111) and (200) reflections. The intensity is plotted in logscale.

the (111) and (200) reflections shift toward larger  $2\theta$  angles, indicating a decrease in the unit-cell parameters, possibly due to stress relaxation when the annealing temperature exceeds the deposition temperature. As seen in the samples annealed earlier, signs of metallic Cu appeared also in the passivated sample. These changes, seen as reflections at ca. 43 and 50.5°, take place just above 300 °C. At 475 °C, the Cu reflections disappear and features corresponding to formation of CuO become visible. These changes in the film structure upon annealing could explain the observed narrow annealing temperature window for optimal TFT performance.

Moreover, when annealed under similar conditions, a Cu<sub>2</sub>O film without the Al<sub>2</sub>O<sub>3</sub> layer undergoes oxidation to CuO already at 300 °C (Figure S3), showing the importance of the Al<sub>2</sub>O<sub>3</sub> layer to the phase stability of the films during annealing. This behavior of both the bare ALD Cu<sub>2</sub>O and the Al<sub>2</sub>O<sub>3</sub>/ Cu<sub>2</sub>O film stack differ from what has been shown for Cu<sub>2</sub>O films and devices fabricated by physical deposition methods such as PLD and sputtering. High temperature deposition or annealing at 500-800 °C, both in vacuum and inert gas atmosphere has shown to improve the device performance significantly by reduction of the CuO phases on the grain boundaries and increase in the  $\text{Cu}_2\text{O}$  crystallite and grain sizes, while the  $\text{Cu}_2\text{O}$  phase remains stable.  $^{3,8,11,26,35,36}$  Though the film thickness may have an effect on the film behavior during the annealing, it does not fully explain the observed differences between PVD and ALD-deposited Cu<sub>2</sub>O. One explanation is that the grain boundaries of the nanocrystalline ALD Cu<sub>2</sub>O contain a higher density of hydroxyl groups, which then accelerate the film reduction, despite the presence of the passivation layer, and the partial oxidation into CuO is later initiated by the oxygen diffusion from both the Al<sub>2</sub>O<sub>3</sub> layer as well as the SiO<sub>2</sub> gate oxide. However, this remains inconclusive.

Al<sub>2</sub>O<sub>3</sub>/Cu<sub>2</sub>O Interface Characterization. Our results and the previous studies on the passivation of TFTs with oxide semiconductor channels show that quality of the interface

between the channel oxide and the passivation layer can have a significant impact on the device performance. Especially, in the case of passivation by chemical routes, such as ALD, it can be assumed that the interface is further modified by the surface chemistry taking place during the layer deposition. It has been shown that exposure to certain ALD metal precursors, namely alkyl compounds, can reduce a surface oxide layer if the reactions are energetically favourable, <sup>37–39</sup> and this is also routinely utilized for example in the so-called "self-cleaning" process of III-V semiconductor materials.<sup>40</sup> In the case of copper oxide surfaces, for surface reactions of diethylzinc, commonly used as a precursor for ALD ZnO, the Gibbs free energies for reduction reactions of the Cu2O surface into metallic Cu are  $\Delta G_r = (-300) - (-200)$  kJ mol<sup>-1</sup> (T = 373K).<sup>38</sup> The reactions between trimethylaluminum (TMA) and Cu<sub>2</sub>O can be assumed to be even more favorable due to higher reactivity of the TMA. The reduction of the oxidized Cu surface during the first  ${\rm Al_2O_3}$  cycles has been verified both numerically and experimentally.  $^{39,41}$

Gharachorlou et al. investigated the TMA and hydroxyl-free copper surface reactions and presented the mechanism where the  $Cu_2O$  surface is reduced by the highly exothermic stepwise dissociative adsorption reactions of the TMA on the surface. This leads to the consumption of the surface oxygen atoms by the Al to form  $CuAlO_2$  and the remaining Cu to be in the reduced  $Cu^0$  state during the first  $Al_2O_3$  cycles. This results in island-type growth of  $CuAlO_2$  followed by  $Al_2O_3$  film growth when the available  $Cu_2O$  sites have been used. Their proposed overall reaction for the  $CuAlO_2$  and Cu formation by TMA is  $^{39}$

$$2Cu2O + Al(CH3)3$$

$$\rightarrow CuAlO2 + 3Cu + 2CH4(g) + CHads$$

(1)

Using a process with  $H_2O$  as a reactant leads to surface hydroxyl group formation during deposition. However, it can be assumed that the mechanism described above is still valid because it has been calculated that the hydroxyl coverage does not affect the TMA dissociation on the surface but only on growth efficiency.<sup>42</sup>

The formation of a  $\text{CuAlO}_2$  interface could be beneficial to TFT performance because it is a known p-type material with low  $V_{\text{Cu}}$  formation energy. In order to investigate in detail the reduction of  $\text{Cu}_2\text{O}$  by TMA and the formation of the  $\text{CuAlO}_2$  interface layer, samples were prepared for XPS and TEM. XPS was used to analyze  $\text{Cu}_2\text{O}$  films with and without the  $\text{Al}_2\text{O}_3$  passivation and subsequent annealing at 300 °C. To minimize the need of  $\text{Ar}^+$  etching to reach the  $\text{Al}_2\text{O}_3/\text{Cu}_2\text{O}$  interface, only 20 cycles that is ca. 2 nm of  $\text{Al}_2\text{O}_3$  was deposited on samples for XPS measurements. The XPS of as-deposited  $\text{Cu}_2\text{O}$  without the  $\text{Al}_2\text{O}_3$  layer confirmed the films to be phasepure  $\text{Cu}_2\text{O}$  seen both in the Cu 2p and Cu LMM spectra, with a minor CuO content present at the film surface, as well as a high content of hydroxyl groups, as seen in the measured O 1s spectra (see Figure S4).

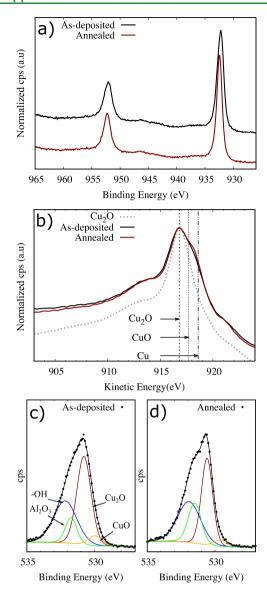

The effect of the annealing on the  $Cu_2O$  film was investigated by measuring a sample annealed at 300 °C. No changes to the film composition were observed (Figure S5). Figure 5 shows the XPS spectra of the  $Al_2O_3/Cu_2O$  films, before and after annealing at 300 °C. As seen in Figure 5a, the Cu 2p spectra of the both films show the absence of the CuO phase. However, the differentiation of between the  $Cu^+$  and  $Cu^0$  states cannot be done from the Cu 2p spectrum. The complementary Cu LMM spectra of the samples in Figure 5b

**Figure 5.** XPS spectra of the  $Al_2O_3/Cu_2O$  interface region, measured after 90 s 0.5 keV  $Ar^+$  sputtering, (a) Cu 2p of the as-deposited (black) and annealed (dark red) samples. (b) Cu LMM Auger electron spectra, the corresponding spectrum of a  $Cu_2O$  film without the  $Al_2O_3$  passivation layer shown by a dashed gray line as a reference. The O 1s spectra of the (c) as-deposited and (d) annealed sample. The deconvoluted peaks correspond to oxygen in  $Cu_2O$  (dark red), CuO (orange), hydroxyl -OH (blue), and  $Al_2O_3$  (green).

show the significant broadening of the Auger electron peak compared to the  $Cu_2O$  sample without the  $Al_2O_3$  layer. This corresponds to the presence of the metallic  $Cu^0$  at the  $Al_2O_3/Cu_2O$  interface, confirming the reduction of  $Cu_2O$  due to TMA exposure. This  $Cu^0$  can remain metallic even after the subsequent pulsing of  $H_2O$ , as the oxidation reactions into  $Cu_2O$  or CuO are not thermodynamically favorable (Table S1a,b). However, the oxidation by residual  $O_2$  in the deposition reactor is possible (Table S1b,c). Furthermore, because the TMA adsorption and dissociation is not favorable on Cu sites, it is feasible to assume that the metallic  $Cu^0$  is not consumed to form  $CuAlO_2$  or oxidized to copper oxides but will remain at the interface, as shown by our results.

The O 1s spectra were also recorded from both samples. The deconvoluted spectra in Figure 5c,d show the oxygen in

lattice  $Cu_2O$  at 530.2 eV, a minor CuO contribution at 529.8 eV, and  $Al_2O_3$  bound oxygen at 531.6 eV, as well as the presence of high hydroxyl concentration ( $\sim$ 532 eV). <sup>45</sup> This is contributed by both the persistent surface hydroxyl groups on the  $Cu_2O$  as well as the remaining -OH species in the  $Al_2O_3$  from the TMA + water process at a relatively low deposition temperature of 150 °C. There is a small difference in the O 1s spectra of the as-deposited and annealed samples, namely in the  $Al_2O_3$  related O content, which may indicate a partial diffusion of the  $Al_2O_3$  related O content, which may indicate a partial diffusion of the  $Al_2O_3$  related O content, which may indicate a partial diffusion of the  $Al_2O_3$  related O content, which may indicate a partial diffusion of the  $Al_2O_3$  related O content, which would lead to a slightly different etching rate during the  $Al_2O_3$  roughly different etching rate  $Al_2O_3$  roughly  $Al_2$

However, the measured ex situ XPS data cannot be reliably used to confirm the presence of the CuAlO2 phase at the Al<sub>2</sub>O<sub>3</sub>/Cu<sub>2</sub>O interface, as the related changes are too subtle to be distinguished from the Al<sub>2</sub>O<sub>3</sub> and Cu<sub>2</sub>O signals within the probed volume. Moreover, we measured the valence spectra of the annealed Cu<sub>2</sub>O and Al<sub>2</sub>O<sub>3</sub>/Cu<sub>2</sub>O samples. Deuermeier et al. reported a shift in the binding energy of a Cu<sub>2</sub>O during the ALD of Al<sub>2</sub>O<sub>3</sub>. In their in situ XPS experiments on ALD Al<sub>2</sub>O<sub>3</sub> growth on the sputtered Cu<sub>2</sub>O surface, the position of the valence band edge  $(E_{\rm F}-E_{\rm VB})$  of the Cu<sub>2</sub>O increased from original 0.4-0.6 eV after the first Al<sub>2</sub>O<sub>3</sub> ALD cycle indicating a formation of Cu/Cu<sub>2</sub>O Schottky junction. 41 Though our core level LMM spectrum showed the formation of the Cu, similar indication of a Schottky junction formation was not observed in the valence spectra and 0.9 eV  $E_{\rm F}-E_{\rm VB}$  was measured for both the original Cu<sub>2</sub>O as well as for the Al<sub>2</sub>O<sub>3</sub>/Cu<sub>2</sub>O interface (see Figure S6). However, this does not exclude the potential Fermi level pinning at the interface due to the reasons explained above.

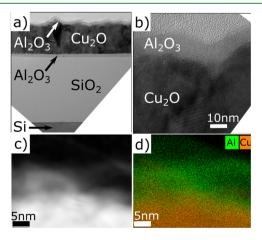

To obtain more evidence on the proposed  $CuAlO_2$  interface layer formation, a sample with 10 nm  $Al_2O_3$  deposited on  $Cu_2O$ , annealed at 300 °C, was imaged with TEM. The TEM and scanning TEM (STEM) coupled with energy dispersive spectroscopy (EDS) elemental mapping were recorded from the film interface (Figure 6) from the very thin edge of the TEM foil.

Figure 6a shows a low magnification image confirming the film stack, with a  $Cu_2O$  film sandwiched between two 10 nm  $Al_2O_3$  films on  $SiO_2/Si$ . In Figure 6b, the enlarged TEM shows the polycrystalline  $Cu_2O$  with the conformal, amorphous  $Al_2O_3$

**Figure 6.** TEM micrographs (a,b) of a  $Cu_2O$  thin film sample with 10 nm  $Al_2O_3$  passivation layer, annealed in 1.5 mbar  $N_2$  for 10 min. (c) STEM image and (d) the corresponding TEM-EDS mapping of Al and Cu at the sample interface.

on top. The STEM image (6c) along with the EDS mapping results (6d) at the interface region reveals a 1–2 nm region at the interface with a mixed Al and Cu oxide composition (Figure 6d). Though the actual composition of this region cannot be reliably determined from the STEM–EDS data, it is in qualitative agreement with the observations by Gharachorlou et al. of a formation of a CuAlO $_2$  layer during the first Al $_2$ O $_3$  cycles according to eq 1.

The partial reduction of the film surface by the TMA can explain the decreased IDS over the whole gate voltage range when the Al2O3 passivation layer is applied, as presented in Figure 2. It has been shown that the inevitable formation of the thin CuO layer on the Cu2O grain surfaces under ambient conditions increases the conductivity of Cu<sub>2</sub>O films, which can affect the device performance.<sup>27</sup> The surface Cu<sub>2</sub>O reduction by TMA thus decreases the film conductivity. However, this reduction mechanism and formation of the interfacial CuAlO<sub>2</sub> do not fully explain the significant improvement in the TFT performance by the decrease in the device off-state current. We tested the effect of the Al2O3 film thickness on the TFT transfer characteristics and observed that when the nominal Al<sub>2</sub>O<sub>3</sub> thickness was 2-5 nm, the device performance was similar to TFTs without the Al<sub>2</sub>O<sub>3</sub> passivation, and the improvement in the TFT transfer characteristics was detected only with thicker, 10 nm Al<sub>2</sub>O<sub>3</sub> layers (see Figure S7). This indicates that the formation of the interface layer by the TMA exposure during the first couple of tens of deposition cycles is not sufficient in improving the device performance, but thicker coverage with the Al<sub>2</sub>O<sub>3</sub> layer is required. The thicker layer can act as an enhanced barrier against oxygen and moisture, but it is unlikely that this is the sole reason for the significant TFT performance improvement. Therefore, the key to the improved characteristics is likely in the properties of the ALD Al<sub>2</sub>O<sub>3</sub> film

A plausible reason for the observed behavior is the high negative fixed charge density ( $Q_f = 10^{-13} \text{ cm}^{-2}$ ) of the ALD Al<sub>2</sub>O<sub>3</sub>, which has traditionally been utilized in c-Si solar cells where it reduces the recombination losses on the Si surface via surface defect density reduction and by field-effect passivation. The field-effect passivation is based on the reduction of electron or hole concentrations on the surface/interface by the means of an intrinsic internal electric field. 46,47 In our measured TFT data, the impact of the field-effect passivation is indicated by the negative shift in the  $V_{\mathrm{TH}}$  and the reduction in the  $I_{\text{off}}$ . It has previously been reported by Han and Flewitt. that the high off-state current in the Cu<sub>2</sub>O TFTs is due to accumulation of minority charge carriers (electrons) at a positive gate voltage regime. We also measured the capacitance of the as-deposited and passivated p-channels (see Figure S8). The results qualitatively show the enhanced hole accumulation in the channel, especially at low frequencies, which supports the hypothesis of the reduced electron accumulation. The application of the field-effect passivation by ALD Al<sub>2</sub>O<sub>3</sub> on the Cu<sub>2</sub>O channel and subsequent annealing can be an effective way in reducing the accumulation of electrons via electrostatic shielding, which leads to the orders of magnitude lower off-state current and, hence, improves the performance of TFTs with Cu<sub>2</sub>O p-channels.

## CONCLUSIONS

p-Type TFTs with ALD grown phase pure polycrystalline  $\text{Cu}_2\text{O}$  channel layer were fabricated. The TFTs with asdeposited films showed only limited switching performance,

due to the unoptimized film properties and processing parameters, but the characteristics were improved by depositing an 10 nm ALD Al<sub>2</sub>O<sub>3</sub> passivation layer on the Cu<sub>2</sub>O channel and by subsequent annealing at 300 °C in low vacuum. The analysis of the transfer characteristics indicates that the improvement is due to the reduced number of trap states at the channel. The detailed investigation of the Al<sub>2</sub>O<sub>3</sub>/ Cu<sub>2</sub>O interface by XPS and TEM showed a partial reduction of Cu<sub>2</sub>O and possible formation of a 1–2 nm thick CuAlO<sub>2</sub> layer. This presents an example of the importance of understanding the surface reactions and interface modification during the ALD growth on multilayer stacks, as it can significantly impact the performance of thin film devices. Here, the reduced copper oxide surface and the formation of the p-type CuAlO<sub>2</sub> layer with a low Cu vacancy formation energy can be beneficial to device operation but cannot solely explain the better performance of the Al<sub>2</sub>O<sub>3</sub> passivated TFTs. Hence, we conclude that the main benefit of the Al<sub>2</sub>O<sub>3</sub> passivation comes from its high negative fixed charge density that reduces the accumulation of electrons in the Cu<sub>2</sub>O channel when positive gate voltage is applied and, thus, reduces the  $I_{\text{off}}$  of the devices. While the field-effect passivation may not be applicable to tradition nanoscale Si-based CMOS devices, as it influences the  $V_{\mathrm{TH}}$  and the transport of charge carriers in ways that can be detrimental to the circuit operation, it can be an useful tool in the development of alternative approaches that utilize p-type oxide semiconductors with moderate charge carrier density.

#### EXPERIMENTAL SECTION

The  $Cu_2O$  films were grown on 5 cm  $\times$  5 cm substrates of thermally grown SiO<sub>2</sub> on p-Si (resistivity 0.001 Ωcm, Si-Mat) by ALD at 200 °C in an ASM F-120 reactor. Copper(II) acetate Cu(OAc)2 with a source temperature of 185  $^{\circ}\text{C}\textsc{,}$  and water vapor was used as precursors. Each Cu<sub>2</sub>O ALD cycle consisted of 2 s Cu(OAc)<sub>2</sub> pulse/2 s purge/1.5 s H<sub>2</sub>O pulse/1.5 s purge, which resulted a growth per cycle of 0.011 nm. A fluorine-free precursor was chosen because residual fluorine impurities can affect the electrical properties of the films, F being a known n-type dopant, and, additionally lead to poor adhesion of the films due to the accumulation of the fluorine into the interfaces.<sup>45</sup> Details of the growth chemistry and materials characterization are published by Iivonen et al. in ref 23. No further optimization of the Cu<sub>2</sub>O film processing or thickness was done regarding the device operation. Bottom gate TFT structures, with the Si substrate acting as a common gate and thermally grown 100 nm thick SiO2 as a gate dielectric, were fabricated with a standard photolithography and nanofabrication methods to test the performance of the Cu<sub>2</sub>O films. The 40 nm Cu<sub>2</sub>O films were patterned by wet etching using diluted (0.025 M aq) HCl, and 100 nm thick Au source and drain electrodes were deposited by thermal evaporation (Edwards Coating System E306A), with a base pressure of 10<sup>-6</sup> mbar. Au was chosen as the electrode material to ensure an Ohmic contact was made between the film and the electrodes. That is because of the high work function (WF) of Au 5.1-5.4 eV<sup>50</sup> that matches the ca. 4.9-5.0 eV WF of Cu<sub>2</sub>O, <sup>27,51</sup> as well as its high standard reduction potential, which avoids electrode oxidation during annealing. After electrode patterning, the device samples were diced, and the Cu<sub>2</sub>O channel was passivated by a 10 nm Al<sub>2</sub>O<sub>3</sub> film grown by ALD (Cambridge Nanotech (Veeco) Savannah S100) at 150 °C with TMA (Sigma-Aldrich) and water vapor. Finally, the devices were annealed in 1.5 mbar  $N_2$  at 200-400 °C for 10 min.

Film thickness was determined with X-ray reflectivity using a PANalytical X'Pert Pro MPD diffractometer, which was also used for XRD measurements. The measurements were performed in the grazing incidence (GIXRD) geometry at an incidence angle of 1°. The same geometry was used with the high-temperature GIXRD

measurements, where an Anton Paar HTK1200N furnace was used for sample heating in 20 mbar  $N_2$  ( $N_2$  flow 40 sccm) and data were collected at 150–600 °C with 15 °C intervals. AFM images were taken with Bruker Multimode 8. The electrical properties of the  $Cu_2O$  films were characterized by Hall-effect measurements using van der Pauw configuration with a magnetic field of 0.2 T at room temperature (MMR Technologies Hall System). TFTs were measured using a Cascade probe station and Agilent B1500A semiconductor device parameter analyzer. The electrical characterizations were performed in dark to suppress the film photoconductivity. In the interface examinations, an ESCALAB (Thermo Fisher Scientific) X-ray microprobe was used for XPS, and the results were analyzed using CasaXPS processing software. TEM imaging was done using FEI TALOS T200X operated at 200 kV with EDS for elemental mapping.

### ASSOCIATED CONTENT

## Supporting Information

The Supporting Information is available free of charge at https://pubs.acs.org/doi/10.1021/acsami.0c18915.

More detailed information and experimental data on Hall mobility; TFT characteristics; high-temperature GIXRD; XPS; and Cu and  $\text{Cu}_2\text{O}$  oxidation (PDF)

#### AUTHOR INFORMATION

#### **Corresponding Author**

Mari Napari — Department of Materials Science and Metallurgy, University of Cambridge, Cambridge CB3 0FS, U.K.; orcid.org/0000-0003-2690-8343; Email: m.p.napari@soton.ac.uk

#### **Authors**

- Tahmida N. Huq Department of Materials Science and Metallurgy, University of Cambridge, Cambridge CB3 0FS, UK

- David J. Meeth Electrical Engineering Division, Department of Engineering, University of Cambridge, Cambridge CB3 0FA, U.K.

- Mikko J. Heikkilä Department of Chemistry, University of Helsinki, Helsinki FI-00014, Finland

- Kham M. Niang Electrical Engineering Division, Department of Engineering, University of Cambridge, Cambridge CB3 0FA, U.K.

- Han Wang School of Materials Engineering, Purdue University, West Lafayette, Indiana 47907, United States; orcid.org/0000-0002-6137-4802

- Tomi Iivonen Department of Chemistry, University of Helsinki, Helsinki FI-00014, Finland; ⊚ orcid.org/0000-0003-1000-5609

- Haiyan Wang School of Materials Engineering, Purdue University, West Lafayette, Indiana 47907, United States; orcid.org/0000-0002-7397-1209

- Markku Leskelä Department of Chemistry, University of Helsinki, Helsinki FI-00014, Finland; orcid.org/0000-0001-5830-2800

- Mikko Ritala Department of Chemistry, University of Helsinki, Helsinki FI-00014, Finland; orcid.org/0000-0002-6210-2980

- Andrew J. Flewitt Electrical Engineering Division,

Department of Engineering, University of Cambridge,

Cambridge CB3 0FA, U.K.; orcid.org/0000-0003-4204-4960

- Robert L. Z. Hoye Department of Materials Science and Metallurgy, University of Cambridge, Cambridge CB3 0FS, U.K.; orcid.org/0000-0002-7675-0065

- Judith L. MacManus-Driscoll Department of Materials Science and Metallurgy, University of Cambridge, Cambridge CB3 0FS, U.K.

Complete contact information is available at: https://pubs.acs.org/10.1021/acsami.0c18915

#### Notes

The authors declare no competing financial interest.

### ACKNOWLEDGMENTS

M.N., T.N.M., A.J.F., and J.L.M.-D. acknowledge funding from the EPSRC grant EP/P027032/1 and PragmatIC Ltd. J.L.M.-D.acknowledges funding from the Royal Academy of Engineering grant CIET 1819\_24. R.L.Z.H. thanks the Royal Academy of Engineering for support via the Research Fellowships scheme (no. RF/201718/1701). H.W. and H.W. acknowledge the support from the U.S. National Science Foundation (NSF, DMR-2016453) for the TEM work at Purdue University.

### REFERENCES

- (1) Hosono, H. Handbook of Visual Display Technology; Chen, J., Cranton, W., Fihn, M., Eds.; Springer Berlin Heidelberg: Berlin, Heidelberg, 2012; pp 729–749.

- (2) Sheng, J.; Hong, T.; Lee, H.-M.; Kim, K.; Sasase, M.; Kim, J.; Hosono, H.; Park, J.-S. Amorphous IGZO TFT with High Mobility of ~70 cm<sup>2</sup>/(V s) via Vertical Dimension Control Using PEALD. *ACS Appl. Mater. Interfaces* **2019**, *11*, 40300–40309.

- (3) Wang, Z.; Nayak, P. K.; Caraveo-Frescas, J. A.; Alshareef, H. N. Recent Developments in p-Type Oxide Semiconductor Materials and Devices. *Adv. Mater.* **2016**, *28*, 3831–3892.

- (4) Nolan, M.; Elliott, S. D. The p-Type Conduction Mechanism in Cu<sub>2</sub>O: a First Principles Study. *Phys. Chem. Chem. Phys.* **2006**, 8, 5350–5358.

- (5) Al-Jawhari, H. A. A Review of Recent Advances in Transparent p-Type Cu<sub>2</sub>O-Based Thin Film Transistors. *Mater. Sci. Semicond. Process.* **2015**, 40, 241–252.

- (6) Zhang, N.; Sun, J.; Gong, H. Transparent p-Type Semi-conductors: Copper-Based Oxides and Oxychalcogenides. *Coatings* **2019**, *9*, 137.

- (7) Matsuzaki, K.; Nomura, K.; Yanagi, H.; Kamiya, T.; Hirano, M.; Hosono, H. Epitaxial Growth of High Mobility Cu<sub>2</sub>O Thin Films and Application to p-Channel Thin Film Transistor. *Appl. Phys. Lett.* **2008**, 93, 202107.

- (8) Zou, X.; Fang, G.; Yuan, L.; Li, M.; Guan, W.; Zhao, X. Top-Gate Low-Threshold Voltage p-Cu<sub>2</sub>O Thin-Film Transistor Grown on SiO<sub>2</sub>/Si Substrate Using a High- $\kappa$  HfON Gate Dielectric. *IEEE Electron Device Lett.* **2010**, 31, 827–829.

- (9) Ran, F.-Y.; Taniguti, M.; Hosono, H.; Kamiya, T. Analyses of Surface and Interfacial Layers in Polycrystalline Cu<sub>2</sub>O Thin-Film Transistors. *J. Disp. Technol.* **2015**, *11*, 720–724.

- (10) Fortunato, E.; Figueiredo, V.; Barquinha, P.; Elamurugu, E.; Barros, R.; Gonçalves, G.; Park, S.-H. K.; Hwang, C.-S.; Martins, R. Thin-film Transistors Based on p-Type Cu<sub>2</sub>O Thin Films Produced at Room Temperature. *Appl. Phys. Lett.* **2010**, *96*, 192102.

- (11) Jeong, C.-Y.; Sohn, J.; Song, S.-H.; Cho, I.-T.; Lee, J.-H.; Cho, E.-S.; Kwon, H.-I. Investigation of the Charge Transport Mechanism and Subgap Density of States in p-Type Cu<sub>2</sub>O Thin-Film Transistors. *Appl. Phys. Lett.* **2013**, *102*, 082103.

- (12) Han, S.; Niang, K. M.; Rughoobur, G.; Flewitt, A. J. Effects of Post-Deposition Vacuum Annealing on Film Characteristics of p-Type Cu<sub>2</sub>O and Its Impact on Thin Film Transistor Characteristics. *Appl. Phys. Lett.* **2016**, *109*, 173502.

- (13) Kim, S. Y.; Ahn, C. H.; Lee, J. H.; Kwon, Y. H.; Hwang, S.; Lee, J. Y.; Cho, H. K. p-Channel Oxide Thin Film Transistors Using Solution-Processed Copper Oxide. *ACS Appl. Mater. Interfaces* **2013**, 5, 2417–2421.

- (14) Jang, J.; Chung, S.; Kang, H.; Subramanian, V. p-Type CuO and  $\text{Cu}_2\text{O}$  Transistors Derived from a Sol-Gel Copper (II) Acetate Monohydrate precursor. *Thin Solid Films* **2016**, 600, 157–161.

- (15) Musselman, K. P.; Marin, A.; Schmidt-Mende, L.; MacManus-Driscoll, J. L. Incompatible Length Scales in Nanostructured Cu<sub>2</sub>O Solar Cells. *Adv. Funct. Mater.* **2012**, *22*, 2202–2208.

- (16) Baby, T. T.; Garlapati, S. K.; Dehm, S.; Häming, M.; Kruk, R.; Hahn, H.; Dasgupta, S. A General Route toward Complete Room Temperature Processing of Printed and High Performance Oxide Electronics. ACS Nano 2015, 9, 3075–3083.

- (17) Cho, M. H.; Seol, H.; Song, A.; Choi, S.; Song, Y.; Yun, P. S.; Chung, K.-B.; Bae, J. U.; Park, K.-S.; Jeong, J. K. Comparative Study on Performance of IGZO Transistors With Sputtered and Atomic Layer Deposited Channel Layer. *IEEE Int. Electron Devices* **2019**, *66*, 1783—1788

- (18) Sheng, J.; Lee, J.-H.; Choi, W.-H.; Hong, T.; Kim, M.; Park, J.-S. Review Article: Atomic Layer Deposition for Oxide Semiconductor Thin Film Transistors: Advances in Research and Development. *J. Vac. Sci. Technol., A* **2018**, *36*, 060801.

- (19) Sheng, J.; Han, K.-L.; Hong, T.; Choi, W.-H.; Park, J.-S. Review of Recent Progresses on Flexible Oxide Semiconductor Thin Film Transistors Based on Atomic Layer Deposition Processes. *J. Semiconduct.* **2018**, *39*, 011008.

- (20) Zardetto, V.; Williams, B. L.; Perrotta, A.; Di Giacomo, F.; Verheijen, M. A.; Andriessen, R.; Kessels, W. M. M.; Creatore, M. Atomic Layer Deposition for Perovskite Solar Cells: Research status, Opportunities and Challenges. Sustainable Energy Fuels 2017, 1, 30–55

- (21) Maeng, W.; Lee, S.-H.; Kwon, J.-D.; Park, J.; Park, J.-S. Atomic Layer Deposited p-Type Copper Oxide Thin Films and the Associated Thin Film Transistor Properties. *Ceram. Int.* **2016**, *42*, 5517–5522.

- (22) Kim, S. H.; Baek, I.-H.; Kim, D. H.; Pyeon, J. J.; Chung, T.-M.; Baek, S.-H.; Kim, J.-S.; Han, J. H.; Kim, S. K. Fabrication of High-Performance p-Type Thin Film Transistors Using Atomic-Layer-Deposited SnO Films. *J. Mater. Chem. C* **2017**, *5*, 3139–3145.

- (23) Iivonen, T.; Heikkilä, M. J.; Popov, G.; Nieminen, H.-E.; Kaipio, M.; Kemell, M.; Mattinen, M.; Meinander, K.; Mizohata, K.; Räisänen, J.; Ritala, M.; Leskelä, M. Atomic Layer Deposition of Photoconductive Cu<sub>2</sub>O Thin Films. *ACS Omega* **2019**, *4*, 11205–11214.

- (24) Muñoz-Rojas, D.; Jordan, M.; Yeoh, C.; Marin, A. T.; Kursumovic, A.; Dunlop, L. A.; Iza, D. C.; Chen, A.; Wang, H.; MacManus Driscoll, J. L. Growth of ~5 cm2V-1s-1 Mobility, p-Type Copper(I) Oxide (Cu<sub>2</sub>O) Films by Fast Atmospheric Atomic Layer Deposition (AALD) at 225°C and Below. *AIP Adv.* **2012**, *2*, 042179.

- (25) Chen, W.-C.; Hsu, P.-C.; Chien, C.-W.; Chang, K.-M.; Hsu, C.-J.; Chang, C.-H.; Lee, W.-K.; Chou, W.-F.; Hsieh, H.-H.; Wu, C.-C. Room-Temperature-Processed Flexible n-InGaZnO/p-Cu<sub>2</sub>O Heterojunction Diodes and High-Frequency Diode Rectifiers. *J. Phys. D: Appl. Phys.* **2014**, *47*, 365101.

- (26) Han, S.; Flewitt, A. J. Analysis of the Conduction Mechanism and Copper Vacancy Density in p-Type Cu<sub>2</sub>O Thin Films. *Sci. Rep.* **2017**, *7*, 5766.

- (27) Deuermeier, J.; Liu, H.; Rapenne, L.; Calmeiro, T.; Renou, G.; Martins, R.; Muñoz-Rojas, D.; Fortunato, E. Visualization of Nanocrystalline CuO in the Grain Boundaries of Cu<sub>2</sub>O Thin Films and Effect on Band Bending and Film Resistivity. *APL Mater.* **2018**, *6*, 096103.

- (28) Chen, Y.-C.; Chang, T.-C.; Li, H.-W.; Chen, S.-C.; Lu, J.; Chung, W.-F.; Tai, Y.-H.; Tseng, T.-Y. Bias-induced Oxygen Adsorption in Zinc Tin Oxide Thin Film Transistors Under Dynamic Stress. *Appl. Phys. Lett.* **2010**, *96*, 262104.

- (29) Hu, S.; Peng, J.; Ning, H.; Lu, K.; Fang, Z.; Tao, R.; Yao, R.; Zou, J.; Xu, M.; Wang, L. Effect of Al<sub>2</sub>O<sub>3</sub> Passivation Layer and Cu

- Electrodes on High Mobility of Amorphous IZO TFT. *IEEE J. Electron Devices* **2018**, *6*, 733–737.

- (30) Hong, S.; Park, S. P.; Kim, Y.-g.; Kang, B. H.; Na, J. W.; Kim, H. J. Low-Temperature Fabrication of an HfO<sub>2</sub> Passivation Layer for Amorphous Indium-Gallium-Zinc Oxide Thin Film Transistors Using a Solution Process. *Sci. Rep.* **2017**, *7*, 16265.

- (31) Tak, Y. J.; Keene, S. T.; Kang, B. H.; Kim, W.-G.; Kim, S. J.; Salleo, A.; Kim, H. J. Multifunctional, Room-Temperature Processable, Heterogeneous Organic Passivation Layer for Oxide Semiconductor Thin-Film Transistors. ACS Appl. Mater. Interfaces 2020, 12, 2615–2624.

- (32) Qu, Y.; Yang, J.; Li, Y.; Zhang, J.; Wang, Q.; Song, A.; Xin, Q. Organic and Inorganic Passivation of p-Type SnO Thin-Film Transistors with Different Active Layer Thicknesses. *Semicond. Sci. Technol.* **2018**, 33, 075001.

- (33) Yao, Z. Q.; Liu, S. L.; Zhang, L.; He, B.; Kumar, A.; Jiang, X.; Zhang, W. J.; Shao, G. Room Temperature Fabrication of p-Channel Cu<sub>2</sub>O Thin-Film Transistors on Flexible Polyethylene Terephthalate Substrates. *Appl. Phys. Lett.* **2012**, *101*, 042114.

- (34) Zou, X.; Fang, G.; Wan, J.; He, X.; Wang, H.; Liu, N.; Long, H.; Zhao, X. Improved Subthreshold Swing and Gate-Bias Stressing Stability of p-Type Cu<sub>2</sub>O Thin-Film Transistors Using a HfO<sub>2</sub> High-k Gate Dielectric Grown on a SiO<sub>2</sub>/Si Substrate by Pulsed Laser Ablation. *IEEE Int. Electron Devices* **2011**, *58*, 2003–2007.

- (35) Sohn, J.; Song, S.-H.; Nam, D.-W.; Cho, I.-T.; Cho, E.-S.; Lee, J.-H.; Kwon, H.-I. Effects of Vacuum Annealing on the Optical and Electrical Properties of p-Type Copper-Oxide Thin-Film Transistors. *Semicond. Sci. Technol.* **2012**, *28*, 015005.

- (36) Nam, D.-W.; Cho, I.-T.; Lee, J.-H.; Cho, E.-S.; Sohn, J.; Song, S.-H.; Kwon, H.-I. Active Layer Thickness Effects on the Structural and Electrical Properties of p-Type Cu<sub>2</sub>O Thin-Film Transistors. *J. Vac. Sci. Technol. B* **2012**, *30*, 060605.

- (37) Lee, S. W.; Liu, Y.; Heo, J.; Gordon, R. G. Creation and Control of Two-Dimensional Electron Gas Using Al-Based Amorphous Oxides/SrTiO<sub>3</sub> Heterostructures Grown by Atomic Layer Deposition. *Nano Lett.* **2012**, *12*, 4775–4783.

- (38) Lee, S. W.; Lee, Y. S.; Heo, J.; Siah, S. C.; Chua, D.; Brandt, R. E.; Kim, S. B.; Mailoa, J. P.; Buonassisi, T.; Gordon, R. G. Improved Cu<sub>2</sub>O-Based Solar Cells Using Atomic Layer Deposition to Control the Cu Oxidation State at the p-n Junction. *Adv. Energy Mater.* **2014**, *4*, 1301916.

- (39) Gharachorlou, A.; Detwiler, M. D.; Gu, X.-K.; Mayr, L.; Klötzer, B.; Greeley, J.; Reifenberger, R. G.; Delgass, W. N.; Ribeiro, F. H.; Zemlyanov, D. Y. Trimethylaluminum and Oxygen Atomic Layer Deposition on Hydroxyl-Free Cu(111). ACS Appl. Mater. Interfaces 2015, 7, 16428–16439.

- (40) Long, R. D.; McIntyre, P. C. Surface Preparation and Deposited Gate Oxides for Gallium Nitride Based Metal Oxide Semiconductor Devices. *Materials* **2012**, *5*, 1297–1335.

- (41) Deuermeier, J.; Bayer, T. J. M.; Yanagi, H.; Kiazadeh, A.; Martins, R.; Klein, A.; Fortunato, E. Substrate Reactivity as the Origin of Fermi Level Pinning at the Cu<sub>2</sub>O/ALD-Al<sub>2</sub>O<sub>3</sub> Interface. *Mater. Res. Express* **2016**, *3*, 046404.

- (42) Elliott, S. D.; Greer, J. C. Simulating the Atomic Layer Deposition of Alumina from First Principles. *J. Mater. Chem.* **2004**, *14*, 3246–3250.

- (43) Kawazoe, H.; Yasukawa, M.; Hyodo, H.; Kurita, M.; Yanagi, H.; Hosono, H. p-Type Electrical Conduction in Transparent Thin Films of CuAlO<sub>2</sub>. *Nature* **1997**, *389*, 939–942.

- (44) Biesinger, M. C. Advanced Analysis of Copper X-ray Photoelectron Spectra. Surf. Interface Anal. 2017, 49, 1325–1334.

- (45) Biesinger, M. C.; Lau, L. W. M.; Gerson, A. R.; Smart, R. S. C. Resolving Surface Chemical States in XPS Analysis of First Row Transition Metals, Oxides and Hydroxides: Sc, Ti, V, Cu and Zn. Appl. Surf. Sci. 2010, 257, 887–898.

- (46) Hoex, B.; Gielis, J. J. H.; van de Sanden, M. C. M.; Kessels, W. M. M. On the c-Si Surface Passivation Mechanism by the Negative-Charge-Dielectric Al<sub>2</sub>O<sub>3</sub>. *J. Appl. Phys.* **2008**, *104*, 113703.

- (47) Dingemans, G.; Kessels, W. M. M. Status and Prospects of Al<sub>2</sub>O<sub>3</sub>-Based Surface Passivation Schemes for Silicon Solar Cells. *J. Vac. Sci. Technol., A* **2012**, *30*, 040802.

- (48) Han, S.; Flewitt, A. J. The Origin of the High Off-State Current in p-Type Cu<sub>2</sub>O Thin Film Transistors. *IEEE Electron Device Lett.* **2017**, 38, 1394–1397.

- (49) Gandikota, S.; Voss, S.; Tao, R.; Duboust, A.; Cong, D.; Chen, L.-Y.; Ramaswami, S.; Carl, D. Adhesion Studies of CVD Copper Metallization. *Microelectron. Eng.* **2000**, *50*, 547–553.

- (50) Uda, M.; Nakamura, A.; Yamamoto, T.; Fujimoto, Y. Work Function of Polycrystalline Ag, Au and Al. J. Electron Spectrosc. 1998, 88–91, 643–648.

- (51) Jagt, R. A.; Huq, T. N.; Hill, S. A.; Thway, M.; Liu, T.; Napari, M.; Roose, B.; Gałkowski, K.; Li, W.; Lin, S. F.; Stranks, S. D.; MacManus-Driscoll, J. L.; Hoye, R. L. Z. Rapid Vapor-Phase Deposition of High-Mobility p-Type Buffer Layers on Perovskite Photovoltaics for Efficient Semitransparent Devices. *ACS Energy Lett.* **2020**, *5*, 2456–2465.